# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f685-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F685 Pin Diagram

| 20-pin PDIP, SOIC, SSOP                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $VDD \longrightarrow \begin{bmatrix} 1\\ RA5/T1CKI/OSC1/CLKIN & \\ 2\\ RA4/AN3/T1G/OSC2/CLKOUT & \\ 3\\ RA3/MCLR/VPP \longrightarrow \begin{bmatrix} 4\\ RC5/CCP1/P1A & \\ 5\\ RC4/C2OUT/P1B & \\ 6\\ RC3/AN7/C12IN3-/P1C & \\ 7\\ RC6/AN8 & \\ 8\\ RC7/AN9 & \\ 9\\ RB7 & \\ 10\\ \end{bmatrix}$ | 20<br>4 Vss<br>19<br>4 RA0/AN0/C1IN+/ICSPDAT/ULPWU<br>18<br>4 RA1/AN1/C12IN0-/VREF/ICSPCLK<br>17<br>4 RA2/AN2/T0CKI/INT/C1OUT<br>16<br>4 RC0/AN4/C2IN+<br>15<br>4 RC0/AN4/C2IN+<br>15<br>4 RC1/AN5/C12IN1-<br>14<br>4 RC2/AN6/C12IN2-/P1D<br>13<br>4 RB4/AN10<br>12<br>4 RB5/AN11<br>11<br>4 RB6 |

### TABLE 3: PIC16F685 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | ECCP     | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|----------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | _      | _        | IOC       | Y       | ICSPDAT     |

| RA1 | 18  | AN1/VREF  | C12IN0-     | _      | —        | IOC       | Y       | ICSPCLK     |

| RA2 | 17  | AN2       | C1OUT       | T0CKI  | —        | IOC/INT   | Y       | —           |

| RA3 | 4   | —         | —           | _      | —        | IOC       | Y(1)    | MCLR/Vpp    |

| RA4 | 3   | AN3       | —           | T1G    | —        | IOC       | Y       | OSC2/CLKOUT |

| RA5 | 2   |           | —           | T1CKI  | —        | IOC       | Y       | OSC1/CLKIN  |

| RB4 | 13  | AN10      | —           | —      | —        | IOC       | Y       | —           |

| RB5 | 12  | AN11      | —           |        | —        | IOC       | Y       | —           |

| RB6 | 11  |           | —           |        | _        | IOC       | Y       | —           |

| RB7 | 10  |           | —           |        | _        | IOC       | Y       | —           |

| RC0 | 16  | AN4       | C2IN+       | —      | _        |           |         | —           |

| RC1 | 15  | AN5       | C12IN1-     |        | _        |           |         | —           |

| RC2 | 14  | AN6       | C12IN2-     |        | P1D      |           |         | —           |

| RC3 | 7   | AN7       | C12IN3-     | _      | P1C      |           |         | —           |

| RC4 | 6   |           | C2OUT       | _      | P1B      |           |         | —           |

| RC5 | 5   | _         | —           | _      | CCP1/P1A |           | _       | —           |

| RC6 | 8   | AN8       | —           | —      | —        | _         | —       | —           |

| RC7 | 9   | AN9       | _           |        | _        | _         | _       | —           |

| —   | 1   |           | _           |        |          | _         | _       | Vdd         |

| —   | 20  |           | _           | _      | _        | _         | _       | Vss         |

**Note 1:** Pull-up activated only with external MCLR configuration.

### FIGURE 2-6: PIC16F685 SPECIAL FUNCTION REGISTERS

|                   | File    |                    | File    |                 | File    |                       | File   |

|-------------------|---------|--------------------|---------|-----------------|---------|-----------------------|--------|

|                   | Address |                    | Address | · · · · · · (1) | Address |                       | Addres |

| ndirect addr. (1) | 00h     | Indirect addr. (1) | 80h     |                 | 100h    | Indirect addr. (1)    | 180h   |

| TMR0              | 01h     | OPTION_REG         | 81h     | TMR0            | 101h    | OPTION_REG            | 181h   |

| PCL               | 02h     | PCL                | 82h     | PCL             | 102h    | PCL                   | 182h   |

| STATUS            | 03h     | STATUS             | 83h     | STATUS          | 103h    | STATUS                | 183h   |

| FSR               | 04h     | FSR                | 84h     | FSR             | 104h    | FSR                   | 184h   |

| PORTA             | 05h     | TRISA              | 85h     | PORTA           | 105h    | TRISA                 | 185h   |

| PORTB             | 06h     | TRISB              | 86h     | PORTB           | 106h    | TRISB                 | 186h   |

| PORTC             | 07h     | TRISC              | 87h     | PORTC           | 107h    | TRISC                 | 187h   |

|                   | 08h     |                    | 88h     |                 | 108h    |                       | 188h   |

|                   | 09h     |                    | 89h     |                 | 109h    |                       | 189h   |

| PCLATH            | 0Ah     | PCLATH             | 8Ah     | PCLATH          | 10Ah    | PCLATH                | 18Ah   |

| INTCON            | 0Bh     | INTCON             | 8Bh     | INTCON          | 10Bh    | INTCON                | 18Bh   |

| PIR1              | 0Ch     | PIE1               | 8Ch     | EEDAT           | 10Ch    | EECON1                | 18Ch   |

| PIR2              | 0Dh     | PIE2               | 8Dh     | EEADR           | 10Dh    | EECON2 <sup>(1)</sup> | 18Dh   |

| TMR1L             | 0Eh     | PCON               | 8Eh     | EEDATH          | 10Eh    |                       | 18Eh   |

| TMR1H             | 0Fh     | OSCCON             | 8Fh     | EEADRH          | 10Fh    |                       | 18Fh   |

| T1CON             | 10h     | OSCTUNE            | 90h     |                 | 110h    |                       | 190h   |

| TMR2              | 11h     |                    | 91h     |                 | 111h    |                       | 191h   |

| T2CON             | 12h     | PR2                | 92h     |                 | 112h    |                       | 192h   |

|                   | 13h     |                    | 93h     |                 | 113h    |                       | 193h   |

|                   | 14h     |                    | 94h     |                 | 114h    |                       | 194h   |

| CCPR1L            | 15h     | WPUA               | 95h     | WPUB            | 115h    |                       | 195h   |

| CCPR1H            | 16h     | IOCA               | 96h     | IOCB            | 116h    |                       | 196h   |

| CCP1CON           | 17h     | WDTCON             | 97h     |                 | 117h    |                       | 197h   |

|                   | 18h     |                    | 98h     | VRCON           | 118h    |                       | 198h   |

|                   | 19h     |                    | 99h     | CM1CON0         | 119h    |                       | 199h   |

|                   | 1Ah     |                    | 9Ah     | CM2CON0         | 11Ah    |                       | 19Ah   |

|                   | 1Bh     |                    | 9Bh     | CM2CON1         | 11Bh    |                       | 19Bh   |

| PWM1CON           | 1Ch     |                    | 9Ch     |                 | 11Ch    |                       | 19Ch   |

| ECCPAS            | 1Dh     |                    | 9Dh     |                 | 11Dh    | PSTRCON               | 19Dh   |

| ADRESH            | 1Eh     | ADRESL             | 9Eh     | ANSEL           | 11Eh    | SRCON                 | 19Eh   |

| ADCON0            | 1Fh     | ADCON1             | 9Fh     | ANSELH          | 11Fh    |                       | 19Fh   |

|                   | 20h     |                    | A0h     |                 | 120h    |                       | 1A0h   |

|                   |         | General            |         | General         |         |                       |        |

| General           |         | Purpose            |         | Purpose         |         |                       |        |

| Purpose           |         | Register           |         | Register        |         |                       |        |

| Register          |         |                    |         |                 |         |                       |        |

| OG Dutoo          |         | 80 Bytes           |         | 80 Bytes        |         |                       |        |

| 96 Bytes          |         |                    | EFh     | ļ               | 16Fh    |                       |        |

|                   |         |                    | F0h     |                 | 170h    |                       | 1F0h   |

|                   | 7Fh     | 70h-7Fh            | FFh     | 70h-7Fh         | 17Fh    | 70h-7Fh               | 1FFh   |

| Bank 0            |         | Bank 1             |         | Bank 2          |         | Bank 3                |        |

**Note 1:** Not a physical register.

### FIGURE 2-8: PIC16F690 SPECIAL FUNCTION REGISTERS

|                    | File    |                       | File    |                     | File    |                       | File    |

|--------------------|---------|-----------------------|---------|---------------------|---------|-----------------------|---------|

|                    | Address |                       | Address |                     | Address |                       | Address |

| Indirect addr. (1) | 00h     | Indirect addr. (1)    | 80h     | Indirect addr. (1)  | 100h    | Indirect addr. (1)    | 180h    |

| TMR0               | 01h     | OPTION_REG            | 81h     | TMR0                | 101h    | OPTION_REG            | 181h    |

| PCL                | 02h     | PCL                   | 82h     | PCL                 | 102h    | PCL                   | 182h    |

| STATUS             | 03h     | STATUS                | 83h     | STATUS              | 103h    | STATUS                | 183h    |

| FSR                | 04h     | FSR                   | 84h     | FSR                 | 104h    | FSR                   | 184h    |

| PORTA              | 05h     | TRISA                 | 85h     | PORTA               | 105h    | TRISA                 | 185h    |

| PORTB              | 06h     | TRISB                 | 86h     | PORTB               | 106h    | TRISB                 | 186h    |

| PORTC              | 07h     | TRISC                 | 87h     | PORTC               | 107h    | TRISC                 | 187h    |

|                    | 08h     |                       | 88h     |                     | 108h    |                       | 188h    |

|                    | 09h     |                       | 89h     |                     | 109h    |                       | 189h    |

| PCLATH             | 0Ah     | PCLATH                | 8Ah     | PCLATH              | 10Ah    | PCLATH                | 18Ah    |

| INTCON             | 0Bh     | INTCON                | 8Bh     | INTCON              | 10Bh    | INTCON                | 18Bh    |

| PIR1               | 0Ch     | PIE1                  | 8Ch     | EEDAT               | 10Ch    | EECON1                | 18Ch    |

| PIR2               | 0Dh     | PIE2                  | 8Dh     | EEADR               | 10Dh    | EECON2 <sup>(1)</sup> | 18Dh    |

| TMR1L              | 0Eh     | PCON                  | 8Eh     | EEDATH              | 10Eh    |                       | 18Eh    |

| TMR1H              | 0Fh     | OSCCON                | 8Fh     | EEADRH              | 10Fh    |                       | 18Fh    |

| T1CON              | 10h     | OSCTUNE               | 90h     |                     | 110h    |                       | 190h    |

| TMR2               | 11h     |                       | 91h     |                     | 111h    |                       | 191h    |

| T2CON              | 12h     | PR2                   | 92h     |                     | 112h    |                       | 192h    |

| SSPBUF             | 13h     | SSPADD <sup>(2)</sup> | 93h     |                     | 113h    |                       | 193h    |

| SSPCON             | 14h     | SSPSTAT               | 94h     |                     | 114h    | -                     | 194h    |

| CCPR1L             | 15h     | WPUA                  | 95h     | WPUB                | 115h    | -                     | 195h    |

| CCPR1H             | 16h     | IOCA                  | 96h     | IOCB                | 116h    | -                     | 196h    |

| CCP1CON            | 17h     | WDTCON                | 97h     |                     | 117h    | -                     | 197h    |

| RCSTA              | 18h     | TXSTA                 | 98h     | VRCON               | 118h    | -                     | 198h    |

| TXREG              | 19h     | SPBRG                 | 99h     | CM1CON0             | 119h    |                       | 199h    |

| RCREG              | 1Ah     | SPBRGH                | 9Ah     | CM2CON0             | 11Ah    |                       | 19Ah    |

|                    | 1Bh     | BAUDCTL               | 9Bh     | CM2CON1             | 11Bh    |                       | 19Bh    |

| PWM1CON            | 1Ch     |                       | 9Ch     |                     | 11Ch    |                       | 19Ch    |

| ECCPAS             | 1Dh     |                       | 9Dh     |                     | 11Dh    | PSTRCON               | 19Dh    |

| ADRESH             | 1Eh     | ADRESL                | 9Eh     | ANSEL               | 11Eh    | SRCON                 | 19Eh    |

| ADCON0             | 1Fh     | ADCON1                | 9Fh     | ANSELH              | 11Fh    |                       | 19Fh    |

|                    | 20h     |                       | A0h     |                     | 120h    |                       | 1A0h    |

|                    |         |                       |         |                     |         |                       |         |

| General            |         | General               |         | General             |         |                       |         |

| General<br>Purpose |         | Purpose<br>Register   |         | Purpose<br>Register |         |                       |         |

| Register           |         | register              |         | register            |         |                       |         |

| -                  |         | 80 Bytes              |         | 80 Bytes            |         |                       |         |

| 96 Bytes           |         |                       | EFh     |                     | 16Fh    |                       |         |

|                    |         | accesses              | F0h     | accesses            | 170h    | accesses              | 1F0h    |

|                    | 7Fh     | 70h-7Fh               | FFh     | 70h-7Fh             | 17Fh    | 70h-7Fh               | 1FFh    |

| Bank 0             | 1       | Bank 1                | 1       | Bank 2              | I       | Bank 3                | I       |

Unimplemented data memory locations, read as '0'.

**Note 1:** Not a physical register.

2: Address 93h also accesses the SSP Mask (SSPMSK) register under certain conditions. See Registers 13-2 and 13-3 for more details.

| Addr | Name                  | Bit 7                 | Bit 6                                         | Bit 5       | Bit 4        | Bit 3               | Bit 2               | Bit 1          | Bit 0                | Value on<br>POR, BOR | Page    |  |

|------|-----------------------|-----------------------|-----------------------------------------------|-------------|--------------|---------------------|---------------------|----------------|----------------------|----------------------|---------|--|

| Bank | 2                     |                       |                                               |             |              | •                   | •                   |                | •                    |                      |         |  |

| 100h | INDF                  | Addressing t          | this location                                 | uses conten | ts of FSR to | address data        | memory (no          | t a physical i | register)            | xxxx xxxx            | 43,200  |  |

| 101h | TMR0                  | Timer0 Modu           | Timer0 Module Register                        |             |              |                     |                     |                |                      |                      |         |  |

| 102h | PCL                   | Program Co            | Program Counter's (PC) Least Significant Byte |             |              |                     |                     |                |                      |                      |         |  |

| 103h | STATUS                | IRP                   | IRP RP1 RP0 TO PD Z DC C 0                    |             |              |                     |                     |                |                      |                      | 35,200  |  |

| 104h | FSR                   | Indirect Data         | Indirect Data Memory Address Pointer          |             |              |                     |                     |                |                      |                      |         |  |

| 105h | PORTA <sup>(4)</sup>  | _                     | _                                             | RA5         | RA4          | RA3                 | RA2                 | RA1            | RA0                  | xx xxxx              | 57,200  |  |

| 106h | PORTB <sup>(4)</sup>  | RB7                   | RB6                                           | RB5         | RB4          | _                   | _                   | -              | _                    | xxxx                 | 67,200  |  |

| 107h | PORTC <sup>(4)</sup>  | RC7                   | RC6                                           | RC5         | RC4          | RC3                 | RC2                 | RC1            | RC0                  | xxxx xxxx            | 74,200  |  |

| 108h | —                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | _                    | _       |  |

| 109h | _                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | _                    | _       |  |

| 10Ah | PCLATH                | _                     | _                                             | _           | Write Bu     | ffer for the up     | oper 5 bits of      | the Program    | Counter              | 0 0000               | 43,200  |  |

| 10Bh | INTCON                | GIE                   | PEIE                                          | TOIE        | INTE         | RABIE               | TOIF                | INTF           | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |  |

| 10Ch | EEDAT                 | EEDAT7                | EEDAT6                                        | EEDAT5      | EEDAT4       | EEDAT3              | EEDAT2              | EEDAT1         | EEDAT0               | 0000 0000            | 118,201 |  |

| 10Dh | EEADR                 | EEADR7 <sup>(3)</sup> | EEADR6                                        | EEADR5      | EEADR4       | EEADR3              | EEADR2              | EEADR1         | EEADR0               | 0000 0000            | 118,201 |  |

| 10Eh | EEDATH <sup>(2)</sup> | _                     | _                                             | EEDATH5     | EEDATH4      | EEDATH3             | EEDATH2             | EEDATH1        | EEDATH0              | 00 0000              | 118,201 |  |

| 10Fh | EEADRH <sup>(2)</sup> | _                     | _                                             | _           | _            | EEADRH3             | EEADRH2             | EEADRH1        | EEADRH0              | 0000                 | 118,201 |  |

| 110h | _                     | Unimplemen            | ted                                           |             |              |                     |                     |                |                      | _                    | _       |  |

| 111h |                       | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | _                    | —       |  |

| 112h | —                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | —                    | —       |  |

| 113h | —                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | —                    | —       |  |

| 114h | _                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      |                      |         |  |

| 115h | WPUB                  | WPUB7                 | WPUB6                                         | WPUB5       | WPUB4        | —                   | _                   | —              | —                    | 1111                 | 68,201  |  |

| 116h | IOCB                  | IOCB7                 | IOCB6                                         | IOCB5       | IOCB4        | —                   | —                   | —              | —                    | 0000                 | 68,201  |  |

| 117h | —                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | —                    | _       |  |

| 118h | VRCON                 | C1VREN                | C2VREN                                        | VRR         | VP6EN        | VR3                 | VR2                 | VR1            | VR0                  | 0000 0000            | 103,201 |  |

| 119h | CM1CON0               | C10N                  | C1OUT                                         | C1OE        | C1POL        | _                   | C1R                 | C1CH1          | C1CH0                | 0000 -000            | 96,201  |  |

| 11Ah | CM2CON0               | C2ON                  | C2OUT                                         | C2OE        | C2POL        | _                   | C2R                 | C2CH1          | C2CH0                | 0000 -000            | 97,201  |  |

| 11Bh | CM2CON1               | MC1OUT                | MC2OUT                                        | _           | _            | _                   |                     | T1GSS          | C2SYNC               | 0010                 | 99,201  |  |

| 11Ch | —                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | —                    | _       |  |

| 11Dh | _                     | Unimplemen            | ited                                          |             |              |                     |                     |                |                      | —                    | _       |  |

| 11Eh | ANSEL                 | ANS7                  | ANS6                                          | ANS5        | ANS4         | ANS3 <sup>(3)</sup> | ANS2 <sup>(3)</sup> | ANS1           | ANS0                 | 1111 1111            | 59,201  |  |

| 11Fh | ANSELH(3)             | _                     | —                                             | —           | —            | ANS11               | ANS10               | ANS9           | ANS8                 | 1111                 | 113,201 |  |

### TABLE 2-3: PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, g = value depends on condition, shaded = unimplemented Note 1: MCLR and WDT Reset does not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the mismatch exists.

**2:** PIC16F685/PIC16F689/PIC16F690 only.

3: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

4: Port pins with analog functions controlled by the ANSEL and ANSELH registers will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets).

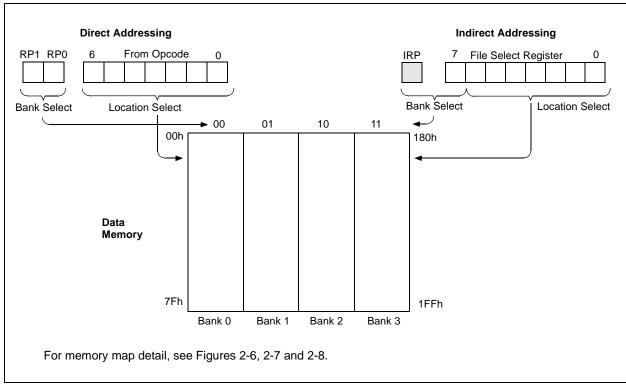

### FIGURE 2-10: DIRECT/INDIRECT ADDRESSING PIC16F631/677/685/687/689/690

### 3.5.2.1 OSCTUNE Register

-n = Value at POR

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

x = Bit is unknown

### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

'1' = Bit is set

| U-0          | U-0 | U-0 R/W-0    |      | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------------|-----|--------------|------|------------------------------------|-------|-------|-------|--|--|

| —            | —   | —            | TUN4 | TUN3                               | TUN2  | TUN1  | TUN0  |  |  |

| bit 7        |     |              |      |                                    |       |       | bit 0 |  |  |

|              |     |              |      |                                    |       |       |       |  |  |

| Legend:      |     |              |      |                                    |       |       |       |  |  |

| R = Readable | bit | W = Writable | bit  | U = Unimplemented bit, read as '0' |       |       |       |  |  |

'0' = Bit is cleared

| bit 7-5 | Unimplemented: Read as '0'                                                |

|---------|---------------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                           |

|         | 01111 = Maximum frequency                                                 |

|         | 01110 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 00001 =                                                                   |

|         | 00000 = Oscillator module is running at the factory-calibrated frequency. |

|         | 11111 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 10000 = Minimum frequency                                                 |

|         |                                                                           |

#### 4.2.5 PIN DESCRIPTIONS AND DIAGRAMS

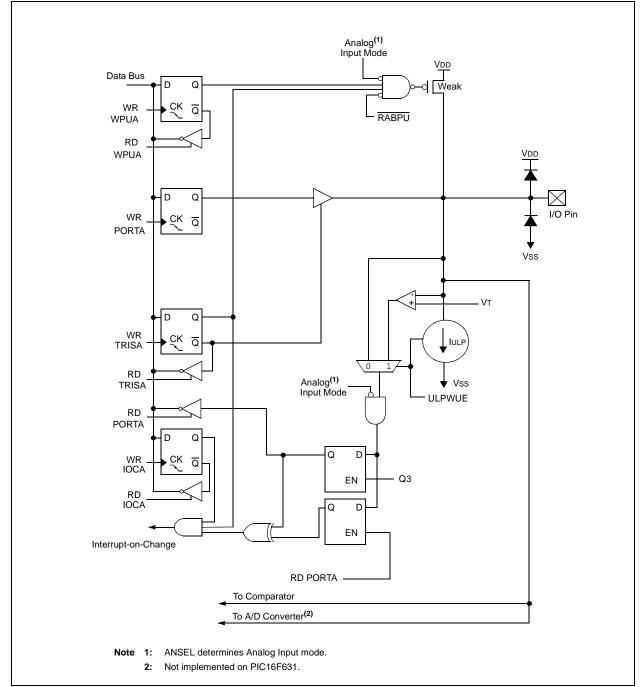

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D Converter (ADC), refer to the appropriate section in this data sheet.

## 4.2.5.1 RA0/AN0/C1IN+/ICSPDAT/ULPWU

Figure 4-2 shows the diagram for this pin. The RA0/ AN0/C1IN+/ICSPDAT/ULPWU pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C1

- In-Circuit Serial Programming<sup>™</sup> data

- · an analog input for the Ultra Low-Power Wake-up

# FIGURE 4-1: BLOCK DIAGRAM OF RA0

| R/W-0         | R/W-0                           | R/W-0             | R/W-0          | R/W-0              | R/W-0           | R/W-0            | R/W-0 |  |  |  |  |  |

|---------------|---------------------------------|-------------------|----------------|--------------------|-----------------|------------------|-------|--|--|--|--|--|

| ADFM          | VCFG                            | CHS3              | CHS2           | CHS1               | CHS0            | GO/DONE          | ADON  |  |  |  |  |  |

| bit 7         |                                 |                   |                |                    |                 |                  | bit 0 |  |  |  |  |  |

|               |                                 |                   |                |                    |                 |                  |       |  |  |  |  |  |

| Legend:       |                                 |                   |                |                    |                 |                  |       |  |  |  |  |  |

| R = Readabl   | e bit                           | W = Writable      | bit            | U = Unimpler       | mented bit, rea | ad as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                             | '1' = Bit is set  |                | '0' = Bit is cle   | ared            | x = Bit is unkn  | own   |  |  |  |  |  |

| 1 2 7         |                                 | о · Б             |                | 1 41.9             |                 |                  |       |  |  |  |  |  |

| bit 7         |                                 | Conversion Res    | sult Format Se | elect bit          |                 |                  |       |  |  |  |  |  |

|               | 1 = Right jus<br>0 = Left justi |                   |                |                    |                 |                  |       |  |  |  |  |  |

| bit 6         | VCFG: Volta                     | ige Reference b   | it             |                    |                 |                  |       |  |  |  |  |  |

|               | 1 = VREF pin                    |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0 = VDD                         |                   |                |                    |                 |                  |       |  |  |  |  |  |

| bit 5-2       | CHS<3:0>:                       | Analog Channe     | el Select bits |                    |                 |                  |       |  |  |  |  |  |

|               | 0000 = AN0                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0001 = AN1                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0010 = AN2                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0011 = AN3                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0100 = AN4                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0101 = AN5<br>0110 - AN6        |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 0110 = AN6<br>0111 = AN7        |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1111 = AN7 $1000 = AN8$         |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1000 = AN9                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1010 = AN1                      |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1011 <b>= AN1</b>               | 1                 |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1100 = CVREF                    |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1101 = 0.6V                     | ' Fixed Voltage I | Reference      |                    |                 |                  |       |  |  |  |  |  |

|               | 1110 = Reserved. Do not use.    |                   |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1111 = Reserved. Do not use.    |                   |                |                    |                 |                  |       |  |  |  |  |  |

| bit 1         | GO/DONE:                        | A/D Conversion    | Status bit     |                    |                 |                  |       |  |  |  |  |  |

|               | $1 = A/D \operatorname{conv}$   | version cycle in  | progress. Set  | ting this bit star | ts an A/D con   | version cycle.   |       |  |  |  |  |  |

|               |                                 |                   |                |                    | e A/D convers   | sion has complet | ed.   |  |  |  |  |  |

|               | $0 = A/D \operatorname{conv}$   | version complet   | ed/not in prog | ress               |                 |                  |       |  |  |  |  |  |

| bit 0         | ADON: ADC                       | Enable bit        |                |                    |                 |                  |       |  |  |  |  |  |

|               | 1 = ADC is e                    | enabled           |                |                    |                 |                  |       |  |  |  |  |  |

|               |                                 | disabled and cor  |                | arating ourrant    |                 |                  |       |  |  |  |  |  |

### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output driver by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- Set the PWM duty cycle by loading the CCPR1L register and DC1B<1:0> bits of the CCP1CON register.

- 5. Configure and start Timer2:

- •Clear the TMR2IF interrupt flag bit of the PIR1 register.

•Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

•Enable Timer2 by setting the TMR2ON bit of the T2CON register.

6. Enable PWM output after a new PWM cycle has started:

•Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

• Enable the CCP1 pin output driver by clearing the associated TRIS bit.

### 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to ten bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-4 shows the pin assignments for each Enhanced PWM mode.

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

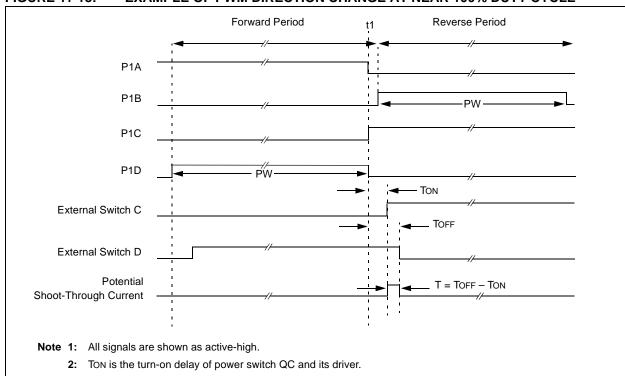

### FIGURE 11-13: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

**3:** TOFF is the turn-off delay of power switch QD and its driver.

### 11.4.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from     |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | Reset, all of the I/O pins are in the high-   |  |  |  |  |  |  |  |  |  |

|       | impedance state. The external circuits        |  |  |  |  |  |  |  |  |  |

|       | must keep the power switch devices in the     |  |  |  |  |  |  |  |  |  |

|       | OFF state until the microcontroller drives    |  |  |  |  |  |  |  |  |  |

|       | the I/O pins with the proper signal levels or |  |  |  |  |  |  |  |  |  |

|       | activates the PWM output(s).                  |  |  |  |  |  |  |  |  |  |

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enabled is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

| R/W-0         | R/W-0                                                                                                                                               | R/W-0                                                                                          | R/W-0             | R/W-0            | R-0              | R-0             | R-x      |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------------|----------|--|--|--|--|--|

| SPEN          | RX9                                                                                                                                                 | SREN                                                                                           | CREN              | ADDEN            | FERR             | OERR            | RX9D     |  |  |  |  |  |

| bit 7         |                                                                                                                                                     |                                                                                                |                   |                  |                  |                 | bit 0    |  |  |  |  |  |

| <u> </u>      |                                                                                                                                                     |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

| Legend:       | • •                                                                                                                                                 |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

| R = Readabl   |                                                                                                                                                     | W = Writable                                                                                   |                   | -                | mented bit, read |                 |          |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                 | '1' = Bit is set                                                                               |                   | '0' = Bit is cle | eared            | x = Bit is unkr | IOWN     |  |  |  |  |  |

| bit 7         | SPEN: Seria                                                                                                                                         | SPEN: Serial Port Enable bit                                                                   |                   |                  |                  |                 |          |  |  |  |  |  |

|               | <ul> <li>1 = Serial port enabled (configures RX/DT and TX/CK pins as serial port pins)</li> <li>0 = Serial port disabled (held in Reset)</li> </ul> |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit R                                                                                                                                 | eceive Enable b                                                                                | oit               |                  |                  |                 |          |  |  |  |  |  |

|               |                                                                                                                                                     | 9-bit reception<br>8-bit reception                                                             |                   |                  |                  |                 |          |  |  |  |  |  |

| bit 5         | SREN: Sing                                                                                                                                          | le Receive Enab                                                                                | ole bit           |                  |                  |                 |          |  |  |  |  |  |

|               | Asynchronous mode:                                                                                                                                  |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | Don't care                                                                                                                                          | Don't care                                                                                     |                   |                  |                  |                 |          |  |  |  |  |  |

|               | •                                                                                                                                                   | Synchronous mode – Master:                                                                     |                   |                  |                  |                 |          |  |  |  |  |  |

|               |                                                                                                                                                     | <ul><li>1 = Enables single receive</li><li>0 = Disables single receive</li></ul>               |                   |                  |                  |                 |          |  |  |  |  |  |

|               |                                                                                                                                                     | 0 = Disables single receive<br>This bit is cleared after reception is complete.                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | Synchronous mode – Slave                                                                                                                            |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | Don't care                                                                                                                                          |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

| bit 4         | CREN: Continuous Receive Enable bit                                                                                                                 |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | Asynchronous mode:                                                                                                                                  |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | 1 = Enables receiver                                                                                                                                |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | 0 = Disables receiver                                                                                                                               |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | Synchronous mode:                                                                                                                                   |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

|               | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul>  |                                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |

| bit 3         | ADDEN: Add                                                                                                                                          | ADDEN: Address Detect Enable bit                                                               |                   |                  |                  |                 |          |  |  |  |  |  |

|               | Asynchronou                                                                                                                                         | us mode 9-bit (F                                                                               | <u> X9 = 1)</u> : |                  |                  |                 |          |  |  |  |  |  |

|               |                                                                                                                                                     | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set |                   |                  |                  |                 |          |  |  |  |  |  |

|               |                                                                                                                                                     | s address detec                                                                                |                   | are received a   | nd ninth bit car | be used as pa   | rity bit |  |  |  |  |  |

|               |                                                                                                                                                     | us mode 8-bit (R                                                                               | (X9 = 0):         |                  |                  |                 |          |  |  |  |  |  |

| <b>h</b> # 0  | Don't care                                                                                                                                          | in a Funan hit                                                                                 |                   |                  |                  |                 |          |  |  |  |  |  |

| bit 2         | FERR: Fram                                                                                                                                          | ing Error bit<br>gerror (can be u                                                              | ndatad by ray     |                  | rogistor and rac |                 | huto)    |  |  |  |  |  |

|               | 1 = Framing<br>0 = No fram                                                                                                                          |                                                                                                | poaled by rea     |                  | register and rec | eive next valid | byle)    |  |  |  |  |  |

| bit 1         | OERR: Over                                                                                                                                          | rrun Error bit                                                                                 |                   |                  |                  |                 |          |  |  |  |  |  |

|               | 1 = Overrun<br>0 = No over                                                                                                                          | n error (can be c<br>run error                                                                 | leared by clea    | aring bit CREN   | )                |                 |          |  |  |  |  |  |

| bit 0         | RX9D: Ninth                                                                                                                                         | bit of Received                                                                                | Data              |                  |                  |                 |          |  |  |  |  |  |

|               | This can be                                                                                                                                         | address/data bit                                                                               | or a parity bi    | it and must be o | calculated by u  | ser firmware.   |          |  |  |  |  |  |

|               |                                                                                                                                                     |                                                                                                | -                 |                  | -                |                 |          |  |  |  |  |  |

# REGISTER 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

|        |                |                                     |                             | SYNC = 0       | , BRGH     | = 1, BRG16                  | = 1 or SY      | ′NC = 1,   | BRG16 = 1                   | _                |            |                             |

|--------|----------------|-------------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc           | Fosc = 20.000 MHz Fosc = 18.432 MHz |                             |                | 2 MHz      | Fosc                        | = 11.059       | 92 MHz     | Fos                         | Fosc = 8.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error                          | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00                                | 16665                       | 300.0          | 0.00       | 15359                       | 300.0          | 0.00       | 9215                        | 300.0            | 0.00       | 6666                        |

| 1200   | 1200           | -0.01                               | 4166                        | 1200           | 0.00       | 3839                        | 1200           | 0.00       | 2303                        | 1200             | -0.02      | 1666                        |

| 2400   | 2400           | 0.02                                | 2082                        | 2400           | 0.00       | 1919                        | 2400           | 0.00       | 1151                        | 2401             | 0.04       | 832                         |

| 9600   | 9597           | -0.03                               | 520                         | 9600           | 0.00       | 479                         | 9600           | 0.00       | 287                         | 9615             | 0.16       | 207                         |

| 10417  | 10417          | 0.00                                | 479                         | 10425          | 0.08       | 441                         | 10433          | 0.16       | 264                         | 10417            | 0          | 191                         |

| 19.2k  | 19.23k         | 0.16                                | 259                         | 19.20k         | 0.00       | 239                         | 19.20k         | 0.00       | 143                         | 19.23k           | 0.16       | 103                         |

| 57.6k  | 57.47k         | -0.22                               | 86                          | 57.60k         | 0.00       | 79                          | 57.60k         | 0.00       | 47                          | 57.14k           | -0.79      | 34                          |

| 115.2k | 116.3k         | 0.94                                | 42                          | 115.2k         | 0.00       | 39                          | 115.2k         | 0.00       | 23                          | 117.6k           | 2.12       | 16                          |

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                |                  |                             |                |                  |                             |                |            |                             |

|--------|------------------|------------------------------------------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |                                                      | Fosc = 3.6864 MHz           |                | Fosc = 2.000 MHz |                             |                | Fosc = 1.000 MHz |                             |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.01                                                 | 3332                        | 300.0          | 0.00             | 3071                        | 299.9          | -0.02            | 1666                        | 300.1          | 0.04       | 832                         |

| 1200   | 1200             | 0.04                                                 | 832                         | 1200           | 0.00             | 767                         | 1199           | -0.08            | 416                         | 1202           | 0.16       | 207                         |

| 2400   | 2398             | 0.08                                                 | 416                         | 2400           | 0.00             | 383                         | 2404           | 0.16             | 207                         | 2404           | 0.16       | 103                         |

| 9600   | 9615             | 0.16                                                 | 103                         | 9600           | 0.00             | 95                          | 9615           | 0.16             | 51                          | 9615           | 0.16       | 25                          |

| 10417  | 10417            | 0.00                                                 | 95                          | 10473          | 0.53             | 87                          | 10417          | 0.00             | 47                          | 10417          | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16                                                 | 51                          | 19.20k         | 0.00             | 47                          | 19.23k         | 0.16             | 25                          | 19.23k         | 0.16       | 12                          |

| 57.6k  | 58.82k           | 2.12                                                 | 16                          | 57.60k         | 0.00             | 15                          | 55.56k         | -3.55            | 8                           | —              | —          | _                           |

| 115.2k | 111.1k           | -3.55                                                | 8                           | 115.2k         | 0.00             | 7                           | _              | _                | —                           | _              | —          | —                           |

# TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

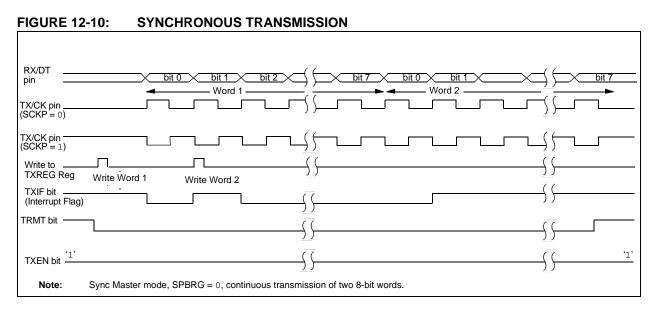

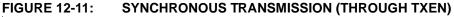

#### TABLE 12-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name                                | Bit 7    | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------------------------|----------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL                             | ABDOVF   | RCIDL      | _           | SCKP   | BRG16 | _      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON                              | GIE      | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| PIE1                                | _        | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1                                | _        | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG                               | EUSART F | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA                               | SPEN     | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG                               | BRG7     | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH                              | BRG15    | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB                               | TRISB7   | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG EUSART Transmit Data Register |          |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA                               | CSRC     | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| Logondu                             | egend:   |            |             |        |       |        |        |        |                      |                                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

## 13.8 Sleep Operation

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to Normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

## 13.9 Effects of a Reset

A Reset disables the SSP module and terminates the current transfer.

### 13.10 Bus Mode Compatibility

Table 13-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

TABLE 13-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |

|-------------------|--------------------|-----|--|--|

| Terminology       | СКР                | CKE |  |  |

| 0,0               | 0                  | 1   |  |  |

| 0,1               | 0                  | 0   |  |  |

| 1,0               | 1                  | 1   |  |  |

| 1,1               | 1                  | 0   |  |  |

There is also a SMP bit which controls when the data is sampled.

| Address               | Name    | Bit 7     | Bit 6         | Bit 5       | Bit 4        | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|---------|-----------|---------------|-------------|--------------|--------------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON  | GIE       | PEIE          | TOIE        | INTE         | RABIE        | TOIF   | INTF   | RABIF  | 0000 000x               | 0000 000x                       |

| 0Ch                   | PIR1    | —         | ADIF          | RCIF        | TXIF         | SSPIF        | CCP1IF | TMR2IF | TMR1IF | -000 0000               | -000 0000                       |

| 13h                   | SSPBUF  | Synchrono | ous Serial Po | ort Receive | Buffer/Trans | smit Registe | r      |        |        | xxxx xxxx               | uuuu uuuu                       |

| 14h                   | SSPCON  | WCOL      | SSPOV         | SSPEN       | CKP          | SSPM3        | SSPM2  | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                       |

| 86h/186h              | TRISB   | TRISB7    | TRISB6        | TRISB5      | TRISB4       | _            | _      | _      | _      | 1111                    | 1111                            |

| 87h/187h              | TRISC   | TRISC7    | TRISC6        | TRISC5      | TRISC4       | TRISC3       | TRISC2 | TRISC1 | TRISC0 | 1111 1111               | 1111 1111                       |

| 8Ch                   | PIE1    | —         | ADIE          | RCIE        | TXIE         | SSPIE        | CCP1IE | TMR2IE | TMR1IE | -000 0000               | -000 0000                       |

| 94h                   | SSPSTAT | SMP       | CKE           | D/A         | Р            | S            | R/W    | UA     | BF     | 0000 0000               | 0000 0000                       |

TABLE 13-2:

REGISTERS ASSOCIATED WITH SPI OPERATION<sup>(1)</sup>

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. Note 1: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

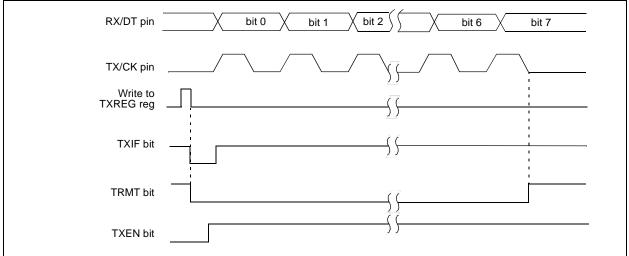

WDT CONTROL

enable it and clearing the bit will disable it.

register. When set, the WDT runs continuously.

The WDTE bit is located in the Configuration Word

When the WDTE bit in the Configuration Word register

is set, the SWDTEN bit of the WDTCON register has no

effect. If WDTE is clear, then the SWDTEN bit can be

used to enable and disable the WDT. Setting the bit will

The PSA and PS<2:0> bits of the OPTION register

have the same function as in previous versions of the PIC16F631/677/685/687/689/690 Family of microcon-

trollers. See Section 5.0 "Timer0 Module" for more

14.5.2

information.

## 14.5 Watchdog Timer (WDT)

The WDT has the following features:

- Operates from the LFINTOSC (31 kHz)

- Contains a 16-bit prescaler

- Shares an 8-bit prescaler with Timer0

- Time-out period is from 1 ms to 268 seconds

- · Configuration bit and software controlled

WDT is cleared under certain conditions described in Table 14-7.

### 14.5.1 WDT OSCILLATOR

The WDT derives its time base from the 31 kHz LFINTOSC. The LTS bit of the OSCCON register does not reflect that the LFINTOSC is enabled.

The value of WDTCON is '---0 1000' on all Resets. This gives a nominal time base of 17 ms.

| Note: | When the Oscillator Start-up Timer (OST)   |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|

|       | is invoked, the WDT is held in Reset,      |  |  |  |  |  |  |

|       | because the WDT Ripple Counter is used     |  |  |  |  |  |  |

|       | by the OST to perform the oscillator delay |  |  |  |  |  |  |

|       | count. When the OST count has expired,     |  |  |  |  |  |  |

|       | the WDT will begin counting (if enabled).  |  |  |  |  |  |  |

### FIGURE 14-9: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 14-7: WDT STATUS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE = 0                                                 | Cleared                      |

| CLRWDT Command                                           |                              |

| Oscillator Fail Detected                                 |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

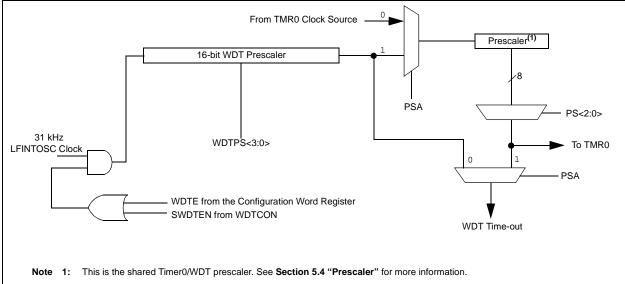

## TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                      |                |                       |      |      |       |                                       |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------------|--|

| Param<br>No. | Sym.                                                                                                                 | Character            | istic          | Min.                  | Тур† | Max. | Units | Conditions                            |  |

| CC01*        | TccL                                                                                                                 | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                       |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | —    | —    | ns    |                                       |  |

| CC02*        | ТссН                                                                                                                 | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                       |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | _    | —    | ns    |                                       |  |

| CC03*        | TccP                                                                                                                 | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale<br>value (1, 4 or<br>16) |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

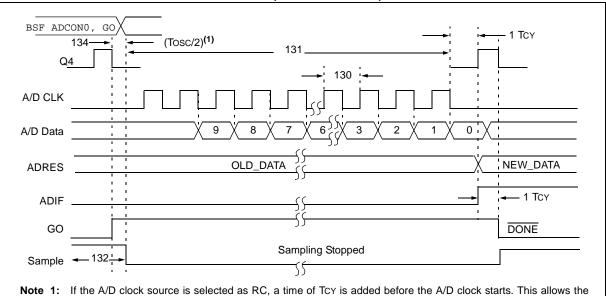

#### FIGURE 17-18: A/D CONVERSION TIMING (NORMAL MODE)

### TABLE 17-16: A/D CONVERSION REQUIREMENTS

SLEEP instruction to be executed.

| Param<br>No. | Sym. | Characteristic                                                        | Min. | Тур†   | Max. | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|-----------------------------------------------------------------------|------|--------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130*         | Tad  | A/D Clock Period                                                      | 1.5  | —      | _    | μS    | Tosc-based, VREF $\ge$ 2.5V                                                                                                                                                                                                |

|              |      |                                                                       | 3.0* | —      | —    | μs    | Tosc-based, VREF full range                                                                                                                                                                                                |