Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | <u>.</u>                                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f685-i-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                       | File<br>Address |                                                   | File<br>Address |                                       | File          |                                             | File<br>Address |

|---------------------------------------|-----------------|---------------------------------------------------|-----------------|---------------------------------------|---------------|---------------------------------------------|-----------------|

| La dia a stata data (1)               | -               | la dina at a dala (1)                             | 1               | lucations et a statu (1)              | Address       | la dina sé a dala (1)                       |                 |

| Indirect addr. <sup>(1)</sup><br>TMR0 | 00h             | Indirect addr. <sup>(1)</sup><br>OPTION REG       | 80h             | Indirect addr. <sup>(1)</sup><br>TMR0 | 100h          | Indirect addr. <sup>(1)</sup><br>OPTION_REG | 180h            |

| PCL                                   | 01h             |                                                   | 81h             |                                       | 101h          |                                             | 181h            |

|                                       | 02h             | PCL                                               | 82h             | PCL                                   | 102h          | PCL                                         | 182h            |

| STATUS                                | 03h             | STATUS                                            | 83h             | STATUS                                | 103h          | STATUS                                      | 183h            |

| FSR                                   | 04h             | FSR                                               | 84h             | FSR                                   | 104h          | FSR                                         | 184h            |

| PORTA                                 | 05h             | TRISA                                             | 85h             | PORTA                                 | 105h          | TRISA                                       | 185h            |

| PORTB<br>PORTC                        | 06h<br>07h      | TRISB<br>TRISC                                    | 86h<br>87h      | PORTB<br>PORTC                        | 106h<br>107h  | TRISB<br>TRISC                              | 186h<br>187h    |

| FURIC                                 | 0711<br>08h     | TRISC                                             | 88h             | FURIC                                 | 10711<br>108h | TRISC                                       | 188h            |

|                                       |                 |                                                   | 89h             |                                       |               |                                             | 189h            |

| PCLATH                                | 09h             | PCLATH                                            |                 | PCLATH                                | 109h<br>104b  | PCLATH                                      | 18Ah            |

| INTCON                                | 0Ah             | INTCON                                            | 8Ah<br>8Bh      | INTCON                                | 10Ah<br>10Bh  | INTCON                                      | 18Bh            |

| PIR1                                  | 0Bh             |                                                   |                 |                                       | 10Bh<br>10Ch  |                                             |                 |

|                                       | 0Ch             | PIE1                                              | 8Ch             | EEDAT                                 | 10Ch          | EECON1                                      | 18Ch            |

| PIR2                                  | 0Dh             | PIE2                                              | 8Dh             | EEADR                                 | 10Dh          | EECON2 <sup>(1)</sup>                       | 18Dh            |

| TMR1L                                 | 0Eh             | PCON                                              | 8Eh             |                                       | 10Eh          |                                             | 18Eh            |

| TMR1H                                 | 0Fh             | OSCCON                                            | 8Fh             |                                       | 10Fh          |                                             | 18Fh            |

| T1CON                                 | 10h             | OSCTUNE                                           | 90h             |                                       | 110h          |                                             | 190h            |

|                                       | 11h             |                                                   | 91h             |                                       | 111h          |                                             | 191h            |

| 0000115                               | 12h             | 000400(2)                                         | 92h             |                                       | 112h          |                                             | 192h            |

| SSPBUF                                | 13h             | SSPADD <sup>(2)</sup>                             | 93h             |                                       | 113h          |                                             | 193h            |

| SSPCON                                | 14h             | SSPSTAT                                           | 94h             |                                       | 114h          |                                             | 194h            |

|                                       | 15h             | WPUA                                              | 95h             | WPUB                                  | 115h          |                                             | 195h            |

|                                       | 16h             | IOCA                                              | 96h             | IOCB                                  | 116h          |                                             | 196h            |

|                                       | 17h             | WDTCON                                            | 97h             |                                       | 117h          |                                             | 197h            |

|                                       | 18h             |                                                   | 98h             | VRCON                                 | 118h          |                                             | 198h            |

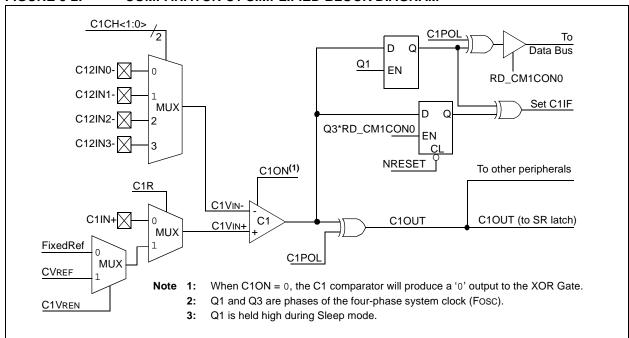

|                                       | 19h             |                                                   | 99h             | CM1CON0                               | 119h          |                                             | 199h            |

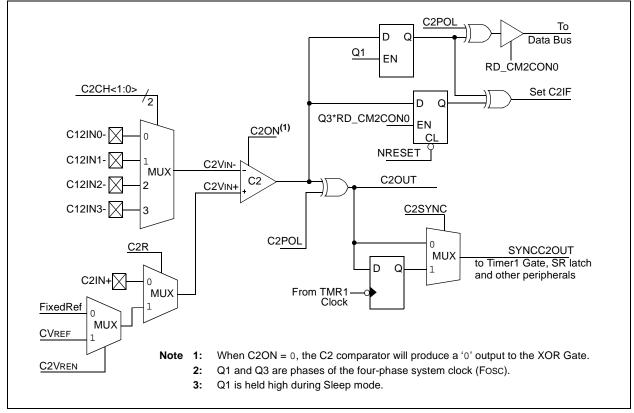

|                                       | 1Ah             |                                                   | 9Ah             | CM2CON0                               | 11Ah          |                                             | 19Ah            |

|                                       | 1Bh             |                                                   | 9Bh             | CM2CON1                               | 11Bh          |                                             | 19Bh            |

|                                       | 1Ch             |                                                   | 9Ch             |                                       | 11Ch          |                                             | 19Ch            |

|                                       | 1Dh             |                                                   | 9Dh             |                                       | 11Dh          |                                             | 19Dh            |

| ADRESH                                | 1Eh             | ADRESL                                            | 9Eh             | ANSEL                                 | 11Eh          | SRCON                                       | 19Eh            |

| ADCON0                                | 1Fh             | ADCON1                                            | 9Fh             | ANSELH                                | 11Fh          |                                             | 19Fh            |

| Quanta                                | 20h             | General<br>Purpose<br>Register                    | A0h             |                                       | 120h          |                                             | 1A0h            |

| General<br>Purpose<br>Register        |                 | 32 Bytes                                          | BFh<br>C0h      |                                       |               |                                             |                 |

| 96 Bytes                              |                 |                                                   | EFh             |                                       | 16Fh          |                                             | 1EFh            |

|                                       | 7Fh             | accesses<br>70h-7Fh                               | F0h<br>FFh      | accesses<br>70h-7Fh                   | 170h<br>17Fh  | accesses<br>70h-7Fh                         | 1F0h<br>1FFh    |

| Bank 0                                | -               | Bank 1                                            | -               | Bank 2                                |               | Bank 3                                      |                 |

| Note 1: Not a                         | physical re     | data memory locat<br>gister.<br>o accesses the SS |                 |                                       | under certa   | in conditions.                              |                 |

#### FIGURE 2-5: PIC16F677 SPECIAL FUNCTION REGISTERS

| FIGURE 3-6:  | INTERNAL OSCILLATOR SWITCH TIMING                         |

|--------------|-----------------------------------------------------------|

|              |                                                           |

| 3698630.960  | LEINTORC (FROM and WOY disalisad)                         |

| HFINTOSC     |                                                           |

| LFINTOSC     | Otart-sp Time Service System Kunning                      |

| IRCF <2:0>   | $\neq 0$ $\chi$ = 0                                       |

| System Clock |                                                           |

| 9898938C     | LFINTOSC (ERNer FSCM of WOT snakied)                      |

| HFINTOSC     |                                                           |

|              | 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 -                   |

| LFINTOSC     |                                                           |

| IRCF <2:0>   | $\neq 0$ $\chi = 0$                                       |

| System Clock |                                                           |

|              |                                                           |

| 1.5937030    | NEWYORC<br>LEWYORC turns of univer WEY or FEOM is enabled |

| EFB/FOSC     |                                                           |

| MERTOSC      |                                                           |

| \$\$CF <33\$ | <u>18.0 X 0</u>                                           |

| System Crosk |                                                           |

|              |                                                           |

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|-------|-------|-------|--------|--------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE | PWRTE | WDTE  | FOSC2  | FOSC1  | FOSC0  | _                    | _                                              |

| OSCCON                | _     | IRCF2 | IRCF1 | IRCF0 | OSTS  | HTS    | LTS    | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | _     | _     | —     | TUN4  | TUN3  | TUN2   | TUN1   | TUN0   | 0 0000               | u uuuu                                         |

| PIE1                  | _     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                                      |

| PIR1                  | -     | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                                      |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 14-1) for operation of all register bits.

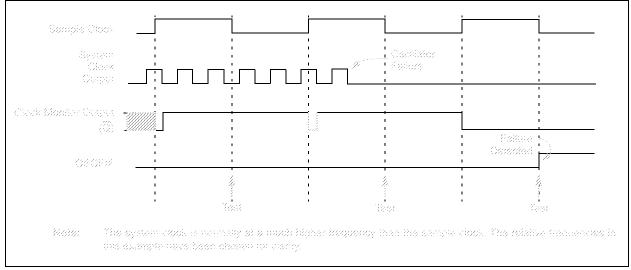

## 4.5.5 RC4/C2OUT/P1B

The RC4/C2OUT/P1B<sup>(1, 2)</sup> is configurable to function as one of the following:

- a general purpose I/O

- a digital output from Comparator C2

- a PWM output

WR

TRISC

RD TRISC RD PORTC

<u>CK</u> Q

- Note 1: Enabling both C2OUT and P1B will cause a conflict on RC4 and create unpredictable results. Therefore, if C2OUT is enabled, the ECCP+ can not be used in Half-Bridge or Full-Bridge mode and vise-versa.

- 2: P1B is available on PIC16F685/ PIC16F690 only.

Available on PIC16F685/PIC16F690 only.

### FIGURE 4-13: BLOCK DIAGRAM OF RC4

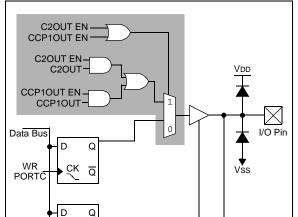

## 4.5.6 RC5/CCP1/P1A

The RC5/CCP1/P1A<sup>(1)</sup> is configurable to function as one of the following:

- a general purpose I/O

- a digital input/output for the Enhanced CCP

- a PWM output

Note 1: CCP1 and P1A are available on PIC16F685/PIC16F690 only.

#### FIGURE 4-14: BLOCK DIAGRAM OF RC5

| TABLE 4-3: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Name                   | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------|--------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| ANSEL                  | ANS7   | ANS6   | ANS5   | ANS4    | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH                 | _      | _      | _      |         | ANS11  | ANS10  | ANS9   | ANS8   | 1111                 | 1111                            |

| CCP1CON <sup>(2)</sup> | P1M1   | P1M0   | DC1B1  | DC1B0   | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 0000 0000            | 0000 0000                       |

| CM2CON0                | C2ON   | C2OUT  | C2OE   | C2POL   | —      | C2R    | C2CH1  | C2CH0  | 0000 -000            | 0000 -000                       |

| CM2CON1                | MC10UT | MC2OUT | _      | -       | _      | _      | T1GSS  | C2SYNC | 0010                 | 0010                            |

| PORTC                  | RC7    | RC6    | RC5    | RC4     | RC3    | RC2    | RC1    | RC0    | XXXX XXXX            | uuuu uuuu                       |

| PSTRCON                | _      | _      | _      | STRSYNC | STRD   | STRC   | STRB   | STRA   | 0 0001               | 0 0001                          |

| SRCON                  | SR1    | SR0    | C1SEN  | C2REN   | PULSS  | PULSR  | _      | _      | 0000 00              | 0000 00                         |

| SSPCON <sup>(1)</sup>  | WCOL   | SSPOV  | SSPEN  | CKP     | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| TRISC                  | TRISC7 | TRISC6 | TRISC5 | TRISC4  | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| VRCON                  | C1VREN | C2VREN | VRR    | VP6EN   | VR3    | VR2    | VR1    | VR0    | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16F687/PIC16F689/PIC16F690 only.

2: PIC16F685/PIC16F690 only.

## 6.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

### 6.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When counting, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC without CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note 1: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or<br>more of the following conditions: |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •Timer1 enabled after POR reset<br>•Write to TMR1H or TMR1L                                                                                                               |

|         | •Timer1 is disabled                                                                                                                                                       |

|         | •Timer1 is disabled (TMR1ON 0) when<br>T1CKI is high then Timer1 is<br>enabled (TMR1ON=1) when T1CKI<br>is low.                                                           |

| 2:      | See Figure 6-2                                                                                                                                                            |

## 6.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 6.4 Timer1 Oscillator

A low-power 32.768 kHz crystal oscillator is built-in between pins OSC1 (input) and OSC2 (amplifier output). The oscillator is enabled by setting the T1OSCEN control bit of the T1CON register. The oscillator will continue to run during Sleep.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is derived from the internal oscillator or when the oscillator is in the LP mode. The user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 bits read as '0' and TRISA5 and TRISA4 bits read as '1'.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

## 6.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 6.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 6.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 6.6 Timer1 Gate

The Timer1 gate (when enabled) allows Timer1 to count when Timer1 gate is active. Timer1 gate source is software configurable to be the T1G pin or the output of Comparator C2. This allows the device to directly time external events using T1G or analog events using Comparator C2. See the CM2CON1 register (Register 8-3) for selecting the Timer1 gate source. This feature can simplify the software for a Delta-Sigma A/D converter and many other applications.

## 8.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in the **Section 17.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

## 8.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their OFF states.

| Name   | Bit 7                         | Bit 6        | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------|--------------|---------|--------|--------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0 | ADFM                          | VCFG         | CHS3    | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 | —                             | ADCS2        | ADCS1   | ADCS0  | _      | _      | _       | -      | -000                 | -000                            |

| ANSEL  | ANS7                          | ANS6         | ANS5    | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH | —                             | —            | —       | —      | ANS11  | ANS10  | ANS9    | ANS8   | 1111                 | 1111                            |

| ADRESH | A/D Result Register High Byte |              |         |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul                     | t Register L | ow Byte |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE                           | PEIE         | TOIE    | INTE   | RABIE  | T0IF   | INTF    | RABIF  | 0000 000x            | x000 000x                       |

| PIE1   | —                             | ADIE         | RCIE    | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | -000 0000            | -000 0000                       |

| PIR1   | _                             | ADIF         | RCIF    | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | -000 0000            | -000 0000                       |

| PORTA  | —                             | —            | RA5     | RA4    | RA3    | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| PORTB  | RB7                           | RB6          | RB5     | RB4    | _      | _      | _       | -      | xxxx                 | uuuu                            |

| PORTC  | RC7                           | RC6          | RC5     | RC4    | RC3    | RC2    | RC1     | RC0    | xxxx xxxx            | uuuu uuuu                       |

| TRISA  | —                             | _            | TRISA5  | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| TRISB  | TRISB7                        | TRISB6       | TRISB5  | TRISB4 | —      | —      | —       | —      | 1111                 | 1111                            |

| TRISC  | TRISC7                        | TRISC6       | TRISC5  | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

### TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

| P1M<1:0> |                                                                | Signal                                                                         | 0                    | Pulse<br>Width  | -                                | PR2+1                |

|----------|----------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------|-----------------|----------------------------------|----------------------|

| 00       | (Single Output)                                                | P1A Modulated                                                                  |                      |                 | Period                           |                      |

|          |                                                                | P1A Modulated                                                                  | Delay <sup>(1)</sup> | )               | <b>→</b><br>Delay <sup>(1)</sup> | <u> </u>             |

| 10       | (Half-Bridge)                                                  | P1B Modulated                                                                  |                      |                 |                                  |                      |

|          |                                                                | P1A Active                                                                     |                      |                 |                                  |                      |

| 01       | (Full-Bridge,<br>Forward)                                      | P1B Inactive                                                                   |                      |                 | <u> </u><br> <br>                | <u> </u>             |

|          | , er maraj                                                     | P1C Inactive                                                                   |                      |                 |                                  | <br>I<br>I           |

|          |                                                                | P1D Modulated                                                                  | <br>'                |                 |                                  |                      |

|          |                                                                | P1A Inactive                                                                   |                      |                 | 1<br>1<br>1                      | 1<br>1<br>1          |

| 11       | (Full-Bridge,<br>Reverse)                                      | P1B Modulated                                                                  |                      |                 |                                  |                      |

|          |                                                                | P1C Active                                                                     |                      |                 | <br>                             |                      |

|          |                                                                | P1D Inactive                                                                   |                      |                 |                                  |                      |

|          | <ul> <li>Pulse Width = To</li> <li>Delay = 4 * Toso</li> </ul> | c * (PR2 + 1) * (TMR2 Presca<br>osc * (CCPR1L<7:0>:CCP1C<br>; * (PWM1CON<6:0>) | ON<5:4>) * (TN       |                 |                                  | ,                    |

| N        | ote 1: Dead-ban<br>mode").                                     | d delay is programmed usi                                                      | ng the PWM10         | CON register (S | Section 11.4.6 "Progra           | ammable Dead-Band De |

## FIGURE 11-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

© 2005-2015 Microchip Technology Inc.

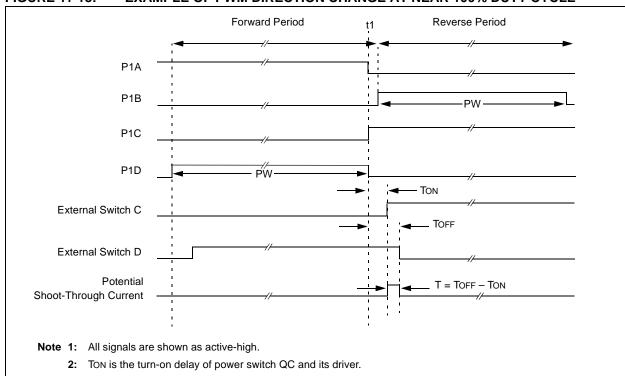

### FIGURE 11-13: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

**3:** TOFF is the turn-off delay of power switch QD and its driver.

## 11.4.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from     |

|-------|-----------------------------------------------|

|       | Reset, all of the I/O pins are in the high-   |

|       | impedance state. The external circuits        |

|       | must keep the power switch devices in the     |

|       | OFF state until the microcontroller drives    |

|       | the I/O pins with the proper signal levels or |

|       | activates the PWM output(s).                  |

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enabled is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

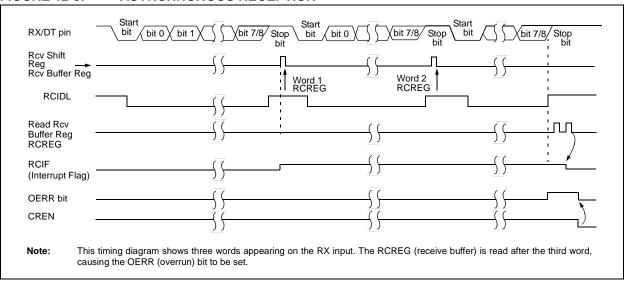

#### 12.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 12.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

### FIGURE 12-5: ASYNCHRONOUS RECEPTION

### 12.3.2 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCTL register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 12-7), and asynchronously if the device is in Sleep mode (Figure 12-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 12.3.2.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

### FIGURE 12-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| 0400      | nininin     | punuinuinu | pinnin. | 9.1        | n na na shi       | uhuhu         | ЪĮ,          | ununun. | punun.    | nupunun              | 1. N.    | punununy | րարարա      |

|-----------|-------------|------------|---------|------------|-------------------|---------------|--------------|---------|-----------|----------------------|----------|----------|-------------|

|           | BR set by p | 98 ·····   | s<br>   | :          | ;                 | :<br>         | ;            |         | :         | ;<br>; ;             | :<br>    |          | Osaced      |

| 9863 b8   |             |            | **<br>5 | 1          |                   | 5<br>5        |              |         | -         |                      |          | ×        |             |

| 8X3211338 |             | :<br>;     | ;<br>;; | :<br>:     | :<br>annaannain   | Herene        | )<br>1       |         | 1<br>1    | , :<br>.aaaaaaaaaaaa | di Santa | ·        |             |

|           |             |            | :       | : ?<br>: ? | 444444444444<br>: | 969ilite.<br> | анта<br>29 с |         | ¢         | yaaqaaaaaaa<br>t     |          | :        |             |

| 8081      |             |            | ·       | · /        |                   |               |              | ·····   |           | t                    |          |          |             |

|           |             |            | :<br>:  | ÷          |                   |               | ÷            |         | pares dos | ાંગ ફેલ્લ્સ શેલ્થ    | C C (    | KCREG)   |             |

| 377       |             | ANGAN MANA | MAMAMA  | Ille       | UMANNANNA         | MAANAA        | MA           |         | MAAMAA.   | CANTAN MAN           | aan      |          | UNICH MANDA |

### 13.5 Master Mode

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 13-2) is to broadcast data by the software protocol.

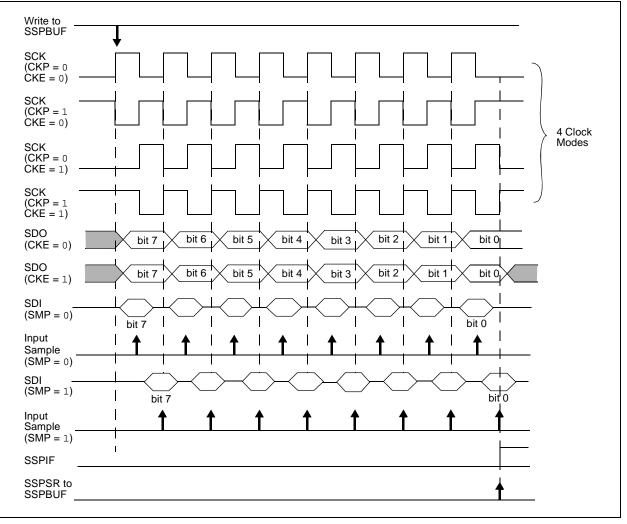

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). This could be useful in receiver applications as a Line Activity Monitor mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. This then, would give waveforms for SPI communication as shown in Figure 13-3, Figure 13-5 and Figure 13-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2 (No SSP module, PIC16F690 only)

Figure 13-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 13-3: SPI MODE WAVEFORM (MASTER MODE)

| Register   | Address               | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |

|------------|-----------------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| W          | —                     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| INDF       | 00h/80h/<br>100h/180h | XXXX XXXX      | XXXX XXXX                                                 | <u>uuuu</u> uuuu                                                                      |

| TMR0       | 01h/101h              | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCL        | 02h/82h/<br>102h/182h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS     | 03h/83h/<br>103h/183h | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                                                              |

| FSR        | 04h/84h/<br>104h184h  | XXXX XXXX      | սսսս սսսս                                                 | <u>uuuu</u> uuuu                                                                      |

| PORTA      | 05h/105h              | xx xxxx        | uu uuuu                                                   | uu uuuu                                                                               |

| PORTB      | 06h/106h              | xxxx           | uuuu                                                      | uuuu                                                                                  |

| PORTC      | 07h/107h              | xxxx xxxx      | uuuu uuuu                                                 | սսսս սսսս                                                                             |

| PCLATH     | 0Ah/8Ah/<br>10Ah/18Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |

| INTCON     | 0Bh/8Bh/<br>10Bh/18Bh | 0000 000x      | 0000 000u                                                 | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR1       | 0Ch                   | -000 0000      | -000 0000                                                 | -uuu uuuu <sup>(2)</sup>                                                              |

| PIR2       | 0Dh                   | 0000           | 0000                                                      | uuuu <b>(2)</b>                                                                       |

| TMR1L      | 0Eh                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR1H      | 0Fh                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| T1CON      | 10h                   | 0000 0000      | <u>uuuu</u> uuuu                                          | սսսս սսսս                                                                             |

| TMR2       | 11h                   | 0000 0000      | 0000 0000                                                 | <u>uuuu</u> uuuu                                                                      |

| T2CON      | 12h                   | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |

| SSPBUF     | 13h                   | xxxx xxxx      | uuuu uuuu                                                 | <u>uuuu</u> uuuu                                                                      |

| SSPCON     | 14h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| CCPR1L     | 15h                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCPR1H     | 16h                   | xxxx xxxx      | uuuu uuuu                                                 | <u>uuuu</u> uuuu                                                                      |

| CCP1CON    | 17h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| RCSTA      | 18h                   | 0000 000x      | 0000 000x                                                 | uuuu uuuu                                                                             |

| TXREG      | 19h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| RCREG      | 1Ah                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| PWM1CON    | 1Ch                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| ECCPAS     | 1Dh                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| ADRESH     | 1Eh                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| ADCON0     | 1Fh                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |

| OPTION_REG | 81h/181h              | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |

| TRISA      | 85h/185h              | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPM < 3:0 > = 1001.

## 15.2 Instruction Descriptions

| ADDLW            | Add literal and W                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ADDLW k                                                                                                        |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                      |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                               |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

|                  |                                                                     |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDLW k                                                                                                      |

| Operands:        | $0 \le k \le 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |

| Status Affected: | Z                                                                                                                    |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                         |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

AND W with f

ANDWF

# TABLE 17-18:ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V,<br/>VREF $\geq$ 2.5V)

| ADC Clock Period (TAD) |           | Device Frequency (Fosc) |               |               |         |  |

|------------------------|-----------|-------------------------|---------------|---------------|---------|--|

| ADC Clock Source       | ADCS<2:0> | 20 MHz                  | 8 MHz         | 4 MHz         | 1 MHz   |  |

| Fosc/2                 | 000       | 100 ns                  | 250 ns        | 500 ns        | 2.0 μs  |  |

| Fosc/4                 | 100       | 200 ns                  | 500 ns        | 1.0 μs        | 4.0 μs  |  |

| Fosc/8                 | 001       | 400 ns                  | 1.0 μs        | 2.0 μs        | 8.0 μs  |  |

| Fosc/16                | 101       | 800 ns                  | 2.0 μs        | 4.0 μs        | 16.0 μs |  |

| Fosc/32                | 010       | 1.6 μs                  | 4.0 μs        | 8.0 μs        | 32.0 μs |  |

| Fosc/64                | 110       | 3.2 μs                  | 8.0 μs        | 16.0 μs       | 64.0 μs |  |

| Frc                    | x11       | 2-6 μs                  | <b>2-6</b> μs | <b>2-6</b> μs | 2-6 μs  |  |

Legend: Shaded cells should not be used for conversions at temperatures above +125°C.

**Note 1:** TAD must be between 1.6  $\mu$ s and 4.0  $\mu$ s.

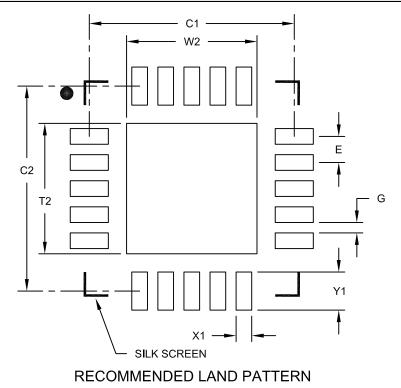

# 20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

|                            | MILLIMETERS      |          |      |      |  |

|----------------------------|------------------|----------|------|------|--|

| Dimensior                  | Dimension Limits |          | NOM  | MAX  |  |

| Contact Pitch E            |                  | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2               |          |      | 2.50 |  |

| Optional Center Pad Length | T2               |          |      | 2.50 |  |

| Contact Pad Spacing        | C1               |          | 3.93 |      |  |

| Contact Pad Spacing        | C2               |          | 3.93 |      |  |

| Contact Pad Width          | X1               |          |      | 0.30 |  |

| Contact Pad Length         | Y1               |          |      | 0.73 |  |

| Distance Between Pads      | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A