# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f685-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16F677 Pin Diagram

| 20-pin PDIP, SOIC, SSOP |                             |

|-------------------------|-----------------------------|

| VDD                     | 15 <b>→</b> RC1/AN5/C12IN1- |

#### TABLE 2: PIC16F631 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | Interrupt | Pull-up | Basic       |  |  |

|-----|-----|-----------|-------------|--------|-----------|---------|-------------|--|--|

| RA0 | 19  | AN0/ULPWU | C1IN+       | —      | IOC       | Y       | ICSPDAT     |  |  |

| RA1 | 18  | AN1       | C12IN0-     |        | IOC       | Y       | ICSPCLK     |  |  |

| RA2 | 17  | —         | C1OUT       | T0CKI  | IOC/INT   | Y       | —           |  |  |

| RA3 | 4   | —         | —           | —      | IOC       | Y(1)    | MCLR/VPP    |  |  |

| RA4 | 3   | —         | —           | T1G    | IOC       | Y       | OSC2/CLKOUT |  |  |

| RA5 | 2   | —         | —           | T1CKI  | IOC       | Y       | OSC1/CLKIN  |  |  |

| RB4 | 13  |           | —           | —      | IOC       | Y       | —           |  |  |

| RB5 | 12  | _         | —           | —      | IOC       | Y       | —           |  |  |

| RB6 | 11  |           | —           | —      | IOC       | Y       | —           |  |  |

| RB7 | 10  |           | —           |        | IOC       | Y       | —           |  |  |

| RC0 | 16  | AN4       | C2IN+       | —      |           |         | —           |  |  |

| RC1 | 15  | AN5       | C12IN1-     | _      |           |         | —           |  |  |

| RC2 | 14  | AN6       | C12IN2-     |        |           |         | —           |  |  |

| RC3 | 7   | AN7       | C12IN3-     |        |           |         | —           |  |  |

| RC4 | 6   | _         | C2OUT       | _      | _         | _       | —           |  |  |

| RC5 | 5   |           | —           |        |           |         | —           |  |  |

| RC6 | 8   |           | _           | _      |           | _       | _           |  |  |

| RC7 | 9   | _         |             |        |           | —       | —           |  |  |

|     | 1   |           |             |        |           | -       | Vdd         |  |  |

| _   | 20  |           |             | _      | _         | _       | Vss         |  |  |

**Note 1:** Pull-up enabled only with external MCLR configuration.

### 2.2 Data Memory Organization

The data memory (see Figures 2-6 through 2-8) is partitioned into four banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. The General Purpose Registers, implemented as static RAM, are located in the last 96 locations of each Bank. Register locations F0h-FFh in Bank 1, 170h-17Fh in Bank 2 and 1F0h-1FFh in Bank 3 point to addresses 70h-7Fh in Bank 0. The actual number of General Purpose Resisters (GPR) in each Bank depends on the device. Details are shown in Figures 2-4 through 2-8. All other RAM is unimplemented and returns '0' when read. RP<1:0> of the STATUS register are the bank select bits:

#### <u>RP1</u> <u>RP0</u>

| 0 | 0 | $\rightarrow$ | Bank 0 is selected |

|---|---|---------------|--------------------|

| 0 | 1 | $\rightarrow$ | Bank 1 is selected |

| 1 | 0 | $\rightarrow$ | Bank 2 is selected |

1 1  $\rightarrow$  Bank 3 is selected

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 in the PIC16F687 and 256 x 8 in the PIC16F685/PIC16F689/ PIC16F690. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see **Section 2.4 "Indirect Addressing, INDF and FSR Registers"**).

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Tables 2-1 through 2-4). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Registers related to the operation of peripheral features are described in the section of that peripheral feature.

| GURE 2-7:                              | File                       | F687/PIC16F68                                          | File              |                                                          |               |                       | File         |

|----------------------------------------|----------------------------|--------------------------------------------------------|-------------------|----------------------------------------------------------|---------------|-----------------------|--------------|

|                                        |                            |                                                        |                   |                                                          | File          |                       | File         |

| Indirect addr. (1)                     | Address                    | ladias et e dela (1)                                   | Address           | ladias et e dala (1)                                     | Address       | Indinent ender (1)    | Addres       |

|                                        |                            | Indirect addr. <sup>(1)</sup>                          |                   | Indirect addr. <sup>(1)</sup>                            |               | Indirect addr. (1)    |              |

| TMR0<br>PCL                            | 01h                        | OPTION_REG<br>PCL                                      | 81h<br>82b        | TMR0<br>PCL                                              | 101h<br>102h  | OPTION_REG<br>PCL     | 181h         |

| STATUS                                 | 02h<br>03h                 | STATUS                                                 | 82h<br>83h        | STATUS                                                   | 102h<br>103h  | STATUS                | 182h<br>183h |

| FSR                                    | -                          | FSR                                                    |                   | FSR                                                      |               | FSR                   |              |

|                                        | 04h                        |                                                        | 84h               | PORTA                                                    | 104h<br>105h  |                       | 184h         |

| PORTA<br>PORTB                         | 05h<br>06h                 | TRISA<br>TRISB                                         | 85h<br>86h        | PORTA                                                    | 105h<br>106h  | TRISA<br>TRISB        | 185h<br>186h |

| PORTE                                  | 00n<br>07h                 | TRISE                                                  | 87h               | PORTE                                                    | 106h<br>107h  | TRISE                 | 187h         |

| FURIC                                  | 08h                        | TRIBC                                                  | 88h               | FORTC                                                    | 107h<br>108h  | TRISC                 | 188h         |

|                                        | 09h                        |                                                        | 89h               |                                                          | 109h          |                       | 189h         |

| PCLATH                                 | 0Ah                        | PCLATH                                                 | 8Ah               | PCLATH                                                   | 10911<br>10Ah | PCLATH                | 18Ah         |

| INTCON                                 | 0Bh                        | INTCON                                                 | 8Bh               | INTCON                                                   | 10An<br>10Bh  | INTCON                | 18Bh         |

| PIR1                                   | 0Ch                        | PIE1                                                   | 8Ch               | EEDAT                                                    | 10Dh          | EECON1                | 18Ch         |

|                                        | -                          |                                                        |                   |                                                          |               | EECON2 <sup>(1)</sup> |              |

| PIR2                                   | 0Dh                        | PIE2                                                   | 8Dh               | EEADR                                                    | 10Dh          | EECONZY               | 18Dh         |

| TMR1L                                  | 0Eh                        | PCON                                                   | 8Eh               | EEDATH <sup>(3)</sup>                                    | 10Eh          |                       | 18Eh         |

| TMR1H                                  | 0Fh                        | OSCCON                                                 | 8Fh               | EEADRH <sup>(3)</sup>                                    | 10Fh          |                       | 18Fh         |

| T1CON                                  | 10h                        | OSCTUNE                                                | 90h               |                                                          | 110h          |                       | 190h         |

|                                        | 11h                        |                                                        | 91h               |                                                          | 111h          |                       | 191h         |

|                                        | 12h                        | (2)                                                    | 92h               |                                                          | 112h          |                       | 192h         |

| SSPBUF                                 | 13h                        | SSPADD <sup>(2)</sup>                                  | 93h               |                                                          | 113h          |                       | 193h         |

| SSPCON                                 | 14h                        | SSPSTAT                                                | 94h               |                                                          | 114h          |                       | 194h         |

|                                        | 15h                        | WPUA                                                   | 95h               | WPUB                                                     | 115h          |                       | 195h         |

|                                        | 16h                        | IOCA                                                   | 96h               | IOCB                                                     | 116h          |                       | 196h         |

|                                        | 17h                        | WDTCON                                                 | 97h               |                                                          | 117h          |                       | 197h         |

| RCSTA                                  | 18h                        | TXSTA                                                  | 98h               | VRCON                                                    | 118h          |                       | 198h         |

| TXREG                                  | 19h                        | SPBRG                                                  | 99h               | CM1CON0                                                  | 119h          |                       | 199h         |

| RCREG                                  | 1Ah                        | SPBRGH                                                 | 9Ah               | CM2CON0                                                  | 11Ah          |                       | 19Ah         |

|                                        | 1Bh                        | BAUDCTL                                                | 9Bh               | CM2CON1                                                  | 11Bh          |                       | 19Bh         |

|                                        | 1Ch                        |                                                        | 9Ch               |                                                          | 11Ch          |                       | 19Ch         |

|                                        | 1Dh                        |                                                        | 9Dh               |                                                          | 11Dh          | 00001                 | 19Dh         |

| ADRESH                                 | 1Eh                        | ADRESL                                                 | 9Eh               | ANSEL                                                    | 11Eh          | SRCON                 | 19Eh         |

| ADCON0                                 | 1Fh                        | ADCON1                                                 | 9Fh               | ANSELH                                                   | 11Fh          |                       | 19Fh         |

| General<br>Purpose<br>Register         | 20h                        | General<br>Purpose<br>Register<br>32 Bytes<br>48 Bytes | A0h<br>BFh<br>C0h | General<br>Purpose<br>Register<br>80 Bytes<br>(PIC16F689 | 120h          |                       | 1A0h         |

| 96 Bytes                               |                            | (PIC16F689<br>only)                                    | EFh               | only)                                                    |               |                       |              |

|                                        | 7Fh                        | accesses<br>70h-7Fh                                    | F0h<br>FFh        | accesses<br>70h-7Fh                                      | 170h<br>17Fh  | accesses<br>70h-7Fh   | 1F0h<br>1FFh |

| Bank 0                                 | 1                          | Bank 1                                                 | I                 | Bank 2                                                   | I             | Bank 3                |              |

| lote 1: Not a p<br>2: Addres<br>See Re | ohysical reg<br>s 93h also | •                                                      | P Mask (SS        | as '0'.<br>SPMSK) register u                             | nder certai   | n conditions.         |              |

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0               | R/W-0               | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIE <sup>(5)</sup> | RCIE <sup>(3)</sup> | TXIE <sup>(3)</sup> | SSPIE <sup>(4)</sup> | CCP1IE <sup>(2)</sup> | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:        |             |                                                    |                                        |                    |

|----------------|-------------|----------------------------------------------------|----------------------------------------|--------------------|

| R = Read       | able bit    | W = Writable bit                                   | U = Unimplemented bit,                 | read as '0'        |

| -n = Value     | at POR      | '1' = Bit is set                                   | '0' = Bit is cleared                   | x = Bit is unknown |

| L : L <b>7</b> | 11          |                                                    |                                        |                    |

| bit 7          | -           | mented: Read as '0'                                | . –                                    |                    |

| bit 6          |             | D Converter (ADC) Interrupt                        | t Enable bit                           |                    |

|                |             | bles the ADC interrupt<br>bles the ADC interrupt   |                                        |                    |

| bit 5          |             | USART Receive Interrupt Er                         | able hit(3)                            |                    |

| Dit J          |             | bles the EUSART receive inter                      |                                        |                    |

|                |             | bles the EUSART receive int                        |                                        |                    |

| bit 4          |             | JSART Transmit Interrupt Er                        |                                        |                    |

|                |             | bles the EUSART transmit in                        |                                        |                    |

|                | 0 = Disa    | bles the EUSART transmit ir                        | nterrupt                               |                    |

| bit 3          | SSPIE: S    | Synchronous Serial Port (SS                        | P) Interrupt Enable bit <sup>(4)</sup> |                    |

|                |             | bles the SSP interrupt                             |                                        |                    |

|                |             | bles the SSP interrupt                             |                                        |                    |

| bit 2          |             | CCP1 Interrupt Enable bit <sup>(2</sup>            | )                                      |                    |

|                |             | bles the CCP1 interrupt<br>bles the CCP1 interrupt |                                        |                    |

| bit 1          |             | : Timer2 to PR2 Match Interr                       | upt Enable bit <sup>(1)</sup>          |                    |

|                |             | bles the Timer2 to PR2 match                       | •                                      |                    |

|                |             | bles the Timer2 to PR2 matc                        |                                        |                    |

| bit 0          | TMR1IE:     | : Timer1 Overflow Interrupt E                      | Enable bit                             |                    |

|                |             | oles the Timer1 overflow inte                      | •                                      |                    |

|                | 0 = Disa    | bles the Timer1 overflow inte                      | errupt                                 |                    |

| Note 1:        |             | IC16F690 only.                                     |                                        |                    |

| 2:             |             | IC16F689/PIC16F690 only.                           |                                        |                    |

| 3:             | PIC16F687/P | IC16F689/PIC16F690 only.                           |                                        |                    |

4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

#### 3.5.2.1 OSCTUNE Register

-n = Value at POR

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

x = Bit is unknown

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

'1' = Bit is set

| U-0                               | U-0 | U-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|-----------------------------------|-----|-----|-------|--------------|------------------|----------|-------|

| —                                 | —   | —   | TUN4  | TUN3         | TUN2             | TUN1     | TUN0  |

| bit 7                             |     |     |       |              |                  |          | bit 0 |

|                                   |     |     |       |              |                  |          |       |

| Legend:                           |     |     |       |              |                  |          |       |

| R = Readable bit W = Writable bit |     |     | bit   | U = Unimpler | nented bit, read | l as '0' |       |

'0' = Bit is cleared

| bit 7-5 | Unimplemented: Read as '0'                                                |

|---------|---------------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                           |

|         | 01111 = Maximum frequency                                                 |

|         | 01110 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 00001 =                                                                   |

|         | 00000 = Oscillator module is running at the factory-calibrated frequency. |

|         | 11111 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 10000 = Minimum frequency                                                 |

|         |                                                                           |

## 4.2 Additional Pin Functions

Every PORTA pin on this device family has an interrupton-change option and a weak pull-up option. RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

### 4.2.1 ANSEL AND ANSELH REGISTERS

The ANSEL and ANSELH registers are used to disable the input buffers of I/O pins, which allow analog voltages to be applied to those pins without causing excessive current. Setting the ANSx bit of a corresponding pin will cause all digital reads of that pin to return '0' and also permit analog functions of that pin to operate correctly.

The state of the ANSx bit has no effect on the digital output function of its corresponding pin. A pin with the TRISx bit clear and ANSx bit set will operate as a digital output, together with the analog input function of that pin. Pins with the ANSx bit set always read '0', which can cause unexpected behavior when executing read or write operations on the port due to the read-modifywrite sequence of all such operations.

### 4.2.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-4. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RABPU bit of the OPTION register. A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an I/O. There is no software control of the MCLR pull-up.

### 4.2.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCAx enable or disable the interrupt function for each pin. Refer to Register 4-6. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (RABIF) in the INTCON register (Register 2-6).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTA. This will end the mismatch condition, then,

- b) Clear the flag bit RABIF.

A mismatch condition will continue to set flag bit RABIF. Reading PORTA will end the mismatch condition and allow flag bit RABIF to be cleared. The latch holding the last read value is not affected by a MCLR nor BOR Reset. After these Resets, the RABIF flag will continue to be set if a mismatch is present.

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set.

| U-0                | U-0                                             | R/W-1              | R/W-1        | U-0              | R/W-1            | R/W-1           | R/W-1 |

|--------------------|-------------------------------------------------|--------------------|--------------|------------------|------------------|-----------------|-------|

| _                  | _                                               | WPUA5              | WPUA4        |                  | WPUA2            | WPUA1           | WPUA0 |

| bit 7              |                                                 |                    |              |                  |                  |                 | bit 0 |

|                    |                                                 |                    |              |                  |                  |                 |       |

| Legend:            |                                                 |                    |              |                  |                  |                 |       |

| R = Read           | able bit                                        | W = Writable       | bit          | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value         | e at POR                                        | '1' = Bit is set   |              | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

| bit 7-6<br>bit 5-4 | -                                               | nented: Read as '( |              |                  |                  |                 |       |

| DIL 5-4            | 1 = Pull-up<br>0 = Pull-up                      |                    | Register bit |                  |                  |                 |       |

| bit 3              | Unimplem                                        | nented: Read as 'o | )'           |                  |                  |                 |       |

| bit 2-0            | <b>WPUA&lt;2:</b><br>1 = Pull-up<br>0 = Pull-up |                    | Register bit |                  |                  |                 |       |

| Note 1:<br>2:      |                                                 | bit of the OPTION  | •            |                  |                  |                 | bled. |

#### WPUA: PORTA REGISTER **REGISTER 4-5:**

3: The RA3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### **REGISTER 4-6: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER**

| Logondi |     |       |       |       |       |       |       |

|---------|-----|-------|-------|-------|-------|-------|-------|

|         |     |       |       |       |       |       |       |

| bit 7   |     |       |       |       |       |       | bit 0 |

| _       | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|         |     |       |       |       |       |       |       |

| Legena.           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

| TABLE 4-1: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|------------|--------------------------------------------|

|------------|--------------------------------------------|

| Name       | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|---------|---------|---------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0     | ADFM   | VCFG   | CHS3    | CHS2    | CHS1    | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ANSEL      | ANS7   | ANS6   | ANS5    | ANS4    | ANS3    | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| CM1CON0    | C1ON   | C1OUT  | C1OE    | C1POL   | _       | C1R    | C1CH1   | C1CH0  | 0000 -000            | 0000 -000                       |

| INTCON     | GIE    | PEIE   | T0IE    | INTE    | RABIE   | T0IF   | INTF    | RABIF  | 0000 000x            | 0000 000x                       |

| IOCA       | _      | _      | IOCA5   | IOCA4   | IOCA3   | IOCA2  | IOCA1   | IOCA0  | 00 0000              | 00 0000                         |

| OPTION_REG | RABPU  | INTEDG | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0    | 1111 1111            | 1111 1111                       |

| PORTA      | _      | _      | RA5     | RA4     | RA3     | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| SSPCON     | WCOL   | SSPOV  | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1   | SSPM0  | 0000 0000            | 0000 0000                       |

| T1CON      | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS  | TMR10N | 0000 0000            | uuuu uuuu                       |

| TRISA      |        | _      | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| WPUA       | _      | —      | WPUA5   | WPUA4   | —       | WPUA2  | WPUA1   | WPUA0  | 11 -111              | 11 -111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

| U-0          | R/W-0                        | R/W-0            | R/W-0          | R/W-0             | R/W-0  | R/W-0           | R/W-0   |

|--------------|------------------------------|------------------|----------------|-------------------|--------|-----------------|---------|

| —            | TOUTPS3                      | TOUTPS2          | TOUTPS1        | TOUTPS0           | TMR2ON | T2CKPS1         | T2CKPS0 |

| oit 7        |                              |                  |                |                   |        |                 | bit     |

|              |                              |                  |                |                   |        |                 |         |

| egend:       |                              |                  |                |                   |        |                 |         |

| R = Readable | e bit                        | W = Writable     | oit            | U = Unimplen      |        | id as '0'       |         |

| n = Value at | POR                          | '1' = Bit is set |                | '0' = Bit is clea | ared   | x = Bit is unkr | nown    |

| oit 7        | Unimplemen                   | ted: Read as '   | ז'             |                   |        |                 |         |

| oit 6-3      | -                            | >: Timer2 Outp   |                | Select hits       |        |                 |         |

|              | 0000 =1:1 Pc                 | •                |                |                   |        |                 |         |

|              | 0000 =1:1 PC                 |                  |                |                   |        |                 |         |

|              | 0010 =1:2 PC                 |                  |                |                   |        |                 |         |

|              | 0010 =1:0 Pc                 |                  |                |                   |        |                 |         |

|              | 0100 =1:5 Pc                 |                  |                |                   |        |                 |         |

|              | 0101 <b>=1:6 Pc</b>          |                  |                |                   |        |                 |         |

|              | 0110 <b>=1:7 Pc</b>          | ostscaler        |                |                   |        |                 |         |

|              | 0111 <b>=1:8 Pc</b>          | ostscaler        |                |                   |        |                 |         |

|              | 1000 <b>=1:9 Pc</b>          | ostscaler        |                |                   |        |                 |         |

|              | 1001 =1:10 F                 |                  |                |                   |        |                 |         |

|              | 1010 <b>=1:11 P</b>          |                  |                |                   |        |                 |         |

|              | 1011 <b>=1:12</b> F          |                  |                |                   |        |                 |         |

|              | 1100 =1:13 F                 |                  |                |                   |        |                 |         |

|              | 1101 =1:14 F                 |                  |                |                   |        |                 |         |

|              | 1110 =1:15 P<br>1111 =1:16 P |                  |                |                   |        |                 |         |

| oit 2        | TMR2ON: Tir                  |                  |                |                   |        |                 |         |

|              | 1 = Timer2 is                | son              |                |                   |        |                 |         |

|              | 0 = Timer2 is                | off              |                |                   |        |                 |         |

| oit 1-0      | T2CKPS<1:0                   | >: Timer2 Cloc   | k Prescale Sel | lect bits         |        |                 |         |

|              | 00 =Prescale                 | ris 1            |                |                   |        |                 |         |

|              | 01 =Prescale                 | r is 4           |                |                   |        |                 |         |

|              | 1x =Prescale                 | r is 16          |                |                   |        |                 |         |

| lote 1: PI   | IC16F685/PIC16               | E600 only        |                |                   |        |                 |         |

#### T2CON: TIMER 2 CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-1:**

# TABLE 7-1: SUMMARY OF ASSOCIATED TIMER2<sup>(1)</sup> REGISTERS

| Name    | Bit 7     | Bit 6                                        | Bit 5          | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0        | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------|----------------------------------------------|----------------|---------|---------|--------|---------|--------------|----------------------|---------------------------------|

| INTCON  | GIE       | PEIE                                         | TOIE           | INTE    | RABIE   | T0IF   | INTF    | RABIF        | 0000 000x            | 0000 000x                       |

| PIE1    | _         | ADIE                                         | RCIE           | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE       | -000 0000            | -000 0000                       |

| PIR1    | _         | ADIF                                         | RCIF           | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF       | -000 0000            | -000 0000                       |

| PR2     | Timer2 M  | lodule Period                                | Register       |         |         |        |         |              | 1111 1111            | 1111 1111                       |

| TMR2    | Holding F | Holding Register for the 8-bit TMR2 Register |                |         |         |        |         |              | 0000 0000            | 0000 0000                       |

| T2CON   | —         | TOUTPS3                                      | TOUTPS2        | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0      | -000 0000            | -000 0000                       |

| Lanandi |           |                                              | als are see al |         |         |        |         | ( <b>T</b> 0 |                      |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

Note

1:

PIC16F685/PIC16F690 only.

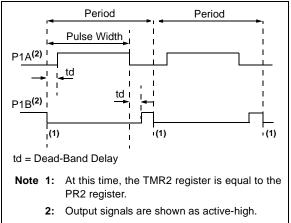

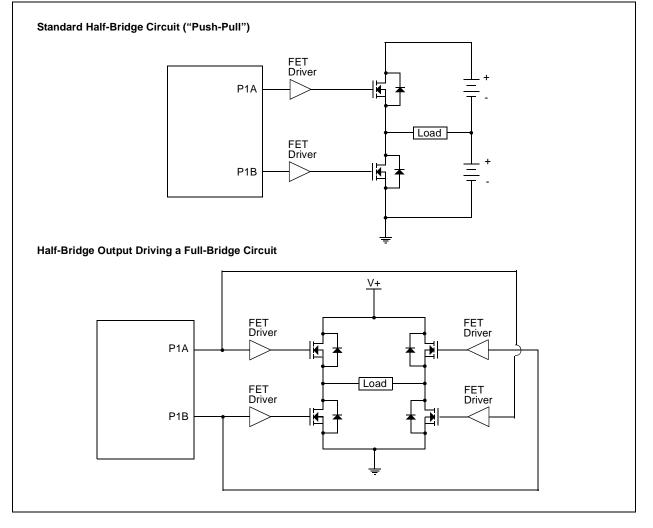

### 11.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 11-6). This mode can be used for Half-Bridge applications, as shown in Figure 11-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 11.4.6 "Programmable Dead-Band Delay mode"** for more details of the dead-band delay operations. Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

### FIGURE 11-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

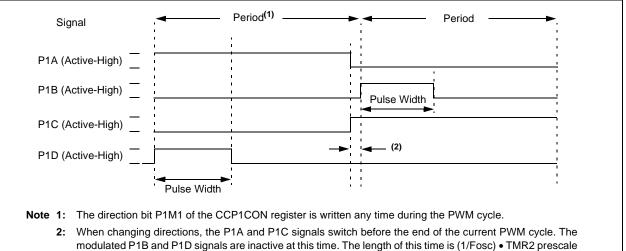

# 11.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 11-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 11-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices QC and QD (see Figure 11-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### FIGURE 11-12: EXAMPLE OF PWM DIRECTION CHANGE

value.

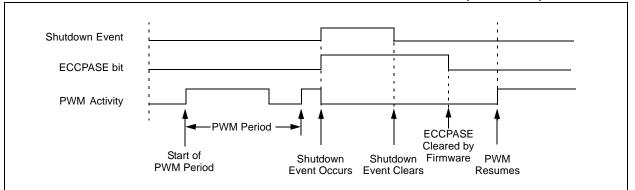

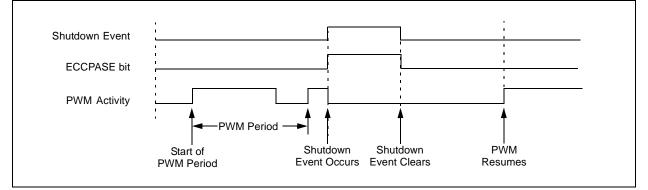

### FIGURE 11-15: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (PRSEN = 0)

#### 11.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 11-16: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

|        |                |            |                             | SYNC = 0          | , BRGH     | = 1, BRG16                  | = 1 or SY          | ′NC = 1, | BRG16 = 1                   | _                |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|----------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc           | : = 20.00  | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |          |                             | Fosc = 8.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual %           |          | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0          | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00     | 9215                        | 300.0            | 0.00       | 6666                        |

| 1200   | 1200           | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00     | 2303                        | 1200             | -0.02      | 1666                        |

| 2400   | 2400           | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00     | 1151                        | 2401             | 0.04       | 832                         |

| 9600   | 9597           | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00     | 287                         | 9615             | 0.16       | 207                         |

| 10417  | 10417          | 0.00       | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16     | 264                         | 10417            | 0          | 191                         |

| 19.2k  | 19.23k         | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00     | 143                         | 19.23k           | 0.16       | 103                         |

| 57.6k  | 57.47k         | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00     | 47                          | 57.14k           | -0.79      | 34                          |

| 115.2k | 116.3k         | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00     | 23                          | 117.6k           | 2.12       | 16                          |

|        |                |            |                             | SYNC = 0          | , BRGH | = 1, BRG16     | = 1 or SΥ        | /NC = 1,                    | BRG16 = 1      |            |                             |     |  |

|--------|----------------|------------|-----------------------------|-------------------|--------|----------------|------------------|-----------------------------|----------------|------------|-----------------------------|-----|--|

| BAUD   | Fos            | c = 4.000  | ) MHz                       | Fosc = 3.6864 MHz |        |                | Fosc = 2.000 MHz |                             |                | Fos        | Fosc = 1.000 MHz            |     |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual % value    |        | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |     |  |

| 300    | 300.0          | 0.01       | 3332                        | 300.0             | 0.00   | 3071           | 299.9            | -0.02                       | 1666           | 300.1      | 0.04                        | 832 |  |

| 1200   | 1200           | 0.04       | 832                         | 1200              | 0.00   | 767            | 1199             | -0.08                       | 416            | 1202       | 0.16                        | 207 |  |

| 2400   | 2398           | 0.08       | 416                         | 2400              | 0.00   | 383            | 2404             | 0.16                        | 207            | 2404       | 0.16                        | 103 |  |

| 9600   | 9615           | 0.16       | 103                         | 9600              | 0.00   | 95             | 9615             | 0.16                        | 51             | 9615       | 0.16                        | 25  |  |

| 10417  | 10417          | 0.00       | 95                          | 10473             | 0.53   | 87             | 10417            | 0.00                        | 47             | 10417      | 0.00                        | 23  |  |

| 19.2k  | 19.23k         | 0.16       | 51                          | 19.20k            | 0.00   | 47             | 19.23k           | 0.16                        | 25             | 19.23k     | 0.16                        | 12  |  |

| 57.6k  | 58.82k         | 2.12       | 16                          | 57.60k            | 0.00   | 15             | 55.56k           | -3.55                       | 8              | —          | _                           | _   |  |

| 115.2k | 111.1k         | -3.55      | 8                           | 115.2k            | 0.00   | 7              | _                | _                           | _              | _          | —                           | —   |  |

## TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

| FIGURE 12-12                                    | : SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                 |

|-------------------------------------------------|-----------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         | bit 0     bit 2     bit 3     bit 4     bit 5     bit 6     bit 7           |

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                             |

| SREN bit                                        | ʻ0'                                                                         |

| RCIF bit<br>(Interrupt) ———<br>Read             |                                                                             |

| RXREG                                           | g diagram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

#### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7                               | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                              | RCIDL      |             | SCKP   | BRG16 | —      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                                 | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | _                                   | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | _                                   | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                            | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                                | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7                                | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                               | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                              | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | TXREG EUSART Transmit Data Register |            |             |        |       |        |        |        |                      | 0000 0000                       |

| TXSTA   | CSRC                                | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

#### 13.12.1 ADDRESSING

Once the SSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the eight bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF of the PIR1 register is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave (Figure 13-8). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address.

The sequence of events for 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address; if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

#### TABLE 13-3: DATA TRANSFER RECEIVED BYTE ACTIONS

|    | ts as Data<br>s Received | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |

|----|--------------------------|--------------------|-----------------------|----------------------------------------|

| BF | SSPOV                    |                    | Fuise                 | if enabled)                            |

| 0  | 0                        | Yes                | Yes                   | Yes                                    |

| 1  | 0                        | No                 | No                    | Yes                                    |

| 1  | 1                        | No                 | No                    | Yes                                    |

| 0  | 1                        | No                 | No                    | Yes                                    |

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

| Register              | Address  | Power-on Reset | MCLR Reset<br>WDT Reset (Continued)<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |

|-----------------------|----------|----------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| TRISB                 | 86h/186h | 1111           | 1111                                                                  | uuuu                                                                                  |

| TRISC                 | 87h/187h | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |

| PIE1                  | 8Ch      | -000 0000      | -000 0000                                                             | -uuu uuuu                                                                             |

| PIE2                  | 8Dh      | 0000           | 0000                                                                  | uuuu uuuu                                                                             |

| PCON                  | 8Eh      | 010x           | 0uuq <sup>1, 5)</sup>                                                 | uuuu                                                                                  |

| OSCCON                | 8Fh      | -110 q000      | -110 q000                                                             | -uuu uuuu                                                                             |

| OSCTUNE               | 90h      | 0 0000         | u uuuu                                                                | u uuuu                                                                                |

| PR2                   | 92h      | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |

| SSPADD                | 93h      | 0000 0000      | 1111 1111                                                             | uuuu uuuu                                                                             |

| SSPMSK <sup>(6)</sup> | 93h      |                | 1111 1111                                                             | uuuu uuuu                                                                             |

| SSPSTAT               | 94h      | 0000 0000      | 1111 1111                                                             | uuuu uuuu                                                                             |

| WPUA                  | 95h      | 11 -111        | 11 -111                                                               | uuuu uuuu                                                                             |

| IOCA                  | 96h      | 00 0000        | 00 0000                                                               | uu uuuu                                                                               |

| WDTCON                | 97h      | 0 1000         | 0 1000                                                                | u uuuu                                                                                |

| TXSTA                 | 98h      | 0000 0010      | 0000 0010                                                             | uuuu uuuu                                                                             |

| SPBRG                 | 99h      | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |

| SPBRGH                | 9Ah      | 0000 0000      | 0000 0000                                                             | սսսս սսսս                                                                             |

| BAUDCTL               | 9Bh      | 01-0 0-00      | 01-0 0-00                                                             | uu-u u-uu                                                                             |

| ADRESL                | 9Eh      | xxxx xxxx      | uuuu uuuu                                                             | սսսս սսսս                                                                             |

| ADCON1                | 9Fh      | -000           | -000                                                                  | -uuu                                                                                  |

| EEDAT                 | 10Ch     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |

| EEADR                 | 10Dh     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |

| EEDATH                | 10Eh     | 00 0000        | 00 0000                                                               | uu uuuu                                                                               |

| EEADRH                | 10Fh     | 0000           | 0000                                                                  | uuuu                                                                                  |

| WPUB                  | 115h     | 1111           | 1111                                                                  | uuuu                                                                                  |

| IOCB                  | 116h     | 0000           | 0000                                                                  | uuuu                                                                                  |

| VRCON                 | 118h     | 0000 0000      | 0000 0000                                                             | սսսս սսսս                                                                             |

| CM1CON0               | 119h     | 0000 -000      | 0000 -000                                                             | uuuu -uuu                                                                             |

| CM2CON0               | 11Ah     | 0000 -000      | 0000 -000                                                             | uuuu -uuu                                                                             |

| CM2CON1               | 11Bh     | 0000           | 0010                                                                  | uuuu                                                                                  |

| ANSEL                 | 11Eh     | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |

| ANSELH                | 11Fh     | 1111           | 1111                                                                  | uuuu                                                                                  |

| EECON1                | 18Ch     | x x000         | u q000                                                                | uuuu                                                                                  |

| EECON2                | 18Dh     |                |                                                                       |                                                                                       |

| PSTRCON               | 19Dh     | 0 0001         | 0 0001                                                                | u uuuu                                                                                |

| SRCON                 | 19EH     | 0000 00        | 0000 00                                                               | uuuu uu                                                                               |

#### TABLE 14-4: INITIALIZATION CONDITION FOR REGISTER (CONTINUED)

$\label{eq:logend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

**5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPM < 3:0 > = 1001.

### TABLE 14-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

### TABLE 17-2: OSCILLATOR PARAMETERS

|              | <b>Operating</b><br>Temperatu | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$  |                    |      |      |      |       |                                                                                                                                                                                 |

|--------------|-------------------------------|--------------------------------------------------------|--------------------|------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym.                          | Characteristic                                         | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                                                                                                                      |

| OS06         | TWARM                         | Internal Oscillator Switch when running <sup>(3)</sup> | —                  |      |      | 2    | Tosc  | Slowest clock                                                                                                                                                                   |

| OS07         | Tsc                           | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | —                  | _    | 21   | -    | ms    | LFINTOSC/64                                                                                                                                                                     |

| OS08         | HFosc                         | Internal Calibrated                                    | ±1%                | 7.92 | 8.0  | 8.08 | MHz   | VDD = 3.5V, 25°C                                                                                                                                                                |

|              |                               | HFINTOSC Frequency <sup>(2)</sup>                      | ±2%                | 7.84 | 8.0  | 8.16 | MHz   | $2.5V \le VDD \le 5.5V$ ,<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                                                                                               |

|              |                               |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz   | $ \begin{array}{l} 2.0V \leq V D D \leq 5.5V, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (Ind.)}, \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (Ext.)} \end{array} $ |

| OS09*        | LFosc                         | Internal Uncalibrated<br>LFINTOSC Frequency            | —                  | 15   | 31   | 45   | kHz   |                                                                                                                                                                                 |

| OS10*        | TIOSC ST                      | HFINTOSC Oscillator                                    | _                  | 5.5  | 12   | 24   | μs    | VDD = 2.0V, -40°C to +85°C                                                                                                                                                      |

|              |                               | Wake-up from Sleep                                     | —                  | 3.5  | 7    | 14   | μs    | VDD = 3.0V, -40°C to +85°C                                                                                                                                                      |

|              |                               | Start-up Time                                          | —                  | 3    | 6    | 11   | μs    | VDD = 5.0V, -40°C to +85°C                                                                                                                                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at 'min' values with an external clock applied to the OSC1 pin. When an external clock input is used, the 'max' cycle time limit is 'DC' (no clock) for all devices.

2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 µF and 0.01 µF values in parallel are recommended.

3: By design.

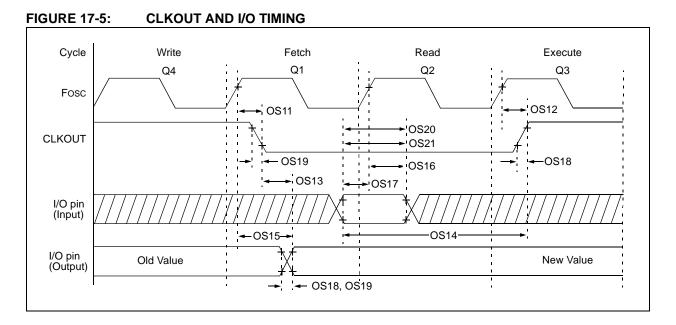

#### TABLE 17-3: CLKOUT AND I/O TIMING PARAMETERS

|              |          | Conditions (unless otherwise stated) re -40°C $\leq$ TA $\leq$ +125°C |               |          |          |       |                          |

|--------------|----------|-----------------------------------------------------------------------|---------------|----------|----------|-------|--------------------------|

| Param<br>No. | Sym.     | Characteristic                                                        | Min.          | Тур†     | Max.     | Units | Conditions               |

| OS11         | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                                       | —             | —        | 70       | ns    | VDD = 5.0V               |

| OS12         | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                                       | _             | _        | 72       | ns    | VDD = 5.0V               |

| OS13         | TckL2IoV | CLKOUT↓ to port out valid <sup>(1)</sup>                              | _             | _        | 20       | ns    |                          |

| OS14         | ТюV2скН  | Port input valid before CLKOUT↑ <sup>(1)</sup>                        | Tosc + 200 ns | _        |          | ns    |                          |

| OS15         | TosH2IoV | Fosc↑ (Q1 cycle) to port out valid                                    | —             | 50       | 70*      | ns    | VDD = 5.0V               |

| OS16         | TosH2iol | Fosc↑ (Q2 cycle) to port input invalid (I/O in hold time)             | 50            |          |          | ns    | VDD = 5.0V               |

| OS17         | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)           | 20            |          | _        | ns    |                          |

| OS18         | TIOR     | Port output rise time <sup>(2)</sup>                                  |               | 15<br>40 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS19         | TIOF     | Port output fall time <sup>(2)</sup>                                  |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS20*        | TINP     | INT pin input high or low time                                        | 25            | —        | _        | ns    |                          |

| OS21*        | Trap     | PORTA interrupt-on-change new input level time                        | Тсү           | —        | _        | ns    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

| Param  | Device<br>Characteristics        | Units | Min. | Тур. |      | Condition |                                                 |  |

|--------|----------------------------------|-------|------|------|------|-----------|-------------------------------------------------|--|

| No.    |                                  |       |      |      | Max. | Vdd       | Note                                            |  |

| D020E  | Power Down Base<br>Current (IPD) | —     |      | 27   | μΑ   | 2.1       | IPD Base: WDT, BOR,                             |  |

|        |                                  | —     |      | 29   |      | 3.0       | Comparators, VREF and                           |  |

|        |                                  | —     |      | 32   |      | 5.0       | T1osc disabled                                  |  |

| D021E  |                                  | —     | _    | 55   | μΑ   | 2.1       | WDT Current                                     |  |

|        |                                  | —     |      | 59   |      | 3.0       |                                                 |  |

|        |                                  | —     |      | 69   |      | 5.0       | ]                                               |  |

| D022E  |                                  | —     | —    | 75   |      | 3.0       | BOD Current                                     |  |

|        |                                  | _     | _    | 147  | μA   | 5.0       | BOR Current                                     |  |

| D023E  |                                  | —     |      | 73   | μA   | 2.1       |                                                 |  |

|        |                                  | —     | —    | 117  |      | 3.0       | Comparator current, both<br>comparators enabled |  |

|        |                                  | _     | _    | 235  |      | 5.0       |                                                 |  |

| D024E  |                                  | —     |      | 102  | μΑ   | 2.1       |                                                 |  |

|        |                                  | —     | _    | 128  |      | 3.0       | CVREF current, high range                       |  |

|        |                                  | —     |      | 170  |      | 5.0       | ]                                               |  |

| D024AE |                                  | —     | _    | 133  | μΑ   | 2.1       | CVREF current, low range                        |  |