# Microchip Technology - PIC16F685T-I/SO Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f685t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr | Name                     | Bit 7        | Bit 6               | Bit 5                     | Bit 4               | Bit 3                | Bit 2                 | Bit 1                 | Bit 0                | Value on<br>POR, BOR | Page    |

|------|--------------------------|--------------|---------------------|---------------------------|---------------------|----------------------|-----------------------|-----------------------|----------------------|----------------------|---------|

| Bank | 1                        |              |                     |                           |                     |                      |                       |                       |                      |                      |         |

| 80h  | INDF                     | Addressing   | this location       | n uses conte              | ents of FSR         | to address c         | ata memory            | (not a physic         | cal register)        | xxxx xxxx            | 43,200  |

| 81h  | OPTION_REG               | RABPU        | INTEDG              | TOCS                      | T0SE                | PSA                  | PS2                   | PS1                   | PS0                  | 1111 1111            | 36,200  |

| 82h  | PCL                      | Program Co   | ounter's (PC        | c) Least Sig              | nificant Byte       | 9                    |                       |                       |                      | 0000 0000            | 43,200  |

| 83h  | STATUS                   | IRP          | RP1                 | RP0                       | TO                  | PD                   | Z                     | DC                    | С                    | 0001 1xxx            | 35,200  |

| 84h  | FSR                      | Indirect Dat | a Memory A          | Address Poi               | nter                |                      |                       |                       |                      | xxxx xxxx            | 43,200  |

| 85h  | TRISA                    | _            | _                   | TRISA5                    | TRISA4              | TRISA3               | TRISA2                | TRISA1                | TRISA0               | 11 1111              | 57,200  |

| 86h  | TRISB                    | TRISB7       | TRISB6              | TRISB5                    | TRISB4              | _                    | _                     | _                     | _                    | 1111                 | 68,201  |

| 87h  | TRISC                    | TRISC7       | TRISC6              | TRISC5                    | TRISC4              | TRISC3               | TRISC2                | TRISC1                | TRISC0               | 1111 1111            | 74,200  |

| 88h  | _                        | Unimpleme    | nted                |                           |                     |                      |                       |                       |                      | —                    | —       |

| 89h  | _                        | Unimpleme    | nted                |                           |                     |                      |                       |                       |                      | _                    | _       |

| 8Ah  | PCLATH                   | —            | _                   | _                         | Write Buffe         | er for the upp       | per 5 bits of t       | he Program            | Counter              | 0 0000               | 43,200  |

| 8Bh  | INTCON                   | GIE          | PEIE                | TOIE                      | INTE                | RABIE                | T0IF                  | INTF                  | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |

| 8Ch  | PIE1                     |              | ADIE <sup>(4)</sup> | RCIE <sup>(2)</sup>       | TXIE <sup>(2)</sup> | SSPIE <sup>(5)</sup> | CCP1IE <sup>(3)</sup> | TMR2IE <sup>(3)</sup> | TMR1IE               | -000 0000            | 38,201  |

| 8Dh  | PIE2                     | OSFIE        | C2IE                | C1IE                      | EEIE                | —                    | _                     | _                     | _                    | 0000                 | 39,201  |

| 8Eh  | PCON                     | _            |                     | ULPWUE                    | SBOREN              | —                    | _                     | POR                   | BOR                  | 01qq                 | 42,201  |

| 8Fh  | OSCCON                   | _            | IRCF2               | IRCF1                     | IRCF0               | OSTS                 | HTS                   | LTS                   | SCS                  | -110 q000            | 46,201  |

| 90h  | OSCTUNE                  | _            | —                   | —                         | TUN4                | TUN3                 | TUN2                  | TUN1                  | TUN0                 | 0 0000               | 50,201  |

| 91h  | _                        | Unimpleme    | nted                |                           |                     |                      |                       |                       |                      | _                    | _       |

| 92h  | PR2 <sup>(3)</sup>       | Timer2 Peri  | iod Register        |                           |                     |                      |                       |                       |                      | 1111 1111            | 89,201  |

| 93h  | SSPADD <sup>(5, 7)</sup> | Synchronou   | us Serial Po        | rt (I <sup>2</sup> C mode | e) Address I        | Register             |                       |                       |                      | 0000 0000            | 184,201 |

| 93h  | SSPMSK <sup>(5,7)</sup>  | MSK7         | MSK6                | MSK5                      | MSK4                | MSK3                 | MSK2                  | MSK1                  | MSK0                 | 1111 1111            | 187,201 |

| 94h  | SSPSTAT <sup>(5)</sup>   | SMP          | CKE                 | D/A                       | Р                   | S                    | R/W                   | UA                    | BF                   | 0000 0000            | 176,201 |

| 95h  | WPUA <sup>(6)</sup>      | _            |                     | WPUA5                     | WPUA4               | _                    | WPUA2                 | WPUA1                 | WPUA0                | 11 -111              | 60,201  |

| 96h  | IOCA                     | _            | _                   | IOCA5                     | IOCA4               | IOCA3                | IOCA2                 | IOCA1                 | IOCA0                | 00 0000              | 60,201  |

| 97h  | WDTCON                   | _            |                     |                           | WDTPS3              | WDTPS2               | WDTPS1                | WDTPS0                | SWDTEN               | 0 1000               | 208,201 |

| 98h  | TXSTA <sup>(2)</sup>     | CSRC         | TX9                 | TXEN                      | SYNC                | SENDB                | BRGH                  | TRMT                  | TX9D                 | 0000 0010            | 157,201 |

| 99h  | SPBRG <sup>(2)</sup>     | BRG7         | BRG6                | BRG5                      | BRG4                | BRG3                 | BRG2                  | BRG1                  | BRG0                 | 0000 0000            | 160,201 |

| 9Ah  | SPBRGH <sup>(2)</sup>    | BRG15        | BRG14               | BRG13                     | BRG12               | BRG11                | BRG10                 | BRG9                  | BRG8                 | 0000 0000            | 160,201 |

| 9Bh  | BAUDCTL <sup>(2)</sup>   | ABDOVF       | RCIDL               | —                         | SCKP                | BRG16                | —                     | WUE                   | ABDEN                | 01-0 0-00            | 159,201 |

| 9Ch  | _                        | Unimpleme    | nted                |                           | I                   | 1                    |                       |                       |                      | _                    | _       |

| 9Dh  | _                        | Unimpleme    |                     |                           |                     |                      |                       |                       |                      | _                    | _       |

| 9Eh  | ADRESL <sup>(4)</sup>    |              | Register Lo         | w Byte                    |                     |                      |                       |                       |                      | xxxx xxxx            | 113,201 |

| 9Fh  | ADCON1 <sup>(4)</sup>    | _            | ADCS2               | ADCS1                     | ADCS0               | —                    | _                     | _                     | _                    | -000                 | 112,201 |

#### TABLE 2-2: PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented Note 1: MCLR and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the mismatch exists.

**2:** PIC16F687/PIC16F689/PIC16F690 only.

EIGENERS//PIC16F689/PIC1

BIC16F685/PIC16F690 only.

PIC16F677/PIC16F697 (PIC16F697 (PIC16F697

4: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

6: RA3 pull-up is enabled when pin is configured as MCLR in Configuration Word.

7: Accessible only when SSPCON register bits SSPM<3:0> = 1001.

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0               | R/W-0               | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIE <sup>(5)</sup> | RCIE <sup>(3)</sup> | TXIE <sup>(3)</sup> | SSPIE <sup>(4)</sup> | CCP1IE <sup>(2)</sup> | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:          |             |                                                    |                                        |                    |

|------------------|-------------|----------------------------------------------------|----------------------------------------|--------------------|

| R = Readable bit |             | W = Writable bit                                   | U = Unimplemented bit,                 | read as '0'        |

| -n = Value       | at POR      | '1' = Bit is set                                   | '0' = Bit is cleared                   | x = Bit is unknown |

| L : L <b>7</b>   | 11          |                                                    |                                        |                    |

| bit 7            | -           | mented: Read as '0'                                | . –                                    |                    |

| bit 6            |             | D Converter (ADC) Interrupt                        | t Enable bit                           |                    |

|                  |             | bles the ADC interrupt<br>bles the ADC interrupt   |                                        |                    |

| bit 5            |             | USART Receive Interrupt Er                         | able hit(3)                            |                    |

| Dit J            |             | bles the EUSART receive inter                      |                                        |                    |

|                  |             | bles the EUSART receive int                        |                                        |                    |

| bit 4            |             | JSART Transmit Interrupt Er                        |                                        |                    |

|                  |             | bles the EUSART transmit in                        |                                        |                    |

|                  | 0 = Disa    | bles the EUSART transmit ir                        | nterrupt                               |                    |

| bit 3            | SSPIE: S    | Synchronous Serial Port (SS                        | P) Interrupt Enable bit <sup>(4)</sup> |                    |

|                  |             | bles the SSP interrupt                             |                                        |                    |

|                  |             | bles the SSP interrupt                             |                                        |                    |

| bit 2            |             | CCP1 Interrupt Enable bit <sup>(2</sup>            | )                                      |                    |

|                  |             | bles the CCP1 interrupt<br>bles the CCP1 interrupt |                                        |                    |

| bit 1            |             | : Timer2 to PR2 Match Interr                       | upt Enable bit <sup>(1)</sup>          |                    |

|                  |             | bles the Timer2 to PR2 match                       | •                                      |                    |

|                  |             | bles the Timer2 to PR2 matc                        |                                        |                    |

| bit 0            | TMR1IE:     | : Timer1 Overflow Interrupt E                      | Enable bit                             |                    |

|                  |             | oles the Timer1 overflow inte                      | •                                      |                    |

|                  | 0 = Disa    | bles the Timer1 overflow inte                      | errupt                                 |                    |

| Note 1:          |             | IC16F690 only.                                     |                                        |                    |

| 2:               |             | IC16F689/PIC16F690 only.                           |                                        |                    |

| 3:               | PIC16F687/P | IC16F689/PIC16F690 only.                           |                                        |                    |

4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

### 2.2.2.8 PCON Register

The Power Control (PCON) register (see Register 2-8) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the Ultra Low-Power Wake-up and software enable of the BOR.

### REGISTER 2-8: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1                 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|-----------------------|-----|-----|-------|-------|

| —     | —   | ULPWUE | SBOREN <sup>(1)</sup> | _   | —   | POR   | BOR   |

| bit 7 |     |        |                       |     |     |       | bit 0 |

| Legend:          |                |                                         |                                  |                       |

|------------------|----------------|-----------------------------------------|----------------------------------|-----------------------|

| R = Readable bit |                | W = Writable bit                        | U = Unimplemented bit,           | read as '0'           |

| -n = Value a     | at POR         | '1' = Bit is set                        | '0' = Bit is cleared             | x = Bit is unknown    |

|                  |                |                                         |                                  |                       |

| bit 7-6          | Unimple        | mented: Read as '0'                     |                                  |                       |

| bit 5            | ULPWU          | E: Ultra Low-Power Wake-up              | o Enable bit                     |                       |

|                  | 1 = Ultra      | Low-Power Wake-up enable                | ed                               |                       |

|                  |                | Low-Power Wake-up disable               |                                  |                       |

| bit 4            | SBORE          | I: Software BOR Enable bit <sup>(</sup> | 1)                               |                       |

|                  | 1 <b>= BOR</b> | enabled                                 |                                  |                       |

|                  | 0 = BOR        | disabled                                |                                  |                       |

| bit 3-2          | Unimple        | mented: Read as '0'                     |                                  |                       |

| bit 1            | POR: Po        | wer-on Reset Status bit                 |                                  |                       |

|                  | 1 = No P       | ower-on Reset occurred                  |                                  |                       |

|                  | 0 = A Po       | wer-on Reset occurred (mus              | st be set in software after a Po | wer-on Reset occurs)  |

| bit 0            | BOR: Br        | own-out Reset Status bit                |                                  |                       |

|                  | 1 = No B       | rown-out Reset occurred                 |                                  |                       |

|                  | 0 = A Bro      | own-out Reset occurred (mu              | st be set in software after a Br | own-out Reset occurs) |

**Note 1:** BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{BOR}$ .

## 4.5 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 4-10). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 4-4 shows how to initialize PORTC. Reading the PORTC register (Register 4-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL and ANSELH registers must         |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | be initialized to configure an analog       |  |  |  |  |

|       | channel as a digital input. Pins configured |  |  |  |  |

|       | as analog inputs will read '0'.             |  |  |  |  |

#### EXAMPLE 4-4: INITIALIZING PORTC

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| BCF   | STATUS, RP1 | ;                      |

| CLRF  | PORTC       | ;Init PORTC            |

| BSF   | STATUS, RP1 | ;Bank 2                |

| CLRF  | ANSEL       | ;digital I/O           |

| BSF   | STATUS, RPO | ;Bank 1                |

| BCF   | STATUS, RP1 | i                      |

| MOVLW | 0Ch         | ;Set RC<3:2> as inputs |

| MOVWF | TRISC       | ;and set RC<5:4,1:0>   |

|       |             | ;as outputs            |

| BCF   | STATUS, RPO | ;Bank 0                |

|       |             |                        |

### REGISTER 4-11: PORTC: PORTC REGISTER

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                           |                                    |  |  |

|-------------------|------------------|---------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown                 |  |  |

bit 7-0

**RC<7:0>:** PORTC General Purpose I/O Pin bit 1 = Port pin is > VIH

0 = Port pin is < VIL

### REGISTER 4-12: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  | R/W-1  | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                                                        |                      |                    |  |

|-------------------|--------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | it W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0

TRISC<7:0>: PORTC Tri-State Control bit

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

# 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or  $$\overline{\text{T1G}}$ pin$

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function (PIC16F685/PIC16F690 only)

- Special Event Trigger (with ECCP) (PIC16F685/PIC16F690 only)

- Comparator output synchronization to Timer1

clock

Figure 6-1 is a block diagram of the Timer1 module.

# 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

# 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock<br>Source | T10SCEN | FOSC<br>Mode      | TMR1CS |

|-----------------|---------|-------------------|--------|

| Fosc/4          | х       | xxx               | 0      |

| T1CKI pin       | 0       | xxx               | 1      |

| T1LPOSC         | 1       | LP or<br>INTOSCIO | 1      |

# 8.2 Comparator Control

Each comparator has a separate control and Configuration register: CM1CON0 for Comparator C1 and CM2CON0 for Comparator C2. In addition, Comparator C2 has a second control register, CM2CON1, for controlling the interaction with Timer1 and simultaneous reading of both comparator outputs.

The CM1CON0 and CM2CON0 registers (see Registers 8-1 and 8-2, respectively) contain the control and Status bits for the following:

- Enable

- Input selection

- Reference selection

- Output selection

- Output polarity

### 8.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 8.2.2 COMPARATOR INPUT SELECTION

The CxCH<1:0> bits of the CMxCON0 register direct one of four analog input pins to the comparator inverting input.

| Note: |                                             |              | d C12INx- p   |     |     |  |  |  |  |  |

|-------|---------------------------------------------|--------------|---------------|-----|-----|--|--|--|--|--|

|       | inputs, the appropriate bits must be set in |              |               |     |     |  |  |  |  |  |

|       | the                                         | ANSEL        | register      | and | the |  |  |  |  |  |

|       | corresponding TRIS bits must also be set    |              |               |     |     |  |  |  |  |  |

|       | to dis                                      | able the out | tput drivers. |     |     |  |  |  |  |  |

# 8.2.3 COMPARATOR REFERENCE SELECTION

Setting the CxR bit of the CMxCON0 register directs an internal voltage reference or an analog input pin to the non-inverting input of the comparator. See **Section 8.9 "Comparator SR Latch"** for more information on the Internal Voltage Reference module.

# 8.2.4 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CM2CON1 register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

- Note 1: The CxOE bit overrides the PORT data latch. Setting the CxON has no impact on the port override.

- 2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

### 8.2.5 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 8-1 shows the output state versus input conditions, including polarity control.

| TABLE 8-1: | COMPARATOR OUTPUT          |

|------------|----------------------------|

|            | STATE VS. INPUT CONDITIONS |

| Input Condition   | CxPOL | CxOUT |

|-------------------|-------|-------|

| CxVIN - > CxVIN + | 0     | 0     |

| CxVIN- < CxVIN+   | 0     | 1     |

| CxVIN - > CxVIN + | 1     | 1     |

| CxVIN- < CxVIN+   | 1     | 0     |

## 8.3 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in **Section 17.0 "Electrical Specifications"** for more details.

| R/W-0         | R-0                                                                   | R/W-0                                                                                                        | R/W-0                                    | U-0             | R/W-0            | R/W-0            | R/W-0    |  |  |  |

|---------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------|------------------|------------------|----------|--|--|--|

| C2ON          | C2OUT                                                                 | C2OE                                                                                                         | C2POL                                    | —               | C2R              | C2CH1            | C2CH0    |  |  |  |

| bit 7         |                                                                       |                                                                                                              |                                          |                 |                  |                  | bit 0    |  |  |  |

| Legend:       |                                                                       |                                                                                                              |                                          |                 |                  |                  |          |  |  |  |

| R = Readabl   | e bit                                                                 | W = Writable                                                                                                 | bit                                      | U = Unimple     | emented bit, rea | ad as '0'        |          |  |  |  |

| -n = Value at | POR                                                                   | '1' = Bit is set                                                                                             | t                                        | '0' = Bit is cl | eared            | x = Bit is unk   | nown     |  |  |  |

| bit 7         | C2ON: Com                                                             | parator C2 Ena                                                                                               | ble bit                                  |                 |                  |                  |          |  |  |  |

|               | 1 = Compara                                                           | ator C2 is enabl<br>ator C2 is disab                                                                         | ed                                       |                 |                  |                  |          |  |  |  |

| bit 6         | C2OUT: Com                                                            | nparator C2 Ou                                                                                               | tput bit                                 |                 |                  |                  |          |  |  |  |

|               | C2OUT = 0 v<br>C2OUT = 1 v<br><u>If C2POL = 0</u><br>C2OUT = 1 v      | <u>_ (inverted pola</u><br>when C2VIN+ ><br>when C2VIN+ <<br>(non-inverted<br>when C2VIN+ ><br>when C2VIN+ < | C2VIN-<br>C2VIN-<br>polarity):<br>C2VIN- |                 |                  |                  |          |  |  |  |

| bit 5         | C2OE: Comp                                                            | : Comparator C2 Output Enable bit                                                                            |                                          |                 |                  |                  |          |  |  |  |

|               |                                                                       | s present on C<br>s internal only                                                                            | 20UT pin <sup>(1)</sup>                  |                 |                  |                  |          |  |  |  |

| bit 4         | C1POL: Comparator C1 Output Polarity Select bit                       |                                                                                                              |                                          |                 |                  |                  |          |  |  |  |

|               |                                                                       | ogic is inverted<br>ogic is not inve                                                                         |                                          |                 |                  |                  |          |  |  |  |

| bit 3         | Unimplemer                                                            | nted: Read as '                                                                                              | 0'                                       |                 |                  |                  |          |  |  |  |

| bit 2         | <b>C2R:</b> Comparator C2 Reference Select bits (non-inverting input) |                                                                                                              |                                          |                 |                  |                  |          |  |  |  |

|               |                                                                       | connects to C2<br>connects to C2                                                                             |                                          |                 |                  |                  |          |  |  |  |

| bit 1-0       | C2CH<1:0>: Comparator C2 Channel Select bits                          |                                                                                                              |                                          |                 |                  |                  |          |  |  |  |

|               | 01 = C2VIN-<br>10 = C2VIN-                                            | of C2 connects<br>of C2 connects<br>of C2 connects<br>of C2 connects                                         | to C12IN1- pi<br>to C12IN2- pi           | n<br>n          |                  |                  |          |  |  |  |

|               | TT = CZVIN                                                            | ut requires the f                                                                                            |                                          |                 | 20E = 1, C20I    | N = 1 and corres | sponding |  |  |  |

### REGISTER 8-2: CM2CON0: COMPARATOR C2 CONTROL REGISTER 0

PORT TRIS bit = 0.

#### 10.1.4 READING THE FLASH PROGRAM MEMORY (PIC16F685/PIC16F689/ PIC16F690)

To read a program memory location, the user must write the Least and Most Significant address bits to the EEADR and EEADRH registers, set the EEPGD control bit of the EECON1 register, and then set control bit RD. Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDAT and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDAT and EEDATH registers will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

- If the WR bit is set when EEPGD = 1, it will be immediately reset to '0' and no operation will take place.

### EXAMPLE 10-3: FLASH PROGRAM READ

|                      | BANKSEL | EEADR            |     | ;                                                        |

|----------------------|---------|------------------|-----|----------------------------------------------------------|

|                      | MOVF    | MS_PROG_EE_ADDR, | W   | ;                                                        |

|                      | MOVWF   | EEADRH           |     | ;MS Byte of Program Address to read                      |

|                      | MOVF    | LS_PROG_EE_ADDR, | W   | ;                                                        |

|                      | MOVWF   | EEADR            |     | ;LS Byte of Program Address to read                      |

|                      | BANKSEL | EECON1           | ;   |                                                          |

|                      | BSF     | EECON1, EEPGD    |     | ;Point to PROGRAM memory                                 |

| <del>т</del> 8       | BSF     | EECON1, RD       |     | ;EE Read                                                 |

| Required<br>Sequence | NOP     |                  |     | ;First instruction after BSF EECON1,RD executes normally |

|                      | NOP     |                  |     | ;Any instructions here are ignored as program            |

| <b></b>              |         |                  |     | ;memory is read in second cycle after BSF EECON1,RD      |

| ;                    |         |                  |     |                                                          |

|                      | BANKSEL | EEDAT            | ;   |                                                          |

|                      | MOVF    | EEDAT, W         |     | ;W = LS Byte of Program Memory                           |

|                      | MOVWF   | LOWPMBYTE        |     | ;                                                        |

|                      | MOVF    | EEDATH, W        |     | ;W = MS Byte of Program EEDAT                            |

|                      | MOVWF   | HIGHPMBYTE       |     | ;                                                        |

|                      | BANKSEL | 0x00             | ;Ba | nk 0                                                     |

|                      |         |                  |     |                                                          |

| R/W-0         | R/W-0                                                                                                     | R/W-0                                                                                                                            | R/W-0          | R/W-0            | R-0              | R-0             | R-x   |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|--|--|

| SPEN          | RX9                                                                                                       | SREN                                                                                                                             | CREN           | ADDEN            | FERR             | OERR            | RX9D  |  |  |  |  |  |  |

| bit 7         |                                                                                                           |                                                                                                                                  |                |                  |                  |                 | bit 0 |  |  |  |  |  |  |

| <u> </u>      |                                                                                                           |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

| Legend:       | • •                                                                                                       |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

| R = Readabl   |                                                                                                           | W = Writable                                                                                                                     |                | -                | mented bit, read |                 |       |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                       | '1' = Bit is set                                                                                                                 |                | '0' = Bit is cle | eared            | x = Bit is unkr | IOWN  |  |  |  |  |  |  |

| bit 7         | SPEN: Seria                                                                                               | al Port Enable bi                                                                                                                | t              |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                           | ort enabled (cor<br>ort disabled (hel                                                                                            | •              | T and TX/CK p    | ins as serial po | rt pins)        |       |  |  |  |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit R                                                                                       | eceive Enable b                                                                                                                  | oit            |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                           | 9-bit reception<br>8-bit reception                                                                                               |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 5         | SREN: Sing                                                                                                | le Receive Enab                                                                                                                  | ole bit        |                  |                  |                 |       |  |  |  |  |  |  |

|               | Asynchrono                                                                                                | SREN: Single Receive Enable bit<br>Asynchronous mode:                                                                            |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Don't care                                                                                                | -                                                                                                                                |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Synchronous mode – Master:                                                                                |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Enables single receive                                                                                |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | <ul> <li>0 = Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul> |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Synchronous mode – Slave                                                                                  |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Don't care                                                                                                |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 4         | CREN: Cont                                                                                                | inuous Receive                                                                                                                   | Enable bit     |                  |                  |                 |       |  |  |  |  |  |  |

|               | Asynchronous mode:                                                                                        |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Enables receiver                                                                                      |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 0 = Disables receiver                                                                                     |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Synchronous mode:                                                                                         |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                           | s continuous rec<br>s continuous rec                                                                                             |                | ble bit CREN is  | s cleared (CRE   | N overrides SR  | EN)   |  |  |  |  |  |  |

| bit 3         | ADDEN: Address Detect Enable bit                                                                          |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | Asynchronous mode 9-bit (RX9 = 1):                                                                        |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set            |                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                           | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit                                   |                |                  |                  |                 |       |  |  |  |  |  |  |

|               |                                                                                                           | <u>Asynchronous mode 8-bit (RX9 = 0)</u> :                                                                                       |                |                  |                  |                 |       |  |  |  |  |  |  |

| <b>h</b> # 0  | Don't care                                                                                                | in a Funan hit                                                                                                                   |                |                  |                  |                 |       |  |  |  |  |  |  |

| bit 2         |                                                                                                           | FERR: Framing Error bit <ol> <li>Framing error (can be updated by reading RCREG register and receive next valid byte)</li> </ol> |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Framing<br>0 = No fram                                                                                |                                                                                                                                  | poaled by rea  |                  | register and rec | eive next valid | byle) |  |  |  |  |  |  |

| bit 1         | OERR: Over                                                                                                | rrun Error bit                                                                                                                   |                |                  |                  |                 |       |  |  |  |  |  |  |

|               | 1 = Overrun<br>0 = No over                                                                                | n error (can be c<br>run error                                                                                                   | leared by clea | aring bit CREN   | )                |                 |       |  |  |  |  |  |  |

| bit 0         | RX9D: Ninth                                                                                               | bit of Received                                                                                                                  | Data           |                  |                  |                 |       |  |  |  |  |  |  |

|               | This can be                                                                                               | address/data bit                                                                                                                 | or a parity bi | it and must be o | calculated by u  | ser firmware.   |       |  |  |  |  |  |  |

|               |                                                                                                           |                                                                                                                                  | -              |                  | -                |                 |       |  |  |  |  |  |  |

# REGISTER 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

### 12.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCTL register starts the auto-baud calibration sequence (Figure 12-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 12-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRG register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRG register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 12-6. During ABD, both the SPBRGH and SPBRG registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRG registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 12.3.2 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- During the auto-baud process, the autobaud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRG register pair.

#### TABLE 12-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

|       |      |                   |                  |

**Note:** During the ABD sequence, SPBRG and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

### FIGURE 12-6: AUTOMATIC BAUD RATE CALIBRATION

| BRG Value               | XXXXh         | 0000h |         | 001Ch              |

|-------------------------|---------------|-------|---------|--------------------|

| RX pin                  |               | Start |         | Edge #5<br>top bit |

| BRG Clock               |               | www.  |         |                    |

| ABDEN bit               | Set by User — |       |         | — Auto Cleared     |

| RCIDL                   |               |       |         |                    |

| RCIF bit<br>(Interrupt) |               |       |         |                    |

| Read<br>RCREG           |               |       |         | <u>_</u>           |

| SPBRG                   |               |       | XXh X_  | 1Ch                |

| SPBRGH                  |               |       | XXh XXh | 00h                |

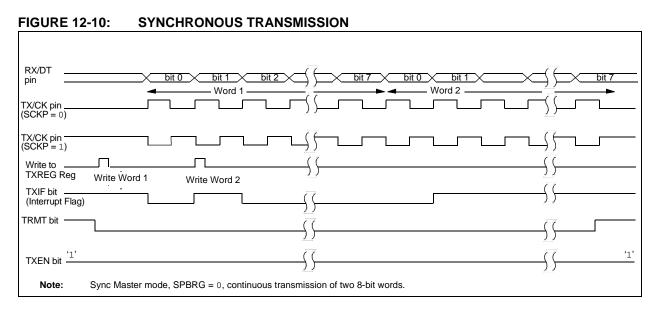

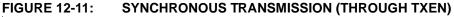

#### TABLE 12-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7    | Bit 6       | Bit 5        | Bit 4       | Bit 3      | Bit 2        | Bit 1      | Bit 0      | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------|-------------|--------------|-------------|------------|--------------|------------|------------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF   | RCIDL       | _            | SCKP        | BRG16      | _            | WUE        | ABDEN      | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE      | PEIE        | TOIE         | INTE        | RABIE      | T0IF         | INTF       | RABIF      | 0000 000x            | 0000 000x                       |

| PIE1    | _        | ADIE        | RCIE         | TXIE        | SSPIE      | CCP1IE       | TMR2IE     | TMR1IE     | -000 0000            | -000 0000                       |

| PIR1    | _        | ADIF        | RCIF         | TXIF        | SSPIF      | CCP1IF       | TMR2IF     | TMR1IF     | -000 0000            | -000 0000                       |

| RCREG   | EUSART F | Receive Da  | ta Register  |             |            |              |            |            | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN     | RX9         | SREN         | CREN        | ADDEN      | FERR         | OERR       | RX9D       | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7     | BRG6        | BRG5         | BRG4        | BRG3       | BRG2         | BRG1       | BRG0       | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15    | BRG14       | BRG13        | BRG12       | BRG11      | BRG10        | BRG9       | BRG8       | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7   | TRISB6      | TRISB5       | TRISB4      |            |              |            |            | 1111                 | 1111                            |

| TXREG   | EUSART   | Fransmit Da | ata Register | r           |            |              |            |            | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC     | TX9         | TXEN         | SYNC        | SENDB      | BRGH         | TRMT       | TX9D       | 0000 0010            | 0000 0010                       |

| Logond: |          |             | nnlomontor   | trand on 'o | , Shadad a | alla ara nat | upod for S | unahranaur | Mactor Trance        | ningion                         |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Transmission.

# 13.11 SSP I<sup>2</sup>C Operation

The SSP module in  $l^2$ C mode, fully implements all slave functions, except general call support, and provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the Standard mode specifications, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RB6/ SCK/SCL pin, which is the clock (SCL), and the RB4/ AN10/SDI/SDA pin, which is the data (SDA).

The SSP module functions are enabled by setting SSP enable bit SSPEN (SSPCON<5>).

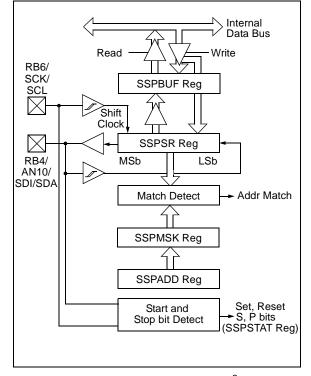

FIGURE 13-7: SSP BLOCK DIAGRAM (I<sup>2</sup>C™ MODE)

The SSP module has six registers for the  $I^2C$  operation, which are listed below.

- SSP Control register (SSPCON)

- SSP Status register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift register (SSPSR) Not directly accessible

- SSP Address register (SSPADD)

- SSP Mask register (SSPMSK)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Slave mode (10-bit address), with Start and Stop bit interrupts enabled to support Firmware Master mode

- I<sup>2</sup>C Start and Stop bit interrupts enabled to support Firmware Master mode; Slave is idle

Selection of any  $I^2C$  mode with the SSPEN bit set forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISB bits. Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the  $I^2C$  module.

## 13.12 Slave Mode

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISB<6,4> are set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge  $(\overline{ACK})$ pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this ACK pulse. They include (either or both):

- a) The Buffer Full bit BF of the SSPSTAT register was set before the transfer was received.

- b) The overflow bit SSPOV of the SSPCON register was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 13-3 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. For high and low times of the  $I^2C$  specification, as well as the requirements of the SSP module, see **Section 17.0 "Electrical Specifications"**.

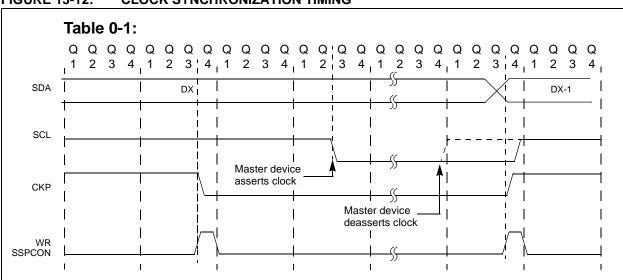

#### FIGURE 13-12: CLOCK SYNCHRONIZATION TIMING

| Addr                  | Name                  | Bit 7              | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------|--------------------|--------------------|-------------|--------------|--------------|--------|--------|--------|----------------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                | GIE                | PEIE               | TOIE        | INTE         | RABIE        | TOIF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| 0Ch                   | PIR1                  | _                  | ADIF               | RCIF        | TXIF         | SSPIF        | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| 13h                   | SSPBUF                | Synchrono          | us Serial Po       | ort Receive | Buffer/Trans | smit Registe | r      |        |        | xxxx xxxx            | uuuu uuuu                       |

| 14h                   | SSPCON                | WCOL               | SSPOV              | SSPEN       | CKP          | SSPM3        | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 86h                   | TRISB                 | TRISB7             | TRISB6             | TRISB5      | TRISB4       | _            | _      | _      | _      | 1111                 | 1111                            |

| 93h                   | SSPMSK <sup>(2)</sup> | MSK7               | MSK6               | MSK5        | MSK4         | MSK3         | MSK2   | MSK1   | MSK0   | 1111 1111            | 1111 1111                       |

| 94h                   | SSPSTAT               | SMP <sup>(3)</sup> | CKE <sup>(3)</sup> | D/A         | Р            | S            | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

| 8Ch                   | PIE1                  | _                  | ADIE               | RCIE        | TXIE         | SSPIE        | CCP1IE | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the SSP module.

Note 1: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

2: SSPMSK register (Register 13-3) can be accessed by reading or writing to SSPADD register with bits SSPM<3:0> = 1001. See Registers 13-2 and 13-3 for more details.

3: Maintain these bits clear.

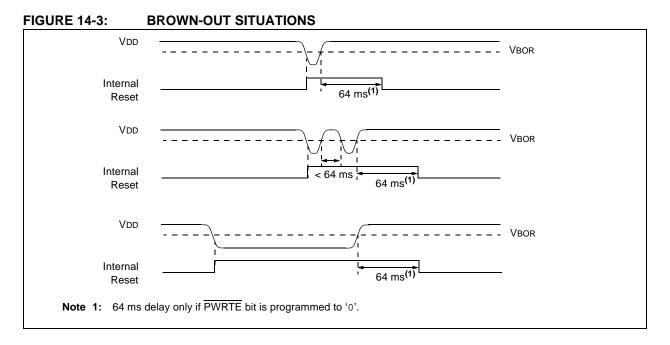

### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

## 17.6 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp5 |                                       | i   |                |  |

|---------|---------------------------------------|-----|----------------|--|

| Т       |                                       |     |                |  |

| F       | Frequency                             | Т   | Time           |  |

| Lowerc  | case letters (pp) and their meanings: |     |                |  |

| рр      |                                       |     |                |  |

| сс      | CCP1                                  | OSC | OSC1           |  |

| ck      | CLKOUT                                | rd  | RD             |  |

| CS      | CS                                    | rw  | RD or WR       |  |

| di      | SDI                                   | SC  | SCK            |  |

| do      | SDO                                   | SS  | SS             |  |

| dt      | Data in                               | tO  | TOCKI          |  |

| io      | I/O Port                              | t1  | T1CKI          |  |

| mc      | MCLR                                  | wr  | WR             |  |

| Upperc  | case letters and their meanings:      |     |                |  |

| S       |                                       |     |                |  |

| F       | Fall                                  | Р   | Period         |  |

| н       | High                                  | R   | Rise           |  |

| I       | Invalid (High-impedance)              | V   | Valid          |  |

| L       | Low                                   | Z   | High-impedance |  |

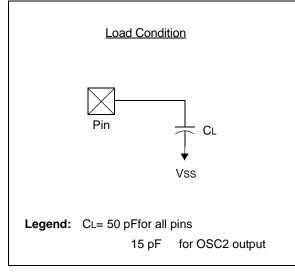

### FIGURE 17-3: LOAD CONDITIONS

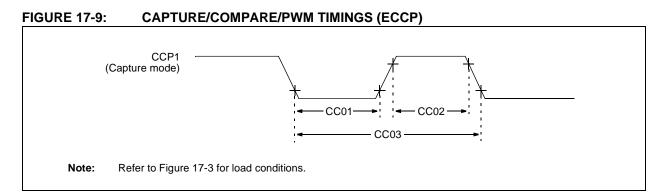

## TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |      |      |       |                                       |  |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------------|--|

| Param<br>No.                                                                                                         | Sym. | Character            | istic          | Min.                  | Тур† | Max. | Units | Conditions                            |  |

| CC01*                                                                                                                | TccL | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                       |  |

|                                                                                                                      |      |                      | With Prescaler | 20                    | —    | —    | ns    |                                       |  |

| CC02*                                                                                                                | ТссН | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                       |  |

|                                                                                                                      |      |                      | With Prescaler | 20                    | _    | —    | ns    |                                       |  |

| CC03*                                                                                                                | TccP | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale<br>value (1, 4 or<br>16) |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 17.8 High Temperature Operation

This section outlines the specifications for the following devices operating in the high temperature range between  $-40^{\circ}$ C and  $150^{\circ}$ C.<sup>(4)</sup>

- PIC16F685

- PIC16F687

- PIC16F689

- PIC16F690

When the value of any parameter is identical for both the 125°C Extended and the 150°C High Temp. temperature ranges, then that value will be found in the standard specification tables shown earlier in this chapter, under the fields listed for the 125°C Extended temperature range. If the value of any parameter is unique to the 150°C High Temp. temperature range, then it will be listed here, in this section of the data sheet.

If a Silicon Errata exists for the product and it lists a modification to the 125°C Extended temperature range value, one that is also shared at the 150°C High Temp. temperature range, then that modified value will apply to both temperature ranges.

- Note 1: Writes are <u>not allowed</u> for Flash program memory above 125°C.

- All AC timing specifications are increased by 30%. This derating factor will include parameters such as TPWRT.

- **3:** The temperature range indicator in the catalog part number and device marking is "H" for -40°C to 150°C.

Example: PIC16F685T-H/SS indicates the device is shipped in a Tape and reel configuration, in the SSOP package, and is rated for operation from -40°C to 150°C.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Endurance of the data EEPROM decreases with increasing temperature. It is recommended that the number of programming cycles to any individual address at temperatures above +125°C not exceed 25,000. Error correction techniques are advised for data requiring more programming cycles above +125°C.

- 6: DS80243 Table 1 refers to various revisions of the PIC16F685, but operation above +125°C will only be available for revision A6 or later.

- 7: The +150°C version of the PIC16F685 will not be offered in PDIP. It will only be offered in SSOP, SOIC, and QFN.

| Parameter                               | Source/Sink | Value | Units |

|-----------------------------------------|-------------|-------|-------|

| Max. Current: VDD                       | Source      | 20    | mA    |

| Max. Current: Vss                       | Sink        | 50    | mA    |

| Max. Current: Pin                       | Source      | 5     | mA    |

| Max. Current: Pin                       | Sink        | 10    | mA    |

| Max. Pin Current: at Voн                | Source      | 3     | mA    |

| Max. Pin Current: at VoL                | Sink        | 8.5   | mA    |

| Max. Port Current: A, B, and C combined | Source      | 20    | mA    |

| Max. Port Current: A, B, and C combined | Sink        | 50    | mA    |

| Max. Junction Temperature               |             | 155   | °C    |

### TABLE 17-17: ABSOLUTE MAXIMUM RATINGS

**Note:** Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

| Param  | Device          | Units | Min. | Тур. |      | Condition |                                                 |  |  |

|--------|-----------------|-------|------|------|------|-----------|-------------------------------------------------|--|--|

| No.    | Characteristics |       |      |      | Max. | Vdd       | Note                                            |  |  |

| D020E  | Power Down Base | —     |      | 27   | μΑ   | 2.1       | IPD Base: WDT, BOR,                             |  |  |

|        | Current (IPD)   | —     |      | 29   |      | 3.0       | Comparators, VREF and                           |  |  |

|        |                 | —     |      | 32   |      | 5.0       | T10sc disabled                                  |  |  |