Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

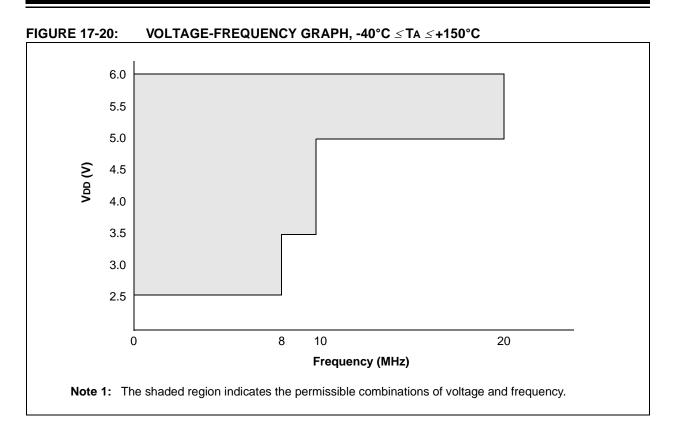

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-e-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PINOUT DESCRIPTION – PIC16F631

| Name                                                              | Function   | Input<br>Type | Output<br>Type | Description                                                                                    |  |

|-------------------------------------------------------------------|------------|---------------|----------------|------------------------------------------------------------------------------------------------|--|

| RA0/C1IN+/ICSPDAT/ULPWU                                           | RA0        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

|                                                                   | C1IN+      | AN            | —              | Comparator C1 non-inverting input.                                                             |  |

|                                                                   | ICSPDAT    | ST            | CMOS           | ICSP™ Data I/O.                                                                                |  |

|                                                                   | ULPWU      | AN            |                | Ultra Low-Power Wake-up input.                                                                 |  |

| RA1/C12IN0-/ICSPCLK                                               | RA1        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

|                                                                   | C12IN0-    | AN            | _              | Comparator C1 or C2 inverting input.                                                           |  |

|                                                                   | ICSPCLK    | ST            | —              | ICSP™ clock.                                                                                   |  |

| RA2/T0CKI/INT/C1OUT                                               | RA2        | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

|                                                                   | T0CKI      | ST            | —              | Timer0 clock input.                                                                            |  |

|                                                                   | INT        | ST            | —              | External interrupt pin.                                                                        |  |

|                                                                   | C10UT      |               | CMOS           | Comparator C1 output.                                                                          |  |

| RA3/MCLR/Vpp                                                      | RA3        | TTL           | —              | General purpose input. Individually controlled interrupt-on-<br>change.                        |  |

|                                                                   | MCLR       | ST            | _              | Master Clear with internal pull-up.                                                            |  |

|                                                                   | VPP        | ΗV            | _              | Programming voltage.                                                                           |  |

| RA4/T1G/OSC2/CLKOUT                                               | RA4        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

|                                                                   | T1G        | ST            | —              | Timer1 gate input.                                                                             |  |

|                                                                   | OSC2       | _             | XTAL           | Crystal/Resonator.                                                                             |  |

|                                                                   | CLKOUT     | _             | CMOS           | Fosc/4 output.                                                                                 |  |

| RA5/T1CKI/OSC1/CLKIN                                              | RA5        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

|                                                                   | T1CKI      | ST            | —              | Timer1 clock input.                                                                            |  |

|                                                                   | OSC1       | XTAL          | _              | Crystal/Resonator.                                                                             |  |

|                                                                   | CLKIN      | ST            | —              | External clock input/RC oscillator connection.                                                 |  |

| RB4                                                               | RB4        | TTL           | CMOS           |                                                                                                |  |

| RB5                                                               | RB5        | TTL           | CMOS           |                                                                                                |  |

| RB6                                                               | RB6        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

| RB7                                                               | RB7        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |  |

| RC0/C2IN+                                                         | RC0        | ST            | CMOS           | General purpose I/O.                                                                           |  |

|                                                                   | C2IN+      | AN            | _              | Comparator C2 non-inverting input.                                                             |  |

| RC1/C12IN1-                                                       | RC1        | ST            | CMOS           | General purpose I/O.                                                                           |  |

|                                                                   | C12IN1-    | AN            | 1 —            | Comparator C1 or C2 inverting input.                                                           |  |

| RC2/C12IN2-                                                       | RC2        | ST            | CMOS           | General purpose I/O.                                                                           |  |

|                                                                   | C12IN2-    | AN            | _              | Comparator C1 or C2 inverting input.                                                           |  |

| RC3/C12IN3-                                                       | RC3        | ST            | CMOS           | General purpose I/O.                                                                           |  |

|                                                                   | C12IN3-    | AN            | —              | Comparator C1 or C2 inverting input.                                                           |  |

| RC4/C2OUT                                                         | RC4        | ST            | CMOS           | General purpose I/O.                                                                           |  |

|                                                                   | C2OUT      | —             | CMOS           | Comparator C2 output.                                                                          |  |

| RC5                                                               | RC5        | ST            | CMOS           | General purpose I/O.                                                                           |  |

| Legend: AN = Analog inpu<br>TTL = TTL compat<br>HV = High Voltage | ible input | ST=           |                | compatible input or output<br>Trigger input with CMOS levels                                   |  |

#### 2.2.2.5 PIE2 Register

The PIE2 register contains the interrupt enable bits, as shown in Register 2-5.

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-5: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| OSFIE | C2IE  | C1IE  | EEIE  | —   | —   | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| Legend:         |                                                                                                                                |                                                                                            |                        |                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Readable    | bit                                                                                                                            | W = Writable bit                                                                           | U = Unimplemented bit, | read as '0'        |

| -n = Value at F | POR                                                                                                                            | '1' = Bit is set                                                                           | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7           | 1 = Enables                                                                                                                    | llator Fail Interrupt Enable b<br>oscillator fail interrupt<br>s oscillator fail interrupt | it                     |                    |

| bit 6           | <b>C2IE:</b> Compa<br>1 = Enables                                                                                              | arator C2 Interrupt Enable b<br>Comparator C2 interrupt<br>Comparator C2 interrupt         | it                     |                    |

| bit 5           | <b>C1IE:</b> Comparator C1 Interrupt Enable bit<br>1 = Enables Comparator C1 interrupt<br>0 = Disables Comparator C1 interrupt |                                                                                            |                        |                    |

| bit 4           | 1 = Enables                                                                                                                    | rite Operation Interrupt Enab<br>write operation interrupt<br>write operation interrupt    | le bit                 |                    |

| bit 3-0         | Unimpleme                                                                                                                      | nted: Read as '0'                                                                          |                        |                    |

| FIGURE 3-6:  | INTERNAL OSCILLATOR SWITCH TIMING                         |

|--------------|-----------------------------------------------------------|

|              |                                                           |

| 3698630.960  | LEINTORC (FROM and WOY disalisad)                         |

| HFINTOSC     |                                                           |

| LFINTOSC     | Otart-sp Time Service System Kunning                      |

| IRCF <2:0>   | $\neq 0$ $\chi$ = 0                                       |

| System Clock |                                                           |

| 9898938C     | LFINTOSC (ERNer FSCM of WOT snakied)                      |

| HFINTOSC     |                                                           |

|              | 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 - 2 -                   |

| LFINTOSC     |                                                           |

| IRCF <2:0>   | $\neq 0$ $\chi = 0$                                       |

| System Clock |                                                           |

|              |                                                           |

| 1.5937030    | NEWYORC<br>LEWYORC turns of univer WEY or FEOM is enabled |

| EFB/FOSC     |                                                           |

| MERTOSC      |                                                           |

| \$\$CF <33\$ | <u>18.0 X 0</u>                                           |

| System Crosk |                                                           |

|              |                                                           |

#### 4.2.4 ULTRA LOW-POWER WAKE-UP

The Ultra Low-Power Wake-up (ULPWU) on RA0 allows a slow falling voltage to generate an interrupt-on-change on RA0 without excess current consumption. The mode is selected by setting the ULPWUE bit of the PCON register. This enables a small current sink, which can be used to discharge a capacitor on RA0.

Follow these steps to use this feature:

- a) Charge the capacitor on RA0 by configuring the RA0 pin to output (= 1).

- b) Configure RA0 as an input.

- c) Enable interrupt-on-change for RA0.

- d) Set the ULPWUE bit of the PCON register to begin the capacitor discharge.

- e) Execute a **SLEEP** instruction.

When the voltage on RA0 drops below VIL, an interrupt will be generated which will cause the device to wakeup and execute the next instruction. If the GIE bit of the INTCON register is set, the device will then call the interrupt vector (0004h). See Section 4.4.2 "Interrupton-change" and Section 14.3.3 "PORTA/PORTB Interrupt" for more information.

This feature provides a low-power technique for periodically waking up the device from Sleep. The time-out is dependent on the discharge time of the RC circuit on RA0. See Example 4-2 for initializing the Ultra Low-Power Wake-up module. A series resistor between RA0 and the external capacitor provides overcurrent protection for the RA0/ AN0/C1IN+/ICSPDAT/ULPWU pin and can allow for software calibration of the time-out (see Figure 4-1). A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The Ultra Low-Power Wake-up peripheral can also be configured as a simple Programmable Low-Voltage Detect or temperature sensor.

Note: For more information, refer to Application Note AN879, "Using the Microchip Ultra Low-Power Wake-up Module" (DS00879).

#### EXAMPLE 4-2: ULTRA LOW-POWER WAKE-UP INITIALIZATION

| BCF   | STATUS, RPO | ;Bank 0             |

|-------|-------------|---------------------|

| BCF   | STATUS, RP1 | ;                   |

| BSF   | porta,0     | ;Set RA0 data latch |

| BSF   | STATUS, RP1 | ;Bank 2             |

| BCF   | ANSEL,0     | ;RAO to digital I/O |

| BSF   | STATUS, RPO | ;Bank 1             |

| BCF   | STATUS, RP1 | ;                   |

| BCF   | TRISA,0     | ;Output high to     |

| CALL  | CapDelay    | ;charge capacitor   |

| BSF   | PCON,ULPWUE | ;Enable ULP Wake-up |

| BSF   | IOCA,0      | ;Select RA0 IOC     |

| BSF   | TRISA,0     | ;RAO to input       |

| MOVLW | B'10001000' | ;Enable interrupt   |

| MOVWF | INTCON      | ;and clear flag     |

| BCF   | STATUS, RPO | ;Bank 0             |

| SLEEP |             | ;Wait for IOC       |

| NOP   |             | ;                   |

|       |             |                     |

#### 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0                 | R/W-0                                 | R/W-0            | R/W-0                  | R/W-0             | R/W-0          | R/W-0            | R/W-0      |

|-----------------------|---------------------------------------|------------------|------------------------|-------------------|----------------|------------------|------------|

| T1GINV <sup>(1)</sup> | ) TMR1GE <sup>(2)</sup>               | T1CKPS1          | T1CKPS0                | T1OSCEN           | T1SYNC         | TMR1CS           | TMR10N     |

| bit 7                 |                                       |                  |                        |                   |                |                  | bit 0      |

|                       |                                       |                  |                        |                   |                |                  |            |

| Legend:               |                                       |                  |                        |                   |                |                  |            |

| R = Readab            |                                       | W = Writable     |                        | U = Unimplen      |                |                  |            |

| -n = Value a          | IT POR                                | '1' = Bit is set |                        | '0' = Bit is clea | ared           | x = Bit is unki  | nown       |

| bit 7                 | T1GINV: Time                          | er1 Gate Invert  | bit(1)                 |                   |                |                  |            |

|                       |                                       |                  |                        | ints when Timer   | 1 gate signal  | is high)         |            |

|                       |                                       |                  |                        | nts when gate is  |                | 0 /              |            |

| bit 6                 | TMR1GE: Tin                           | ner1 Gate Ena    | ble bit <sup>(2)</sup> |                   |                |                  |            |

|                       | If TMR1ON =                           |                  |                        |                   |                |                  |            |

|                       | This bit is igno                      |                  |                        |                   |                |                  |            |

|                       | <u>If TMR1ON =</u><br>1 = Timer1 co   |                  | olled by the Ti        | mer1 Gate fund    | tion           |                  |            |

|                       |                                       | always countir   |                        |                   |                |                  |            |

| bit 5-4               | T1CKPS<1:0                            | >: Timer1 Inpu   | t Clock Presca         | ale Select bits   |                |                  |            |

|                       | 11 = 1:8 Pres                         | cale Value       |                        |                   |                |                  |            |

|                       | 10 = 1:4 Pres                         |                  |                        |                   |                |                  |            |

|                       | 01 = 1:2 Pres<br>00 = 1:1 Pres        |                  |                        |                   |                |                  |            |

| bit 3                 |                                       | P Oscillator En  | able Control b         | it                |                |                  |            |

|                       | If INTOSC wit                         | thout CLKOUT     | oscillator is a        | <u>ctive:</u>     |                |                  |            |

|                       |                                       | tor is enabled   | for Timer1 cloc        | ck                |                |                  |            |

|                       | 0 = LP oscilla<br><u>Else:</u>        | tor is off       |                        |                   |                |                  |            |

|                       | This bit is igno                      | ored             |                        |                   |                |                  |            |

| bit 2                 | 0                                     |                  | lock Input Syr         | hchronization Co  | ontrol bit     |                  |            |

|                       | <u>TMR1CS = 1</u> :                   |                  |                        |                   |                |                  |            |

|                       |                                       | nchronize exte   |                        | ıt                |                |                  |            |

|                       |                                       | ize external clo | ock input              |                   |                |                  |            |

|                       | <u>TMR1CS = 0:</u><br>This bit is ign | ored. Timer1 u   | ses the interna        | al clock          |                |                  |            |

| bit 1                 | 0                                     | ner1 Clock Sou   |                        |                   |                |                  |            |

|                       | 1 = External o                        | KI pin (on the   | rising edge)           |                   |                |                  |            |

|                       | 0 = Internal cl                       |                  |                        |                   |                |                  |            |

| bit 0                 | TMR1ON: Timer1 On bit                 |                  |                        |                   |                |                  |            |

|                       | 1 = Enables T                         |                  |                        |                   |                |                  |            |

|                       | 0 = Stops Tim                         | ner1             |                        |                   |                |                  |            |

|                       | 1GINV bit inverts                     | -                |                        |                   |                |                  |            |

|                       | MR1GE bit must                        |                  |                        | or C2OUT, as s    | elected by the | T1GSS bit of the | ne CM2CON1 |

| r                     | egister, as a Time                    | era gate source  |                        |                   |                |                  |            |

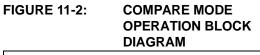

### 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP module may:

- Toggle the CCP1 output

- Set the CCP1 output

- Clear the CCP1 output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCP1M<3:0> control bits of the CCP1CON register.

All Compare modes can generate an interrupt.

Special Event Trigger Will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

- Set the GO/DONE bit to start the ADC conversion.

#### 11.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCP1CON register will force    |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | the CCP1 compare output latch to the        |  |  |  |  |

|       | default low level. This is not the port I/O |  |  |  |  |

|       | data latch.                                 |  |  |  |  |

#### 11.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

#### 11.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP module does not assert control of the CCP1 pin (see the CCP1CON register).

#### 11.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCP1M<3:0> = 1011), the CCP module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCP module does not assert control of the CCP1 pin in this mode (see the CCP1CON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPR1H, CCPR1L register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPR1H and CCPR1L register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

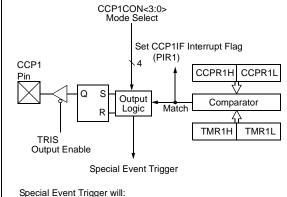

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- **3:** Any pin not used by an Enhanced PWM mode is available for alternate pin functions

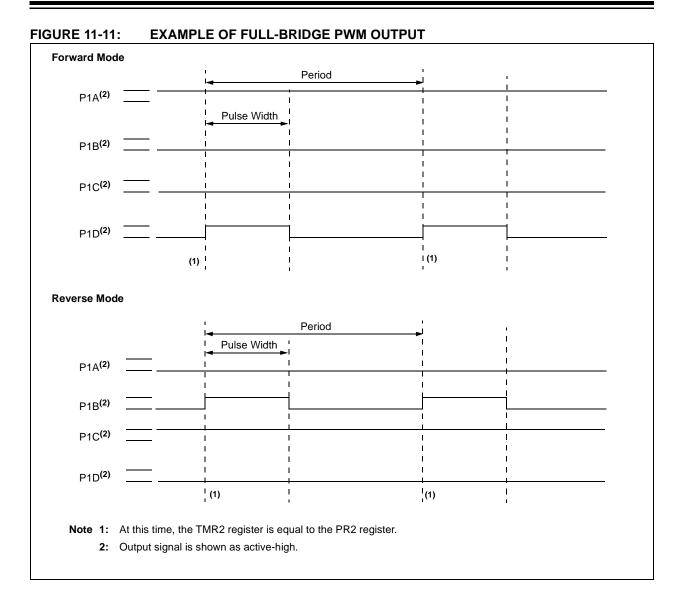

#### TABLE 11-4: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M<1:0> | CCP1/P1A           | P1B                | P1C                | P1D                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

Note 1: Pulse Steering enables outputs in Single mode.

#### 11.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Figure 11-19.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 11.4.4** "**Enhanced PWM Auto-shutdown mode**". An autoshutdown event will only affect pins that have PWM outputs enabled.

#### **REGISTER 11-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0          | U-0                | U-0              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-1 |

|--------------|--------------------|------------------|------------------|------------------|------------------|-----------------|-------|

| _            |                    | _                | STRSYNC          | STRD             | STRC             | STRB            | STRA  |

| bit 7        |                    | ·                |                  |                  |                  |                 | bit ( |

| Legend:      |                    |                  |                  |                  |                  |                 |       |

| R = Readat   | ole bit            | W = Writable     | bit              | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value a | at POR             | '1' = Bit is se  | t                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                    |                  |                  |                  |                  |                 |       |

| bit 7-5      | Unimpleme          | ented: Read as   | '0'              |                  |                  |                 |       |

| bit 4        | STRSYNC:           | Steering Sync I  | pit              |                  |                  |                 |       |

|              | 1 = Output         | steering update  | occurs on next   | PWM period       |                  |                 |       |

|              | 0 = Output         | steering update  | occurs at the be | eginning of the  | instruction cyc  | le boundary     |       |

| bit 3        | STRD: Stee         | ering Enable bit | D                |                  |                  |                 |       |

|              |                    | has the PWM      |                  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1D pir        | n is assigned to | port pin         |                  |                  |                 |       |

| bit 2        | STRC: Stee         | ering Enable bit | С                |                  |                  |                 |       |

|              | 1 = P1C pir        | has the PWM      | waveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1C pir        | n is assigned to | port pin         |                  |                  |                 |       |

| bit 1        | STRB: Stee         | ering Enable bit | В                |                  |                  |                 |       |

|              | 1 <b>= P1B pir</b> | has the PWM      | vaveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1B pir        | is assigned to p | oort pin         |                  |                  |                 |       |

| bit 0        | STRA: Stee         | ering Enable bit | A                |                  |                  |                 |       |

|              | 1 = P1A pir        | has the PWM      | vaveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1A pir        | n is assigned to | port pin         |                  |                  |                 |       |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

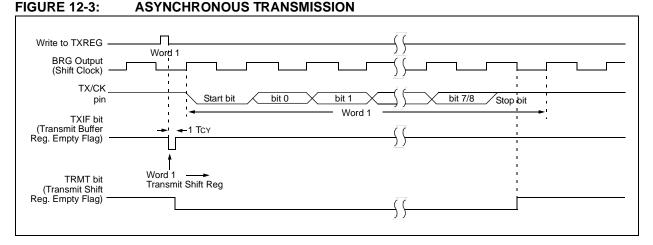

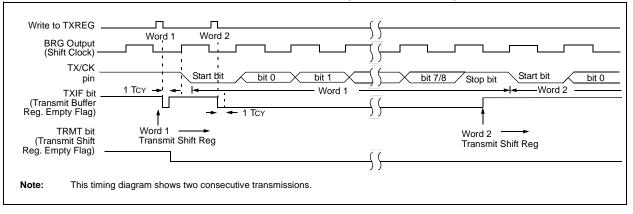

#### 12.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 12.1.1.5 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 12.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 12.1.1.6 Asynchronous Transmission Set-up:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 7. Load 8-bit data into the TXREG register. This will start the transmission.

#### FIGURE 12-4: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### 12.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 12.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 12.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 12.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

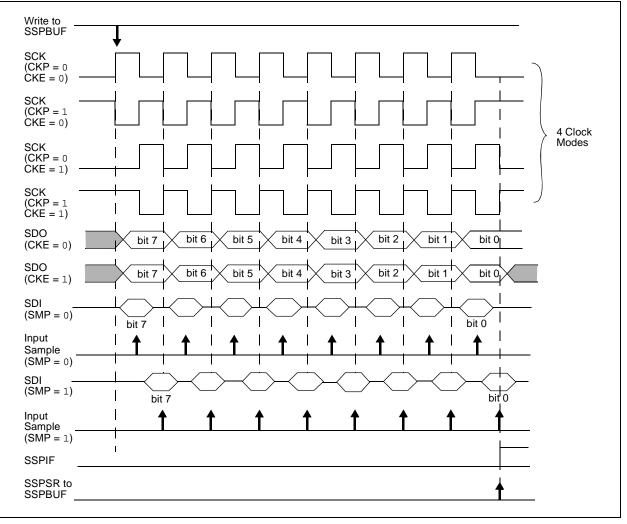

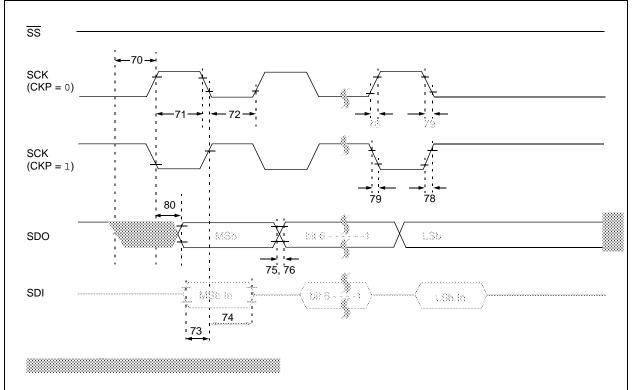

#### 13.5 Master Mode

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 13-2) is to broadcast data by the software protocol.

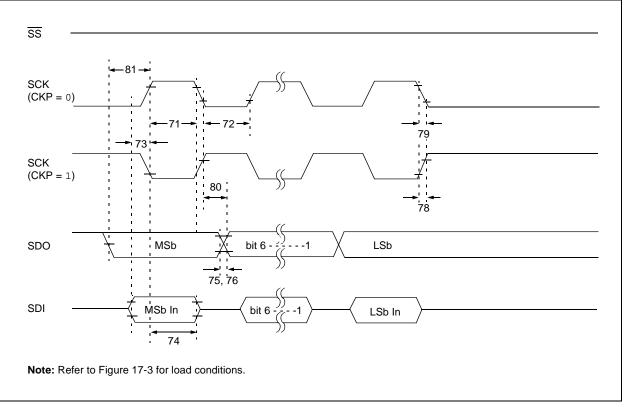

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). This could be useful in receiver applications as a Line Activity Monitor mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. This then, would give waveforms for SPI communication as shown in Figure 13-3, Figure 13-5 and Figure 13-6, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2 (No SSP module, PIC16F690 only)

Figure 13-3 shows the waveforms for Master mode. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 13-3: SPI MODE WAVEFORM (MASTER MODE)

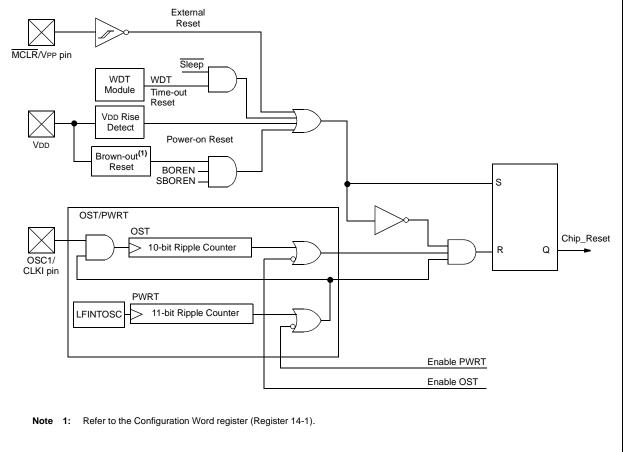

#### 14.2 Reset

The PIC16F631/677/685/687/689/690 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- WDT Reset during Sleep C)

- MCLR Reset during normal operation d)

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

**FIGURE 14-1:**

Brown-out Reset (BOR)

They are not affected by a WDT Wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 14-2. These bits are used in software to determine the nature of the Reset. See Table 14-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 14-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Section 17.0 "Electrical Specifications" for pulse-width specifications.

### External Reset

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 16.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 16.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

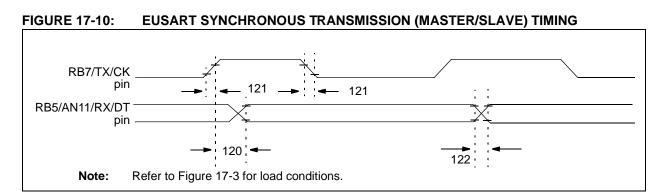

#### TABLE 17-10: EUSART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                       |      |      |       |            |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------|------|------|-------|------------|--|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                                                        | Min. | Max. | Units | Conditions |  |  |

| 120                                                                                                                  | ТскН2ртV | <u>SYNC XMIT (Master &amp; Slave)</u><br>Clock high to data-out valid |      | 40   | ns    |            |  |  |

| 121                                                                                                                  | Tckrf    | Clock out rise time and fall time (Master mode)                       |      | 20   | ns    |            |  |  |

| 122                                                                                                                  | Tdtrf    | Data-out rise time and fall time                                      | _    | 20   | ns    |            |  |  |

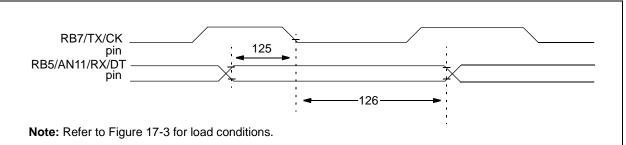

#### FIGURE 17-11: EUSART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 17-11: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                              |      |      |       |            |  |

|----------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------|------|------|-------|------------|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                                                               | Min. | Max. | Units | Conditions |  |

| 125                                                                                                                  | TDTV2CKL | <u>SYNC RCV (Master &amp; Slave)</u><br>Data-hold before CK ↓ (DT hold time) | 10   | _    | ns    |            |  |

| 126                                                                                                                  | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                               | 15   | —    | ns    |            |  |

#### FIGURE 17-12: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

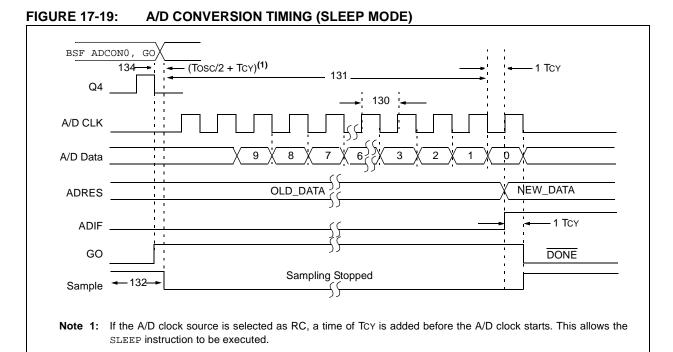

A/D CONVERSION REQUIREMENTS (SLEEP MODE)

| TABLE 1: A/D CONVERSION REQUIREMENTS (SLEEP MODE)                                                                    |      |                                                                       |      |              |      |       |                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------|------|--------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                       |      |              |      |       |                                                                                                                                                                                                                               |

| Param<br>No.                                                                                                         | Sym. | Characteristic                                                        | Min. | Тур†         | Max. | Units | Conditions                                                                                                                                                                                                                    |

| 130*                                                                                                                 | Tad  | A/D Internal RC<br>Oscillator Period                                  | 3.0* | 6.0          | 9.0* | μS    | ADCS<1:0> = 11 (RC mode)<br>At VDD = 2.5V                                                                                                                                                                                     |

|                                                                                                                      |      |                                                                       | 2.0* | 4.0          | 6.0* | μs    | At VDD = 5.0V                                                                                                                                                                                                                 |

| 131                                                                                                                  | Τςνν | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | —    | 11           | _    | TAD   |                                                                                                                                                                                                                               |

| 132*                                                                                                                 | TACQ | Acquisition Time                                                      | (2)  | 11.5         | _    | μS    |                                                                                                                                                                                                                               |

|                                                                                                                      |      |                                                                       | 5*   | _            | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>4.1 mV @ 4.096V) from the last<br>sampled voltage (as stored on<br>CHOLD). |

| 134                                                                                                                  | TGO  | Q4 to A/D Clock<br>Start                                              | _    | Tosc/2 + Tcy |      | _     | If the A/D clock source is selected<br>as RC, a time of TcY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Table 9-1 for minimum conditions.

TABLE 1.

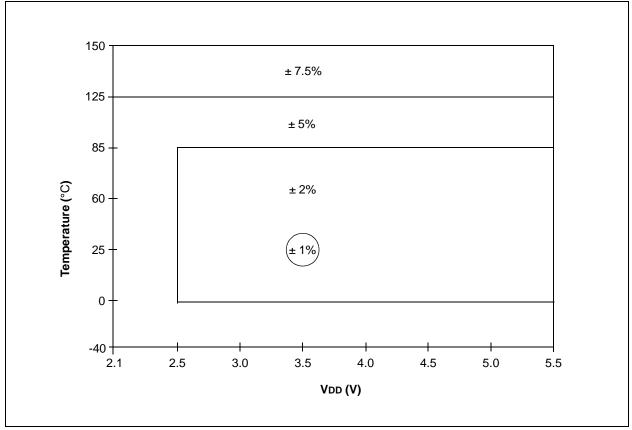

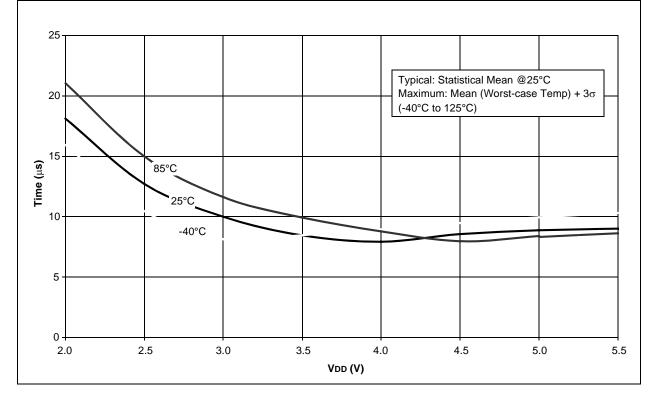

#### FIGURE 17-21: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

© 2005-2015 Microchip Technology Inc.

#### 16 Typical: Statistical Mean @25°C 14 Maximum: Mean (Worst-case Temp) + 3o (-40°C to 125°C) 85°C 12 25°C 10-Time (µs) -40°C 8 6 4 2 0 2.5 3.0 3.5 4.5 5.0 5.5 2.0 4.0 VDD (V)

#### FIGURE 18-36: TYPICAL HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

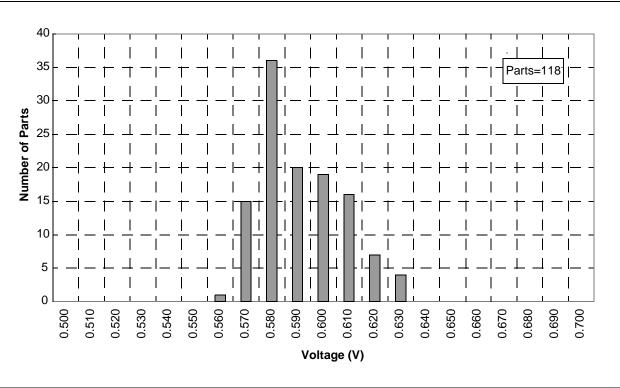

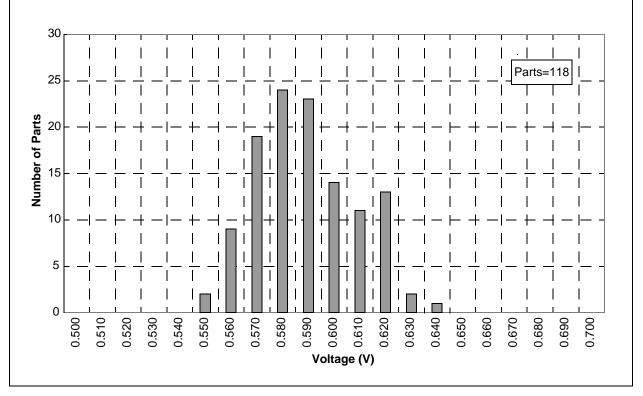

FIGURE 18-48: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (3V, 125°C)