# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 × 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

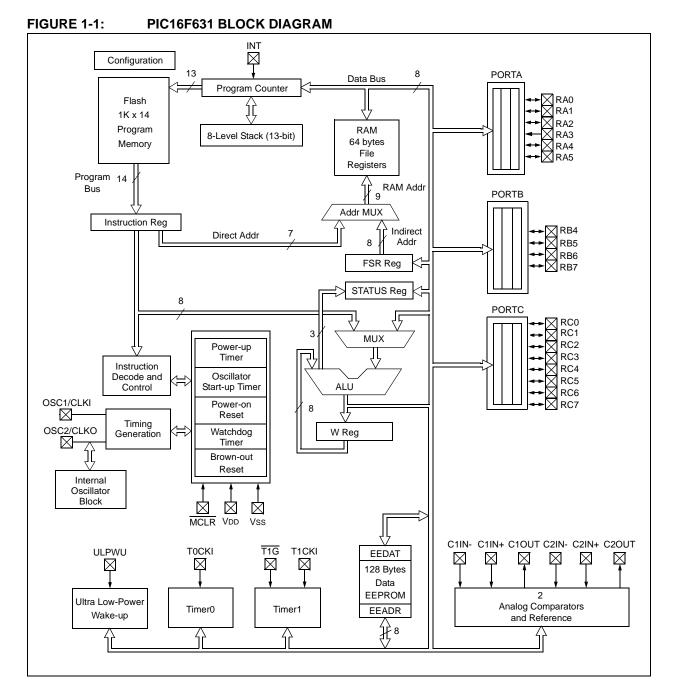

## 1.0 DEVICE OVERVIEW

The PIC16F631/677/685/687/689/690 devices are covered by this data sheet. They are available in 20-pin PDIP, SOIC, TSSOP and QFN packages.

Block Diagrams and pinout descriptions of the devices are as follows:

- PIC16F631 (Figure 1-1, Table 1-1)

- PIC16F677 (Figure 1-2, Table 1-2)

- PIC16F685 (Figure 1-3, Table 1-3)

- PIC16F687/PIC16F689 (Figure 1-4, Table 1-4)

- PIC16F690 (Figure 1-5, Table 1-5)

#### TABLE 1-1: PINOUT DESCRIPTION – PIC16F631

| Name Fund                                                         |            | Input<br>Type | Output<br>Type | Description                                                                                    |

|-------------------------------------------------------------------|------------|---------------|----------------|------------------------------------------------------------------------------------------------|

| RA0/C1IN+/ICSPDAT/ULPWU                                           | RA0        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | C1IN+      | AN            | —              | Comparator C1 non-inverting input.                                                             |

|                                                                   | ICSPDAT    | ST            | CMOS           | ICSP™ Data I/O.                                                                                |

|                                                                   | ULPWU      | AN            |                | Ultra Low-Power Wake-up input.                                                                 |

| RA1/C12IN0-/ICSPCLK                                               | RA1        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | C12IN0-    | AN            | _              | Comparator C1 or C2 inverting input.                                                           |

|                                                                   | ICSPCLK    | ST            | —              | ICSP™ clock.                                                                                   |

| RA2/T0CKI/INT/C1OUT                                               | RA2        | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | T0CKI      | ST            | —              | Timer0 clock input.                                                                            |

|                                                                   | INT        | ST            | —              | External interrupt pin.                                                                        |

|                                                                   | C10UT      |               | CMOS           | Comparator C1 output.                                                                          |

| RA3/MCLR/Vpp                                                      | RA3        | TTL           | —              | General purpose input. Individually controlled interrupt-on-<br>change.                        |

|                                                                   | MCLR       | ST            | _              | Master Clear with internal pull-up.                                                            |

|                                                                   | VPP        | ΗV            | _              | Programming voltage.                                                                           |

| RA4/T1G/OSC2/CLKOUT                                               | RA4        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | T1G        | ST            | —              | Timer1 gate input.                                                                             |

|                                                                   | OSC2       | —             | XTAL           | Crystal/Resonator.                                                                             |

|                                                                   | CLKOUT     | _             | CMOS           | Fosc/4 output.                                                                                 |

| RA5/T1CKI/OSC1/CLKIN                                              | RA5        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | T1CKI      | ST            | —              | Timer1 clock input.                                                                            |

|                                                                   | OSC1       | XTAL          | _              | Crystal/Resonator.                                                                             |

|                                                                   | CLKIN      | ST            | —              | External clock input/RC oscillator connection.                                                 |

| RB4                                                               | RB4        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RB5                                                               | RB5        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RB6                                                               | RB6        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RB7                                                               | RB7        | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RC0/C2IN+                                                         | RC0        | ST            | CMOS           | General purpose I/O.                                                                           |

|                                                                   | C2IN+      | AN            | _              | Comparator C2 non-inverting input.                                                             |

| RC1/C12IN1-                                                       | RC1        | ST            | CMOS           | General purpose I/O.                                                                           |

|                                                                   | C12IN1-    | AN            | 1 —            | Comparator C1 or C2 inverting input.                                                           |

| RC2/C12IN2-                                                       | RC2        | ST            | CMOS           | General purpose I/O.                                                                           |

|                                                                   | C12IN2-    | AN            | _              | Comparator C1 or C2 inverting input.                                                           |

| RC3/C12IN3-                                                       | RC3        | ST            | CMOS           | General purpose I/O.                                                                           |

|                                                                   | C12IN3-    | AN            | —              | Comparator C1 or C2 inverting input.                                                           |

| RC4/C2OUT                                                         | RC4        | ST            | CMOS           | General purpose I/O.                                                                           |

|                                                                   | C2OUT      | —             | CMOS           | Comparator C2 output.                                                                          |

| RC5                                                               | RC5        | ST            | CMOS           | General purpose I/O.                                                                           |

| Legend: AN = Analog inpu<br>TTL = TTL compat<br>HV = High Voltage | ible input | ST=           |                | compatible input or output<br>Trigger input with CMOS levels                                   |

| Addr | Name                     | Bit 7        | Bit 6                                                                                          | Bit 5               | Bit 4               | Bit 3                | Bit 2                 | Bit 1                 | Bit 0                | Value on<br>POR, BOR | Page    |  |  |

|------|--------------------------|--------------|------------------------------------------------------------------------------------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|----------------------|----------------------|---------|--|--|

| Bank | Bank 0                   |              |                                                                                                |                     |                     |                      |                       |                       |                      |                      |         |  |  |

| 00h  | INDF                     | Addressing   | Addressing this location uses contents of FSR to address data memory (not a physical register) |                     |                     |                      |                       |                       |                      |                      |         |  |  |

| 01h  | TMR0                     | Timer0 Mod   | lule Register                                                                                  |                     |                     |                      |                       |                       |                      | xxxx xxxx            | 79,200  |  |  |

| 02h  | PCL                      | Program Co   | ounter's (PC)                                                                                  | Least Signif        | icant Byte          |                      |                       |                       |                      | 0000 0000            | 43,200  |  |  |

| 03h  | STATUS                   | IRP          | RP1                                                                                            | RP0                 | TO                  | PD                   | Z                     | DC                    | С                    | 0001 1xxx            | 35,200  |  |  |

| 04h  | FSR                      | Indirect Dat | a Memory A                                                                                     | ddress Pointe       | ər                  |                      |                       |                       |                      | xxxx xxxx            | 43,200  |  |  |

| 05h  | PORTA <sup>(7)</sup>     | _            | _                                                                                              | RA5                 | RA4                 | RA3                  | RA2                   | RA1                   | RA0                  | xx xxxx              | 57,200  |  |  |

| 06h  | PORTB <sup>(7)</sup>     | RB7          | RB6                                                                                            | RB5                 | RB4                 | _                    | _                     | _                     | _                    | xxxx                 | 67,200  |  |  |

| 07h  | PORTC <sup>(7)</sup>     | RC7          | RC6                                                                                            | RC5                 | RC4                 | RC3                  | RC2                   | RC1                   | RC0                  | xxxx xxxx            | 74,200  |  |  |

| 08h  | —                        | Unimpleme    | nted                                                                                           |                     |                     |                      |                       |                       |                      | —                    | —       |  |  |

| 09h  | —                        | Unimpleme    | nted                                                                                           |                     |                     |                      |                       |                       |                      | —                    | —       |  |  |

| 0Ah  | PCLATH                   |              | _                                                                                              |                     | Write Buffer        | for upper 5 l        | oits of Progra        | am Counter            |                      | 0 0000               | 43,200  |  |  |

| 0Bh  | INTCON                   | GIE          | PEIE                                                                                           | TOIE                | INTE                | RABIE                | TOIF                  | INTF                  | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |  |  |

| 0Ch  | PIR1                     | _            | ADIF <sup>(4)</sup>                                                                            | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF <sup>(5)</sup> | CCP1IF <sup>(3)</sup> | TMR2IF <sup>(3)</sup> | TMR1IF               | -000 0000            | 40,200  |  |  |

| 0Dh  | PIR2                     | OSFIF        | OSFIF C2IF C1IF EEIF — — — —                                                                   |                     |                     |                      |                       |                       |                      |                      | 41,200  |  |  |

| 0Eh  | TMR1L                    | Holding Re   | gister for the                                                                                 | Least Signifi       | cant Byte of        | the 16-bit TM        | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |  |  |

| 0Fh  | TMR1H                    | Holding Re   | gister for the                                                                                 | Most Signific       | cant Byte of t      | he 16-bit TM         | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |  |  |

| 10h  | T1CON                    | T1GINV       | TMR1GE                                                                                         | T1CKPS1             | T1CKPS0             | T1OSCEN              | T1SYNC                | TMR1CS                | TMR10N               | 0000 0000            | 87,200  |  |  |

| 11h  | TMR2 <sup>(3)</sup>      | Timer2 Mod   | ule Register                                                                                   |                     |                     |                      |                       |                       |                      | 0000 0000            | 89,200  |  |  |

| 12h  | T2CON <sup>(3)</sup>     | -            | TOUTPS3                                                                                        | TOUTPS2             | TOUTPS1             | TOUTPS0              | TMR2ON                | T2CKPS1               | T2CKPS0              | -000 0000            | 90,200  |  |  |

| 13h  | SSPBUF <sup>(5)</sup>    | Synchronou   | us Serial Port                                                                                 | Receive But         | ffer/Transmit       | Register             |                       |                       |                      | xxxx xxxx            | 178,200 |  |  |

| 14h  | SSPCON <sup>(5, 6)</sup> | WCOL         | SSPOV                                                                                          | SSPEN               | CKP                 | SSPM3                | SSPM2                 | SSPM1                 | SSPM0                | 0000 0000            | 177,200 |  |  |

| 15h  | CCPR1L <sup>(3)</sup>    | Capture/Co   | mpare/PWM                                                                                      | Register 1 (I       | LSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |  |  |

| 16h  | CCPR1H <sup>(3)</sup>    | Capture/Co   | mpare/PWM                                                                                      | Register 1 (I       | MSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |  |  |

| 17h  | CCP1CON <sup>(3)</sup>   | P1M1         | P1M0                                                                                           | DC1B1               | DC1B0               | CCP1M3               | CCP1M2                | CCP1M1                | CCP1M0               | 0000 0000            | 125,200 |  |  |

| 18h  | RCSTA <sup>(2)</sup>     | SPEN         | RX9                                                                                            | SREN                | CREN                | ADDEN                | FERR                  | OERR                  | RX9D                 | 0000 000x            | 158,200 |  |  |

| 19h  | TXREG <sup>(2)</sup>     | EUSART T     | ransmit Data                                                                                   | Register            |                     |                      |                       |                       |                      | 0000 0000            | 150     |  |  |

| 1Ah  | RCREG <sup>(2)</sup>     | EUSART R     | eceive Data                                                                                    | Register            |                     |                      |                       |                       |                      | 0000 0000            | 155     |  |  |

| 1Bh  | _                        | Unimpleme    | nted                                                                                           |                     |                     |                      |                       |                       |                      | _                    | _       |  |  |

| 1Ch  | PWM1CON <sup>(3)</sup>   | PRSEN        | PDC6                                                                                           | PDC5                | PDC4                | PDC3                 | PDC2                  | PDC1                  | PDC0                 | 0000 0000            | 143,200 |  |  |

| 1Dh  | ECCPAS <sup>(3)</sup>    | ECCPASE      | ECCPAS2                                                                                        | ECCPAS1             | ECCPAS0             | PSSAC1               | PSSAC0                | PSSBD1                | PSSBD0               | 0000 0000            | 140,200 |  |  |

| 1Eh  | ADRESH <sup>(4)</sup>    | A/D Result   | Register Hig                                                                                   | h Byte              |                     |                      |                       |                       |                      | xxxx xxxx            | 113,200 |  |  |

| 1Fh  | ADCON0 <sup>(4)</sup>    | ADFM         | VCFG                                                                                           | CHS3                | CHS2                | CHS1                 | CHS0                  | GO/DONE               | ADON                 | 0000 0000            | 111,200 |  |  |

| TABLE 2-1: | PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0 |

|------------|-------------------------------------------------------------------------|

|------------|-------------------------------------------------------------------------|

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplementedNote1:MCLR and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

mismatch exists.

2: PIC16F687/PIC16F689/PIC16F690 only.

3: PIC16F685/PIC16F690 only.

4: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

6: When SSPCON register bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. See Registers 13-2 and 13-3 for more detail.

7: Port pins with analog functions controlled by the ANSEL and ANSELH registers will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets).

## PIC16F631/677/685/687/689/690

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|-------|-------|-------|--------|--------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE | PWRTE | WDTE  | FOSC2  | FOSC1  | FOSC0  | _                    | _                                              |

| OSCCON                | _     | IRCF2 | IRCF1 | IRCF0 | OSTS  | HTS    | LTS    | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | _     | _     | —     | TUN4  | TUN3  | TUN2   | TUN1   | TUN0   | 0 0000               | u uuuu                                         |

| PIE1                  | _     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                                      |

| PIR1                  | -     | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                                      |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 14-1) for operation of all register bits.

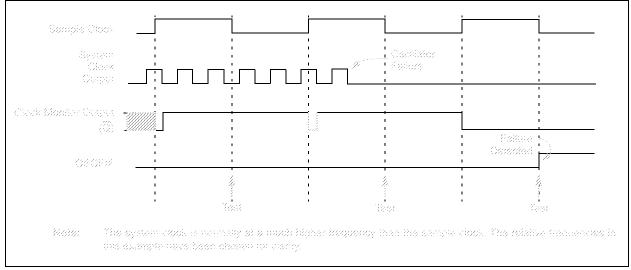

#### 4.2.5.2 RA1/AN1/C12IN0-/VREF/ICSPCLK

Figure 4-2 shows the diagram for this pin. The RA1/ AN1/C12IN0-/VREF/ICSPCLK pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C1 or C2

- a voltage reference input for the ADC

- In-Circuit Serial Programming clock

#### **BLOCK DIAGRAM OF RA1** FIGURE 4-2: Analog(1) Input Mode Data Bus D Q Vdd WR CK Q Weak WPU RABPU RD WPU/ Vdd D Q WR СК Q PORTA I/O Pin D G Vss WR СК Q TRIS Analog<sup>(1)</sup> Input Mode RD TRIS/ RD PORT/ D Q D Q WR Q IOCA ΕN Q3 RD IOCA Q D ΕN Interrupt-on-Change **RD PORTA** To Comparator To A/D Converter(2) ANSEL determines Analog Input mode. Note 1: Not implemented on PIC16F631. 2:

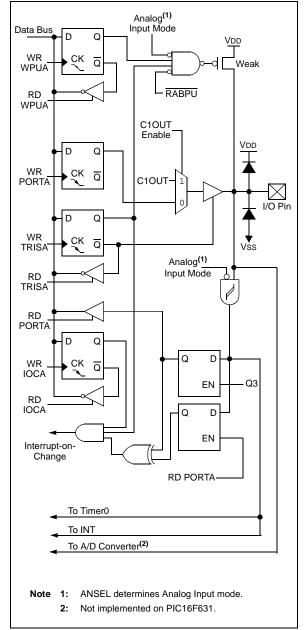

#### 4.2.5.3 RA2/AN2/T0CKI/INT/C1OUT

Figure 4-3 shows the diagram for this pin. The RA2/AN2/ T0CKI/INT/C1OUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- the clock input for Timer0

- an external edge triggered interrupt

- a digital output from Comparator C1

#### FIGURE 4-3: BLOCK DIAGRAM OF RA2

## 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The Analog Comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- PWM shutdown

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- SR Latch

- Programmable and Fixed Voltage Reference

## Note: Only Comparator C2 can be linked to Timer1.

### 8.1 Comparator Overview

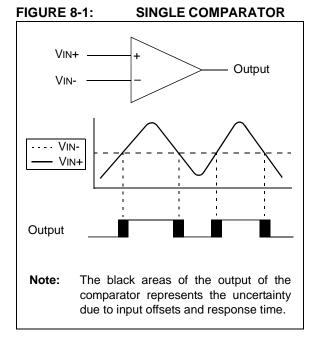

A single comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### 8.7 Analog Input Connection Considerations

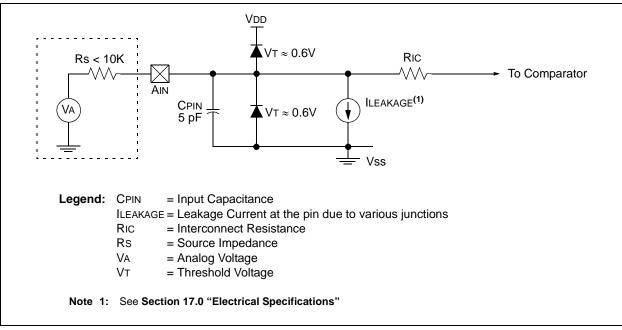

A simplified circuit for an analog input is shown in Figure 8-6. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 8-6: ANALOG INPUT MODEL

#### 10.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDAT register; therefore, it can be read in the next instruction. EEDAT will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 10-1: DATA EEPROM READ

| BANKSEL | EEADR ;     |                         |

|---------|-------------|-------------------------|

| MOVF    | DATA_EE_ADD | R, W;                   |

| MOVWF   | EEADR       | ;Data Memory            |

|         |             | ;Address to read        |

| BANKSEL | EECON1      | ;                       |

| BCF     | EECON1, EEP | GD;Point to DATA memory |

| BSF     | EECON1, RD  | ;EE Read                |

| BANKSEL | EEDAT       | ;                       |

| MOVF    | EEDAT, W    | ;W = EEDAT              |

| BANKSEL | PORTA       | ;Bank 0                 |

|         |             |                         |

## 10.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the specific sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### BANKSELEEADR MOVFDATA\_EE\_ADDR, W; MOVWFEEADR ;Data Memory Address to write MOVFDATA\_EE\_DATA, W; MOVWFEEDAT ;Data Memory Value to write BANKSELEECON1 ; BCF EECON1, EEPGD; Point to DATA memory BSF EECON1, WREN; Enable writes BCF INTCON, GIE ; Disable INTs. BTFSCINTCON, GIE;SEE AN576 GOTO\$-2 MOVLW55h ; Required Sequence MOVWFEECON2 ;Write 55h MOVLWAAh ; MOVWFEECON2 ;Write AAh BSF EECON1, WR ;Set WR bit to begin write BSF INTCON, GIE ; Enable INTs. SLEEP ;Wait for interrupt to signal write complete (optional) BCF EECON1, WREN; Disable writes BANKSEL0x00 ;Bank 0

#### EXAMPLE 10-2: DATA EEPROM WRITE

#### 10.1.4 READING THE FLASH PROGRAM MEMORY (PIC16F685/PIC16F689/ PIC16F690)

To read a program memory location, the user must write the Least and Most Significant address bits to the EEADR and EEADRH registers, set the EEPGD control bit of the EECON1 register, and then set control bit RD. Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDAT and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDAT and EEDATH registers will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

- If the WR bit is set when EEPGD = 1, it will be immediately reset to '0' and no operation will take place.

#### EXAMPLE 10-3: FLASH PROGRAM READ

|                      | BANKSEL | EEADR            |     | ;                                                        |

|----------------------|---------|------------------|-----|----------------------------------------------------------|

|                      | MOVF    | MS_PROG_EE_ADDR, | W   | ;                                                        |

|                      | MOVWF   | EEADRH           |     | ;MS Byte of Program Address to read                      |

|                      | MOVF    | LS_PROG_EE_ADDR, | W   | ;                                                        |

|                      | MOVWF   | EEADR            |     | ;LS Byte of Program Address to read                      |

|                      | BANKSEL | EECON1           | ;   |                                                          |

|                      | BSF     | EECON1, EEPGD    |     | ;Point to PROGRAM memory                                 |

| <del>т</del> 8       | BSF     | EECON1, RD       |     | ;EE Read                                                 |

| Required<br>Sequence | NOP     |                  |     | ;First instruction after BSF EECON1,RD executes normally |

|                      | NOP     |                  |     | ;Any instructions here are ignored as program            |

| <b></b>              |         |                  |     | ;memory is read in second cycle after BSF EECON1,RD      |

| ;                    |         |                  |     |                                                          |

|                      | BANKSEL | EEDAT            | ;   |                                                          |

|                      | MOVF    | EEDAT, W         |     | ;W = LS Byte of Program Memory                           |

|                      | MOVWF   | LOWPMBYTE        |     | ;                                                        |

|                      | MOVF    | EEDATH, W        |     | ;W = MS Byte of Program EEDAT                            |

|                      | MOVWF   | HIGHPMBYTE       |     | ;                                                        |

|                      | BANKSEL | 0x00             | ;Ba | nk 0                                                     |

|                      |         |                  |     |                                                          |

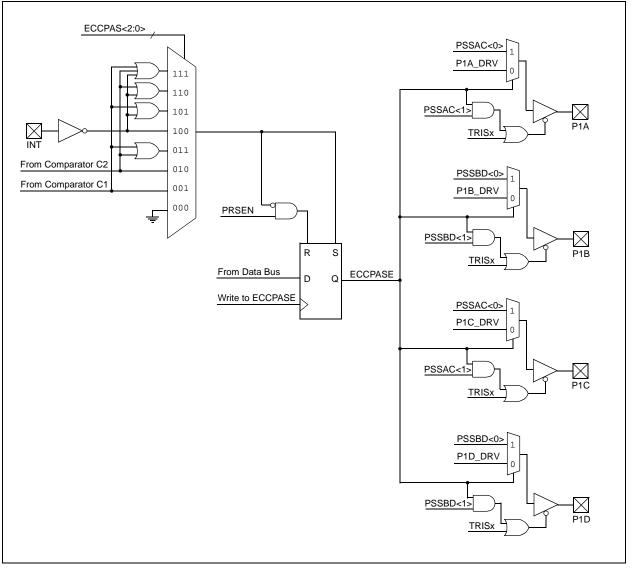

#### 11.4.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPASx bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator C1

- Comparator C2

- Setting the ECCPASE bit in firmware

A shutdown condition is indicated by the ECCPASE (Auto-Shutdown Event Status) bit of the ECCPAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPASE bit is set to '1'. The ECCPASE will remain set until cleared in firmware or an auto-restart occurs (see Section 11.4.5 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [P1A/P1C] and [P1B/P1D]. The state of each pin pair is determined by the PSSAC and PSSBD bits of the ECCPAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### FIGURE 11-14: AUTO-SHUTDOWN BLOCK DIAGRAM

#### REGISTER 11-2: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

| -                                                                                                                                                                                  |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 |        |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|--------|-----------------|--------|--|--|--|--|

| R/W-0                                                                                                                                                                              | R/W-0                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                              | R/W-0                                                                             | R/W-0                | R/W-0  | R/W-0           | R/W-0  |  |  |  |  |

| ECCPAS                                                                                                                                                                             | E ECCPAS2                                                                                                                                                            | ECCPAS1                                                                                                                                                                                                                                                                            | ECCPAS0                                                                           | PSSAC1               | PSSAC0 | PSSBD1          | PSSBD0 |  |  |  |  |

| bit 7                                                                                                                                                                              |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 | bit 0  |  |  |  |  |

|                                                                                                                                                                                    |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 |        |  |  |  |  |

| Legend:                                                                                                                                                                            |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 |        |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                                                 |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 |        |  |  |  |  |

| -n = Value                                                                                                                                                                         | at POR                                                                                                                                                               | '1' = Bit is set                                                                                                                                                                                                                                                                   |                                                                                   | '0' = Bit is cle     | ared   | x = Bit is unkr | nown   |  |  |  |  |

| bit 7                                                                                                                                                                              | bit 7 <b>ECCPASE:</b> ECCP Auto-Shutdown Event Status bit<br>1 = A shutdown event has occurred; ECCP outputs are in shutdown state<br>0 = ECCP outputs are operating |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 |        |  |  |  |  |

| bit 6-4                                                                                                                                                                            | 000 =Auto-S<br>001 =Compa<br>010 =Compa<br>011 =Either (<br>100 =ViL on<br>101 =ViL on<br>110 =ViL on                                                                | INT pin or Com<br>INT pin or Com                                                                                                                                                                                                                                                   | abled<br>t high<br>t high(1)<br>utput is high<br>parator C1 out<br>parator C2 out | put high<br>put high |        |                 |        |  |  |  |  |

| bit 3-2                                                                                                                                                                            | 00 = Drive pi<br>01 = Drive pi<br>1x = Pins P1                                                                                                                       | <ul> <li>111 =VIL on INT pin or either Comparators output is high</li> <li><b>PSSACn:</b> Pins P1A and P1C Shutdown State Control bits</li> <li>00 = Drive pins P1A and P1C to '0'</li> <li>01 = Drive pins P1A and P1C to '1'</li> <li>1x = Pins P1A and P1C tri-state</li> </ul> |                                                                                   |                      |        |                 |        |  |  |  |  |

| bit 1-0 <b>PSSBDn:</b> Pins P1B and P1D Shutdown State Control bits<br>00 = Drive pins P1B and P1D to '0'<br>01 = Drive pins P1B and P1D to '1'<br>1x = Pins P1B and P1D tri-state |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                    |                                                                                   |                      |        |                 |        |  |  |  |  |

| Note 1:                                                                                                                                                                            | If C2SYNC is ena                                                                                                                                                     | bled, the shutd                                                                                                                                                                                                                                                                    | own will be del                                                                   | ayed by Timer        | 1.     |                 |        |  |  |  |  |

| Note 1: | The auto-shutdown condition is a level-    |

|---------|--------------------------------------------|

|         | based signal, not an edge-based signal.    |

|         | As long as the level is present, the auto- |

|         | shutdown will persist.                     |

- 2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

- **3:** Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

### 12.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind. The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 3.5** "Internal Clock Modes" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 12.3.1 "Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

#### REGISTER 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0           | R/W-0                                                              | R/W-0                | R/W-0           | R/W-0              | R/W-0              | R-1              | R/W-0 |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------|----------------------|-----------------|--------------------|--------------------|------------------|-------|--|--|--|--|--|--|

| CSRC            | TX9                                                                | TXEN <sup>(1)</sup>  | SYNC            | SENDB              | BRGH               | TRMT             | TX9D  |  |  |  |  |  |  |

| bit 7           |                                                                    |                      |                 |                    |                    |                  | bit 0 |  |  |  |  |  |  |

|                 |                                                                    |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

| Legend:         |                                                                    |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

| R = Readable    |                                                                    | W = Writable bit     |                 |                    | ented bit, read as |                  |       |  |  |  |  |  |  |

| -n = Value at F | POR                                                                | '1' = Bit is set     |                 | '0' = Bit is clear | red                | x = Bit is unkno | wn    |  |  |  |  |  |  |

| bit 7           | CSRC: Clock                                                        | Source Select bit    |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Asynchronous                                                       |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Don't care                                                         |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Synchronous                                                        | Synchronous mode:    |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 1 = Master r                                                       | node (clock genera   | ated internally | from BRG)          |                    |                  |       |  |  |  |  |  |  |

|                 | 0 = Slave m                                                        | ode (clock from ex   | ternal source)  |                    |                    |                  |       |  |  |  |  |  |  |

| bit 6           | TX9: 9-bit Tra                                                     | nsmit Enable bit     |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 1 = Selects 9-bit transmission                                     |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 0 = Selects 8                                                      | 8-bit transmission   |                 |                    |                    |                  |       |  |  |  |  |  |  |

| bit 5           | TXEN: Transmit Enable bit <sup>(1)</sup>                           |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 1 = Transmit enabled                                               |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 0 = Transmit disabled                                              |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

| bit 4           |                                                                    | RT Mode Select bi    | t               |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 1 = Synchror                                                       |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 0 = Asynchro                                                       |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

| bit 3           |                                                                    | d Break Character    | bit             |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Asynchronous                                                       |                      | enomiacion (a   | loored by borduro  | re upon complet    | ion)             |       |  |  |  |  |  |  |

|                 |                                                                    | nc Break on next to  |                 | leared by nardwa   | ire upon complet   | ion)             |       |  |  |  |  |  |  |

|                 | 0 = Sync Break transmission completed<br><u>Synchronous mode</u> : |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Don't care                                                         |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

| bit 2           | BRGH: High F                                                       | Baud Rate Select b   | bit             |                    |                    |                  |       |  |  |  |  |  |  |

| 2.1.2           | BRGH: High Baud Rate Select bit<br>Asynchronous mode:              |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 |                                                                    | 1 = High speed       |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 0 = Low spee                                                       | ed                   |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Synchronous mode:                                                  |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Unused in this                                                     | s mode               |                 |                    |                    |                  |       |  |  |  |  |  |  |

| bit 1           | TRMT: Transn                                                       | nit Shift Register S | tatus bit       |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 1 = TSR emp                                                        | oty                  |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | 0 = TSR full                                                       |                      |                 |                    |                    |                  |       |  |  |  |  |  |  |

| bit 0           |                                                                    | it of Transmit Data  |                 |                    |                    |                  |       |  |  |  |  |  |  |

|                 | Can be addres                                                      | ss/data bit or a par | ity bit.        |                    |                    |                  |       |  |  |  |  |  |  |

Note 1: SREN/CREN overrides TXEN in Sync mode.

| R/W-0           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                             | R/W-0                                                                                                               | R/W-0                                        | R/W-0                | R/W-0                |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------|----------------------|--|--|--|--|--|--|

| WCOL            | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SSPEN                                                                                                                                                                                                                                                         | CKP                                                                                                                                                                                               | SSPM3 <sup>(2)</sup>                                                                                                | SSPM2 <sup>(2)</sup>                         | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |  |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                                                                                                                     | •                                            |                      | bit                  |  |  |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                                                                                                                     |                                              |                      |                      |  |  |  |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |                                                                                                                     |                                              |                      |                      |  |  |  |  |  |  |