Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16F631/677/685/687/689/690

| Device    | Program<br>Memory | Data N          | lemory            | I/O | 10-bit A/D | Comparators | Timers   | SSP          | ECCP+ | EUSART |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|--------------|-------|--------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit | 3 <b>5</b> F | ECCFŦ | EUSARI |

| PIC16F631 | 1024              | 64              | 128               | 18  | —          | 2           | 1/1      | No           | No    | No     |

| PIC16F677 | 2048              | 128             | 256               | 18  | 12         | 2           | 1/1      | Yes          | No    | No     |

| PIC16F685 | 4096              | 256             | 256               | 18  | 12         | 2           | 2/1      | No           | Yes   | No     |

| PIC16F687 | 2048              | 128             | 256               | 18  | 12         | 2           | 1/1      | Yes          | No    | Yes    |

| PIC16F689 | 4096              | 256             | 256               | 18  | 12         | 2           | 1/1      | Yes          | No    | Yes    |

| PIC16F690 | 4096              | 256             | 256               | 18  | 12         | 2           | 2/1      | Yes          | Yes   | Yes    |

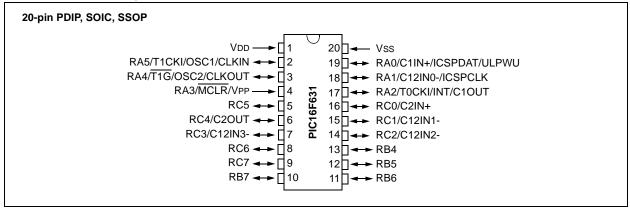

## PIC16F631 Pin Diagram

#### TABLE 1: PIC16F631 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | —      | IOC       | Y       | ICSPDAT     |

| RA1 | 18  | AN1       | C12IN0-     |        | IOC       | Y       | ICSPCLK     |

| RA2 | 17  | _         | C1OUT       | T0CKI  | IOC/INT   | Y       | —           |

| RA3 | 4   | —         | —           | —      | IOC       | Y(1)    | MCLR/Vpp    |

| RA4 | 3   | —         | —           | T1G    | IOC       | Y       | OSC2/CLKOUT |

| RA5 | 2   |           | —           | T1CKI  | IOC       | Y       | OSC1/CLKIN  |

| RB4 | 13  |           | —           | —      | IOC       | Y       | —           |

| RB5 | 12  | —         | —           | —      | IOC       | Y       | —           |

| RB6 | 11  | —         | —           | —      | IOC       | Y       | —           |

| RB7 | 10  |           | —           | _      | IOC       | Y       | —           |

| RC0 | 16  | AN4       | C2IN+       | —      | _         | —       | —           |

| RC1 | 15  | AN5       | C12IN1-     | _      |           |         | —           |

| RC2 | 14  | AN6       | C12IN2-     | —      |           | _       | —           |

| RC3 | 7   | AN7       | C12IN3-     |        |           |         | —           |

| RC4 | 6   |           | C2OUT       | —      |           |         | —           |

| RC5 | 5   |           | —           |        |           |         | —           |

| RC6 | 8   | —         |             | —      | _         | —       | —           |

| RC7 | 9   |           |             |        |           | _       | —           |

| —   | 1   |           |             | _      |           | _       | Vdd         |

| —   | 20  | _         |             | _      |           | _       | Vss         |

**Note 1:** Pull-up enabled only with external MCLR configuration.

|                                       | File<br>Address |                                                   | File<br>Address |                                       | File          |                                             | File<br>Address |

|---------------------------------------|-----------------|---------------------------------------------------|-----------------|---------------------------------------|---------------|---------------------------------------------|-----------------|

| La dia a stata data (1)               | -               | la dina at a dala (1)                             | 1               | lucations et a data (1)               | Address       | la dina sé a dala (1)                       |                 |

| Indirect addr. <sup>(1)</sup><br>TMR0 | 00h             | Indirect addr. <sup>(1)</sup><br>OPTION REG       | 80h             | Indirect addr. <sup>(1)</sup><br>TMR0 | 100h          | Indirect addr. <sup>(1)</sup><br>OPTION_REG | 180h            |

| PCL                                   | 01h             |                                                   | 81h             |                                       | 101h          |                                             | 181h            |

|                                       | 02h             | PCL                                               | 82h             | PCL                                   | 102h          | PCL                                         | 182h            |

| STATUS                                | 03h             | STATUS                                            | 83h             | STATUS                                | 103h          | STATUS                                      | 183h            |

| FSR                                   | 04h             | FSR                                               | 84h             | FSR                                   | 104h          | FSR                                         | 184h            |

| PORTA                                 | 05h             | TRISA                                             | 85h             | PORTA                                 | 105h          | TRISA                                       | 185h            |

| PORTB<br>PORTC                        | 06h<br>07h      | TRISB<br>TRISC                                    | 86h<br>87h      | PORTB<br>PORTC                        | 106h<br>107h  | TRISB<br>TRISC                              | 186h<br>187h    |

| FURIC                                 | 0711<br>08h     | TRISC                                             | 88h             | FURIC                                 | 10711<br>108h | TRISC                                       | 188h            |

|                                       |                 |                                                   | 89h             |                                       |               |                                             | 189h            |

| PCLATH                                | 09h             | PCLATH                                            |                 | PCLATH                                | 109h<br>104b  | PCLATH                                      | 18Ah            |

| INTCON                                | 0Ah             | INTCON                                            | 8Ah<br>8Bh      | INTCON                                | 10Ah<br>10Bh  | INTCON                                      | 18Bh            |

| PIR1                                  | 0Bh             |                                                   |                 |                                       | 10Bh<br>10Ch  |                                             |                 |

|                                       | 0Ch             | PIE1                                              | 8Ch             | EEDAT                                 | 10Ch          | EECON1                                      | 18Ch            |

| PIR2                                  | 0Dh             | PIE2                                              | 8Dh             | EEADR                                 | 10Dh          | EECON2 <sup>(1)</sup>                       | 18Dh            |

| TMR1L                                 | 0Eh             | PCON                                              | 8Eh             |                                       | 10Eh          |                                             | 18Eh            |

| TMR1H                                 | 0Fh             | OSCCON                                            | 8Fh             |                                       | 10Fh          |                                             | 18Fh            |

| T1CON                                 | 10h             | OSCTUNE                                           | 90h             |                                       | 110h          |                                             | 190h            |

|                                       | 11h             |                                                   | 91h             |                                       | 111h          |                                             | 191h            |

| 0000115                               | 12h             | 000400(2)                                         | 92h             |                                       | 112h          |                                             | 192h            |

| SSPBUF                                | 13h             | SSPADD <sup>(2)</sup>                             | 93h             |                                       | 113h          |                                             | 193h            |

| SSPCON                                | 14h             | SSPSTAT                                           | 94h             |                                       | 114h          |                                             | 194h            |

|                                       | 15h             | WPUA                                              | 95h             | WPUB                                  | 115h          |                                             | 195h            |

|                                       | 16h             | IOCA                                              | 96h             | IOCB                                  | 116h          |                                             | 196h            |

|                                       | 17h             | WDTCON                                            | 97h             |                                       | 117h          |                                             | 197h            |

|                                       | 18h             |                                                   | 98h             | VRCON                                 | 118h          |                                             | 198h            |

|                                       | 19h             |                                                   | 99h             | CM1CON0                               | 119h          |                                             | 199h            |

|                                       | 1Ah             |                                                   | 9Ah             | CM2CON0                               | 11Ah          |                                             | 19Ah            |

|                                       | 1Bh             |                                                   | 9Bh             | CM2CON1                               | 11Bh          |                                             | 19Bh            |

|                                       | 1Ch             |                                                   | 9Ch             |                                       | 11Ch          |                                             | 19Ch            |

|                                       | 1Dh             |                                                   | 9Dh             |                                       | 11Dh          |                                             | 19Dh            |

| ADRESH                                | 1Eh             | ADRESL                                            | 9Eh             | ANSEL                                 | 11Eh          | SRCON                                       | 19Eh            |

| ADCON0                                | 1Fh             | ADCON1                                            | 9Fh             | ANSELH                                | 11Fh          |                                             | 19Fh            |

| Quanta                                | 20h             | General<br>Purpose<br>Register                    | A0h             |                                       | 120h          |                                             | 1A0h            |

| General<br>Purpose<br>Register        |                 | 32 Bytes                                          | BFh<br>C0h      |                                       |               |                                             |                 |

| 96 Bytes                              |                 |                                                   | EFh             |                                       | 16Fh          |                                             | 1EFh            |

|                                       | 7Fh             | accesses<br>70h-7Fh                               | F0h<br>FFh      | accesses<br>70h-7Fh                   | 170h<br>17Fh  | accesses<br>70h-7Fh                         | 1F0h<br>1FFh    |

| Bank 0                                | -               | Bank 1                                            | -               | Bank 2                                |               | Bank 3                                      |                 |

| Note 1: Not a                         | physical re     | data memory locat<br>gister.<br>o accesses the SS |                 |                                       | under certa   | in conditions.                              |                 |

#### FIGURE 2-5: PIC16F677 SPECIAL FUNCTION REGISTERS

# PIC16F631/677/685/687/689/690

## 3.5.2.1 OSCTUNE Register

-n = Value at POR

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

x = Bit is unknown

## REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

'1' = Bit is set

| U-0          | U-0 | U-0          | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------------|-----|--------------|-------|------------------------------------|-------|-------|-------|--|--|--|

| —            | —   | —            | TUN4  | TUN3                               | TUN2  | TUN1  | TUN0  |  |  |  |

| bit 7        |     |              |       |                                    |       |       | bit 0 |  |  |  |

|              |     |              |       |                                    |       |       |       |  |  |  |

| Legend:      |     |              |       |                                    |       |       |       |  |  |  |

| R = Readable | bit | W = Writable | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |

'0' = Bit is cleared

| bit 7-5 | Unimplemented: Read as '0'                                                |

|---------|---------------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                           |

|         | 01111 = Maximum frequency                                                 |

|         | 01110 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 00001 =                                                                   |

|         | 00000 = Oscillator module is running at the factory-calibrated frequency. |

|         | 11111 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 10000 = Minimum frequency                                                 |

|         |                                                                           |

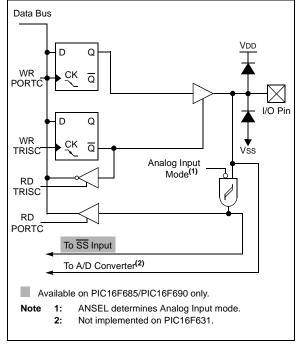

## 4.5.7 RC6/AN8/SS

The RC6/AN8/ $\overline{SS}^{(1,2)}$  is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a slave select input

| Note 1: | SS is available on PIC16F687/PIC16F689/ |

|---------|-----------------------------------------|

|         | PIC16F690 only.                         |

2: AN8 is not implemented on PIC16F631.

## FIGURE 4-15: BLOCK DIAGRAM OF RC6

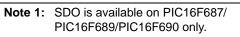

## 4.5.8 RC7/AN9/SDO

The RC7/AN9/SDO $^{(1,2)}$  is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a serial data output

2: AN9 is not implemented on PIC16F631.

### FIGURE 4-16: BLOCK DIAGRAM OF RC7

| Name    | Bit 7                                                                       | Bit 6          | Bit 5         | Bit 4          | Bit 3         | Bit 2       | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|----------------|---------------|----------------|---------------|-------------|--------|--------|----------------------|---------------------------------|

| CM2CON1 | MC10UT                                                                      | MC2OUT         | —             | —              | —             | —           | T1GSS  | C2SYNC | 10                   | 10                              |

| INTCON  | GIE                                                                         | PEIE           | T0IE          | INTE           | RABIE         | T0IF        | INTF   | RABIF  | 0000 0000            | 0000 0000                       |

| PIE1    | —                                                                           | ADIE           | RCIE          | TXIE           | SSPIE         | CCP1IE      | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —                                                                           | ADIF           | RCIF          | TXIF           | SSPIF         | CCP1IF      | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| TMR1H   | Holding Reg                                                                 | gister for the | Most Signific | ant Byte of th | he 16-bit TMI | R1 Register |        | •      | xxxx xxxx            | uuuu uuuu                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |               |                |               |             |        |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON   | T1GINV                                                                      | TMR1GE         | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC      | TMR1CS | TMR10N | 0000 0000            | uuuu uuuu                       |

## TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

| R/W-0         | R-0                                                              | R/W-0                                                                                                        | R/W-0                                    | U-0              | R/W-0            | R/W-0            | R/W-0    |  |  |  |

|---------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|------------------|----------|--|--|--|

| C2ON          | C2OUT                                                            | C2OE                                                                                                         | C2POL                                    | —                | C2R              | C2CH1            | C2CH0    |  |  |  |

| bit 7         |                                                                  |                                                                                                              |                                          |                  |                  |                  | bit 0    |  |  |  |

| Legend:       |                                                                  |                                                                                                              |                                          |                  |                  |                  |          |  |  |  |

| R = Readabl   | e bit                                                            | W = Writable                                                                                                 | bit                                      | U = Unimple      | emented bit, rea | ad as '0'        |          |  |  |  |

| -n = Value at | POR                                                              | '1' = Bit is set                                                                                             | t                                        | '0' = Bit is cl  | eared            | x = Bit is unk   | nown     |  |  |  |

| bit 7         | C2ON: Com                                                        | parator C2 Ena                                                                                               | ble bit                                  |                  |                  |                  |          |  |  |  |

|               | 1 = Compara                                                      | ator C2 is enabl<br>ator C2 is disab                                                                         | ed                                       |                  |                  |                  |          |  |  |  |

| bit 6         | C2OUT: Com                                                       | nparator C2 Ou                                                                                               | tput bit                                 |                  |                  |                  |          |  |  |  |

|               | C2OUT = 0 v<br>C2OUT = 1 v<br><u>If C2POL = 0</u><br>C2OUT = 1 v | <u>_ (inverted pola</u><br>when C2VIN+ ><br>when C2VIN+ <<br>(non-inverted<br>when C2VIN+ ><br>when C2VIN+ < | C2VIN-<br>C2VIN-<br>polarity):<br>C2VIN- |                  |                  |                  |          |  |  |  |

| bit 5         | C2OE: Comparator C2 Output Enable bit                            |                                                                                                              |                                          |                  |                  |                  |          |  |  |  |

|               |                                                                  | s present on C<br>s internal only                                                                            | 20UT pin <sup>(1)</sup>                  |                  |                  |                  |          |  |  |  |

| bit 4         | C1POL: Con                                                       | nparator C1 Ou                                                                                               | tput Polarity S                          | elect bit        |                  |                  |          |  |  |  |

|               |                                                                  | ogic is inverted<br>ogic is not inve                                                                         |                                          |                  |                  |                  |          |  |  |  |

| bit 3         | Unimplemer                                                       | nted: Read as '                                                                                              | 0'                                       |                  |                  |                  |          |  |  |  |

| bit 2         | C2R: Compa                                                       | arator C2 Refer                                                                                              | ence Select bi                           | ts (non-invertii | ng input)        |                  |          |  |  |  |

|               |                                                                  | connects to C2<br>connects to C2                                                                             |                                          |                  |                  |                  |          |  |  |  |

| bit 1-0       | C2CH<1:0>: Comparator C2 Channel Select bits                     |                                                                                                              |                                          |                  |                  |                  |          |  |  |  |

|               | 01 = C2VIN-<br>10 = C2VIN-                                       | of C2 connects<br>of C2 connects<br>of C2 connects<br>of C2 connects                                         | to C12IN1- pi<br>to C12IN2- pi           | n<br>n           |                  |                  |          |  |  |  |

|               | TT = CZVIN                                                       | ut requires the f                                                                                            |                                          |                  | 20E = 1, C20I    | N = 1 and corres | sponding |  |  |  |

## REGISTER 8-2: CM2CON0: COMPARATOR C2 CONTROL REGISTER 0

PORT TRIS bit = 0.

## 8.7 Analog Input Connection Considerations

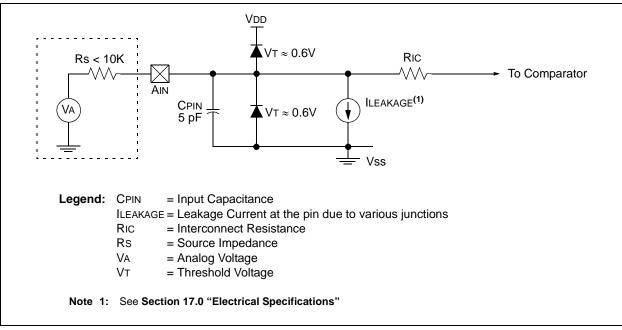

A simplified circuit for an analog input is shown in Figure 8-6. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 8-6: ANALOG INPUT MODEL

## 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

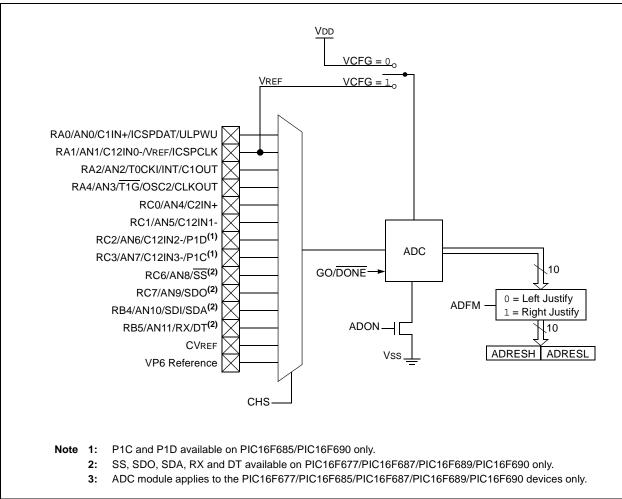

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

Note: The ADC module applies to PIC16F677/ PIC16F685/PIC16F687/PIC16F689/ PIC16F690 devices only.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

## FIGURE 9-1: ADC BLOCK DIAGRAM

Figure 9-1 shows the block diagram of the ADC.

#### 10.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDAT register; therefore, it can be read in the next instruction. EEDAT will hold this value until another read or until it is written to by the user (during a write operation).

### EXAMPLE 10-1: DATA EEPROM READ

| BANKSEL | EEADR ;     |                         |

|---------|-------------|-------------------------|

| MOVF    | DATA_EE_ADD | R, W;                   |

| MOVWF   | EEADR       | ;Data Memory            |

|         |             | ;Address to read        |

| BANKSEL | EECON1      | ;                       |

| BCF     | EECON1, EEP | GD;Point to DATA memory |

| BSF     | EECON1, RD  | ;EE Read                |

| BANKSEL | EEDAT       | ;                       |

| MOVF    | EEDAT, W    | ;W = EEDAT              |

| BANKSEL | PORTA       | ;Bank 0                 |

|         |             |                         |

## 10.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the specific sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### BANKSELEEADR MOVFDATA\_EE\_ADDR, W; MOVWFEEADR ;Data Memory Address to write MOVFDATA\_EE\_DATA, W; MOVWFEEDAT ;Data Memory Value to write BANKSELEECON1 ; BCF EECON1, EEPGD; Point to DATA memory BSF EECON1, WREN; Enable writes BCF INTCON, GIE ; Disable INTs. BTFSCINTCON, GIE;SEE AN576 GOTO\$-2 MOVLW55h ; Required Sequence MOVWFEECON2 ;Write 55h MOVLWAAh ; MOVWFEECON2 ;Write AAh BSF EECON1, WR ;Set WR bit to begin write BSF INTCON, GIE ; Enable INTs. SLEEP ;Wait for interrupt to signal write complete (optional) BCF EECON1, WREN; Disable writes BANKSEL0x00 ;Bank 0

#### EXAMPLE 10-2: DATA EEPROM WRITE

# PIC16F631/677/685/687/689/690

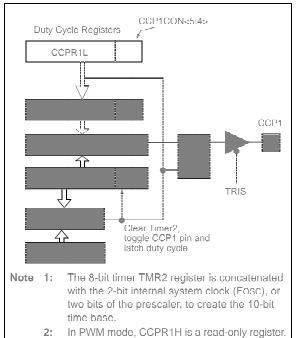

## 11.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the   | CCP1CON        | ON register |      |  |

|-------|------------|-------|----------------|-------------|------|--|

|       | relinquish | n CCF | 1 control of t | he CCP1     | pin. |  |

Figure 11-3 shows a simplified block diagram of PWM operation.

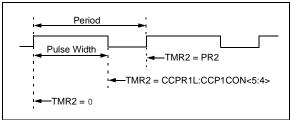

Figure 11-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

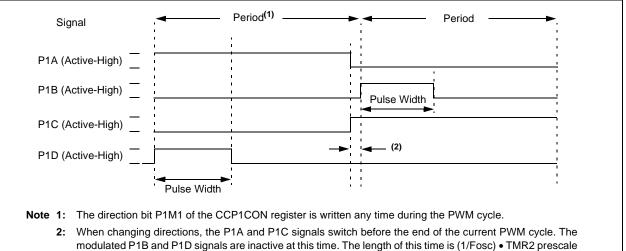

## 11.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 11-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 11-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices QC and QD (see Figure 11-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

## FIGURE 11-12: EXAMPLE OF PWM DIRECTION CHANGE

value.

|        | SYNC = 0, BRGH = 0, BRG16 = 0 |                   |                             |                |                   |                             |                    |            |                             |                  |            |                             |

|--------|-------------------------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|--------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc                          | Fosc = 20.000 MHz |                             | Fosc           | Fosc = 18.432 MHz |                             | Fosc = 11.0592 MHz |            |                             | Fosc = 8.000 MHz |            |                             |

| RATE   | Actual<br>Rate                | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                             |                   | _                           |                | _                 | _                           | _                  | _          | _                           | _                | _          | _                           |

| 1200   | 1221                          | 1.73              | 255                         | 1200           | 0.00              | 239                         | 1200               | 0.00       | 143                         | 1202             | 0.16       | 103                         |

| 2400   | 2404                          | 0.16              | 129                         | 2400           | 0.00              | 119                         | 2400               | 0.00       | 71                          | 2404             | 0.16       | 51                          |

| 9600   | 9470                          | -1.36             | 32                          | 9600           | 0.00              | 29                          | 9600               | 0.00       | 17                          | 9615             | 0.16       | 12                          |

| 10417  | 10417                         | 0.00              | 29                          | 10286          | -1.26             | 27                          | 10165              | -2.42      | 16                          | 10417            | 0.00       | 11                          |

| 19.2k  | 19.53k                        | 1.73              | 15                          | 19.20k         | 0.00              | 14                          | 19.20k             | 0.00       | 8                           | _                | _          | _                           |

| 57.6k  | —                             | —                 | _                           | 57.60k         | 0.00              | 7                           | 57.60k             | 0.00       | 2                           | —                | —          | —                           |

| 115.2k | —                             |                   | _                           | —              | _                 | _                           | _                  |            | _                           | _                | _          | _                           |

#### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |            |                             |                   |            |                             |                  |            |                             |                  |            |                             |  |

|--------|----------------------------------------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|

| BAUD   | Fosc = 4.000 MHz                                   |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |

| RATE   | Actual<br>Rate                                     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | 300                                                | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 103                         | 300              | 0.16       | 51                          |  |

| 1200   | 1202                                               | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 25                          | 1202             | 0.16       | 12                          |  |

| 2400   | 2404                                               | 0.16       | 25                          | 2400              | 0.00       | 23                          | 2404             | 0.16       | 12                          | —                | _          | _                           |  |

| 9600   | —                                                  | _          | _                           | 9600              | 0.00       | 5                           | _                | _          | _                           | —                | _          | _                           |  |

| 10417  | 10417                                              | 0.00       | 5                           | —                 | _          | _                           | 10417            | 0.00       | 2                           | —                | _          | _                           |  |

| 19.2k  | —                                                  | _          | _                           | 19.20k            | 0.00       | 2                           | _                | _          | _                           | —                | _          | _                           |  |

| 57.6k  | —                                                  | —          | —                           | 57.60k            | 0.00       | 0                           | —                | —          | —                           | —                | —          | —                           |  |

| 115.2k | —                                                  | —          | _                           | _                 | _          | —                           | _                | —          | _                           | —                | —          | —                           |  |

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                |            |                             |                |            |                             |                |            |                             |  |

|--------|-------------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|

| BAUD   | Fosc = 20.000 MHz |                               | Fosc = 18.432 MHz           |                |            | Fosc = 11.0592 MHz          |                |            | Fosc = 8.000 MHz            |                |            |                             |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    | —                 |                               | _                           | _              |            | _                           |                | —          | _                           |                | —          |                             |  |

| 1200   | —                 | —                             | —                           | —              | _          | —                           | —              | —          | —                           | —              | —          | —                           |  |

| 2400   | _                 | _                             | _                           | —              | _          | _                           | —              | _          | _                           | 2404           | 0.16       | 207                         |  |

| 9600   | 9615              | 0.16                          | 129                         | 9600           | 0.00       | 119                         | 9600           | 0.00       | 71                          | 9615           | 0.16       | 51                          |  |

| 10417  | 10417             | 0.00                          | 119                         | 10378          | -0.37      | 110                         | 10473          | 0.53       | 65                          | 10417          | 0.00       | 47                          |  |

| 19.2k  | 19.23k            | 0.16                          | 64                          | 19.20k         | 0.00       | 59                          | 19.20k         | 0.00       | 35                          | 19231          | 0.16       | 25                          |  |

| 57.6k  | 56.82k            | -1.36                         | 21                          | 57.60k         | 0.00       | 19                          | 57.60k         | 0.00       | 11                          | 55556          | -3.55      | 8                           |  |

| 115.2k | 113.64k           | -1.36                         | 10                          | 115.2k         | 0.00       | 9                           | 115.2k         | 0.00       | 5                           | —              | —          | _                           |  |

## 14.0 SPECIAL FEATURES OF THE CPU

The PIC16F631/677/685/687/689/690 have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming

The PIC16F631/677/685/687/689/690 have two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 14-2).

## 14.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 14-2. These bits are mapped in program memory location 2007h.

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information.

| Register Address |                       | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |  |  |

|------------------|-----------------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| W                | —                     | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| INDF             | 00h/80h/<br>100h/180h | XXXX XXXX      | XXXX XXXX                                                 | <u>uuuu</u> uuuu                                                                      |  |  |

| TMR0             | 01h/101h              | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| PCL              | 02h/82h/<br>102h/182h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |  |  |

| STATUS           | 03h/83h/<br>103h/183h | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                                                              |  |  |

| FSR              | 04h/84h/<br>104h184h  | XXXX XXXX      | սսսս սսսս                                                 | <u>uuuu</u> uuuu                                                                      |  |  |

| PORTA            | 05h/105h              | xx xxxx        | uu uuuu                                                   | uu uuuu                                                                               |  |  |

| PORTB            | 06h/106h              | xxxx           | uuuu                                                      | uuuu                                                                                  |  |  |

| PORTC            | 07h/107h              | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| PCLATH           | 0Ah/8Ah/<br>10Ah/18Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |  |  |

| INTCON           | 0Bh/8Bh/<br>10Bh/18Bh | 0000 000x      | 0000 000u                                                 | uuuu uuuu <sup>(2)</sup>                                                              |  |  |

| PIR1             | 0Ch                   | -000 0000      | -000 0000                                                 | -uuu uuuu <sup>(2)</sup>                                                              |  |  |

| PIR2             | 0Dh                   | 0000           | 0000                                                      | uuuu <b>(2)</b>                                                                       |  |  |

| TMR1L            | 0Eh                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| TMR1H            | 0Fh                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| T1CON            | 10h                   | 0000 0000      | <u>uuuu</u> uuuu                                          | սսսս սսսս                                                                             |  |  |

| TMR2             | 11h                   | 0000 0000      | 0000 0000                                                 | <u>uuuu</u> uuuu                                                                      |  |  |

| T2CON            | 12h                   | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |  |  |

| SSPBUF           | 13h                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| SSPCON           | 14h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| CCPR1L           | 15h                   | XXXX XXXX      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| CCPR1H           | 16h                   | xxxx xxxx      | uuuu uuuu                                                 | <u>uuuu</u> uuuu                                                                      |  |  |

| CCP1CON          | 17h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| RCSTA            | 18h                   | 0000 000x      | 0000 000x                                                 | uuuu uuuu                                                                             |  |  |

| TXREG            | 19h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| RCREG            | 1Ah                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| PWM1CON          | 1Ch                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| ECCPAS           | 1Dh                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |

| ADRESH           | 1Eh                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |  |  |

| ADCON0           | 1Fh                   | 0000 0000      | 0000 0000                                                 | սսսս սսսս                                                                             |  |  |

| OPTION_REG       | 81h/181h              | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |  |  |

| TRISA            | 85h/185h              | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |  |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPM < 3:0 > = 1001.

| Register Addres       |          | Power-on Reset | MCLR Reset<br>WDT Reset (Continued)<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |  |  |

|-----------------------|----------|----------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| TRISB                 | 86h/186h | 1111           | 1111                                                                  | uuuu                                                                                  |  |  |

| TRISC                 | 87h/187h | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| PIE1                  | 8Ch      | -000 0000      | -000 0000                                                             | -uuu uuuu                                                                             |  |  |

| PIE2                  | 8Dh      | 0000           | 0000                                                                  | uuuu uuuu                                                                             |  |  |

| PCON                  | 8Eh      | 010x           | 0uuq <sup>1, 5)</sup>                                                 | uuuu                                                                                  |  |  |

| OSCCON                | 8Fh      | -110 q000      | -110 q000                                                             | -uuu uuuu                                                                             |  |  |

| OSCTUNE               | 90h      | 0 0000         | u uuuu                                                                | u uuuu                                                                                |  |  |

| PR2                   | 92h      | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| SSPADD                | 93h      | 0000 0000      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| SSPMSK <sup>(6)</sup> | 93h      |                | 1111 1111                                                             | սսսս սսսս                                                                             |  |  |

| SSPSTAT               | 94h      | 0000 0000      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| WPUA                  | 95h      | 11 -111        | 11 -111                                                               | uuuu uuuu                                                                             |  |  |

| IOCA                  | 96h      | 00 0000        | 00 0000                                                               | uu uuuu                                                                               |  |  |

| WDTCON                | 97h      | 0 1000         | 0 1000                                                                | u uuuu                                                                                |  |  |

| TXSTA                 | 98h      | 0000 0010      | 0000 0010                                                             | uuuu uuuu                                                                             |  |  |

| SPBRG                 | 99h      | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| SPBRGH                | 9Ah      | 0000 0000      | 0000 0000                                                             | սսսս սսսս                                                                             |  |  |

| BAUDCTL               | 9Bh      | 01-0 0-00      | 01-0 0-00                                                             | uu-u u-uu                                                                             |  |  |

| ADRESL                | 9Eh      | xxxx xxxx      | uuuu uuuu                                                             | uuuu uuuu                                                                             |  |  |

| ADCON1                | 9Fh      | -000           | -000                                                                  | -uuu                                                                                  |  |  |

| EEDAT                 | 10Ch     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| EEADR                 | 10Dh     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| EEDATH                | 10Eh     | 00 0000        | 00 0000                                                               | uu uuuu                                                                               |  |  |

| EEADRH                | 10Fh     | 0000           | 0000                                                                  | uuuu                                                                                  |  |  |

| WPUB                  | 115h     | 1111           | 1111                                                                  | uuuu                                                                                  |  |  |

| IOCB                  | 116h     | 0000           | 0000                                                                  | uuuu                                                                                  |  |  |

| VRCON                 | 118h     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| CM1CON0               | 119h     | 0000 -000      | 0000 -000                                                             | uuuu -uuu                                                                             |  |  |

| CM2CON0               | 11Ah     | 0000 -000      | 0000 -000                                                             | uuuu -uuu                                                                             |  |  |

| CM2CON1               | 11Bh     | 0000           | 0010                                                                  | uuuu                                                                                  |  |  |

| ANSEL                 | 11Eh     | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| ANSELH                | 11Fh     | 1111           | 1111                                                                  | uuuu                                                                                  |  |  |

| EECON1                | 18Ch     | x x000         | u q000                                                                | uuuu                                                                                  |  |  |

| EECON2                | 18Dh     |                |                                                                       |                                                                                       |  |  |

| PSTRCON               | 19Dh     | 0 0001         | 0 0001                                                                | u uuuu                                                                                |  |  |

| SRCON                 | 19EH     | 0000 00        | 0000 00                                                               | uuuu uu                                                                               |  |  |

## TABLE 14-4: INITIALIZATION CONDITION FOR REGISTER (CONTINUED)

$\label{eq:logend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

**5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPM < 3:0 > = 1001.

## TABLE 14-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

## 14.3 Interrupts

The PIC16F631/677/685/687/689/690 have multiple sources of interrupt:

- External Interrupt RA2/INT

- TMR0 Overflow Interrupt

- PORTA/PORTB Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt (except PIC16F631)

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt (PIC16F685/PIC16F690 only)

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- Enhanced CCP Interrupt (PIC16F685/PIC16F690 only)

- EUSART Receive and Transmit interrupts (PIC16F687/PIC16F689/PIC16F690 only)

The Interrupt Control register (INTCON) and Peripheral Interrupt Request Register 1 (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON, PIE1 and PIE2 registers, respectively. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- PORTA/PORTB Change Interrupts

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the PIR1 and PIR2 registers. The corresponding interrupt enable bits are contained in PIE1 and PIE2 registers.

The following interrupt flags are contained in the PIR1 register:

- A/D Interrupt

- EUSART Receive and Transmit Interrupts

- Timer1 Overflow Interrupt

- Synchronous Serial Port (SSP) Interrupt

- Enhanced CCP1 Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

The following interrupt flags are contained in the PIR2 register:

- Fail-Safe Clock Monitor Interrupt

- 2 Comparator Interrupts

- EEPROM Data Write Interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

For external interrupt events, such as the INT pin, PORTA/PORTB change interrupts, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 14-8). The latency is the same for one or 2-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, A/D, data EEPROM, EUSART, SSP or Enhanced CCP modules, refer to the respective peripheral section.

## 14.3.1 RA2/INT INTERRUPT

External interrupt on RA2/INT pin is edge-triggered; either rising if the INTEDG bit (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep, if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up (0004h). See Section 14.6 "Power-Down Mode (Sleep)" for details on Sleep and Figure 14-10 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL and CM2CON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

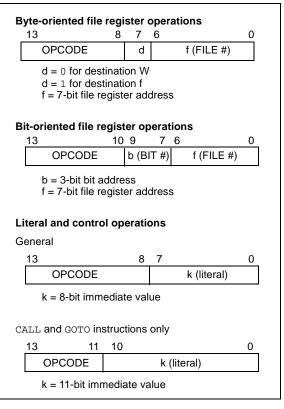

## **15.0 INSTRUCTION SET SUMMARY**

The PIC16F690 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 15-1, while the various opcode fields are summarized in Table 15-1.

Table 15-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 15.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

## TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| х     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

#### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| TABLE 17-14: | I <sup>2</sup> C <sup>™</sup> BUS DATA REQUIREMEN <sup>™</sup> | ΓS |

|--------------|----------------------------------------------------------------|----|

|--------------|----------------------------------------------------------------|----|

| Param.<br>No. | Symbol  | Characte               | eristic      | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|