Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 1.0   | Device Overview                                                           | 9   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                       | 24  |

| 3.0   | Oscillator Module (With Fail-Safe Clock Monitor)                          | 45  |

| 4.0   | I/O Ports                                                                 |     |

| 5.0   | Timer0 Module                                                             | 79  |

| 6.0   | Timer1 Module with Gate Control                                           | 82  |

| 7.0   | Timer2 Module                                                             | 89  |

| 8.0   | Comparator Module                                                         | 91  |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                  |     |

| 10.0  | Data EEPROM and Flash Program Memory Control                              | 117 |

| 11.0  | Enhanced Capture/Compare/PWM Module                                       | 125 |

| 12.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 148 |

| 13.0  | SSP Module Overview                                                       | 175 |

| 14.0  | Special Features of the CPU                                               | 193 |

| 15.0  | Instruction Set Summary                                                   | 212 |

| 16.0  | Development Support                                                       |     |

| 17.0  | Electrical Specifications                                                 |     |

| 18.0  | DC and AC Characteristics Graphs and Tables                               | 258 |

| 19.0  | Packaging Information                                                     | 285 |

| The M | Vicrochip Web Site                                                        | 295 |

|       | omer Change Notification Service                                          |     |

| Custo | omer Support                                                              | 295 |

| Produ | uct Identification System                                                 | 296 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Name                                                                     | Function | Input<br>Type | Output<br>Type | Description          |  |  |  |  |

|--------------------------------------------------------------------------|----------|---------------|----------------|----------------------|--|--|--|--|

| RC6                                                                      | RC6      | ST            | CMOS           | General purpose I/O. |  |  |  |  |

| RC7                                                                      | RC7      | ST            | CMOS           | General purpose I/O. |  |  |  |  |

| Vss                                                                      | Vss      | Power         | _              | Ground reference.    |  |  |  |  |

| VDD                                                                      | Vdd      | Power         | _              | Positive supply.     |  |  |  |  |

| Legend: AN = Analog input or output CMOS=CMOS compatible input or output |          |               |                |                      |  |  |  |  |

#### TABLE 1-1: PINOUT DESCRIPTION – PIC16F631 (CONTINUED)

TTL = TTL compatible input

HV = High Voltage

ST= Schmitt Trigger input with CMOS levels XTAL= Crystal

| Addr | Name                  | Bit 7                 | Bit 6                  | Bit 5         | Bit 4        | Bit 3               | Bit 2               | Bit 1          | Bit 0                | Value on<br>POR, BOR | Page    |  |  |  |

|------|-----------------------|-----------------------|------------------------|---------------|--------------|---------------------|---------------------|----------------|----------------------|----------------------|---------|--|--|--|

| Bank | 2                     |                       |                        |               |              | •                   | •                   |                | •                    |                      |         |  |  |  |

| 100h | INDF                  | Addressing t          | this location          | uses conten   | ts of FSR to | address data        | memory (no          | t a physical i | register)            | xxxx xxxx            | 43,200  |  |  |  |

| 101h | TMR0                  | Timer0 Modu           | Timer0 Module Register |               |              |                     |                     |                |                      |                      |         |  |  |  |

| 102h | PCL                   | Program Co            | 0000 0000              | 43,200        |              |                     |                     |                |                      |                      |         |  |  |  |

| 103h | STATUS                | IRP                   | RP1                    | RP0           | TO           | PD                  | Z                   | DC             | С                    | 0001 1xxx            | 35,200  |  |  |  |

| 104h | FSR                   | Indirect Data         | Memory Ac              | Idress Pointe | er           |                     | •                   |                | •                    | xxxx xxxx            | 43,200  |  |  |  |

| 105h | PORTA <sup>(4)</sup>  | _                     | _                      | RA5           | RA4          | RA3                 | RA2                 | RA1            | RA0                  | xx xxxx              | 57,200  |  |  |  |

| 106h | PORTB <sup>(4)</sup>  | RB7                   | RB6                    | RB5           | RB4          | _                   | _                   | -              | _                    | xxxx                 | 67,200  |  |  |  |

| 107h | PORTC <sup>(4)</sup>  | RC7                   | RC6                    | RC5           | RC4          | RC3                 | RC2                 | RC1            | RC0                  | xxxx xxxx            | 74,200  |  |  |  |

| 108h | —                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | _                    | _       |  |  |  |

| 109h | _                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | _                    | _       |  |  |  |

| 10Ah | PCLATH                | _                     | _                      | _             | Write Bu     | ffer for the up     | oper 5 bits of      | the Program    | Counter              | 0 0000               | 43,200  |  |  |  |

| 10Bh | INTCON                | GIE                   | PEIE                   | TOIE          | INTE         | RABIE               | TOIF                | INTF           | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |  |  |  |

| 10Ch | EEDAT                 | EEDAT7                | EEDAT6                 | EEDAT5        | EEDAT4       | EEDAT3              | EEDAT2              | EEDAT1         | EEDAT0               | 0000 0000            | 118,201 |  |  |  |

| 10Dh | EEADR                 | EEADR7 <sup>(3)</sup> | EEADR6                 | EEADR5        | EEADR4       | EEADR3              | EEADR2              | EEADR1         | EEADR0               | 0000 0000            | 118,201 |  |  |  |

| 10Eh | EEDATH <sup>(2)</sup> | _                     | _                      | EEDATH5       | EEDATH4      | EEDATH3             | EEDATH2             | EEDATH1        | EEDATH0              | 00 0000              | 118,201 |  |  |  |

| 10Fh | EEADRH <sup>(2)</sup> | _                     | _                      | _             | _            | EEADRH3             | EEADRH2             | EEADRH1        | EEADRH0              | 0000                 | 118,201 |  |  |  |

| 110h | _                     | Unimplemen            | ted                    |               |              |                     |                     |                |                      | _                    | _       |  |  |  |

| 111h |                       | Unimplemen            | ited                   |               |              |                     |                     |                |                      | _                    | _       |  |  |  |

| 112h | —                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | —                    | —       |  |  |  |

| 113h | —                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | —                    | —       |  |  |  |

| 114h | _                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      |                      |         |  |  |  |

| 115h | WPUB                  | WPUB7                 | WPUB6                  | WPUB5         | WPUB4        | —                   | _                   | —              | —                    | 1111                 | 68,201  |  |  |  |

| 116h | IOCB                  | IOCB7                 | IOCB6                  | IOCB5         | IOCB4        | —                   | —                   | —              | —                    | 0000                 | 68,201  |  |  |  |

| 117h | —                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | —                    | _       |  |  |  |

| 118h | VRCON                 | C1VREN                | C2VREN                 | VRR           | VP6EN        | VR3                 | VR2                 | VR1            | VR0                  | 0000 0000            | 103,201 |  |  |  |

| 119h | CM1CON0               | C10N                  | C1OUT                  | C1OE          | C1POL        | _                   | C1R                 | C1CH1          | C1CH0                | 0000 -000            | 96,201  |  |  |  |

| 11Ah | CM2CON0               | C2ON                  | C2OUT                  | C2OE          | C2POL        | _                   | C2R                 | C2CH1          | C2CH0                | 0000 -000            | 97,201  |  |  |  |

| 11Bh | CM2CON1               | MC1OUT                | MC2OUT                 | _             | _            | _                   |                     | T1GSS          | C2SYNC               | 0010                 | 99,201  |  |  |  |

| 11Ch | —                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | —                    | _       |  |  |  |

| 11Dh | _                     | Unimplemen            | ited                   |               |              |                     |                     |                |                      | —                    | _       |  |  |  |

| 11Eh | ANSEL                 | ANS7                  | ANS6                   | ANS5          | ANS4         | ANS3 <sup>(3)</sup> | ANS2 <sup>(3)</sup> | ANS1           | ANS0                 | 1111 1111            | 59,201  |  |  |  |

| 11Fh | ANSELH(3)             | _                     | —                      | —             | —            | ANS11               | ANS10               | ANS9           | ANS8                 | 1111                 | 113,201 |  |  |  |

#### TABLE 2-3: PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, g = value depends on condition, shaded = unimplemented Note 1: MCLR and WDT Reset does not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the mismatch exists.

**2:** PIC16F685/PIC16F689/PIC16F690 only.

3: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

4: Port pins with analog functions controlled by the ANSEL and ANSELH registers will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets).

### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 9.2.6 "A/D Conversion   |

|       | Procedure".                              |

#### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete Analog-to-Digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

| Note: | A device Reset forces all registers to their         |

|-------|------------------------------------------------------|

|       | Reset state. Thus, the ADC module is                 |

|       | turned off and any pending conversion is terminated. |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

An ECCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

#### See Section 11.0 "Enhanced Capture/Compare/ PWM Module" for more information.

#### 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: See Section 9.3 "A/D Acquisition Requirements".

### 10.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

Data EEPROM memory is readable and writable and the Flash program memory (PIC16F685/PIC16F689/ PIC16F690 only) is readable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDAT

- EEDATH (PIC16F685/PIC16F689/PIC16F690 only)

- EEADR

- EEADRH (PIC16F685/PIC16F689/PIC16F690 only)

When interfacing the data memory block, EEDAT holds the 8-bit data for read/write, and EEADR holds the address of the EEDAT location being accessed. These devices, except for the PIC16F631, have 256 bytes of data EEPROM with an address range from 0h to 0FFh. The PIC16F631 has 128 bytes of data EEPROM with an address range from 0h to 07Fh.

When accessing the program memory block of the PIC16F685/PIC16F689/PIC16F690 devices, the EEDAT and EEDATH registers form a 2-byte word that holds the 14-bit data for read/write, and the EEADR and EEADRH registers form a 2-byte word that holds the 12-bit address of the EEPROM location being read. These devices (PIC16F685/PIC16F689/PIC16F690) have 4K words of program EEPROM with an address range from 0h to 0FFFh. The program memory allows one-word reads.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory and read the program memory. When code-protected, the device programmer can no longer access data or program memory.

#### 10.1 EEADR and EEADRH Registers

The EEADR and EEADRH registers can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 4K words of program EEPROM.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register. When selecting a data address value, only the LSB of the address is written to the EEADR register.

#### 10.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD (PIC16F685/PIC16F689/PIC16F690) determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory. Program memory can only be read.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to data EEPROM. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

#### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output driver by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- Set the PWM duty cycle by loading the CCPR1L register and DC1B<1:0> bits of the CCP1CON register.

- 5. Configure and start Timer2:

- •Clear the TMR2IF interrupt flag bit of the PIR1 register.

•Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

•Enable Timer2 by setting the TMR2ON bit of the T2CON register.

6. Enable PWM output after a new PWM cycle has started:

•Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

• Enable the CCP1 pin output driver by clearing the associated TRIS bit.

#### 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to ten bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-4 shows the pin assignments for each Enhanced PWM mode.

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

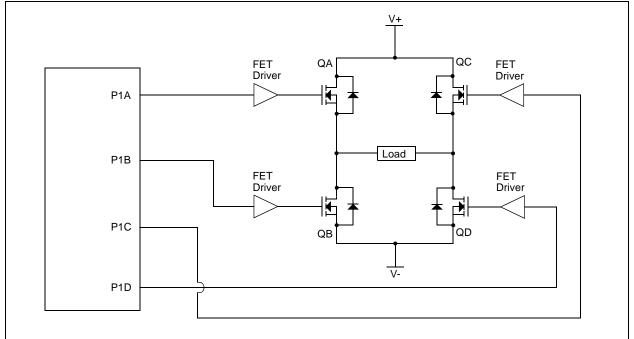

#### 11.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 11-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 11-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 11-11.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

#### FIGURE 11-10: EXAMPLE OF FULL-BRIDGE APPLICATION

#### 12.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 12-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 12.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the RX/DT I/O pin as an input. If the RX/DT pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

| Note: | When the SPEN bit is set the TX/CK I/O         |  |  |  |  |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|--|--|--|--|

|       | pin is automatically configured as an          |  |  |  |  |  |  |  |  |

|       | output, regardless of the state of the         |  |  |  |  |  |  |  |  |

|       | corresponding TRIS bit and whether or          |  |  |  |  |  |  |  |  |

|       | not the EUSART transmitter is enabled.         |  |  |  |  |  |  |  |  |

|       | The PORT latch is disconnected from the        |  |  |  |  |  |  |  |  |

|       | output driver so it is not possible to use the |  |  |  |  |  |  |  |  |

|       | TX/CK pin as a general purpose output.         |  |  |  |  |  |  |  |  |

#### 12.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 12.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | characters will be received until the overrun |  |  |  |  |  |  |  |  |  |

|       | condition is cleared. See Section 12.1.2.5    |  |  |  |  |  |  |  |  |  |

|       | "Receive Overrun Error" for more              |  |  |  |  |  |  |  |  |  |

|       | information on overrun errors.                |  |  |  |  |  |  |  |  |  |

#### 12.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

|        |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |            |                             |                |            |                             |                  |            |                             |  |  |  |

|--------|-------------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 20.000 MHz |                               |                             | Fosc           | ; = 18.43  | 2 MHz                       | Fosc           | = 11.059   | 92 MHz                      | Fosc = 8.000 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | _                 |                               | _                           |                | _          | _                           | _              | _          | _                           | _                | _          | _                           |  |  |  |

| 1200   | 1221              | 1.73                          | 255                         | 1200           | 0.00       | 239                         | 1200           | 0.00       | 143                         | 1202             | 0.16       | 103                         |  |  |  |

| 2400   | 2404              | 0.16                          | 129                         | 2400           | 0.00       | 119                         | 2400           | 0.00       | 71                          | 2404             | 0.16       | 51                          |  |  |  |

| 9600   | 9470              | -1.36                         | 32                          | 9600           | 0.00       | 29                          | 9600           | 0.00       | 17                          | 9615             | 0.16       | 12                          |  |  |  |

| 10417  | 10417             | 0.00                          | 29                          | 10286          | -1.26      | 27                          | 10165          | -2.42      | 16                          | 10417            | 0.00       | 11                          |  |  |  |

| 19.2k  | 19.53k            | 1.73                          | 15                          | 19.20k         | 0.00       | 14                          | 19.20k         | 0.00       | 8                           | _                | _          | _                           |  |  |  |

| 57.6k  | —                 | —                             | _                           | 57.60k         | 0.00       | 7                           | 57.60k         | 0.00       | 2                           | —                | —          | —                           |  |  |  |

| 115.2k | —                 |                               | _                           | —              | _          | _                           | _              |            | _                           | _                | _          | _                           |  |  |  |

#### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |                   |                             |                |                  |                             |                |                  |                             |  |  |  |

|--------|------------------|-------------------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|------------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 4.000 MHz |                               |                             | Fosc           | Fosc = 3.6864 MHz |                             |                | Fosc = 2.000 MHz |                             |                | Fosc = 1.000 MHz |                             |  |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | 300              | 0.16                          | 207                         | 300            | 0.00              | 191                         | 300            | 0.16             | 103                         | 300            | 0.16             | 51                          |  |  |  |

| 1200   | 1202             | 0.16                          | 51                          | 1200           | 0.00              | 47                          | 1202           | 0.16             | 25                          | 1202           | 0.16             | 12                          |  |  |  |

| 2400   | 2404             | 0.16                          | 25                          | 2400           | 0.00              | 23                          | 2404           | 0.16             | 12                          | —              | —                | _                           |  |  |  |

| 9600   | —                | _                             | —                           | 9600           | 0.00              | 5                           | _              | _                | _                           | —              | _                | _                           |  |  |  |

| 10417  | 10417            | 0.00                          | 5                           | —              | _                 | _                           | 10417          | 0.00             | 2                           | —              | —                | _                           |  |  |  |

| 19.2k  | —                | _                             | _                           | 19.20k         | 0.00              | 2                           | —              | _                | _                           | _              | _                | _                           |  |  |  |

| 57.6k  | —                | —                             | —                           | 57.60k         | 0.00              | 0                           | —              | _                | —                           | —              | —                | —                           |  |  |  |

| 115.2k | —                | _                             | _                           | _              | _                 | —                           | _              | _                | _                           | —              | _                | —                           |  |  |  |

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                   |            |                             |                |            |                             |                  |            |                             |  |  |  |

|--------|-------------------|-------------------------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 20.000 MHz |                               |                             | Fosc = 18.432 MHz |            |                             | Fosc           | = 11.059   | 92 MHz                      | Fosc = 8.000 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | —                 |                               | _                           |                   |            | _                           | _              | —          | —                           | _                | —          |                             |  |  |  |

| 1200   | —                 | _                             | —                           | —                 | _          | —                           | —              | —          | —                           | —                | —          | —                           |  |  |  |

| 2400   | _                 | _                             | _                           | —                 | _          | _                           | —              | _          | _                           | 2404             | 0.16       | 207                         |  |  |  |

| 9600   | 9615              | 0.16                          | 129                         | 9600              | 0.00       | 119                         | 9600           | 0.00       | 71                          | 9615             | 0.16       | 51                          |  |  |  |

| 10417  | 10417             | 0.00                          | 119                         | 10378             | -0.37      | 110                         | 10473          | 0.53       | 65                          | 10417            | 0.00       | 47                          |  |  |  |

| 19.2k  | 19.23k            | 0.16                          | 64                          | 19.20k            | 0.00       | 59                          | 19.20k         | 0.00       | 35                          | 19231            | 0.16       | 25                          |  |  |  |

| 57.6k  | 56.82k            | -1.36                         | 21                          | 57.60k            | 0.00       | 19                          | 57.60k         | 0.00       | 11                          | 55556            | -3.55      | 8                           |  |  |  |

| 115.2k | 113.64k           | -1.36                         | 10                          | 115.2k            | 0.00       | 9                           | 115.2k         | 0.00       | 5                           | —                | _          | _                           |  |  |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |                   |                             |                |                    |                             |                |                  |                             |  |  |

|--------|------------------------------------------------------|------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|--------------------|-----------------------------|----------------|------------------|-----------------------------|--|--|

| BAUD   | Fosc = 20.000 MHz                                    |            |                             | Fosc           | Fosc = 18.432 MHz |                             |                | Fosc = 11.0592 MHz |                             |                | Fosc = 8.000 MHz |                             |  |  |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 300.0                                                | 0.00       | 16665                       | 300.0          | 0.00              | 15359                       | 300.0          | 0.00               | 9215                        | 300.0          | 0.00             | 6666                        |  |  |

| 1200   | 1200                                                 | -0.01      | 4166                        | 1200           | 0.00              | 3839                        | 1200           | 0.00               | 2303                        | 1200           | -0.02            | 1666                        |  |  |

| 2400   | 2400                                                 | 0.02       | 2082                        | 2400           | 0.00              | 1919                        | 2400           | 0.00               | 1151                        | 2401           | 0.04             | 832                         |  |  |

| 9600   | 9597                                                 | -0.03      | 520                         | 9600           | 0.00              | 479                         | 9600           | 0.00               | 287                         | 9615           | 0.16             | 207                         |  |  |

| 10417  | 10417                                                | 0.00       | 479                         | 10425          | 0.08              | 441                         | 10433          | 0.16               | 264                         | 10417          | 0                | 191                         |  |  |

| 19.2k  | 19.23k                                               | 0.16       | 259                         | 19.20k         | 0.00              | 239                         | 19.20k         | 0.00               | 143                         | 19.23k         | 0.16             | 103                         |  |  |

| 57.6k  | 57.47k                                               | -0.22      | 86                          | 57.60k         | 0.00              | 79                          | 57.60k         | 0.00               | 47                          | 57.14k         | -0.79            | 34                          |  |  |

| 115.2k | 116.3k                                               | 0.94       | 42                          | 115.2k         | 0.00              | 39                          | 115.2k         | 0.00               | 23                          | 117.6k         | 2.12             | 16                          |  |  |

|        |                  |            |                             | SYNC = 0          | , BRGH     | = 1, BRG16                  | = 1 or SΥ        | /NC = 1,   | BRG16 = 1                   |                  |            |                             |

|--------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 299.9            | -0.02      | 1666                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1199             | -0.08      | 416                         | 1202             | 0.16       | 207                         |

| 2400   | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         |

| 9600   | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          |

| 10417  | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 25                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | 55.56k           | -3.55      | 8                           | —                | _          | _                           |

| 115.2k | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                | _          | _                           | _                | —          | —                           |

### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

#### 12.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCTL register starts the auto-baud calibration sequence (Figure 12-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 12-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRG register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRG register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 12-6. During ABD, both the SPBRGH and SPBRG registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRG registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 12.3.2 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- During the auto-baud process, the autobaud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRG register pair.

#### TABLE 12-6: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

|       |      |                   |                  |

**Note:** During the ABD sequence, SPBRG and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### FIGURE 12-6: AUTOMATIC BAUD RATE CALIBRATION

| BRG Value               | XXXXh         | 0000h |         | 001Ch              |

|-------------------------|---------------|-------|---------|--------------------|

| RX pin                  |               | Start |         | Edge #5<br>top bit |

| BRG Clock               |               | www.  |         |                    |

| ABDEN bit               | Set by User — |       |         | — Auto Cleared     |

| RCIDL                   |               |       |         |                    |

| RCIF bit<br>(Interrupt) |               |       |         |                    |

| Read<br>RCREG           |               |       |         | <u>`</u>           |

| SPBRG                   |               |       | XXh X_  | 1Ch                |

| SPBRGH                  |               |       | XXh XXh | 00h                |

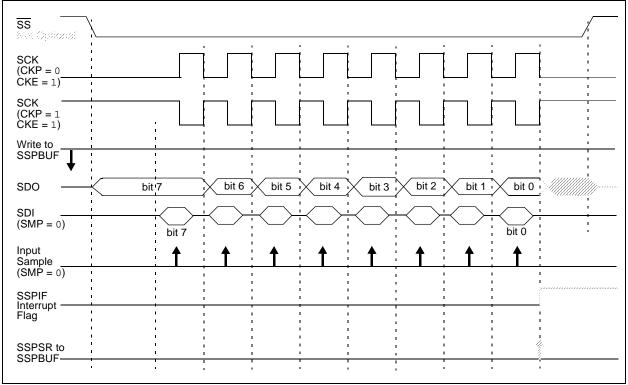

| IGURE 13-5:                                         | SPI N                           | IODE W            | /AVEFO                                         | RM (SL                                           | AVE MC      | DE WIT                                                                                            | HCKE                                  | = 0)                                  |                                       |                  |                       |

|-----------------------------------------------------|---------------------------------|-------------------|------------------------------------------------|--------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|------------------|-----------------------|

| <br>SE<br>Optional                                  | ч<br>У<br>А                     |                   |                                                |                                                  |             |                                                                                                   |                                       |                                       |                                       |                  | anna.<br>A            |

| SCA<br>ACKP = 0                                     | 1<br>5<br>7<br>7                |                   |                                                |                                                  |             |                                                                                                   |                                       |                                       |                                       |                  | 2<br>2<br>2<br>4      |

| (3148) == 63<br>860X<br>(6149) == 63<br>(7KB == 63) | <pre> {    </pre>               |                   | · · · · · · · · · · · · · · · · · · ·          | · · · · · · · · · · · · · · · · · · ·            |             |                                                                                                   | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |                                       |                  | (<br>(<br>(<br>(<br>( |

| Virito to<br>SSPELP                                 |                                 | ç                 | z                                              | zerren er en | ;X          | ()<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{<br>{ | zanana<br>2<br>2<br>2<br>2<br>2       | 3,,                                   | ;<br>;<br>;<br>;                      | ;<br>;<br>;<br>; | 5<br>6<br>5<br>7      |

| 80X)                                                |                                 | 80. <u>198</u> 7. | X 23.6                                         | ,<br>X_ 38.5<br>,                                | K 1998 A    | X in i                                                                                            | ;<br>,                                |                                       |                                       |                  |                       |

| 9355<br>(SNAP = 0)                                  | 5<br>5<br>7<br>7<br>7           |                   | •<br>••••]]]]]]]]]]<br>•<br>•                  | ,                                                | ,           |                                                                                                   | ,                                     |                                       |                                       | ////p<br>5_0     | )<br>,<br>,<br>,      |

| норыя<br>Sompte<br>(SIASP = 0)                      | 4<br>5<br>5<br>5<br>7<br>7<br>7 |                   | · //.<br>· · · · · · · · · · · · · · · · · · · |                                                  |             |                                                                                                   | , &<br>,                              |                                       | · · · · · · · · · · · · · · · · · · · | Ø.               |                       |

| SSP#<br>Pasesunt<br>Plag                            | 2<br>2<br>4<br>5                | <<br><<br><       | ><br><<br><<br>/                               | ><br>><br>><br>>                                 | ;<br>;<br>; | 2<br>6<br>6                                                                                       | 2<br>2<br>2<br>2<br>2                 | 5<br>5<br>7<br>7                      | ;<br>;<br>;                           |                  |                       |

| 982998-85<br>8829907                                | 5<br>5<br>5<br>5                | 2<br>2<br>2<br>2  | c<br>s<br>s<br>c                               | e<br>6<br>6                                      |             | 5<br>2<br>2                                                                                       | c<br>s<br>s                           | <<br><<br>>                           | · /                                   | }                | ·····                 |

#### **FIGURE 13-6:** SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### TABLE 17-2: OSCILLATOR PARAMETERS

|              | <b>Operating</b><br>Temperatu | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$  |                    |      |      |      |       |                                                                                                                                                                                 |

|--------------|-------------------------------|--------------------------------------------------------|--------------------|------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym.                          | Characteristic                                         | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                                                                                                                      |

| OS06         | TWARM                         | Internal Oscillator Switch when running <sup>(3)</sup> | —                  |      |      | 2    | Tosc  | Slowest clock                                                                                                                                                                   |

| OS07         | Tsc                           | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | —                  | _    | 21   | -    | ms    | LFINTOSC/64                                                                                                                                                                     |

| OS08         | HFosc                         | Internal Calibrated                                    | ±1%                | 7.92 | 8.0  | 8.08 | MHz   | VDD = 3.5V, 25°C                                                                                                                                                                |

|              |                               | HFINTOSC Frequency <sup>(2)</sup>                      | ±2%                | 7.84 | 8.0  | 8.16 | MHz   | $2.5V \le VDD \le 5.5V$ ,<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                                                                                               |

|              |                               |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz   | $ \begin{array}{l} 2.0V \leq V D D \leq 5.5V, \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (Ind.)}, \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (Ext.)} \end{array} $ |

| OS09*        | LFosc                         | Internal Uncalibrated<br>LFINTOSC Frequency            | —                  | 15   | 31   | 45   | kHz   |                                                                                                                                                                                 |

| OS10*        | TIOSC ST                      | HFINTOSC Oscillator                                    | _                  | 5.5  | 12   | 24   | μs    | VDD = 2.0V, -40°C to +85°C                                                                                                                                                      |

|              |                               | Wake-up from Sleep                                     | —                  | 3.5  | 7    | 14   | μs    | VDD = 3.0V, -40°C to +85°C                                                                                                                                                      |

|              |                               | Start-up Time                                          | —                  | 3    | 6    | 11   | μs    | VDD = 5.0V, -40°C to +85°C                                                                                                                                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at 'min' values with an external clock applied to the OSC1 pin. When an external clock input is used, the 'max' cycle time limit is 'DC' (no clock) for all devices.

2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 µF and 0.01 µF values in parallel are recommended.

3: By design.

| TABLE 17-14: | I <sup>2</sup> C <sup>™</sup> BUS DATA REQUIRE | EMENTS |

|--------------|------------------------------------------------|--------|

|--------------|------------------------------------------------|--------|

| Param.<br>No. | Symbol  | Characte               | eristic      | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*          | Тнідн   | Clock high time        | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 0.6        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5TCY     | _    |       |                                             |

| 101*          | TLOW    | Clock low time         | 100 kHz mode | 4.7        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                        | 400 kHz mode | 1.3        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                        | SSP Module   | 1.5TCY     | _    |       |                                             |

| 102*          | TR      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |

|               |         | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 103*          | TF      | SDA and SCL fall       | 100 kHz mode | —          | 300  | ns    |                                             |

|               |         | time                   | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| 90*           | TSU:STA | Start condition        | 100 kHz mode | 4.7        |      | μS    | Only relevant for                           |

|               |         | setup time             | 400 kHz mode | 0.6        |      | μS    | Repeated Start condition                    |

| 91*           | THD:STA | Start condition hold   | 100 kHz mode | 4.0        | _    | μS    | After this period the first                 |

|               |         | time                   | 400 kHz mode | 0.6        |      | μS    | clock pulse is generated                    |

| 106*          | THD:DAT | Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                             |

|               |         |                        | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| 107*          | TSU:DAT | Data input setup       | 100 kHz mode | 250        | —    | ns    | (Note 2)                                    |

|               |         | time                   | 400 kHz mode | 100        | _    | ns    |                                             |

| 92*           | TSU:STO | Stop condition         | 100 kHz mode | 4.7        | _    | μS    |                                             |

|               |         | setup time             | 400 kHz mode | 0.6        | —    | μS    |                                             |

| 109*          | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                  | 400 kHz mode | —          | —    | ns    |                                             |

| 110*          | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μS    | Time the bus must be free                   |

|               |         |                        | 400 kHz mode | 1.3        | _    | μS    | before a new transmission<br>can start      |

|               | Св      | Bus capacitive loading | ng           | —          | 400  | pF    |                                             |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TsU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

## TABLE 17-18:ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V,<br/>VREF $\geq$ 2.5V)

| ADC Clock F      | Period (TAD)                         | Device Frequency (Fosc) |               |               |         |  |  |  |

|------------------|--------------------------------------|-------------------------|---------------|---------------|---------|--|--|--|

| ADC Clock Source | C Clock Source ADCS<2:0> 20 MHz 8 MI |                         | 8 MHz         | 4 MHz         | 1 MHz   |  |  |  |

| Fosc/2           | 000                                  | 100 ns                  | 250 ns        | 500 ns        | 2.0 μs  |  |  |  |

| Fosc/4           | 100                                  | 200 ns                  | 500 ns        | 1.0 μs        | 4.0 μs  |  |  |  |

| Fosc/8           | 001                                  | 400 ns                  | 1.0 μs        | 2.0 μs        | 8.0 μs  |  |  |  |

| Fosc/16          | 101                                  | 800 ns                  | 2.0 μs        | 4.0 μs        | 16.0 μs |  |  |  |

| Fosc/32          | 010                                  | 1.6 μs                  | 4.0 μs        | 8.0 μs        | 32.0 μs |  |  |  |

| Fosc/64          | 110                                  | 3.2 μs                  | 8.0 μs        | 16.0 μs       | 64.0 μs |  |  |  |

| Frc              | x11                                  | 2-6 μs                  | <b>2-6</b> μs | <b>2-6</b> μs | 2-6 μs  |  |  |  |

Legend: Shaded cells should not be used for conversions at temperatures above +125°C.

**Note 1:** TAD must be between 1.6  $\mu$ s and 4.0  $\mu$ s.

| Param<br>No. | Sym.   | Characteristic                                 | Frequency<br>Tolerance | Min. | Тур. | Max. | Units | Conditions                                                                                                                       |

|--------------|--------|------------------------------------------------|------------------------|------|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| OS08         | INTosc | Int. Calibrated INTOSC<br>Freq. <sup>(1)</sup> | ±7.5%                  | 7.4  | 8.0  | 8.6  | MHz   | $\begin{array}{l} 2.1V \leq V \text{DD} \leq 5.5V \\ \text{-40}^\circ\text{C} \leq \text{TA} \leq 150^\circ\text{C} \end{array}$ |

#### TABLE 17-23: OSCILLATOR PARAMETERS FOR PIC16F685/687/689/690-H (High Temp.)

**Note 1:** To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

#### TABLE 17-24: WATCHDOG TIMER SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic                                   | Min. | Тур. | Max. | Units | Conditions        |

|--------------|------|--------------------------------------------------|------|------|------|-------|-------------------|

| 31           |      | Watchdog Timer Time-out Period<br>(No Prescaler) | 10   | 20   | 70   | ms    | 150°C Temperature |

#### TABLE 17-25: BROWN-OUT RESET SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic          | Min. | Тур. | Max. | Units | Conditions        |

|--------------|------|-------------------------|------|------|------|-------|-------------------|

| 35           | VBOR | Brown-Out Reset Voltage | 2.0  | _    | 2.3  | V     | 150°C Temperature |

#### TABLE 17-26: COMPARATOR SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic       | Min. | Тур. | Max. | Units | Conditions    |

|--------------|------|----------------------|------|------|------|-------|---------------|

| CM01         | Vos  | Input Offset Voltage |      | ±5   | ±20  | mV    | (Vdd - 1.5)/2 |

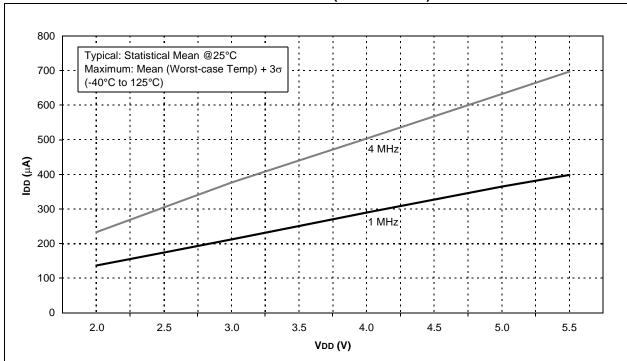

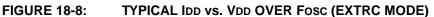

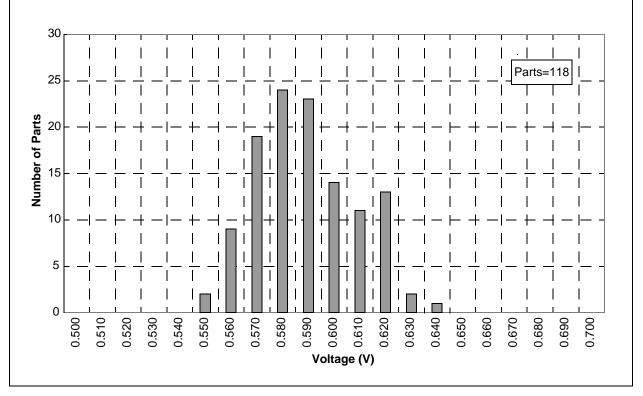

FIGURE 18-9: MAXIMUM IDD vs. VDD OVER Fosc (EXTRC MODE)

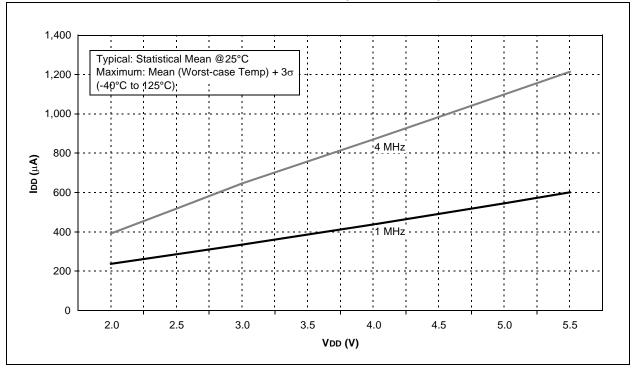

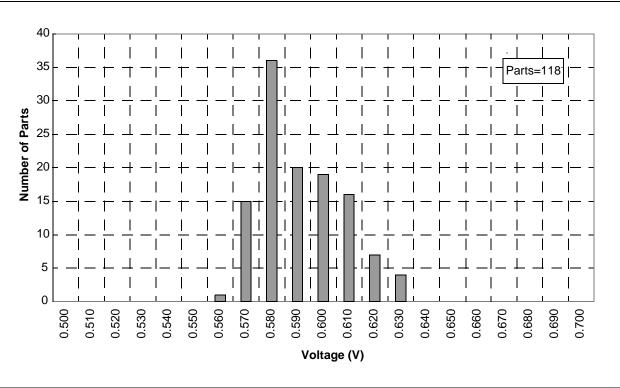

FIGURE 18-48: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (3V, 125°C)

#### 19.2 Package Details

The following sections give the technical details of the packages.

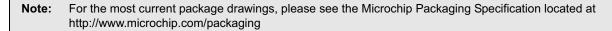

#### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

| Units                      |    | INCHES   |       |       |

|----------------------------|----|----------|-------|-------|

| Dimension Limits           |    | MIN      | NOM   | MAX   |

| Number of Pins             | Ν  | 20       |       |       |

| Pitch                      | е  | .100 BSC |       |       |

| Top to Seating Plane       | Α  | -        | -     | .210  |

| Molded Package Thickness   | A2 | .115     | .130  | .195  |

| Base to Seating Plane      | A1 | .015     | -     | -     |

| Shoulder to Shoulder Width | E  | .300     | .310  | .325  |

| Molded Package Width       | E1 | .240     | .250  | .280  |

| Overall Length             | D  | .980     | 1.030 | 1.060 |

| Tip to Seating Plane       | L  | .115     | .130  | .150  |

| Lead Thickness             | С  | .008     | .010  | .015  |

| Upper Lead Width           | b1 | .045     | .060  | .070  |

| Lower Lead Width           | b  | .014     | .018  | .022  |

| Overall Row Spacing §      | eB | -        | -     | .430  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

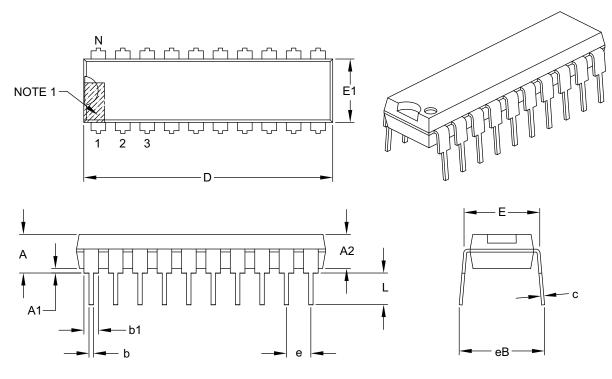

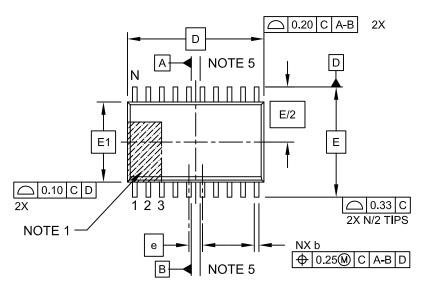

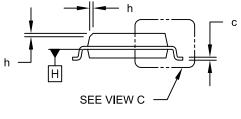

### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

Microchip Technology Drawing C04-094C Sheet 1 of 2