# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 18                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-i-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                | Function | Input<br>Type | Output<br>Type | Description                         |  |  |

|---------------------|----------|---------------|----------------|-------------------------------------|--|--|

| RC1/AN5/C12IN1-     | RC1      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | AN5      | AN            | _              | A/D Channel 5 input.                |  |  |

|                     | C12IN1-  | AN            |                | Comparator C1 or C2 negative input. |  |  |

| RC2/AN6/C12IN2-/P1D | RC2      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | AN6      | AN            | _              | A/D Channel 6 input.                |  |  |

|                     | C12IN2-  | AN            | _              | Comparator C1 or C2 negative input. |  |  |

|                     | P1D      | _             | CMOS           | PWM output.                         |  |  |

| RC3/AN7/C12IN3-/P1C | RC3      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | AN7      | AN            | _              | A/D Channel 7 input.                |  |  |

|                     | C12IN3-  | AN            |                | Comparator C1 or C2 negative input. |  |  |

|                     | P1C      | _             | CMOS           | PWM output.                         |  |  |

| RC4/C2OUT/P1B       | RC4      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | C2OUT    | _             | CMOS           | Comparator C2 output.               |  |  |

|                     | P1B      | _             | CMOS           | PWM output.                         |  |  |

| RC5/CCP1/P1A        | RC5      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | CCP1     | ST            | CMOS           | Capture/Compare input.              |  |  |

|                     | P1A      | ST            | CMOS           | PWM output.                         |  |  |

| RC6/AN8             | RC6      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | AN8      | AN            | _              | A/D Channel 8 input.                |  |  |

| RC7/AN9             | RC7      | ST            | CMOS           | General purpose I/O.                |  |  |

|                     | AN9      | AN            | _              | A/D Channel 9 input.                |  |  |

| Vss                 | Vss      | Power         | _              | Ground reference.                   |  |  |

| Vdd                 | Vdd      | Power         | —              | Positive supply.                    |  |  |

#### **TABLE 1-3: PINOUT DESCRIPTION – PIC16F685 (CONTINUED)**

HV = High Voltage

TTL = TTL compatible input ST= Schmitt Trigger input with CMOS levels XTAL= Crystal

| Description                                          |  |  |

|------------------------------------------------------|--|--|

| dividually controlled interrupt-on-<br>bled pull-up. |  |  |

|                                                      |  |  |

|                                                      |  |  |

| dividually controlled interrupt-on-<br>bled pull-up. |  |  |

| output.                                              |  |  |

| lock.                                                |  |  |

|                                                      |  |  |

|                                                      |  |  |

| input.                                               |  |  |

|                                                      |  |  |

|                                                      |  |  |

| egative input.                                       |  |  |

|                                                      |  |  |

|                                                      |  |  |

| egative input.                                       |  |  |

|                                                      |  |  |

| A/D Channel 7 input.                                 |  |  |

| egative input.                                       |  |  |

| General purpose I/O.                                 |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

| c                                                    |  |  |

#### **TABLE 1-4:** PINOUT DESCRIPTION - PIC16F687/PIC16F689 (CONTINUED)

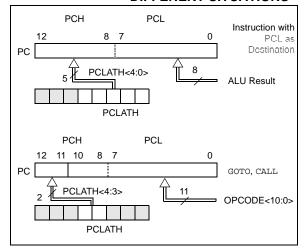

### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-9 shows the two situations for the loading of the PC. The upper example in Figure 2-9 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-9 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-9: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper five bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower eight bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 2.3.2 STACK

The PIC16F631/677/685/687/689/690 devices have an 8-level x 13-bit wide hardware stack (see Figures 2-2 and 2-3). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| Note 1: | There are no Status bits to indicate stack overflow or stack underflow conditions.                                                                                                                   |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2:      | There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address. |  |  |  |  |  |  |

|         |                                                                                                                                                                                                      |  |  |  |  |  |  |

#### 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-10.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

|        | MOVLW    | 0x20  | ;initialize pointer  |  |  |

|--------|----------|-------|----------------------|--|--|

|        | MOVWF    | FSR   | ;to RAM              |  |  |

| NEXT   | CLRF     | INDF  | ;clear INDF register |  |  |

|        | INCF     | FSR   | ;inc pointer         |  |  |

|        | BTFSS    | FSR,4 | ;all done?           |  |  |

|        | GOTO     | NEXT  | ;no clear next       |  |  |

| CONTIN | CONTINUE |       | ;yes continue        |  |  |

|        |          | NEXT  |                      |  |  |

#### 3.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 3-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

#### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0 | R/W-0 |

|---------|-------|-------|-------|---------------------|-----|-----|-------|

| —       | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7   |       |       |       |                     |     |     | bit 0 |

|         |       |       |       |                     |     |     |       |

| Legend: |       |       |       |                     |     |     |       |

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits<br>111 = 8 MHz<br>110 = 4 MHz (default)<br>101 = 2 MHz<br>100 = 1 MHz<br>011 = 500 kHz<br>010 = 250 kHz<br>001 = 125 kHz<br>000 = 31 kHz (LFINTOSC)                             |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup><br>1 = Device is running from the clock defined by FOSC<2:0> of the CONFIG register<br>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC) |

| bit 2   | <ul> <li>HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)</li> <li>1 = HFINTOSC is stable</li> <li>0 = HFINTOSC is not stable</li> </ul>                                                                                 |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)<br>1 = LFINTOSC is stable<br>0 = LFINTOSC is not stable                                                                                                                            |

| bit 0   | <ul> <li>SCS: System Clock Select bit</li> <li>1 = Internal oscillator is used for system clock</li> <li>0 = Clock source defined by FOSC&lt;2:0&gt; of the CONFIG register</li> </ul>                                               |

| Note 1. | Discrete to (o) with Two Greed Oters up and LD VT or LIC collected on the Opeillater mode on Feil                                                                                                                                    |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

## PIC16F631/677/685/687/689/690

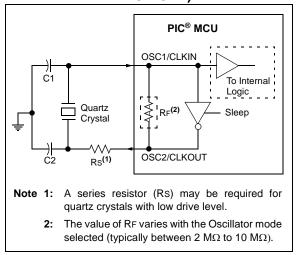

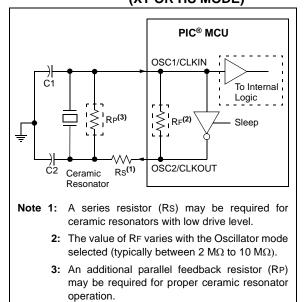

#### 3.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

- **Note 1:** Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

### FIGURE 3-3: QUARTZ CRYSTAL

#### OPERATION (LP, XT OR HS MODE)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

#### 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | of the OSCCON register are set to '110'  |  |  |  |  |  |  |  |  |

|       | and the frequency selection is set to    |  |  |  |  |  |  |  |  |

|       | 4 MHz. The user can modify the IRCF bits |  |  |  |  |  |  |  |  |

|       | to select a different frequency.         |  |  |  |  |  |  |  |  |

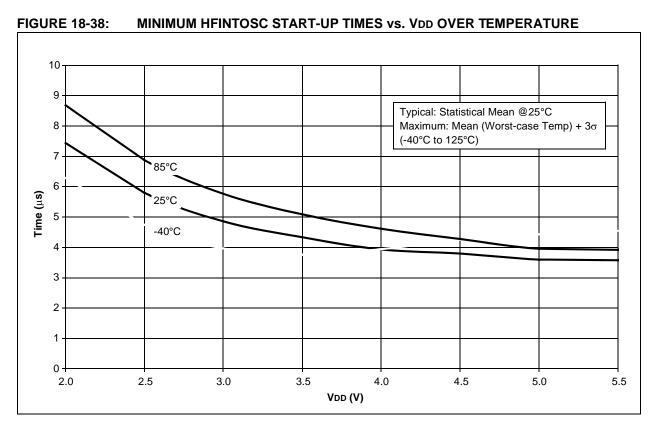

#### 3.5.5 HFINTOSC AND LFINTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the oscillator tables of **Section 17.0** "**Electrical Specifications**".

# PIC16F631/677/685/687/689/690

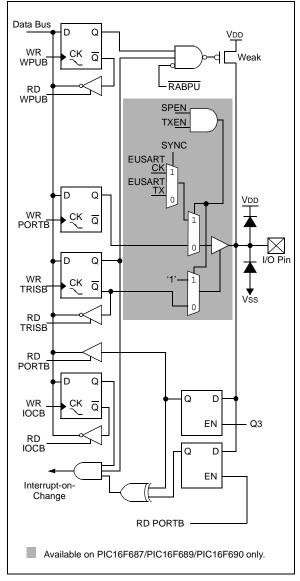

#### 4.4.3.4 RB7/TX/CK

Figure 4-10 shows the diagram for this pin. The RB7/  $TX/CK^{(1)}$  pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

Note 1: TX and CK are available on PIC16F687/ PIC16F689/PIC16F690 only.

#### FIGURE 4-10: BLOCK DIAGRAM OF RB7

| R/W-0         | R-0                                                              | R/W-0                                                                                                        | R/W-0                                    | U-0              | R/W-0            | R/W-0            | R/W-0    |  |  |

|---------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|------------------|----------|--|--|

| C2ON          | C2OUT                                                            | C2OE                                                                                                         | C2POL                                    | —                | C2R              | C2CH1            | C2CH0    |  |  |

| bit 7         |                                                                  |                                                                                                              |                                          |                  |                  |                  | bit 0    |  |  |

| Legend:       |                                                                  |                                                                                                              |                                          |                  |                  |                  |          |  |  |

| R = Readabl   | e bit                                                            | W = Writable                                                                                                 | bit                                      | U = Unimple      | emented bit, rea | ad as '0'        |          |  |  |

| -n = Value at | POR                                                              | '1' = Bit is set                                                                                             | t                                        | '0' = Bit is cl  | eared            | x = Bit is unk   | nown     |  |  |

| bit 7         | C2ON: Com                                                        | parator C2 Ena                                                                                               | ble bit                                  |                  |                  |                  |          |  |  |

|               | 1 = Compara                                                      | ator C2 is enabl<br>ator C2 is disab                                                                         | ed                                       |                  |                  |                  |          |  |  |

| bit 6         | C2OUT: Com                                                       | nparator C2 Ou                                                                                               | tput bit                                 |                  |                  |                  |          |  |  |

|               | C2OUT = 0 v<br>C2OUT = 1 v<br><u>If C2POL = 0</u><br>C2OUT = 1 v | <u>_ (inverted pola</u><br>when C2VIN+ ><br>when C2VIN+ <<br>(non-inverted<br>when C2VIN+ ><br>when C2VIN+ < | C2VIN-<br>C2VIN-<br>polarity):<br>C2VIN- |                  |                  |                  |          |  |  |

| bit 5         | C2OE: Comparator C2 Output Enable bit                            |                                                                                                              |                                          |                  |                  |                  |          |  |  |

|               |                                                                  | s present on C<br>s internal only                                                                            | 20UT pin <sup>(1)</sup>                  |                  |                  |                  |          |  |  |

| bit 4         | C1POL: Comparator C1 Output Polarity Select bit                  |                                                                                                              |                                          |                  |                  |                  |          |  |  |

|               |                                                                  | ogic is inverted<br>ogic is not inve                                                                         |                                          |                  |                  |                  |          |  |  |

| bit 3         | Unimplemer                                                       | nted: Read as '                                                                                              | 0'                                       |                  |                  |                  |          |  |  |

| bit 2         | C2R: Compa                                                       | arator C2 Refer                                                                                              | ence Select bi                           | ts (non-invertii | ng input)        |                  |          |  |  |

|               |                                                                  | connects to C2<br>connects to C2                                                                             |                                          |                  |                  |                  |          |  |  |

| bit 1-0       | C2CH<1:0>: Comparator C2 Channel Select bits                     |                                                                                                              |                                          |                  |                  |                  |          |  |  |

|               | 01 = C2VIN-<br>10 = C2VIN-                                       | of C2 connects<br>of C2 connects<br>of C2 connects<br>of C2 connects                                         | to C12IN1- pi<br>to C12IN2- pi           | n<br>n           |                  |                  |          |  |  |

|               | TT = CZVIN                                                       | ut requires the f                                                                                            |                                          |                  | 20E = 1, C20I    | N = 1 and corres | sponding |  |  |

#### REGISTER 8-2: CM2CON0: COMPARATOR C2 CONTROL REGISTER 0

PORT TRIS bit = 0.

| R/W-0         | R/W-0                                                                                  | R/W-0            | R/W-0          | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------|------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| ADFM          | VCFG                                                                                   | CHS3             | CHS2           | CHS1             | CHS0            | GO/DONE         | ADON  |  |  |  |  |

| bit 7         |                                                                                        |                  |                |                  |                 |                 | bit 0 |  |  |  |  |

|               |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |  |

| Legend:       |                                                                                        |                  |                |                  |                 |                 |       |  |  |  |  |

| R = Readabl   | e bit                                                                                  | W = Writable     | bit            | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |  |

| -n = Value at | POR                                                                                    | '1' = Bit is set |                | '0' = Bit is cle | ared            | x = Bit is unkn | own   |  |  |  |  |

| 1 2 7         |                                                                                        | о · Б            |                | 1 41.9           |                 |                 |       |  |  |  |  |

| bit 7         |                                                                                        | Conversion Res   | sult Format Se | elect bit        |                 |                 |       |  |  |  |  |

|               | 1 = Right jus<br>0 = Left justi                                                        |                  |                |                  |                 |                 |       |  |  |  |  |

| bit 6         | VCFG: Volta                                                                            | ige Reference b  | it             |                  |                 |                 |       |  |  |  |  |

|               | 1 = VREF pin                                                                           | 1                |                |                  |                 |                 |       |  |  |  |  |

|               | 0 = VDD                                                                                |                  |                |                  |                 |                 |       |  |  |  |  |

| bit 5-2       | CHS<3:0>: Analog Channel Select bits                                                   |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0000 = ANO                                                                             |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0001 = AN1                                                                             |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0010 = AN2                                                                             |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0011 = AN3                                                                             |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0100 = AN4                                                                             |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0101 = AN5                                                                             |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 0110 = AN6<br>0111 = AN7                                                               |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 111 = AN7<br>1000 = AN8                                                                |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 1000 = ANS<br>1001 = ANS                                                               |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 1010 = AN10                                                                            |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 1011 <b>= AN1</b>                                                                      | 1                |                |                  |                 |                 |       |  |  |  |  |

|               | 1100 = CVREF                                                                           |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 1101 = 0.6V Fixed Voltage Reference                                                    |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 1110 = Reserved. Do not use.                                                           |                  |                |                  |                 |                 |       |  |  |  |  |

|               | 1111 = Reserved. Do not use.                                                           |                  |                |                  |                 |                 |       |  |  |  |  |

| bit 1         | GO/DONE:                                                                               | A/D Conversion   | Status bit     |                  |                 |                 |       |  |  |  |  |

|               | 1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. |                  |                |                  |                 |                 |       |  |  |  |  |

|               | This bit is automatically cleared by hardware when the A/D conversion has completed.   |                  |                |                  |                 |                 |       |  |  |  |  |

|               | $0 = A/D \operatorname{conv}$                                                          | version complet  | ed/not in prog | ress             |                 |                 |       |  |  |  |  |

| bit 0         | ADON: ADC                                                                              | Enable bit       |                |                  |                 |                 |       |  |  |  |  |

|               | 1 = ADC is e                                                                           | enabled          |                |                  |                 |                 |       |  |  |  |  |

|               | 0 = ADC is disabled and consumes no operating current                                  |                  |                |                  |                 |                 |       |  |  |  |  |

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| P1M< | 1:0>                                                           | Signal                                                                        | 0                   | Pulse Width   |                           | PR2+1             |

|------|----------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|---------------|---------------------------|-------------------|

| 00   | (Single Output)                                                | P1A Modulated                                                                 |                     |               | – Period ————             |                   |

|      |                                                                | P1A Modulated                                                                 | <b>⊲ ►</b><br>Delay | 1)            | <br>Delay <sup>(1)</sup>  |                   |

| 10   | (Half-Bridge)                                                  | P1B Modulated                                                                 |                     |               |                           |                   |

|      |                                                                | P1A Active                                                                    |                     |               |                           |                   |

| 01   | (Full-Bridge,<br>Forward)                                      | P1B Inactive                                                                  |                     |               |                           | <br>!<br>!        |

|      | , er maraj                                                     | P1C Inactive                                                                  | <br>                |               |                           | <br><br>          |

|      |                                                                | P1D Modulated                                                                 |                     |               | [                         |                   |

|      |                                                                | P1A Inactive                                                                  |                     |               | <br> <br>                 |                   |

| 11   | (Full-Bridge,<br>Reverse)                                      | P1B Modulated                                                                 |                     |               |                           |                   |

|      |                                                                | P1C Active                                                                    |                     |               | 1<br>                     |                   |

|      |                                                                | P1D Inactive                                                                  |                     |               |                           |                   |

|      | <ul> <li>Pulse Width = To</li> <li>Delay = 4 * Toso</li> </ul> | c * (PR2 + 1) * (TMR2 Presca<br>osc * (CCPR1L<7:0>:CCP1C0<br>* (PWM1CON<6:0>) | ON<5:4>) * (T       |               |                           |                   |

| N    | ote 1: Dead-ban<br>mode").                                     | d delay is programmed usir                                                    | ng the PWM1         | 1CON register | (Section 11.4.6 "Programm | able Dead-Band De |

#### FIGURE 11-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

© 2005-2015 Microchip Technology Inc.

#### 12.3 EUSART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUDCTL register selects 16-bit mode.

The SPBRGH, SPBRG register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TXSTA register and the BRG16 bit of the BAUDCTL register. In Synchronous mode, the BRGH bit is ignored.

Table 12-3 contains the formulas for determining the baud rate. Example 12-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 12-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SPBRGH, SPBRG register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate. If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is Idle before changing the system clock.

#### EXAMPLE 12-1: CALCULATING BAUD RATE ERROR

| c    | Configuration Bits |      | Configuration Bits BRG/EUSART Mode |                   | Baud Rate Formula |  |

|------|--------------------|------|------------------------------------|-------------------|-------------------|--|

| SYNC | BRG16              | BRGH | BRG/EUSART Mode                    | Dauu Kale Formula |                   |  |

| 0    | 0                  | 0    | 8-bit/Asynchronous                 | Fosc/[64 (n+1)]   |                   |  |

| 0    | 0                  | 1    | 8-bit/Asynchronous                 |                   |                   |  |

| 0    | 1                  | 0    | 16-bit/Asynchronous                | Fosc/[16 (n+1)]   |                   |  |

| 0    | 1                  | 1    | 16-bit/Asynchronous                |                   |                   |  |

| 1    | 0                  | x    | 8-bit/Synchronous                  | Fosc/[4 (n+1)]    |                   |  |

| 1    | 1                  | x    | 16-bit/Synchronous                 |                   |                   |  |

#### TABLE 12-3: BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SPBRGH, SPBRG register pair

#### TABLE 12-4: REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF | RCIDL | —     | SCKP  | BRG16 |       | WUE   | ABDEN | 01-0 0-00            | 01-0 0-00                       |

| RCSTA   | SPEN   | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | x000 000x            | x000 000x                       |

| SPBRG   | BRG7   | BRG6  | BRG5  | BRG4  | BRG3  | BRG2  | BRG1  | BRG0  | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15  | BRG14 | BRG13 | BRG12 | BRG11 | BRG10 | BRG9  | BRG8  | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC   | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 0000 0010            | 0000 0010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for the Baud Rate Generator.

# PIC16F631/677/685/687/689/690

### REGISTER 13-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0                                                                                                                      | R-0                                                                           | R-0                                               | R-0                | R-0                | R-0                 | R-0           |

|------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------|--------------------|--------------------|---------------------|---------------|

| SMP              | CKE                                                                                                                        | D/A                                                                           | Р                                                 | S                  | R/W                | UA                  | BF            |

| bit 7            |                                                                                                                            |                                                                               |                                                   |                    |                    |                     | bit (         |

|                  |                                                                                                                            |                                                                               |                                                   |                    |                    |                     |               |

| Legend:          |                                                                                                                            |                                                                               |                                                   |                    |                    | (                   |               |

| R = Readable b   |                                                                                                                            | W = Writable bit                                                              |                                                   |                    | iented bit, read a |                     |               |

| -n = Value at PC | DR                                                                                                                         | '1' = Bit is set                                                              |                                                   | '0' = Bit is clea  | ared               | x = Bit is unkno    | wn            |

| bit 7            | SPI Master mo<br>1 = Input data =<br>0 = Input data =<br>SPI Slave mod<br>SMP must be o<br>$I^2C^{TM}$ mode:               | sampled at end of sampled at middle                                           | data output ti<br>of data outpu<br>is used in Sla | ut time (Microwire | e)                 |                     |               |

| bit 6            | SPI mode. CKI<br>1 = Data transi<br>0 = Data transi<br>SPI mode. CKI<br>1 = Data transi<br>0 = Data transi<br>$l^2C$ mode: | mitted on rising ed<br>mitted on falling ed                                   | dge of SCK<br>dge of SCK (N<br>lge of SCK         |                    |                    |                     |               |

| bit 5            | 1 = Indicates the                                                                                                          | DRESS bit (I <sup>2</sup> C m<br>nat the last byte re<br>nat the last byte re | eceived or trar                                   |                    |                    |                     |               |

| bit 4            | SSPEN is clea<br>1 = Indicates th                                                                                          | red when the SSP                                                              | been detected                                     |                    |                    | tected last.        |               |

| bit 3            | SSPEN is clea<br>1 = Indicates th                                                                                          | red when the SSP                                                              | been detected                                     |                    |                    | ected last.         |               |

| bit 2            | This bit holds th                                                                                                          | RITE bit Information<br>ne R/W bit informa<br>rt bit, Stop bit or A           | tion following                                    |                    | match. This bit is | only valid from the | address match |

| bit 1            | 1 = Indicates th                                                                                                           | ldress bit (10-bit l <sup>2</sup><br>nat the user needs<br>bes not need to be | s to update the                                   |                    | SSPADD registe     | r                   |               |

| bit 0            | 1 = Receive co<br>0 = Receive not<br>$\frac{\text{Transmit (I}^2 \text{C r})}{1 = \text{Transmit in}}$                     | and I <sup>2</sup> C modes):<br>omplete, SSPBUF<br>ot complete, SSPE          | BUF is empty<br>JF is full                        |                    |                    |                     |               |

|                  |                                                                                                                            | 689/PIC16F690 or                                                              | •                                                 |                    |                    |                     |               |

2: Does not update if receive was ignored.

#### 14.2.4 BROWN-OUT RESET (BOR)

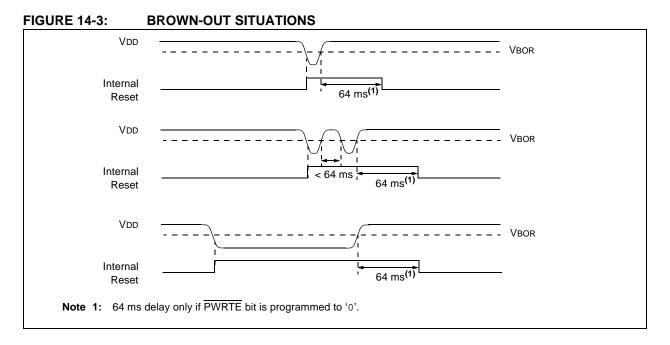

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

| Register              | Address  | Power-on Reset | MCLR Reset<br>WDT Reset (Continued)<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |  |  |

|-----------------------|----------|----------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| TRISB                 | 86h/186h | 1111           | 1111                                                                  | uuuu                                                                                  |  |  |

| TRISC                 | 87h/187h | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| PIE1                  | 8Ch      | -000 0000      | -000 0000                                                             | -uuu uuuu                                                                             |  |  |

| PIE2                  | 8Dh      | 0000           | 0000                                                                  | uuuu uuuu                                                                             |  |  |

| PCON                  | 8Eh      | 010x           | 0uuq <sup>1, 5)</sup>                                                 | uuuu                                                                                  |  |  |

| OSCCON                | 8Fh      | -110 q000      | -110 q000                                                             | -uuu uuuu                                                                             |  |  |

| OSCTUNE               | 90h      | 0 0000         | u uuuu                                                                | u uuuu                                                                                |  |  |

| PR2                   | 92h      | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| SSPADD                | 93h      | 0000 0000      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| SSPMSK <sup>(6)</sup> | 93h      |                | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| SSPSTAT               | 94h      | 0000 0000      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| WPUA                  | 95h      | 11 -111        | 11 -111                                                               | uuuu uuuu                                                                             |  |  |

| IOCA                  | 96h      | 00 0000        | 00 0000                                                               | uu uuuu                                                                               |  |  |

| WDTCON                | 97h      | 0 1000         | 0 1000                                                                | u uuuu                                                                                |  |  |

| TXSTA                 | 98h      | 0000 0010      | 0000 0010                                                             | uuuu uuuu                                                                             |  |  |

| SPBRG                 | 99h      | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| SPBRGH                | 9Ah      | 0000 0000      | 0000 0000                                                             | սսսս սսսս                                                                             |  |  |

| BAUDCTL               | 9Bh      | 01-0 0-00      | 01-0 0-00                                                             | uu-u u-uu                                                                             |  |  |

| ADRESL                | 9Eh      | xxxx xxxx      | uuuu uuuu                                                             | uuuu uuuu                                                                             |  |  |

| ADCON1                | 9Fh      | -000           | -000                                                                  | -uuu                                                                                  |  |  |

| EEDAT                 | 10Ch     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| EEADR                 | 10Dh     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| EEDATH                | 10Eh     | 00 0000        | 00 0000                                                               | uu uuuu                                                                               |  |  |

| EEADRH                | 10Fh     | 0000           | 0000                                                                  | uuuu                                                                                  |  |  |

| WPUB                  | 115h     | 1111           | 1111                                                                  | uuuu                                                                                  |  |  |

| IOCB                  | 116h     | 0000           | 0000                                                                  | uuuu                                                                                  |  |  |

| VRCON                 | 118h     | 0000 0000      | 0000 0000                                                             | uuuu uuuu                                                                             |  |  |

| CM1CON0               | 119h     | 0000 -000      | 0000 -000                                                             | uuuu -uuu                                                                             |  |  |

| CM2CON0               | 11Ah     | 0000 -000      | 0000 -000                                                             | uuuu -uuu                                                                             |  |  |

| CM2CON1               | 11Bh     | 0000           | 0010                                                                  | uuuu                                                                                  |  |  |

| ANSEL                 | 11Eh     | 1111 1111      | 1111 1111                                                             | uuuu uuuu                                                                             |  |  |

| ANSELH                | 11Fh     | 1111           | 1111                                                                  | uuuu                                                                                  |  |  |

| EECON1                | 18Ch     | x x000         | u q000                                                                | uuuu                                                                                  |  |  |

| EECON2                | 18Dh     |                |                                                                       |                                                                                       |  |  |

| PSTRCON               | 19Dh     | 0 0001         | 0 0001                                                                | u uuuu                                                                                |  |  |

| SRCON                 | 19EH     | 0000 00        | 0000 00                                                               | uuuu uu                                                                               |  |  |

#### TABLE 14-4: INITIALIZATION CONDITION FOR REGISTER (CONTINUED)

$\label{eq:logend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 14-5 for Reset value for specific condition.

**5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**6:** Accessible only when SSPM < 3:0 > = 1001.

#### TABLE 14-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

#### 14.3.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. See **Section 5.0 "Timer0 Module**" for operation of the Timer0 module.

#### 14.3.3 PORTA/PORTB INTERRUPT

An input change on PORTA or PORTB change sets the RABIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the RABIE (INTCON<3>) bit. Plus, individual pins can be configured through the IOCA or IOCB registers.

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set. See Section 4.2.3 "Interrupt-on-change" for more information.

IOC-RA0 -IOCA0 -IOC-RA1 -IOCA1 -IOC-RA2 -IOCA2 IOC-RA3 -IOCA3 -SSPIF SSPIE IOC-RA4-IOCA4-TXIF-TXIE-IOC-RA5-IOCA5 RCIF Wake-up (If in Sleep mode)(1) RCIE IOC-RB4 -TOIF -IOCB4 TOIE -TMR2IF-TMR2IE-Interrupt to CPU INTF -IOC-RB5 -INTE IOCB5 TMR1IF RABIF TMR1IE IOC-RB6 -RABIE IOCB6 C1IF C1IE-PEIE IOC-RB7 -IOCB7 C2IF GIE C2IE ADIF ADIE EEIF EEIE Note 1: Some peripherals depend upon the system OSFIF clock for operation. Since the system clock is OSFIE suspended during Sleep, these peripherals will not wake the part from Sleep. See CCP1IF Section 14.6.1 "Wake-up from Sleep". CCP1IE

#### FIGURE 14-7: INTERRUPT LOGIC

## 17.0 ELECTRICAL SPECIFICATIONS

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                            | 40° to +125°C        |

|-----------------------------------------------------------|----------------------|

| Storage temperature                                       | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                        | 0.3V to +6.5V        |

| Voltage on MCLR with respect to Vss                       | 0.3V to +13.5V       |

| Voltage on all other pins with respect to Vss             | 0.3V to (VDD + 0.3V) |

| Total power dissipation <sup>(1)</sup>                    | 800 mW               |

| Maximum current out of Vss pin                            |                      |

| Maximum current into VDD pin                              |                      |

| Input clamp current, Iικ (Vi < 0 or Vi > VDD)             | ± 20 mA              |

| Output clamp current, loк (Vo < 0 or Vo >VDD)             | ± 20 mA              |

| Maximum output current sunk by any I/O pin                | 25 mA                |

| Maximum output current sourced by any I/O pin             | 25 mA                |

| Maximum current sunk by PORTA, PORTB and PORTC (combined) | 200 mA               |

| Maximum current sourced PORTA, PORTB and PORTC (combined) | 200 mA               |

**Note 1:** Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to Vss.

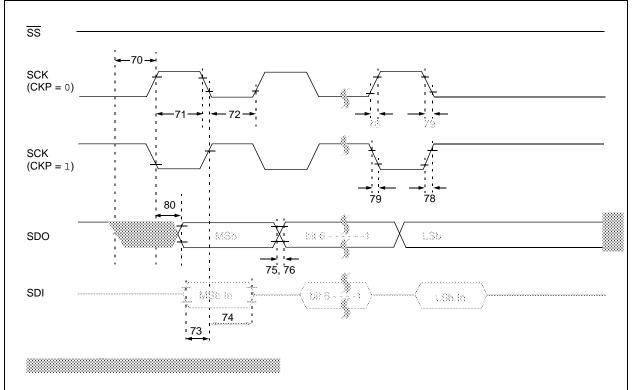

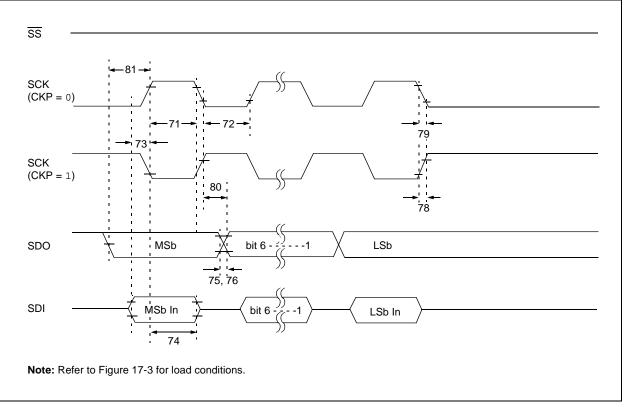

#### FIGURE 17-12: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

| TABLE 17-14: | I <sup>2</sup> C <sup>™</sup> BUS DATA REQUIREMEN <sup>™</sup> | ΓS |

|--------------|----------------------------------------------------------------|----|

|--------------|----------------------------------------------------------------|----|

| Param.<br>No. | Symbol  | Characte               | eristic                    | Min.         | Max. | Units | Conditions                                  |  |

|---------------|---------|------------------------|----------------------------|--------------|------|-------|---------------------------------------------|--|

| 100*          | Тнідн   | Clock high time        | 100 kHz mode               | 4.0          |      | μS    | Device must operate at a minimum of 1.5 MHz |  |

|               |         |                        | 400 kHz mode               | 0.6          |      | μS    | Device must operate at a minimum of 10 MHz  |  |

|               |         |                        | SSP Module                 | 1.5TCY       | _    |       |                                             |  |

| 101*          | TLOW    | Clock low time         | 100 kHz mode               | 4.7          |      | μS    | Device must operate at a minimum of 1.5 MHz |  |

|               |         |                        | 400 kHz mode               | 1.3          |      | μS    | Device must operate at a minimum of 10 MHz  |  |

|               |         |                        | SSP Module                 | 1.5TCY       | _    |       |                                             |  |

| 102*          | TR      | SDA and SCL rise       | 100 kHz mode               | —            | 1000 | ns    |                                             |  |

|               |         | time                   | 400 kHz mode               | 20 + 0.1Св   | 300  | ns    | CB is specified to be from 10-400 pF        |  |

| 103*          | TF      | SDA and SCL fall       | 100 kHz mode               | —            | 300  | ns    |                                             |  |

|               |         | time                   | 400 kHz mode               | 20 + 0.1Св   | 300  | ns    | CB is specified to be from 10-400 pF        |  |

| 90*           | TSU:STA | Start condition        | 100 kHz mode               | 4.7          |      | μS    | Only relevant for                           |  |

|               |         | setup time             | 400 kHz mode               | 0.6          |      | μS    | Repeated Start condition                    |  |

| 91*           | THD:STA | Start condition hold   | 100 kHz mode               | 4.0          | _    | μS    | After this period the first                 |  |

|               |         | time                   | 400 kHz mode               | 0.6          |      | μS    | clock pulse is generated                    |  |

| 106*          | THD:DAT | THD:DAT                | D:DAT Data input hold time | 100 kHz mode | 0    | _     | ns                                          |  |

|               |         |                        | 400 kHz mode               | 0            | 0.9  | μS    |                                             |  |

| 107*          | TSU:DAT | Data input setup       | 100 kHz mode               | 250          | —    | ns    | (Note 2)                                    |  |

|               |         | time                   | 400 kHz mode               | 100          | _    | ns    |                                             |  |

| 92*           | TSU:STO | Stop condition         | 100 kHz mode               | 4.7          | _    | μS    |                                             |  |

|               |         | setup time             | 400 kHz mode               | 0.6          | —    | μS    |                                             |  |

| 109*          | ΤΑΑ     | Output valid from      | 100 kHz mode               | —            | 3500 | ns    | (Note 1)                                    |  |

|               |         | clock                  | 400 kHz mode               | —            | —    | ns    |                                             |  |

| 110*          | TBUF    | Bus free time          | 100 kHz mode               | 4.7          | —    | μS    | Time the bus must be free                   |  |

|               |         |                        | 400 kHz mode               | 1.3          | _    | μS    | before a new transmission<br>can start      |  |

|               | Св      | Bus capacitive loading | ng                         | —            | 400  | pF    |                                             |  |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TsU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

# PIC16F631/677/685/687/689/690

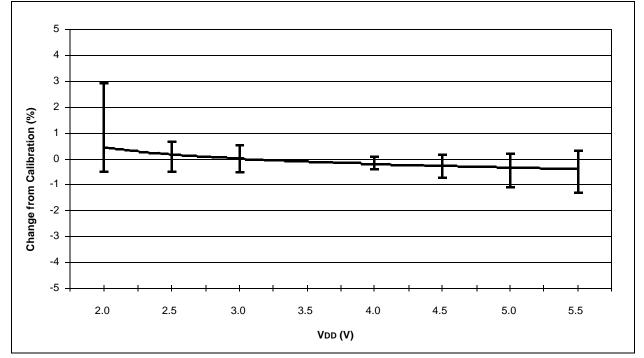

FIGURE 18-39: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

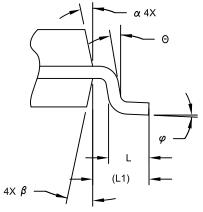

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | N    | <b>ILLIMETER</b> | S        |      |  |  |

|--------------------------|------|------------------|----------|------|--|--|

| Dimension Lim            | nits | MIN              | NOM      | MAX  |  |  |

| Number of Pins           | N    |                  | 20       |      |  |  |

| Pitch                    | е    |                  | 1.27 BSC |      |  |  |

| Overall Height           | Α    | -                | -        | 2.65 |  |  |

| Molded Package Thickness | A2   | 2.05             | -        | -    |  |  |

| Standoff §               | A1   | 0.10             | -        | 0.30 |  |  |

| Overall Width            | Е    | 10.30 BSC        |          |      |  |  |

| Molded Package Width     | E1   | 7.50 BSC         |          |      |  |  |

| Overall Length           | D    | 12.80 BSC        |          |      |  |  |

| Chamfer (Optional)       | h    | 0.25             | -        | 0.75 |  |  |

| Foot Length              | L    | 0.40             | -        | 1.27 |  |  |

| Footprint                | L1   | 1.40 REF         |          |      |  |  |

| Lead Angle               | Θ    | 0°               | -        | -    |  |  |

| Foot Angle               | φ    | 0°               | -        | 8°   |  |  |

| Lead Thickness           | С    | 0.20             | -        | 0.33 |  |  |

| Lead Width               | b    | 0.31             | -        | 0.51 |  |  |

| Mold Draft Angle Top     | α    | 5°               | -        | 15°  |  |  |

| Mold Draft Angle Bottom  | β    | 5°               | -        | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2