Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-i-so |

| Device    | Program<br>Memory | Data N          | <b>l</b> lemory | I/O | 10-bit A/D | Comparators | Timers   | SSP | ECCP+ | EUSART |

|-----------|-------------------|-----------------|-----------------|-----|------------|-------------|----------|-----|-------|--------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM (bytes)  |     | (ch)       | Comparators | 8/16-bit | 331 | ECCFT | LOSAKI |

| PIC16F631 | 1024              | 64              | 128             | 18  | _          | 2           | 1/1      | No  | No    | No     |

| PIC16F677 | 2048              | 128             | 256             | 18  | 12         | 2           | 1/1      | Yes | No    | No     |

| PIC16F685 | 4096              | 256             | 256             | 18  | 12         | 2           | 2/1      | No  | Yes   | No     |

| PIC16F687 | 2048              | 128             | 256             | 18  | 12         | 2           | 1/1      | Yes | No    | Yes    |

| PIC16F689 | 4096              | 256             | 256             | 18  | 12         | 2           | 1/1      | Yes | No    | Yes    |

| PIC16F690 | 4096              | 256             | 256             | 18  | 12         | 2           | 2/1      | Yes | Yes   | Yes    |

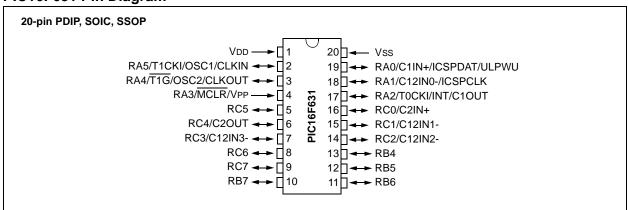

### PIC16F631 Pin Diagram

TABLE 1: PIC16F631 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | Interrupt | Pull-up          | Basic       |

|-----|-----|-----------|-------------|--------|-----------|------------------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | _      | IOC       | Y                | ICSPDAT     |

| RA1 | 18  | AN1       | C12IN0-     | _      | IOC       | Υ                | ICSPCLK     |

| RA2 | 17  | _         | C1OUT       | T0CKI  | IOC/INT   | Y                | _           |

| RA3 | 4   | _         | _           | _      | IOC       | Y <sup>(1)</sup> | MCLR/VPP    |

| RA4 | 3   | _         | _           | T1G    | IOC       | Y                | OSC2/CLKOUT |

| RA5 | 2   | _         | _           | T1CKI  | IOC       | Y                | OSC1/CLKIN  |

| RB4 | 13  | _         | _           | _      | IOC       | Y                | _           |

| RB5 | 12  | _         | _           | _      | IOC       | Y                | _           |

| RB6 | 11  | _         | _           | _      | IOC       | Y                | _           |

| RB7 | 10  | _         | _           | _      | IOC       | Y                | _           |

| RC0 | 16  | AN4       | C2IN+       | _      | _         | _                | _           |

| RC1 | 15  | AN5       | C12IN1-     | _      | _         | _                | _           |

| RC2 | 14  | AN6       | C12IN2-     | _      |           |                  | _           |

| RC3 | 7   | AN7       | C12IN3-     | _      | _         | _                | _           |

| RC4 | 6   | _         | C2OUT       | _      | _         | _                | _           |

| RC5 | 5   | _         | _           | _      | _         | _                | _           |

| RC6 | 8   | _         | _           |        |           |                  | _           |

| RC7 | 9   |           | _           |        |           |                  | _           |

|     | 1   | _         | _           |        |           | _                | VDD         |

|     | 20  | _         | _           | _      | _         | _                | Vss         |

**Note 1:** Pull-up enabled only with external  $\overline{MCLR}$  configuration.

TABLE 1-3: PINOUT DESCRIPTION – PIC16F685 (CONTINUED)

| Name                | Function | Input<br>Type | Output<br>Type | Description                         |

|---------------------|----------|---------------|----------------|-------------------------------------|

| RC1/AN5/C12IN1-     | RC1      | ST            | CMOS           | General purpose I/O.                |

|                     | AN5      | AN            | _              | A/D Channel 5 input.                |

|                     | C12IN1-  | AN            | _              | Comparator C1 or C2 negative input. |

| RC2/AN6/C12IN2-/P1D | RC2      | ST            | CMOS           | General purpose I/O.                |

|                     | AN6      | AN            | _              | A/D Channel 6 input.                |

|                     | C12IN2-  | AN            | _              | Comparator C1 or C2 negative input. |

|                     | P1D      |               | CMOS           | PWM output.                         |

| RC3/AN7/C12IN3-/P1C | RC3      | ST            | CMOS           | General purpose I/O.                |

|                     | AN7      | AN            | _              | A/D Channel 7 input.                |

|                     | C12IN3-  | AN            | _              | Comparator C1 or C2 negative input. |

|                     | P1C      |               | CMOS           | PWM output.                         |

| RC4/C2OUT/P1B       | RC4      | ST            | CMOS           | General purpose I/O.                |

|                     | C2OUT    |               | CMOS           | Comparator C2 output.               |

|                     | P1B      | _             | CMOS           | PWM output.                         |

| RC5/CCP1/P1A        | RC5      | ST            | CMOS           | General purpose I/O.                |

|                     | CCP1     | ST            | CMOS           | Capture/Compare input.              |

|                     | P1A      | ST            | CMOS           | PWM output.                         |

| RC6/AN8             | RC6      | ST            | CMOS           | General purpose I/O.                |

|                     | AN8      | AN            | _              | A/D Channel 8 input.                |

| RC7/AN9             | RC7      | ST            | CMOS           | General purpose I/O.                |

|                     | AN9      | AN            |                | A/D Channel 9 input.                |

| Vss                 | Vss      | Power         |                | Ground reference.                   |

| VDD                 | VDD      | Power         | _              | Positive supply.                    |

**Legend:** AN = Analog input or output

CMOS=CMOS compatible input or output

TTL = TTL compatible input

ST= Schmitt Trigger input with CMOS levels

HV = High Voltage X

XTAL= Crystal

### 2.2 Data Memory Organization

The data memory (see Figures 2-6 through 2-8) is partitioned into four banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. The General Purpose Registers, implemented as static RAM, are located in the last 96 locations of each Bank. Register locations F0h-FFh in Bank 1, 170h-17Fh in Bank 2 and 1F0h-1FFh in Bank 3 point to addresses 70h-7Fh in Bank 0. The actual number of General Purpose Resisters (GPR) in each Bank depends on the device. Details are shown in Figures 2-4 through 2-8. All other RAM is unimplemented and returns '0' when read. RP<1:0> of the STATUS register are the bank select bits:

| <u>RP1</u> | <u>RP0</u> |               |                    |

|------------|------------|---------------|--------------------|

| 0          | 0          | $\rightarrow$ | Bank 0 is selected |

| 0          | 1          | $\rightarrow$ | Bank 1 is selected |

| 1          | 0          | $\rightarrow$ | Bank 2 is selected |

| 1          | 1          | $\rightarrow$ | Bank 3 is selected |

# 2.2.1 GENERAL PURPOSE REGISTER

The register file is organized as 128 x 8 in the PIC16F687 and 256 x 8 in the PIC16F685/PIC16F689/ PIC16F690. Each register is accessed, either directly or indirectly, through the File Select Register (FSR) (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Tables 2-1 through 2-4). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Registers related to the operation of peripheral features are described in the section of that peripheral feature.

Note:

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the interrupt flag bits, as shown in Register 2-7.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### **REGISTER 2-7:** PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| OSFIF | C2IF  | C1IF  | EEIF  | _   | _   | _   | _     |

| bit 7 |       |       |       |     |     |     | bit 0 |

| W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|------------------|------------------------|--------------------|

| '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                  |                        |                    |

|                  |                        | · ·                |

bit 7 **OSFIF:** Oscillator Fail Interrupt Flag bit 1 = System oscillator failed, clock input has changed to INTOSC (must be cleared in software) 0 = System clock operating bit 6 C2IF: Comparator C2 Interrupt Flag bit 1 = Comparator output (C2OUT bit) has changed (must be cleared in software) 0 = Comparator output (C2OUT bit) has not changed bit 5 C1IF: Comparator C1 Interrupt Flag bit 1 = Comparator output (C1OUT bit) has changed (must be cleared in software) 0 = Comparator output (C1OUT bit) has not changed bit 4 EEIF: EE Write Operation Interrupt Flag bit

> 1 = Write operation completed (must be cleared in software) 0 = Write operation has not completed or has not started

bit 3-0 Unimplemented: Read as '0'

### 4.0 **I/O PORTS**

There are as many as eighteen general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

### 4.1 PORTA and the TRISA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 4-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Reading the PORTA register (Register 4-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write

operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

Note: The ANSEL register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

### **EXAMPLE 4-1: INITIALIZING PORTA**

BCF STATUS, RP0; Bank 0 BCF STATUS, RP1; CLRF PORTA ;Init PORTA BSF STATUS, RP1; Bank 2 CLRF ANSEL ;digital I/O BSF STATUS, RP0; Bank 1 BCF STATUS, RP1; MOVLW 0Ch ;Set RA<3:2> as inputs MOVWE TRISA ;and set RA<5:4,1:0> ;as outputs BCF STATUS, RP0; Bank 0

#### REGISTER 4-1: PORTA: PORTA REGISTER

| U-0   | U-0 | R/W-x | R/W-x | R-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-----|-------|-------|-------|

| _     |     | RA5   | RA4   | RA3 | RA2   | RA1   | RA0   |

| bit 7 |     |       |       |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### REGISTER 4-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 TRISA<5:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

Note 1: TRISA<3> always reads '1'.

2: TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

### REGISTER 8-2: CM2CON0: COMPARATOR C2 CONTROL REGISTER 0

| R/W-0 | R-0   | R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----|-------|-------|-------|

| C2ON  | C2OUT | C2OE  | C2POL | _   | C2R   | C2CH1 | C2CH0 |

| bit 7 |       |       |       |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 C2ON: Comparator C2 Enable bit

1 = Comparator C2 is enabled

0 = Comparator C2 is disabled

bit 6 C2OUT: Comparator C2 Output bit

If C2POL = 1 (inverted polarity):

C2OUT = 0 when C2VIN+ > C2VINC2OUT = 1 when C2VIN+ < C2VINIf C2POL = 0 (non-inverted polarity):

C2OUT = 1 when C2VIN+ > C2VINC2OUT = 0 when C2VIN+ < C2VIN-

bit 5 C20E: Comparator C2 Output Enable bit

1 = C2OUT is present on C2OUT  $pin^{(1)}$

0 = C2OUT is internal only

bit 4 C1POL: Comparator C1 Output Polarity Select bit

1 = C1OUT logic is inverted 0 = C1OUT logic is not inverted

bit 3 **Unimplemented:** Read as '0'

bit 2 C2R: Comparator C2 Reference Select bits (non-inverting input)

1 = C2VIN+ connects to C2VREF 0 = C2VIN+ connects to C2IN+ pin

bit 1-0 C2CH<1:0>: Comparator C2 Channel Select bits

00 = C2VIN- of C2 connects to C12IN0- pin 01 = C2VIN- of C2 connects to C12IN1- pin 10 = C2VIN- of C2 connects to C12IN2- pin 11 = C2VIN- of C2 connects to C12IN3- pin

**Note 1:** Comparator output requires the following three conditions: C2OE = 1, C2ON = 1 and corresponding PORT TRIS bit = 0.

#### REGISTER 8-5: VRCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| C1VREN | C2VREN | VRR   | VP6EN | VR3   | VR2   | VR1   | VR0   |

| bit 7  |        |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 C1VREN: Comparator 1 Voltage Reference Enable bit

1 = CVREF circuit powered on and routed to C1VREF input of Comparator C1 0 = 0.6 Volt constant reference routed to C1VREF input of Comparator C1

bit 6 C2VREN: Comparator 2 Voltage Reference Enable bit

1 = CVREF circuit powered on and routed to C2VREF input of Comparator C2 0 = 0.6 Volt constant reference routed to C2VREF input of Comparator C2

bit 5 VRR: CVREF Range Selection bit

1 = Low range0 = High range

bit 4 **VP6EN:** 0.6V Reference Enable bit

1 = Enabled0 = Disabled

bit 3-0 VR<3:0>: Comparator Voltage Reference CVREF Value Selection bits (0 ≤ VR<3:0> ≤ 15)

When VRR = 1: CVREF = (VR < 3:0 > /24) \* VDDWhen VRR = 0: CVREF = VDD/4 + (VR < 3:0 > /32) \* VDD

# TABLE 8-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND VOLTAGE REFERENCE MODULES

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| ANSEL   | ANS7   | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| CM1CON0 | C10N   | C1OUT  | C10E   | C1POL  | _      | C1R    | C1CH1  | C1CH0  | 0000 -000            | 0000 0000                       |

| CM2CON0 | C2ON   | C2OUT  | C2OE   | C2POL  | -      | C2R    | C2CH1  | C2CH0  | 0000 -000            | 0000 -000                       |

| CM2CON1 | MC1OUT | MC2OUT | _      | _      | _      | _      | T1GSS  | C2SYNC | 0010                 | 0010                            |

| INTCON  | GIE    | PEIE   | TOIE   | INTE   | RABIE  | TOIF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| PIE2    | OSFIE  | C2IE   | C1IE   | EEIE   | _      | _      | _      | _      | 0000                 | 0000                            |

| PIR2    | OSFIF  | C2IF   | C1IF   | EEIF   | _      | _      | _      | _      | 0000                 | 0000                            |

| PORTA   | _      | _      | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xx xxxx              | uu uuuu                         |

| PORTC   | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx            | uuuu uuuu                       |

| SRCON   | SR1    | SR0    | C1SEN  | C2REN  | PULSS  | PULSR  | _      | _      | 0000 00              | 0000 00                         |

| TRISA   | _      | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| TRISC   | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| VRCON   | C1VREN | C2VREN | VRR    | VP6EN  | VR3    | VR2    | VR1    | VR0    | 0000 0000            | 0000 0000                       |

$\textbf{Legend:} \quad \textbf{x} = \text{unknown}, \textbf{u} = \text{unchanged}, -= \text{unimplemented}, \text{ read as '0'}. \text{ Shaded cells are not used for comparator.}$

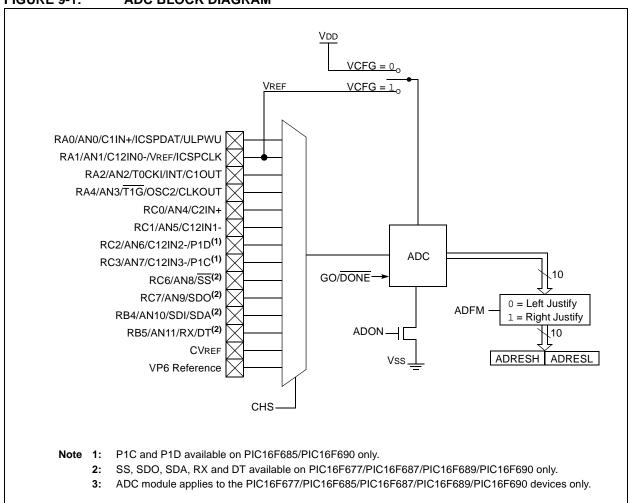

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

Figure 9-1 shows the block diagram of the ADC.

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

Note: The ADC module applies to PIC16F677/

PIC16F685/PIC16F687/PIC16F689/

PIC16F690 devices only.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

FIGURE 9-1: ADC BLOCK DIAGRAM

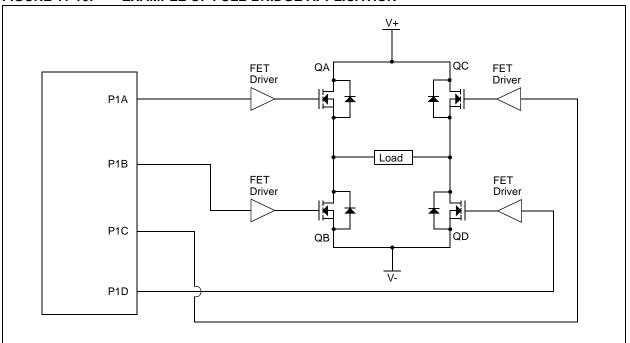

### 11.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 11-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 11-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 11-11.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

FIGURE 11-10: EXAMPLE OF FULL-BRIDGE APPLICATION

#### 12.3.2 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCTL register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 12-7), and asynchronously if the device is in Sleep mode (Figure 12-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 12.3.2.1 Special Considerations

#### **Break Character**

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### **WUE Bit**

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### 13.12.3 SSP MASK REGISTER

An SSP Mask (SSPMSK) register is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit in the SSPSR register a 'don't care'.

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

This register must be initiated prior to setting SSPM<3:0> bits to select the I<sup>2</sup>C Slave mode (7-bit or 10-bit address).

This register can only be accessed when the appropriate mode is selected by bits (SSPM<3:0> of SSPCON).

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0>

only. The SSP mask has no effect during the

reception of the first (high) byte of the address.

### REGISTER 13-3: SSPMSK: SSP MASK REGISTER<sup>(1)</sup>

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 |       |       |       |       |       |       | bit 0               |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | r, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-1 **MSK<7:1>:** Mask bits

1 = The received address bit n is compared to SSPADD<n> to detect  $I^2C$  address match

0 = The received address bit n is not used to detect I<sup>2</sup>C address match

bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address<sup>(2)</sup>

$I^2C$  Slave mode, 10-bit Address (SSPM<3:0> = 0111):

1 = The received address bit 0 is compared to SSPADD<0> to detect I<sup>2</sup>C address match

0 = The received address bit 0 is not used to detect  $I^2C$  address match

Note 1: When SSPCON bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. The SSPEN bit of the SSPCON register should be zero when accessing the SSPMSK register.

2: In all other SSP modes, this bit has no effect.

TABLE 14-4: INITIALIZATION CONDITION FOR REGISTER

| Register   | Address               | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |

|------------|-----------------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|

| W          | _                     | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| INDF       | 00h/80h/<br>100h/180h | xxxx xxxx      | xxxx xxxx                                                 | uuuu uuuu                                                                             |

| TMR0       | 01h/101h              | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCL        | 02h/82h/<br>102h/182h | 0000 0000      | 0000 0000                                                 | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS     | 03h/83h/<br>103h/183h | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                  | uuuq quuu <sup>(4)</sup>                                                              |

| FSR        | 04h/84h/<br>104h184h  | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PORTA      | 05h/105h              | xx xxxx        | uu uuuu                                                   | uu uuuu                                                                               |

| PORTB      | 06h/106h              | xxxx           | uuuu                                                      | uuuu                                                                                  |

| PORTC      | 07h/107h              | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| PCLATH     | 0Ah/8Ah/<br>10Ah/18Ah | 0 0000         | 0 0000                                                    | u uuuu                                                                                |

| INTCON     | 0Bh/8Bh/<br>10Bh/18Bh | 0000 000x      | 0000 000u                                                 | uuuu uuuu <sup>(2)</sup>                                                              |

| PIR1       | 0Ch                   | -000 0000      | -000 0000                                                 | -uuu uuuu <b>(2)</b>                                                                  |

| PIR2       | 0Dh                   | 0000           | 0000                                                      | uuuu <b>(2)</b>                                                                       |

| TMR1L      | 0Eh                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR1H      | 0Fh                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| T1CON      | 10h                   | 0000 0000      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| TMR2       | 11h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| T2CON      | 12h                   | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |

| SSPBUF     | 13h                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| SSPCON     | 14h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| CCPR1L     | 15h                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCPR1H     | 16h                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| CCP1CON    | 17h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| RCSTA      | 18h                   | 0000 000x      | 0000 000x                                                 | uuuu uuuu                                                                             |

| TXREG      | 19h                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| RCREG      | 1Ah                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| PWM1CON    | 1Ch                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| ECCPAS     | 1Dh                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| ADRESH     | 1Eh                   | xxxx xxxx      | uuuu uuuu                                                 | uuuu uuuu                                                                             |

| ADCON0     | 1Fh                   | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |

| OPTION_REG | 81h/181h              | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |

| TRISA      | 85h/185h              | 11 1111        | 11 1111                                                   | uu uuuu                                                                               |

**Legend:** u = unchanged, x = unknown, -= unimplemented bit, reads as '0', <math>q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

<sup>2:</sup> One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

<sup>3:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**<sup>4:</sup>** See Table 14-5 for Reset value for specific condition.

<sup>5:</sup> If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

**<sup>6:</sup>** Accessible only when SSPM<3:0> = 1001.

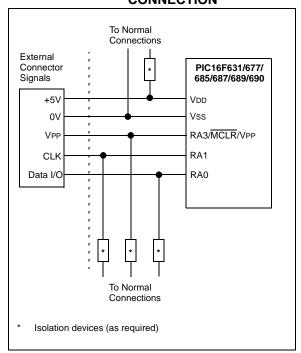

FIGURE 14-11: TYPICAL IN-CIRCUIT

SERIAL PROGRAMMING

CONNECTION

#### 16.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers (MCU) and dsPIC® digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 16.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

#### **TABLE 17-2: OSCILLATOR PARAMETERS**

| Standard Operating Conditions (unless otherwise stated)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |          |                                                        |                    |      |      |      |       |                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------|--------------------|------|------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                                                | Sym.     | Characteristic                                         | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                                                                                                                       |

| OS06                                                                                                                                        | TWARM    | Internal Oscillator Switch when running <sup>(3)</sup> | _                  | _    | _    | 2    | Tosc  | Slowest clock                                                                                                                                    |

| OS07                                                                                                                                        | Tsc      | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | _                  | _    | 21   | _    | ms    | LFINTOSC/64                                                                                                                                      |

| OS08                                                                                                                                        | HFosc    | Internal Calibrated                                    | ±1%                | 7.92 | 8.0  | 8.08 | MHz   | VDD = 3.5V, 25°C                                                                                                                                 |

|                                                                                                                                             |          | HFINTOSC Frequency <sup>(2)</sup>                      | ±2%                | 7.84 | 8.0  | 8.16 | MHz   | $2.5V \le VDD \le 5.5V$ , $0^{\circ}C \le TA \le +85^{\circ}C$                                                                                   |

|                                                                                                                                             |          |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz   | $2.0V \le VDD \le 5.5V$ ,<br>- $40^{\circ}C \le TA \le +85^{\circ}C \text{ (Ind.)}$ ,<br>- $40^{\circ}C \le TA \le +125^{\circ}C \text{ (Ext.)}$ |

| OS09*                                                                                                                                       | LFosc    | Internal Uncalibrated LFINTOSC Frequency               | _                  | 15   | 31   | 45   | kHz   |                                                                                                                                                  |

| OS10*                                                                                                                                       | Tiosc st | HFINTOSC Oscillator                                    | _                  | 5.5  | 12   | 24   | μS    | $VDD = 2.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                              |

|                                                                                                                                             |          | Wake-up from Sleep                                     | _                  | 3.5  | 7    | 14   | μS    | $VDD = 3.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                              |

|                                                                                                                                             |          | Start-up Time                                          | _                  | 3    | 6    | 11   | μS    | VDD = 5.0V, -40°C to +85°C                                                                                                                       |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at 'min' values with an external clock applied to the OSC1 pin. When an external clock input is used, the 'max' cycle time limit is 'DC' (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

- 3: By design.

TABLE 17-18: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD  $\geq$  3.0V, VREF  $\geq$  2.5V)

| ADC Clock        | Period (TAD) | Device Frequency (Fosc) |        |         |         |  |  |

|------------------|--------------|-------------------------|--------|---------|---------|--|--|

| ADC Clock Source | ADCS<2:0>    | 20 MHz                  | 8 MHz  | 4 MHz   | 1 MHz   |  |  |

| Fosc/2           | 000          | 100 ns                  | 250 ns | 500 ns  | 2.0 μs  |  |  |

| Fosc/4           | 100          | 200 ns                  | 500 ns | 1.0 μs  | 4.0 μs  |  |  |

| Fosc/8           | 001          | 400 ns                  | 1.0 μs | 2.0 μs  | 8.0 µs  |  |  |

| Fosc/16          | 101          | 800 ns                  | 2.0 μs | 4.0 μs  | 16.0 μs |  |  |

| Fosc/32          | 010          | 1.6 µs                  | 4.0 μs | 8.0 µs  | 32.0 μs |  |  |

| Fosc/64          | 110          | 3.2 μs                  | 8.0 µs | 16.0 μs | 64.0 μs |  |  |

| Frc              | x11          | 2-6 μs                  | 2-6 μs | 2-6 μs  | 2-6 μs  |  |  |

**Legend:** Shaded cells should not be used for conversions at temperatures above +125°C.

Note 1: TAD must be between 1.6  $\mu$ s and 4.0  $\mu$ s.

### TABLE 17-23: OSCILLATOR PARAMETERS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym.   | Characteristic                                 | Frequency<br>Tolerance | Min. | Тур. | Max. | Units | Conditions                              |

|--------------|--------|------------------------------------------------|------------------------|------|------|------|-------|-----------------------------------------|

| OS08         | INTosc | Int. Calibrated INTOSC<br>Freq. <sup>(1)</sup> | ±7.5%                  | 7.4  | 8.0  | 8.6  |       | 2.1V ≤ VDD ≤ 5.5V<br>-40°C ≤ TA ≤ 150°C |

**Note 1:** To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1 µF and 0.01 µF values in parallel are recommended.

### TABLE 17-24: WATCHDOG TIMER SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic                                | Min. | Тур. | Max. | Units | Conditions        |

|--------------|------|-----------------------------------------------|------|------|------|-------|-------------------|

| 31           | TWDT | Watchdog Timer Time-out Period (No Prescaler) | 10   | 20   | 70   | ms    | 150°C Temperature |

### TABLE 17-25: BROWN-OUT RESET SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic          | Min. | Тур. | Max. | Units | Conditions        |

|--------------|------|-------------------------|------|------|------|-------|-------------------|

| 35           | VBOR | Brown-Out Reset Voltage | 2.0  | _    | 2.3  | V     | 150°C Temperature |

### TABLE 17-26: COMPARATOR SPECIFICATIONS FOR PIC16F685/687/689/690-H (High Temp.)

| Param<br>No. | Sym. | Characteristic       | Min. | Тур. | Max. | Units | Conditions    |

|--------------|------|----------------------|------|------|------|-------|---------------|

| CM01         | Vos  | Input Offset Voltage | _    | ±5   | ±20  | mV    | (VDD - 1.5)/2 |

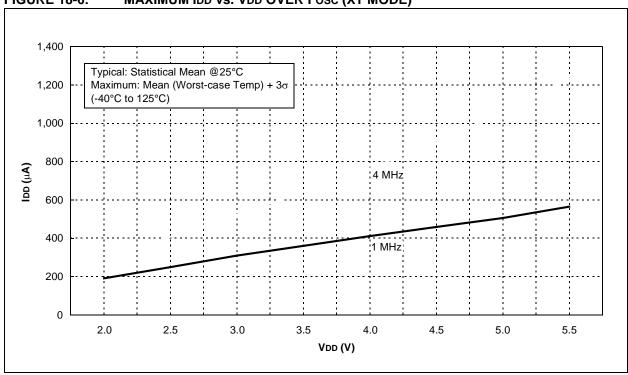

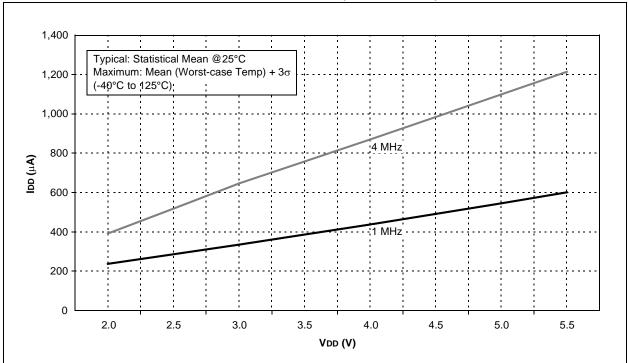

FIGURE 18-6: MAXIMUM IDD vs. VDD OVER FOSC (XT MODE)

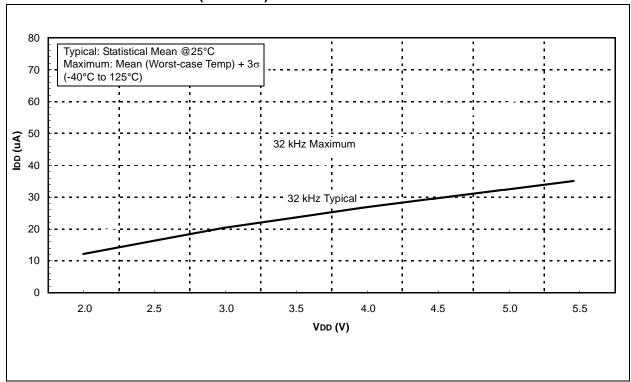

FIGURE 18-7: IDD vs. VDD (LP MODE)

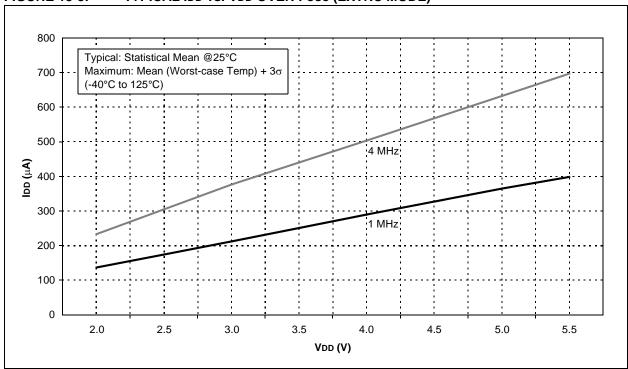

FIGURE 18-8: TYPICAL IDD vs. VDD OVER FOSC (EXTRC MODE)

FIGURE 18-9: MAXIMUM IDD vs. VDD OVER FOSC (EXTRC MODE)

## Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Support Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY

Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880 China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828

Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf

Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15