Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| -                          |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687-i-ss |

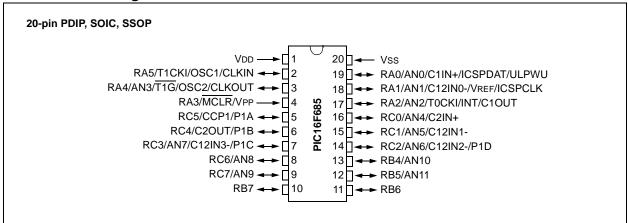

# PIC16F685 Pin Diagram

TABLE 3: PIC16F685 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | ECCP     | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|----------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | _      | _        | IOC       | Υ       | ICSPDAT     |

| RA1 | 18  | AN1/VREF  | C12IN0-     | _      | _        | IOC       | Υ       | ICSPCLK     |

| RA2 | 17  | AN2       | C1OUT       | T0CKI  | _        | IOC/INT   | Υ       | _           |

| RA3 | 4   | _         | _           | _      | _        | IOC       | Y(1)    | MCLR/VPP    |

| RA4 | 3   | AN3       | _           | T1G    | _        | IOC       | Υ       | OSC2/CLKOUT |

| RA5 | 2   | _         | _           | T1CKI  | _        | IOC       | Υ       | OSC1/CLKIN  |

| RB4 | 13  | AN10      | _           | _      | _        | IOC       | Υ       | _           |

| RB5 | 12  | AN11      | _           | _      | _        | IOC       | Υ       | _           |

| RB6 | 11  |           | _           | _      | _        | IOC       | Υ       | _           |

| RB7 | 10  | _         | _           | _      | _        | IOC       | Υ       | _           |

| RC0 | 16  | AN4       | C2IN+       | _      |          | 1         | _       | _           |

| RC1 | 15  | AN5       | C12IN1-     | _      |          |           | _       | _           |

| RC2 | 14  | AN6       | C12IN2-     | _      | P1D      | 1         |         | _           |

| RC3 | 7   | AN7       | C12IN3-     | _      | P1C      |           | _       | _           |

| RC4 | 6   |           | C2OUT       | _      | P1B      |           |         | _           |

| RC5 | 5   | _         | _           | _      | CCP1/P1A |           | _       | _           |

| RC6 | 8   | AN8       |             |        | _        |           | _       |             |

| RC7 | 9   | AN9       |             |        |          |           | _       | _           |

| _   | 1   |           |             |        | _        | _         | _       | Vdd         |

| _   | 20  | _         | _           | _      | _        | _         | _       | Vss         |

**Note 1:** Pull-up activated only with external MCLR configuration.

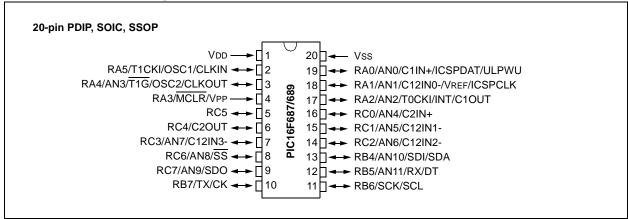

# PIC16F687/689 Pin Diagram

TABLE 4: PIC16F687/689 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | EUSART | SSP     | Interrupt | Pull-up          | Basic       |

|-----|-----|-----------|-------------|--------|--------|---------|-----------|------------------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       | _      | _      | _       | IOC       | Y                | ICSPDAT     |

| RA1 | 18  | AN1/VREF  | C12IN0-     | _      | _      | _       | IOC       | Υ                | ICSPCLK     |

| RA2 | 17  | AN2       | C1OUT       | T0CKI  | _      | _       | IOC/INT   | Y                |             |

| RA3 | 4   | _         | _           | _      | _      | _       | IOC       | Y <sup>(1)</sup> | MCLR/VPP    |

| RA4 | 3   | AN3       | _           | T1G    | _      | _       | IOC       | Y                | OSC2/CLKOUT |

| RA5 | 2   | _         | _           | T1CKI  | _      | _       | IOC       | Y                | OSC1/CLKIN  |

| RB4 | 13  | AN10      | _           | _      | _      | SDI/SDA | IOC       | Y                | _           |

| RB5 | 12  | AN11      | _           | _      | RX/DT  | _       | IOC       | Y                | _           |

| RB6 | 11  | _         | _           | _      | _      | SCL/SCK | IOC       | Υ                | _           |

| RB7 | 10  | _         | _           | _      | TX/CK  | _       | IOC       | Υ                | _           |

| RC0 | 16  | AN4       | C2IN+       | _      | _      |         | 1         | _                |             |

| RC1 | 15  | AN5       | C12IN1-     | _      | _      | _       |           | _                |             |

| RC2 | 14  | AN6       | C12IN2-     | _      | _      | 1       | -         | _                | _           |

| RC3 | 7   | AN7       | C12IN3-     | _      | _      | -       | 1         | _                | _           |

| RC4 | 6   | _         | C2OUT       | _      | _      | 1       | 1         | _                | _           |

| RC5 | 5   | _         | _           | _      | _      | _       | _         | _                | _           |

| RC6 | 8   | AN8       | _           | _      | _      | SS      | _         | _                |             |

| RC7 | 9   | AN9       |             |        |        | SDO     |           |                  |             |

| _   | 1   | _         | _           |        | _      | _       | _         | _                | VDD         |

| _   | 20  | _         | _           |        |        |         |           |                  | Vss         |

**Note 1:** Pull-up activated only with external  $\overline{\text{MCLR}}$  configuration.

#### 4.2 Additional Pin Functions

Every PORTA pin on this device family has an interrupton-change option and a weak pull-up option. RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

#### 4.2.1 ANSEL AND ANSELH REGISTERS

The ANSEL and ANSELH registers are used to disable the input buffers of I/O pins, which allow analog voltages to be applied to those pins without causing excessive current. Setting the ANSx bit of a corresponding pin will cause all digital reads of that pin to return '0' and also permit analog functions of that pin to operate correctly.

The state of the ANSx bit has no effect on the digital output function of its corresponding pin. A pin with the TRISx bit clear and ANSx bit set will operate as a digital output, together with the analog input function of that pin. Pins with the ANSx bit set always read '0', which can cause unexpected behavior when executing read or write operations on the port due to the read-modify-write sequence of all such operations.

#### 4.2.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-4. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RABPU bit of the OPTION register. A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an I/O. There is no software control of the MCLR pull-up.

#### 4.2.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCAx enable or disable the interrupt function for each pin. Refer to Register 4-6. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (RABIF) in the INTCON register (Register 2-6).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTA. This will end the mismatch condition, then,

- b) Clear the flag bit RABIF.

A mismatch condition will continue to set flag bit RABIF. Reading PORTA will end the mismatch condition and allow flag bit RABIF to be cleared. The latch holding the last read value is not affected by a  $\overline{\text{MCLR}}$  nor BOR Reset. After these Resets, the RABIF flag will continue to be set if a mismatch is present.

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set.

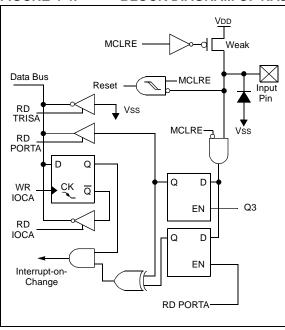

# 4.2.5.4 RA3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The RA3/MCLR/VPP pin is configurable to function as one of the following:

- · a general purpose input

- · as Master Clear Reset with weak pull-up

# FIGURE 4-4: BLOCK DIAGRAM OF RA3

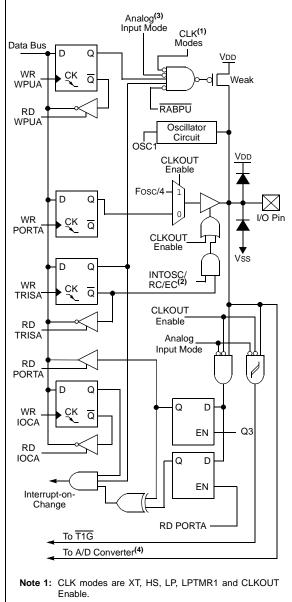

# 4.2.5.5 RA4/AN3/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The RA4/ AN3/T1G/OSC2/CLKOUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a Timer1 gate input

- · a crystal/resonator connection

- · a clock output

# FIGURE 4-5: BLOCK DIAGRAM OF RA4

- 2: With CLKOUT option.

- 3: ANSEL determines Analog Input mode.

- 4: Not implemented on PIC16F631.

# 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 3-bit prescaler

- · Optional LP oscillator

- · Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or T1G pin

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function (PIC16F685/PIC16F690 only)

- Special Event Trigger (with ECCP) (PIC16F685/PIC16F690 only)

- Comparator output synchronization to Timer1 clock

Figure 6-1 is a block diagram of the Timer1 module.

# 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

#### 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is Fosc/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock<br>Source | T10SCEN | FOSC<br>Mode   | TMR1CS |

|-----------------|---------|----------------|--------|

| Fosc/4          | osc/4 x |                | 0      |

| T1CKI pin       | 0       | xxx            | 1      |

| T1LPOSC         | 1       | LP or INTOSCIO | 1      |

# REGISTER 7-1: T2CON: TIMER 2 CONTROL REGISTER<sup>(1)</sup>

| U-0   | -0 R/W-0 R/W-0 R/W- |         | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0   |

|-------|---------------------|---------|---------|---------|--------|---------|---------|

| _     | TOUTPS3             | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |                     |         |         |         |        |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 Unimplemented: Read as '0'

bit 6-3 TOUTPS<3:0>: Timer2 Output Postscaler Select bits

0000 =1:1 Postscaler

0001 =1:2 Postscaler

0010 =1:3 Postscaler

0011 =1:4 Postscaler

0100 =1:5 Postscaler

0101 =1:6 Postscaler

0110 =1:7 Postscaler

0111 =1:8 Postscaler

1000 =1:9 Postscaler

1001 =1:10 Postscaler

1010 **=1:11 Postscaler**

1011 =1:12 Postscaler

1100 =1:13 Postscaler

1101 =1:14 Postscaler

1110 =1:15 Postscaler

1111 =1:16 Postscaler

bit 2 TMR2ON: Timer2 On bit

1 = Timer2 is on

0 = Timer2 is off

bit 1-0 T2CKPS<1:0>: Timer2 Clock Prescale Select bits

00 =Prescaler is 1

01 =Prescaler is 4

1x =Prescaler is 16

Note 1: PIC16F685/PIC16F690 only.

# TABLE 7-1: SUMMARY OF ASSOCIATED TIMER2(1) REGISTERS

| Name   | Bit 7                                             | Bit 6         | Bit 5    | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------------------------------|---------------|----------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE                                               | PEIE          | TOIE     | INTE    | RABIE   | TOIF   | INTF    | RABIF   | 0000 000x            | 0000 000x                       |

| PIE1   | _                                                 | ADIE          | RCIE     | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -000 0000            | -000 0000                       |

| PIR1   | _                                                 | ADIF          | RCIF     | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -000 0000            | -000 0000                       |

| PR2    | Timer2 M                                          | lodule Period | Register |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | TMR2 Holding Register for the 8-bit TMR2 Register |               |          |         |         |        |         |         |                      | 0000 0000                       |

| T2CON  | _                                                 | TOUTPS3       | TOUTPS2  | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

Note 1: PIC16F685/PIC16F690 only.

# 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The Analog Comparator module includes the following features:

- · Independent comparator control

- · Programmable input selection

- · Comparator output is available internally/externally

- · Programmable output polarity

- Interrupt-on-change

- · Wake-up from Sleep

- PWM shutdown

- Timer1 gate (count enable)

- · Output synchronization to Timer1 clock input

- · SR Latch

- Programmable and Fixed Voltage Reference

**Note:** Only Comparator C2 can be linked to Timer1.

# 8.1 Comparator Overview

A single comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

# VIN+ VIN Output Output Note: The black areas of the output of the comparator represents the uncertainty

due to input offsets and response time.

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

| Name   | Bit 7     | Bit 6        | Bit 5     | Bit 4     | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|--------------|-----------|-----------|--------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0 | ADFM      | VCFG         | CHS3      | CHS2      | CHS1   | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 | _         | ADCS2        | ADCS1     | ADCS0     | _      | _      | _       | _      | -000                 | -000                            |

| ANSEL  | ANS7      | ANS6         | ANS5      | ANS4      | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH | _         | _            | _         | _         | ANS11  | ANS10  | ANS9    | ANS8   | 1111                 | 1111                            |

| ADRESH | A/D Resul |              | xxxx xxxx | uuuu uuuu |        |        |         |        |                      |                                 |

| ADRESL | A/D Resul | t Register L | ow Byte   |           |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE       | PEIE         | TOIE      | INTE      | RABIE  | TOIF   | INTF    | RABIF  | 0000 000x            | 0000 000x                       |

| PIE1   | _         | ADIE         | RCIE      | TXIE      | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | -000 0000            | -000 0000                       |

| PIR1   | _         | ADIF         | RCIF      | TXIF      | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | -000 0000            | -000 0000                       |

| PORTA  | _         | _            | RA5       | RA4       | RA3    | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| PORTB  | RB7       | RB6          | RB5       | RB4       | _      | _      | _       | _      | xxxx                 | uuuu                            |

| PORTC  | RC7       | RC6          | RC5       | RC4       | RC3    | RC2    | RC1     | RC0    | xxxx xxxx            | uuuu uuuu                       |

| TRISA  | _         | _            | TRISA5    | TRISA4    | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| TRISB  | TRISB7    | TRISB6       | TRISB5    | TRISB4    | _      | _      | _       | _      | 1111                 | 1111                            |

| TRISC  | TRISC7    | TRISC6       | TRISC5    | TRISC4    | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

#### 11.0 **ENHANCED CAPTURE/ COMPARE/PWM MODULE**

The Enhanced Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

Table 11-1 shows the timer resources required by the ECCP module.

**TABLE 11-1: ECCP MODE - TIMER** RESOURCES REQUIRED

| ECCP Mode | Timer Resource |  |  |  |

|-----------|----------------|--|--|--|

| Capture   | Timer1         |  |  |  |

| Compare   | Timer1         |  |  |  |

| PWM       | Timer2         |  |  |  |

#### REGISTER 11-1: CCP1CON: ENHANCED CCP1 CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| P1M1  | P1M0  | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |       | •     |       |        | •      |        | bit 0  |

| 1 ~~ |     | ١. |

|------|-----|----|

| Leg  | ena | ١. |

|      |     |    |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 7-6 P1M<1:0>: PWM Output Configuration bits

<u>lf CCP1M<3:2> = 00</u>, 01, 10:

xx =P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins

#### If CCP1M<3:2> = 11:

- 00 =Single output; P1A modulated; P1B, P1C, P1D assigned as port pins

- 01 =Full-Bridge output forward; P1D modulated; P1A active; P1B, P1C inactive

- 10 =Half-Bridge output; P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins

- 11 =Full-Bridge output reverse; P1B modulated; P1C active; P1A, P1D inactive

#### bit 5-4 DC1B<1:0>: PWM Duty Cycle Least Significant bits

Capture mode:

Unused.

Compare mode:

Unused.

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L.

#### bit 3-0 CCP1M<3:0>: ECCP Mode Select bits

- 0000 =Capture/Compare/PWM off (resets ECCP module)

- 0001 =Unused (reserved)

- 0010 =Compare mode, toggle output on match (CCP1IF bit is set)

- 0011 =Unused (reserved)

- 0100 =Capture mode, every falling edge

- 0101 =Capture mode, every rising edge

- 0110 =Capture mode, every 4th rising edge

- 0111 =Capture mode, every 16th rising edge

- 1000 = Compare mode, set output on match (CCP1IF bit is set)

- 1001 =Compare mode, clear output on match (CCP1IF bit is set)

- 1010 =Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected) 1011 =Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 or TMR2, and starts an A/D conversion, if the ADC module is enabled)

- 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high

- 1101 =PWM mode; P1A, P1C active-high; P1B, P1D active-low 1110 =PWM mode; P1A, P1C active-low; P1B, P1D active-low 1111 =PWM mode; P1A, P1C active-low; P1B, P1D active-low

#### 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

# 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- Disable the PWM pin (CCP1) output driver by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- Set the PWM duty cycle by loading the CCPR1L register and DC1B<1:0> bits of the CCP1CON register.

- Configure and start Timer2:

- •Clear the TMR2IF interrupt flag bit of the PIR1 register.

- •Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output driver by clearing the associated TRIS bit.

## 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to ten bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- · Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-4 shows the pin assignments for each Enhanced PWM mode.

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

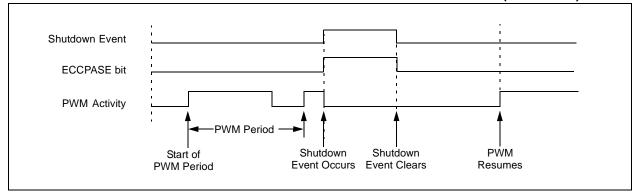

FIGURE 11-15: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (PRSEN = 0) Shutdown Event **ECCPASE** bit **PWM Activity** PWM Period **ECCPASE** Cleared by Start of Shutdown Firmware **PWM** Shutdown **PWM Period Event Occurs** Resumes **Event Clears**

#### 11.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

FIGURE 11-16: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

TABLE 12-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name    | Bit 7                               | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                              | RCIDL      | _           | SCKP   | BRG16 | _      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                                 | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| PIE1    | _                                   | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | _                                   | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                            | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                                | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7                                | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                               | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                              | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | TXREG EUSART Transmit Data Register |            |             |        |       |        |        |        |                      | 0000 0000                       |

| TXSTA   | CSRC                                | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Asynchronous Transmission.

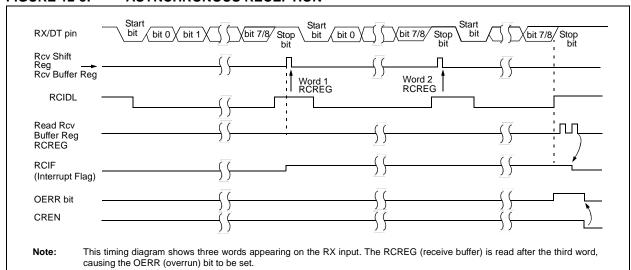

#### 12.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

# 12.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### FIGURE 12-5: ASYNCHRONOUS RECEPTION

# 17.3 DC Characteristics: PIC16F631/677/685/687/689/690-E (Extended)

| DC CHAF | RACTERISTICS                |        | rd Opera<br>ng tempe | •      | nditions (unless otherwise stated)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |     |                                               |  |

|---------|-----------------------------|--------|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------|--|

| Param   | Device Characteristics      | Min.   | Тур†                 | Max.   | Units                                                                                                                                               |     | Conditions                                    |  |

| No.     | Device Characteristics      | IVIII. | Турі                 | IVIAX. | Units                                                                                                                                               | VDD | Note                                          |  |

| D020E   | Power-down Base             | _      | 0.05                 | 9      | μА                                                                                                                                                  | 2.0 | WDT, BOR, Comparators, VREF and               |  |

|         | Current(IPD) <sup>(2)</sup> | _      | 0.15                 | 11     | μΑ                                                                                                                                                  | 3.0 | T1OSC disabled                                |  |

|         |                             | _      | 0.35                 | 15     | μΑ                                                                                                                                                  | 5.0 | 7                                             |  |

|         |                             | _      | 90                   | 500    | nA                                                                                                                                                  | 3.0 | -40°C ≤ TA ≤ +25°C                            |  |

| D021E   |                             | _      | 1.0                  | 17.5   | μΑ                                                                                                                                                  | 2.0 | WDT Current <sup>(1)</sup>                    |  |

|         |                             | _      | 2.0                  | 19     | μΑ                                                                                                                                                  | 3.0 | ]                                             |  |

|         |                             | _      | 3.0                  | 22     | μΑ                                                                                                                                                  | 5.0 | ]                                             |  |

| D022E   |                             | _      | 42                   | 65     | μΑ                                                                                                                                                  | 3.0 | BOR Current <sup>(1)</sup>                    |  |

|         |                             | _      | 85                   | 127    | μΑ                                                                                                                                                  | 5.0 |                                               |  |

| D023E   |                             | _      | 32                   | 45     | μΑ                                                                                                                                                  | 2.0 | Comparator Current <sup>(1)</sup> , both      |  |

|         |                             | _      | 60                   | 78     | μΑ                                                                                                                                                  | 3.0 | comparators enabled                           |  |

|         |                             | _      | 120                  | 160    | μΑ                                                                                                                                                  | 5.0 |                                               |  |

| D024E   |                             | _      | 30                   | 70     | μΑ                                                                                                                                                  | 2.0 | CVREF Current <sup>(1)</sup> (high range)     |  |

|         |                             | _      | 45                   | 90     | μΑ                                                                                                                                                  | 3.0 |                                               |  |

|         |                             | _      | 75                   | 120    | μА                                                                                                                                                  | 5.0 |                                               |  |

| D024AE* |                             | _      | 39                   | 91     | μΑ                                                                                                                                                  | 2.0 | CVREF Current <sup>(1)</sup> (low range)      |  |

|         |                             | _      | 59                   | 117    | μΑ                                                                                                                                                  | 3.0 |                                               |  |

|         |                             | _      | 98                   | 156    | μΑ                                                                                                                                                  | 5.0 |                                               |  |

| D025E   |                             | _      | 2.0                  | 18     | μΑ                                                                                                                                                  | 2.0 | T1OSC Current                                 |  |

|         |                             | _      | 2.5                  | 21     | μΑ                                                                                                                                                  | 3.0 |                                               |  |

|         |                             |        | 3.0                  | 24     | μΑ                                                                                                                                                  | 5.0 |                                               |  |

| D026E   |                             | _      | 0.30                 | 12     | μΑ                                                                                                                                                  | 3.0 | A/D Current <sup>(1)</sup> , no conversion in |  |

|         |                             | _      | 0.36                 | 16     | μΑ                                                                                                                                                  | 5.0 | progress                                      |  |

| D027E   |                             |        | 90                   | 130    | μΑ                                                                                                                                                  | 3.0 | VP6 Current                                   |  |

|         |                             | _      | 125                  | 170    | μΑ                                                                                                                                                  | 5.0 |                                               |  |

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

- **4:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral Δ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

- 5: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

# TABLE 17-15: A/D CONVERTER (ADC) CHARACTERISTICS:

Standard Operating Conditions (unless otherwise stated)

Operating temperature -40°C ≤ TA ≤ +125°C

| Param | Sym. | Characteristic                                       | Min. | Typ†  | Max.    | Units | Conditions                                                       |

|-------|------|------------------------------------------------------|------|-------|---------|-------|------------------------------------------------------------------|

| No.   | -,   |                                                      |      | -71-1 |         |       |                                                                  |

| AD01  | NR   | Resolution                                           | —    |       | 10 bits | bit   |                                                                  |

| AD02  | EIL  | Integral Error                                       | _    | _     | ±1      | LSb   | VREF = 5.12V                                                     |

| AD03  | EDL  | Differential Error                                   | _    | ı     | ±1      | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                      |

| AD04  | EOFF | Offset Error                                         | _    | _     | ±1      | LSb   | VREF = 5.12V                                                     |

| AD04A |      |                                                      | _    | +1.5  | +3.0    | LSb   | (PIC16F677 only)                                                 |

| AD07  | Egn  | Gain Error                                           | _    | _     | ±1      | LSb   | VREF = 5.12V                                                     |

| AD06  | VREF | Reference Voltage <sup>(3)</sup>                     | 2.2  | _     | _       | V     |                                                                  |

| AD06A |      |                                                      | 2.5  |       | VDD     |       | Absolute minimum to ensure 1 LSb accuracy                        |

| AD07  | Vain | Full-Scale Range                                     | Vss  | _     | VREF    | V     |                                                                  |

| AD08  | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | _    | _     | 10      | kΩ    |                                                                  |

| AD09* | IREF | VREF Input Current <sup>(3)</sup>                    | 10   | _     | 1000    | μА    | During VAIN acquisition. Based on differential of VHOLD to VAIN. |

|       |      |                                                      | _    | _     | 50      | μΑ    | During A/D conversion cycle                                      |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

- **4:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

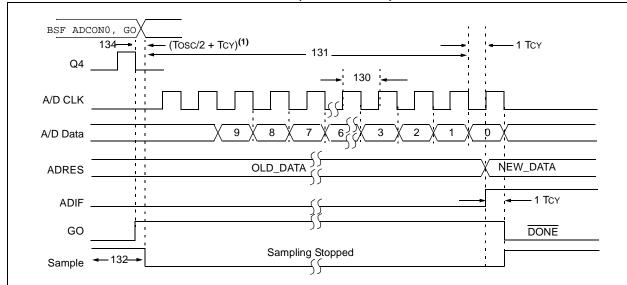

# FIGURE 17-19: A/D CONVERSION TIMING (SLEEP MODE)

Note 1: If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

# TABLE 1: A/D CONVERSION REQUIREMENTS (SLEEP MODE)

# Standard Operating Conditions (unless otherwise stated)

Operating Temperature -40°C ≤ TA ≤ +125°C

| Param<br>No. | Sym. | Characteristic                                                  | Min. | Тур†         | Max. | Units | Conditions                                                                                                                                                                                                  |  |

|--------------|------|-----------------------------------------------------------------|------|--------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 130*         | TAD  | A/D Internal RC                                                 | 0.0* | 0.0          | 0.0* |       | ADCS<1:0> = 11 (RC mode)                                                                                                                                                                                    |  |

|              |      | Oscillator Period                                               | 3.0* | 6.0          | 9.0* | μS    | At VDD = 2.5V                                                                                                                                                                                               |  |

|              |      |                                                                 | 2.0* | 4.0          | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                               |  |

| 131          | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _    | 11           |      | TAD   |                                                                                                                                                                                                             |  |

| 132*         | TACQ | Acquisition Time                                                | (2)  | 11.5         | _    | μS    |                                                                                                                                                                                                             |  |

|              |      |                                                                 | 5*   | _            | _    | μ\$   | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 4.1 mV @ 4.096V) from the last sampled voltage (as stored on CHOLD). |  |

| 134          | Tgo  | Q4 to A/D Clock<br>Start                                        | _    | Tosc/2 + Tcy | _    | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |  |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: ADRES register may be read on the following TcY cycle.

- 2: See Table 9-1 for minimum conditions.

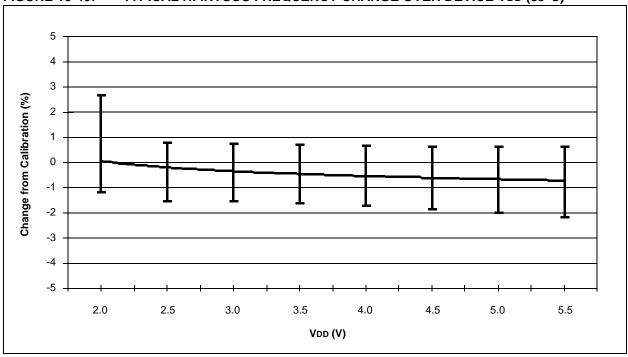

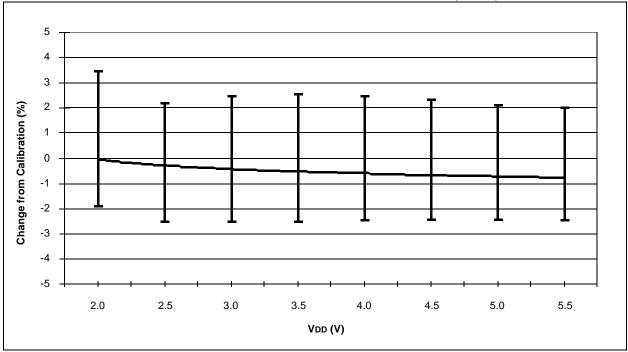

FIGURE 18-40: TYPICAL HFINTOSC FREQUENCY CHANGE OVER DEVICE VDD (85°C)

FIGURE 18-41: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (125°C)

# 19.0 PACKAGING INFORMATION

# 19.1 Package Marking Information

20-Lead PDIP

20-Lead SOIC (7.50 mm)

20-Lead SSOP

20-Lead QFN

Example

Example

Example

Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

B Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

te: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

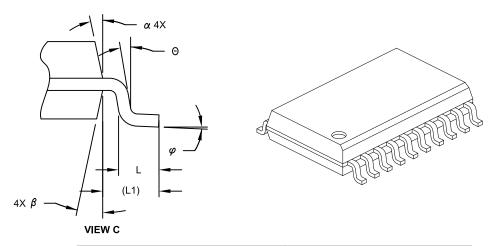

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |

|--------------------------|-------------|-----------|-----|------|--|

| Dimension Lim            | nits        | MIN       | NOM | MAX  |  |

| Number of Pins           | N           | 20        |     |      |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |

| Overall Height           | Α           | -         | -   | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -   | ı    |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |

| Overall Length           | D           | 12.80 BSC |     |      |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |

| Lead Angle               | Θ           | 0°        | -   | ı    |  |

| Foot Angle               | $\varphi$   | 0°        | -   | 8°   |  |

| Lead Thickness           | С           | 0.20      | -   | 0.33 |  |

| Lead Width               | b           | 0.31      | _   | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | _   | 15°  |  |

## Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-094C Sheet 2 of 2

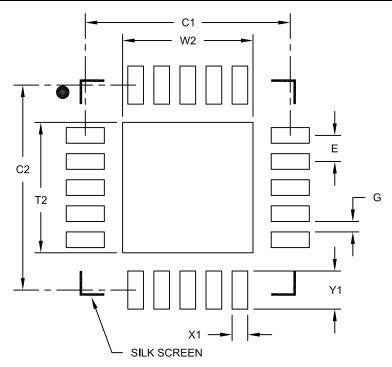

20-Lead Plastic Quad Flat, No Lead Package (ML) - 4x4 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | Е           | 0.50 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 2.50 |

| Optional Center Pad Length | T2          |          |      | 2.50 |

| Contact Pad Spacing        | C1          |          | 3.93 |      |

| Contact Pad Spacing        | C2          |          | 3.93 |      |

| Contact Pad Width          | X1          |          |      | 0.30 |

| Contact Pad Length         | Y1          |          |      | 0.73 |

| Distance Between Pads      | G           | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2126A