#### Microchip Technology - PIC16F687T-I/SO Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f687t-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table of Contents

| 1.0   | Device Overview                                                           | 9   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                       | 24  |

| 3.0   | Oscillator Module (With Fail-Safe Clock Monitor)                          | 45  |

| 4.0   | I/O Ports                                                                 |     |

| 5.0   | Timer0 Module                                                             | 79  |

| 6.0   | Timer1 Module with Gate Control                                           | 82  |

| 7.0   | Timer2 Module                                                             | 89  |

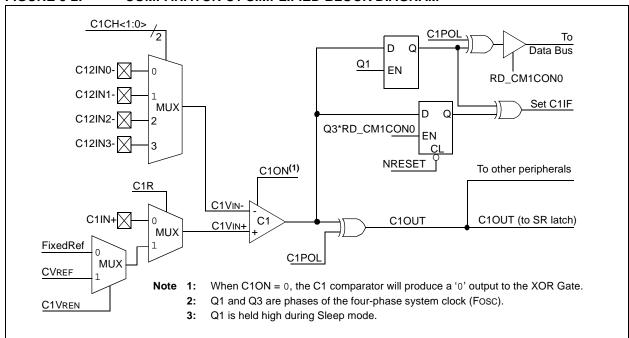

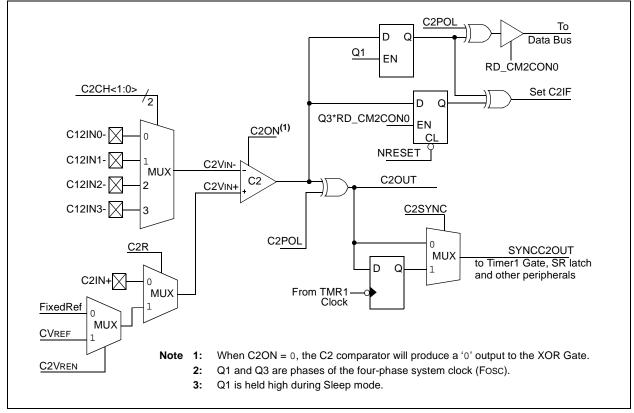

| 8.0   | Comparator Module                                                         | 91  |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                  |     |

| 10.0  | Data EEPROM and Flash Program Memory Control                              | 117 |

| 11.0  | Enhanced Capture/Compare/PWM Module                                       | 125 |

| 12.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 148 |

| 13.0  | SSP Module Overview                                                       | 175 |

| 14.0  | Special Features of the CPU                                               | 193 |

| 15.0  | Instruction Set Summary                                                   | 212 |

| 16.0  | Development Support                                                       |     |

| 17.0  | Electrical Specifications                                                 |     |

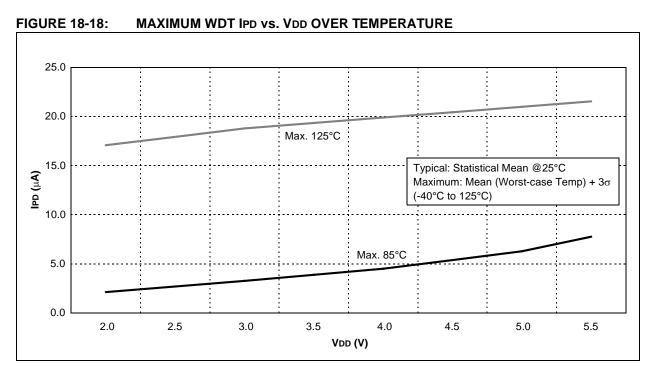

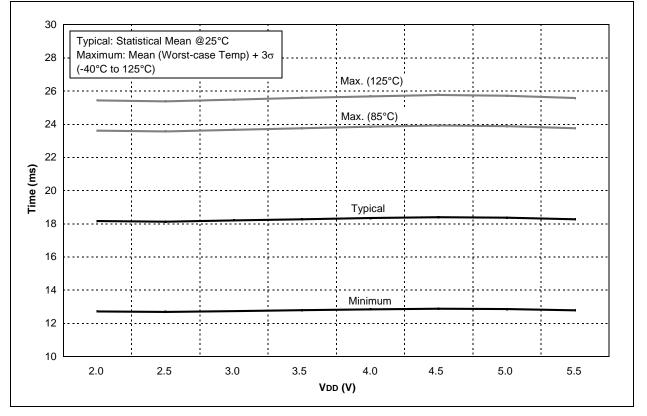

| 18.0  | DC and AC Characteristics Graphs and Tables                               | 258 |

| 19.0  | Packaging Information                                                     | 285 |

| The M | Vicrochip Web Site                                                        | 295 |

|       | omer Change Notification Service                                          |     |

| Custo | omer Support                                                              | 295 |

| Produ | uct Identification System                                                 | 296 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

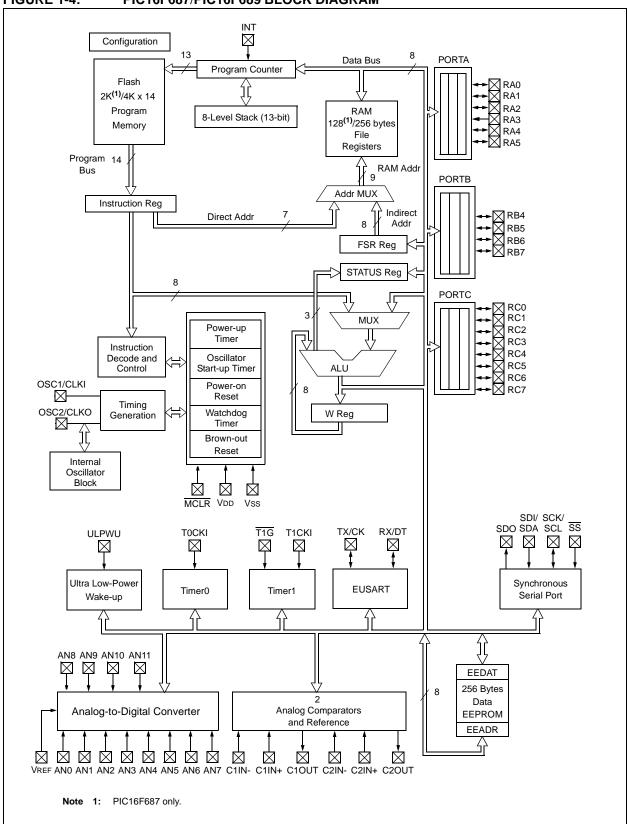

#### FIGURE 1-4: PIC16F687/PIC16F689 BLOCK DIAGRAM

#### TABLE 1-1: PINOUT DESCRIPTION – PIC16F631

| Name                                                              | Function   | Input<br>Type | Output<br>Type                                                                                  | Description                                                                                    |

|-------------------------------------------------------------------|------------|---------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| RA0/C1IN+/ICSPDAT/ULPWU                                           | RA0        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | C1IN+      | AN            | —                                                                                               | Comparator C1 non-inverting input.                                                             |

|                                                                   | ICSPDAT    | ST            | CMOS                                                                                            | ICSP™ Data I/O.                                                                                |

|                                                                   | ULPWU      | AN            |                                                                                                 | Ultra Low-Power Wake-up input.                                                                 |

| RA1/C12IN0-/ICSPCLK                                               | RA1        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | C12IN0-    | AN            | _                                                                                               | Comparator C1 or C2 inverting input.                                                           |

|                                                                   | ICSPCLK    | ST            | —                                                                                               | ICSP™ clock.                                                                                   |

| RA2/T0CKI/INT/C1OUT                                               | RA2        | ST            | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | T0CKI      | ST            | —                                                                                               | Timer0 clock input.                                                                            |

|                                                                   | INT        | ST            | —                                                                                               | External interrupt pin.                                                                        |

|                                                                   | C10UT      |               | CMOS                                                                                            | Comparator C1 output.                                                                          |

| RA3/MCLR/Vpp                                                      | RA3        | TTL           | —                                                                                               | General purpose input. Individually controlled interrupt-on-<br>change.                        |

|                                                                   | MCLR       | ST            | _                                                                                               | Master Clear with internal pull-up.                                                            |

|                                                                   | VPP        | ΗV            | _                                                                                               | Programming voltage.                                                                           |

| RA4/T1G/OSC2/CLKOUT                                               | RA4        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | T1G        | ST            | —                                                                                               | Timer1 gate input.                                                                             |

|                                                                   | OSC2       | —             | XTAL                                                                                            | Crystal/Resonator.                                                                             |

|                                                                   | CLKOUT     | _             | CMOS                                                                                            | Fosc/4 output.                                                                                 |

| RA5/T1CKI/OSC1/CLKIN                                              | RA5        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

|                                                                   | T1CKI      | ST            | —                                                                                               | Timer1 clock input.                                                                            |

|                                                                   | OSC1       | XTAL          | _                                                                                               | Crystal/Resonator.                                                                             |

|                                                                   | CLKIN      | ST            | —                                                                                               | External clock input/RC oscillator connection.                                                 |

| RB4                                                               | RB4        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RB5                                                               | RB5        | TTL           | CMOS General purpose I/O. Individually controlled interrupt-on<br>Individually enabled pull-up. |                                                                                                |

| RB6                                                               | RB6        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RB7                                                               | RB7        | TTL           | CMOS                                                                                            | General purpose I/O. Individually controlled interrupt-on-change Individually enabled pull-up. |

| RC0/C2IN+                                                         | RC0        | ST            | CMOS                                                                                            | General purpose I/O.                                                                           |

|                                                                   | C2IN+      | AN            | _                                                                                               | Comparator C2 non-inverting input.                                                             |

| RC1/C12IN1-                                                       | RC1        | ST            | CMOS                                                                                            | General purpose I/O.                                                                           |

|                                                                   | C12IN1-    | AN            | 1 —                                                                                             | Comparator C1 or C2 inverting input.                                                           |

| RC2/C12IN2-                                                       | RC2        | ST            | CMOS                                                                                            | General purpose I/O.                                                                           |

|                                                                   | C12IN2-    | AN            | _                                                                                               | Comparator C1 or C2 inverting input.                                                           |

| RC3/C12IN3-                                                       | RC3        | ST            | CMOS                                                                                            | General purpose I/O.                                                                           |

|                                                                   | C12IN3-    | AN            | —                                                                                               | Comparator C1 or C2 inverting input.                                                           |

| RC4/C2OUT                                                         | RC4        | ST            | CMOS                                                                                            | General purpose I/O.                                                                           |

|                                                                   | C2OUT      | —             | CMOS                                                                                            | Comparator C2 output.                                                                          |

| RC5                                                               | RC5        | ST            | CMOS                                                                                            | General purpose I/O.                                                                           |

| Legend: AN = Analog inpu<br>TTL = TTL compat<br>HV = High Voltage | ible input | ST=           |                                                                                                 | compatible input or output<br>Trigger input with CMOS levels                                   |

| Description                                          |  |  |  |

|------------------------------------------------------|--|--|--|

| dividually controlled interrupt-on-<br>bled pull-up. |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

| dividually controlled interrupt-on-<br>bled pull-up. |  |  |  |

| output.                                              |  |  |  |

| lock.                                                |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

| input.                                               |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

| egative input.                                       |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

| egative input.                                       |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

| egative input.                                       |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

|                                                      |  |  |  |

| c                                                    |  |  |  |

#### **TABLE 1-4:** PINOUT DESCRIPTION - PIC16F687/PIC16F689 (CONTINUED)

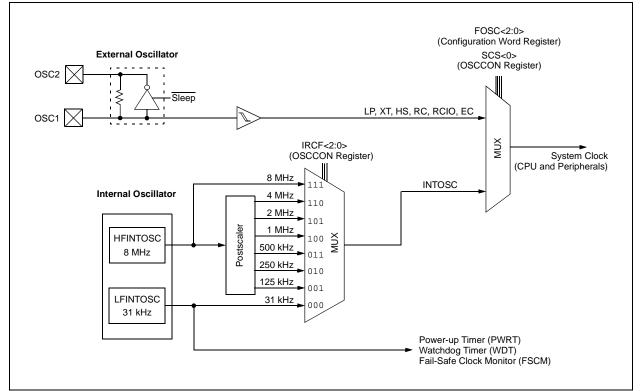

# 3.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 3.1 Overview

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 3-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured from one of two internal oscillators, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

The Oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The internal clock can be generated from two internal oscillators. The HFINTOSC is a calibrated highfrequency oscillator. The LFINTOSC is an uncalibrated low-frequency oscillator.

#### FIGURE 3-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

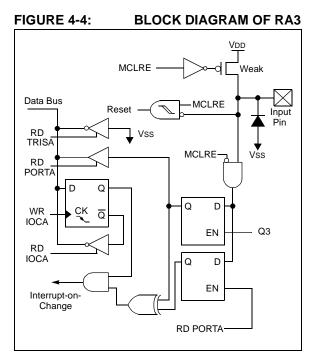

#### 4.2.5.4 RA3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The RA3/ MCLR/VPP pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

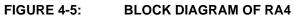

#### 4.2.5.5 RA4/AN3/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The RA4/ AN3/T1G/OSC2/CLKOUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a Timer1 gate input

- a crystal/resonator connection

- · a clock output

- 2: With CLKOUT option.

- 3: ANSEL determines Analog Input mode.

- 4: Not implemented on PIC16F631.

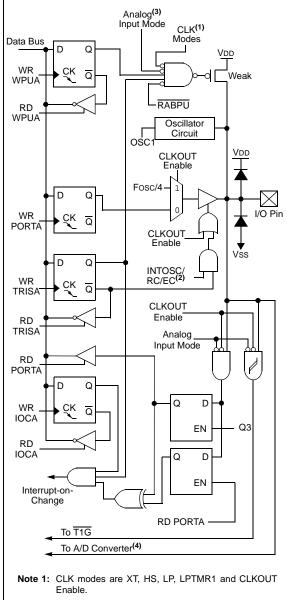

#### 4.4.3.4 RB7/TX/CK

Figure 4-10 shows the diagram for this pin. The RB7/  $TX/CK^{(1)}$  pin is configurable to function as one of the following:

- a general purpose I/O

- an asynchronous serial output

- a synchronous clock I/O

Note 1: TX and CK are available on PIC16F687/ PIC16F689/PIC16F690 only.

#### FIGURE 4-10: BLOCK DIAGRAM OF RB7

### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 9.2.6 "A/D Conversion   |

|       | Procedure".                              |

#### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete Analog-to-Digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

| Note: | A device Reset forces all registers to their         |

|-------|------------------------------------------------------|

|       | Reset state. Thus, the ADC module is                 |

|       | turned off and any pending conversion is terminated. |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

An ECCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

#### See Section 11.0 "Enhanced Capture/Compare/ PWM Module" for more information.

#### 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: See Section 9.3 "A/D Acquisition Requirements".

| Name   | Bit 7     | Bit 6        | Bit 5     | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|--------------|-----------|--------|--------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0 | ADFM      | VCFG         | CHS3      | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 | —         | ADCS2        | ADCS1     | ADCS0  | _      | _      | _       | -      | -000                 | -000                            |

| ANSEL  | ANS7      | ANS6         | ANS5      | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH | —         | —            | —         | —      | ANS11  | ANS10  | ANS9    | ANS8   | 1111                 | 1111                            |

| ADRESH | A/D Resul | t Register H | ligh Byte |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul | t Register L | ow Byte   |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE       | PEIE         | TOIE      | INTE   | RABIE  | T0IF   | INTF    | RABIF  | 0000 000x            | x000 000x                       |

| PIE1   | —         | ADIE         | RCIE      | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | -000 0000            | -000 0000                       |

| PIR1   | _         | ADIF         | RCIF      | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | -000 0000            | -000 0000                       |

| PORTA  | —         | —            | RA5       | RA4    | RA3    | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| PORTB  | RB7       | RB6          | RB5       | RB4    | _      | _      | _       | -      | xxxx                 | uuuu                            |

| PORTC  | RC7       | RC6          | RC5       | RC4    | RC3    | RC2    | RC1     | RC0    | xxxx xxxx            | uuuu uuuu                       |

| TRISA  | —         | _            | TRISA5    | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| TRISB  | TRISB7    | TRISB6       | TRISB5    | TRISB4 | —      | —      | —       | —      | 1111                 | 1111                            |

| TRISC  | TRISC7    | TRISC6       | TRISC5    | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

#### TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                    |            |                             |                  |            |                             |

|--------|-------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |                                                      |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             | Fosc = 8.000 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00                                                 | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        | 300.0            | 0.00       | 6666                        |

| 1200   | 1200              | -0.01                                                | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        | 1200             | -0.02      | 1666                        |

| 2400   | 2400              | 0.02                                                 | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        | 2401             | 0.04       | 832                         |

| 9600   | 9597              | -0.03                                                | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         | 9615             | 0.16       | 207                         |

| 10417  | 10417             | 0.00                                                 | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         | 10417            | 0          | 191                         |

| 19.2k  | 19.23k            | 0.16                                                 | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         | 19.23k           | 0.16       | 103                         |

| 57.6k  | 57.47k            | -0.22                                                | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          | 57.14k           | -0.79      | 34                          |

| 115.2k | 116.3k            | 0.94                                                 | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          | 117.6k           | 2.12       | 16                          |

|        |                  | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                  |            |                             |                  |            |                             |

|--------|------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |                                                      |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.01                                                 | 3332                        | 300.0             | 0.00       | 3071                        | 299.9            | -0.02      | 1666                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200             | 0.04                                                 | 832                         | 1200              | 0.00       | 767                         | 1199             | -0.08      | 416                         | 1202             | 0.16       | 207                         |

| 2400   | 2398             | 0.08                                                 | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         |

| 9600   | 9615             | 0.16                                                 | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          |

| 10417  | 10417            | 0.00                                                 | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16                                                 | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 25                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 58.82k           | 2.12                                                 | 16                          | 57.60k            | 0.00       | 15                          | 55.56k           | -3.55      | 8                           | —                | _          | _                           |

| 115.2k | 111.1k           | -3.55                                                | 8                           | 115.2k            | 0.00       | 7                           | _                | —          | _                           | _                | —          | —                           |

### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

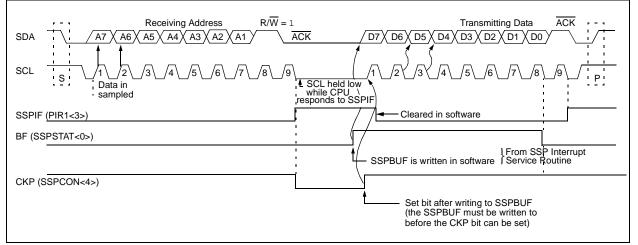

#### 13.12.4 TRANSMISSION

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RB6/SCK/SCL is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RB6/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 13-10). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the ACK pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not ACK), then the data transfer is complete. When the ACK is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the Start bit. If the SDA line was low (ACK), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RB6/SCK/SCL should be enabled by setting bit CKP.

#### 14.6 Power-Down Mode (Sleep)

The Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit in the STATUS register is cleared.

- TO bit is set.

- Oscillator driver is turned off.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or Vss, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are highimpedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pullups on PORTA should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level.

Note: It should be noted that a Reset generated by a WDT time-out does not drive MCLR pin low.

#### 14.6.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from RA2/INT pin, PORTA change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT Wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. ECCP Capture mode interrupt.

- 3. A/D conversion (when A/D clock source is FRC).

- 4. EEPROM write operation completion.

- 5. Comparator output changes state.

- 6. Interrupt-on-change.

- 7. External Interrupt from INT pin.

- 8. EUSART Break detect, I<sup>2</sup>C slave.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is |

|-------|-----------------------------------------------|

|       | cleared), but any interrupt source has both   |

|       | its interrupt enable bit and the              |

|       | corresponding interrupt flag bits set, the    |

|       | device will immediately wake-up from          |

|       | Sleep. The SLEEP instruction is completely    |

|       | executed.                                     |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 14.6.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### 15.2 Instruction Descriptions

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

|                  |                                                                     |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label]BSF f,b                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |  |  |  |

| Status Affected: | None                                                                |  |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |  |  |

| ANDLW            | AND literal with W                                                                                                   |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDLW k                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                    |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |  |  |  |  |  |

| Status Affected: | Z                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |  |  |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                   |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                         |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                         |  |  |  |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                        |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |  |  |  |  |

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

AND W with f

ANDWF

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| MOVWF            | Move W to f                                                                                       |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                          |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                 |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                             |  |  |  |  |  |

| Status Affected: | None                                                                                              |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'.                                                        |  |  |  |  |  |

| Words:           | 1                                                                                                 |  |  |  |  |  |

| Cycles:          | 1                                                                                                 |  |  |  |  |  |

| Example:         | MOVW OPTION<br>F                                                                                  |  |  |  |  |  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

### 16.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 16.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

### 17.0 ELECTRICAL SPECIFICATIONS

### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                            | 40° to +125°C        |

|-----------------------------------------------------------|----------------------|

| Storage temperature                                       | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                        | 0.3V to +6.5V        |

| Voltage on MCLR with respect to Vss                       | 0.3V to +13.5V       |

| Voltage on all other pins with respect to Vss             | 0.3V to (VDD + 0.3V) |

| Total power dissipation <sup>(1)</sup>                    | 800 mW               |

| Maximum current out of Vss pin                            |                      |

| Maximum current into VDD pin                              |                      |

| Input clamp current, Iικ (Vi < 0 or Vi > VDD)             | ± 20 mA              |

| Output clamp current, loк (Vo < 0 or Vo >VDD)             | ± 20 mA              |

| Maximum output current sunk by any I/O pin                | 25 mA                |

| Maximum output current sourced by any I/O pin             | 25 mA                |

| Maximum current sunk by PORTA, PORTB and PORTC (combined) | 200 mA               |

| Maximum current sourced PORTA, PORTB and PORTC (combined) | 200 mA               |

**Note 1:** Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to Vss.

| Param<br>No. | Symbol  | Characteristic  |              |      | Тур. | Max. | Units | Conditions                   |

|--------------|---------|-----------------|--------------|------|------|------|-------|------------------------------|

| 90*          | TSU:STA | Start condition | 100 kHz mode | 4700 | —    |      | ns    | Only relevant for Repeated   |

|              |         | Setup time      | 400 kHz mode | 600  |      | _    |       | Start condition              |

| 91*          | THD:STA | Start condition | 100 kHz mode | 4000 |      | _    | ns    | After this period, the first |

|              |         | Hold time       | 400 kHz mode | 600  | _    | _    |       | clock pulse is generated     |

| 92*          | TSU:STO | Stop condition  | 100 kHz mode | 4700 | —    | _    | ns    |                              |

|              |         | Setup time      | 400 kHz mode | 600  | _    | _    |       |                              |

| 93           | THD:STO | Stop condition  | 100 kHz mode | 4000 | _    | _    | ns    |                              |

|              |         | Hold time       | 400 kHz mode | 600  |      | _    |       |                              |

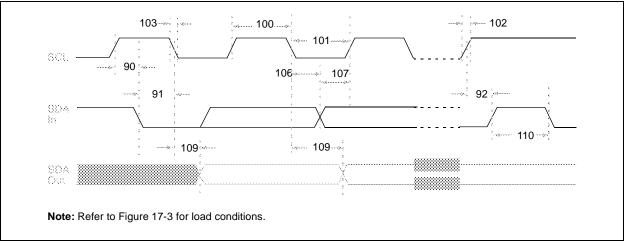

### TABLE 17-13: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

### FIGURE 17-17: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

#### TABLE 17-15: A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                      |            |      |         |       |                                                                     |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------------|------|---------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                       | Min.       | Тур† | Max.    | Units | Conditions                                                          |

| AD01                                                                                                                 | NR   | Resolution                                           | —          |      | 10 bits | bit   |                                                                     |

| AD02                                                                                                                 | EIL  | Integral Error                                       | —          |      | ±1      | LSb   | VREF = 5.12V                                                        |

| AD03                                                                                                                 | Edl  | Differential Error                                   | —          |      | ±1      | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |

| AD04                                                                                                                 | EOFF | Offset Error                                         | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |

| AD04A                                                                                                                |      |                                                      | —          | +1.5 | +3.0    | LSb   | (PIC16F677 only)                                                    |

| AD07                                                                                                                 | Egn  | Gain Error                                           | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |

| AD06<br>AD06A                                                                                                        | Vref | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.5 | _    | <br>Vdd | V     | Absolute minimum to ensure 1 LSb accuracy                           |

| AD07                                                                                                                 | Vain | Full-Scale Range                                     | Vss        | _    | Vref    | V     |                                                                     |

| AD08                                                                                                                 | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | _          | _    | 10      | kΩ    |                                                                     |

| AD09*                                                                                                                | IREF | VREF Input Current <sup>(3)</sup>                    | 10         | _    | 1000    | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|                                                                                                                      |      |                                                      | _          | _    | 50      | μA    | During A/D conversion cycle                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- **2:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

- 4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.