#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f689-e-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

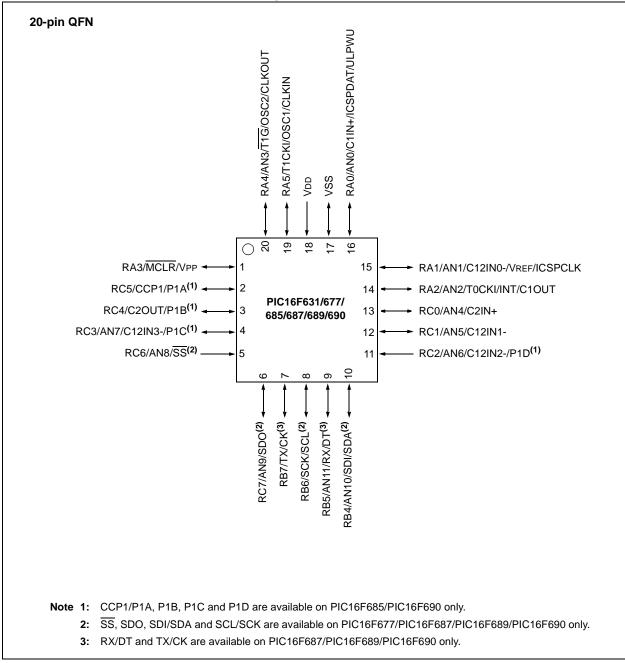

#### PIC16F631/677/685/687/689/690 Pin Diagram (QFN)

| GURE 2-7:                              | File                       | F687/PIC16F68                                          | File              |                                                          |              |                       | File         |

|----------------------------------------|----------------------------|--------------------------------------------------------|-------------------|----------------------------------------------------------|--------------|-----------------------|--------------|

|                                        |                            |                                                        |                   |                                                          | File         |                       | File         |

| Indirect addr. (1)                     | Address                    | ladias et e dela (1)                                   | Address           | ladias et e dala (1)                                     | Address      | Indinent ender (1)    | Addres       |

|                                        |                            | Indirect addr. <sup>(1)</sup>                          |                   | Indirect addr. <sup>(1)</sup>                            |              | Indirect addr. (1)    |              |

| TMR0<br>PCL                            | 01h                        | OPTION_REG<br>PCL                                      | 81h<br>82b        | TMR0<br>PCL                                              | 101h<br>102h | OPTION_REG<br>PCL     | 181h         |

| STATUS                                 | 02h<br>03h                 | STATUS                                                 | 82h<br>83h        | STATUS                                                   | 102h<br>103h | STATUS                | 182h<br>183h |

| FSR                                    | -                          | FSR                                                    |                   | FSR                                                      |              | FSR                   |              |

|                                        | 04h                        |                                                        | 84h               | PORTA                                                    | 104h<br>105h |                       | 184h         |

| PORTA<br>PORTB                         | 05h<br>06h                 | TRISA<br>TRISB                                         | 85h<br>86h        | PORTA                                                    | 105h<br>106h | TRISA<br>TRISB        | 185h<br>186h |

| PORTE                                  | 00n<br>07h                 | TRISE                                                  | 87h               | PORTE                                                    | 106h<br>107h | TRISE                 | 187h         |

| FURIC                                  | 0711<br>08h                | TRIBC                                                  | 88h               | FORTC                                                    | 107h<br>108h | TRISC                 | 188h         |

|                                        | 09h                        |                                                        | 89h               |                                                          | 109h         |                       | 189h         |

| PCLATH                                 | 0Ah                        | PCLATH                                                 | 8Ah               | PCLATH                                                   | 1031<br>10Ah | PCLATH                | 18Ah         |

| INTCON                                 | 0Bh                        | INTCON                                                 | 8Bh               | INTCON                                                   | 10An<br>10Bh | INTCON                | 18Bh         |

| PIR1                                   | 0Ch                        | PIE1                                                   | 8Ch               | EEDAT                                                    | 10Dh         | EECON1                | 18Ch         |

|                                        | -                          |                                                        |                   |                                                          |              | EECON2 <sup>(1)</sup> |              |

| PIR2                                   | 0Dh                        | PIE2                                                   | 8Dh               | EEADR                                                    | 10Dh         | EECONZY               | 18Dh         |

| TMR1L                                  | 0Eh                        | PCON                                                   | 8Eh               | EEDATH <sup>(3)</sup>                                    | 10Eh         |                       | 18Eh         |

| TMR1H                                  | 0Fh                        | OSCCON                                                 | 8Fh               | EEADRH <sup>(3)</sup>                                    | 10Fh         |                       | 18Fh         |

| T1CON                                  | 10h                        | OSCTUNE                                                | 90h               |                                                          | 110h         |                       | 190h         |

|                                        | 11h                        |                                                        | 91h               |                                                          | 111h         |                       | 191h         |

|                                        | 12h                        | (2)                                                    | 92h               |                                                          | 112h         |                       | 192h         |

| SSPBUF                                 | 13h                        | SSPADD <sup>(2)</sup>                                  | 93h               |                                                          | 113h         |                       | 193h         |

| SSPCON                                 | 14h                        | SSPSTAT                                                | 94h               |                                                          | 114h         |                       | 194h         |

|                                        | 15h                        | WPUA                                                   | 95h               | WPUB                                                     | 115h         |                       | 195h         |

|                                        | 16h                        | IOCA                                                   | 96h               | IOCB                                                     | 116h         |                       | 196h         |

|                                        | 17h                        | WDTCON                                                 | 97h               |                                                          | 117h         |                       | 197h         |

| RCSTA                                  | 18h                        | TXSTA                                                  | 98h               | VRCON                                                    | 118h         |                       | 198h         |

| TXREG                                  | 19h                        | SPBRG                                                  | 99h               | CM1CON0                                                  | 119h         |                       | 199h         |

| RCREG                                  | 1Ah                        | SPBRGH                                                 | 9Ah               | CM2CON0                                                  | 11Ah         |                       | 19Ah         |

|                                        | 1Bh                        | BAUDCTL                                                | 9Bh               | CM2CON1                                                  | 11Bh         |                       | 19Bh         |

|                                        | 1Ch                        |                                                        | 9Ch               |                                                          | 11Ch         |                       | 19Ch         |

|                                        | 1Dh                        |                                                        | 9Dh               |                                                          | 11Dh         | 00001                 | 19Dh         |

| ADRESH                                 | 1Eh                        | ADRESL                                                 | 9Eh               | ANSEL                                                    | 11Eh         | SRCON                 | 19Eh         |

| ADCON0                                 | 1Fh                        | ADCON1                                                 | 9Fh               | ANSELH                                                   | 11Fh         |                       | 19Fh         |

| General<br>Purpose<br>Register         | 20h                        | General<br>Purpose<br>Register<br>32 Bytes<br>48 Bytes | A0h<br>BFh<br>C0h | General<br>Purpose<br>Register<br>80 Bytes<br>(PIC16F689 | 120h         |                       | 1A0h         |

| 96 Bytes                               |                            | (PIC16F689<br>only)                                    | EFh               | only)                                                    |              |                       |              |

|                                        | 7Fh                        | accesses<br>70h-7Fh                                    | F0h<br>FFh        | accesses<br>70h-7Fh                                      | 170h<br>17Fh | accesses<br>70h-7Fh   | 1F0h<br>1FFh |

| Bank 0                                 | 1                          | Bank 1                                                 | I                 | Bank 2                                                   | I            | Bank 3                |              |

| lote 1: Not a p<br>2: Addres<br>See Re | ohysical reg<br>s 93h also | •                                                      | P Mask (SS        | as '0'.<br>SPMSK) register u                             | nder certai  | n conditions.         |              |

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0               | R/W-0               | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIE <sup>(5)</sup> | RCIE <sup>(3)</sup> | TXIE <sup>(3)</sup> | SSPIE <sup>(4)</sup> | CCP1IE <sup>(2)</sup> | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:        |                                                                                                                 |                                                    |                                        |                    |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|--------------------|--|--|--|--|

| R = Read       | able bit                                                                                                        | W = Writable bit                                   | U = Unimplemented bit,                 | read as '0'        |  |  |  |  |

| -n = Value     | at POR                                                                                                          | '1' = Bit is set                                   | '0' = Bit is cleared                   | x = Bit is unknown |  |  |  |  |

| L : L <b>7</b> | 11                                                                                                              |                                                    |                                        |                    |  |  |  |  |

| bit 7          | -                                                                                                               | mented: Read as '0'                                | . –                                    |                    |  |  |  |  |

| bit 6          |                                                                                                                 | D Converter (ADC) Interrupt                        | t Enable bit                           |                    |  |  |  |  |

|                |                                                                                                                 | bles the ADC interrupt<br>bles the ADC interrupt   |                                        |                    |  |  |  |  |

| bit 5          |                                                                                                                 | USART Receive Interrupt Er                         | able hit(3)                            |                    |  |  |  |  |

| Dit J          |                                                                                                                 |                                                    |                                        |                    |  |  |  |  |

|                | <ol> <li>1 = Enables the EUSART receive interrupt</li> <li>0 = Disables the EUSART receive interrupt</li> </ol> |                                                    |                                        |                    |  |  |  |  |

| bit 4          |                                                                                                                 | JSART Transmit Interrupt Er                        |                                        |                    |  |  |  |  |

|                |                                                                                                                 | 1 = Enables the EUSART transmit interrupt          |                                        |                    |  |  |  |  |

|                | 0 = Disa                                                                                                        | bles the EUSART transmit ir                        | nterrupt                               |                    |  |  |  |  |

| bit 3          | SSPIE: S                                                                                                        | Synchronous Serial Port (SS                        | P) Interrupt Enable bit <sup>(4)</sup> |                    |  |  |  |  |

|                |                                                                                                                 | bles the SSP interrupt                             |                                        |                    |  |  |  |  |

|                |                                                                                                                 | bles the SSP interrupt                             |                                        |                    |  |  |  |  |

| bit 2          |                                                                                                                 | CCP1 Interrupt Enable bit <sup>(2</sup>            | )                                      |                    |  |  |  |  |

|                |                                                                                                                 | bles the CCP1 interrupt<br>bles the CCP1 interrupt |                                        |                    |  |  |  |  |

| bit 1          |                                                                                                                 | : Timer2 to PR2 Match Interr                       | upt Enable bit <sup>(1)</sup>          |                    |  |  |  |  |

|                |                                                                                                                 | bles the Timer2 to PR2 match                       | •                                      |                    |  |  |  |  |

|                |                                                                                                                 | 0 = Disables the Timer2 to PR2 match interrupt     |                                        |                    |  |  |  |  |

| bit 0          | TMR1IE:                                                                                                         | : Timer1 Overflow Interrupt E                      | Enable bit                             |                    |  |  |  |  |

|                |                                                                                                                 | oles the Timer1 overflow inte                      | •                                      |                    |  |  |  |  |

|                | 0 = Disa                                                                                                        | bles the Timer1 overflow inte                      | errupt                                 |                    |  |  |  |  |

| Note 1:        |                                                                                                                 | IC16F690 only.                                     |                                        |                    |  |  |  |  |

| 2:             |                                                                                                                 | IC16F689/PIC16F690 only.                           |                                        |                    |  |  |  |  |

| 3:             | PIC16F687/P                                                                                                     | IC16F689/PIC16F690 only.                           |                                        |                    |  |  |  |  |

4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

### 3.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

### 3.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word register (CONFIG).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

## 3.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

### 3.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear. When the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 3.4.1 "Oscillator Start-up Timer (OST)"**). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

## 3.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word register) = 1; Internal/External Switchover bit (Two-Speed Startup mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word register (CONFIG) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Twospeed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

#### 3.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

#### 4.0 I/O PORTS

There are as many as eighteen general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

#### 4.1 **PORTA and the TRISA Registers**

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 4-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Reading the PORTA register (Register 4-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write

#### **REGISTER 4-1:** PORTA: PORTA REGISTER

operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The ANSEL register must be initialized to Note: configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### EXAMPLE 4-1: **INITIALIZING PORTA**

| BCF   | STATUS, RP0; Bank 0        |

|-------|----------------------------|

| BCF   | STATUS, RP1;               |

| CLRF  | PORTA ;Init PORTA          |

| BSF   | STATUS, RP1; Bank 2        |

| CLRF  | ANSEL ;digital I/O         |

| BSF   | STATUS, RP0; Bank 1        |

| BCF   | STATUS, RP1;               |

| MOVLW | 0Ch ;Set RA<3:2> as inputs |

| MOVWF | TRISA ;and set RA<5:4,1:0> |

|       | ;as outputs                |

| BCF   | STATUS, RP0; Bank 0        |

|       |                            |

| U-0     | U-0 | R/W-x | R/W-x | R-x | R/W-x | R/W-x | R/W-x |

|---------|-----|-------|-------|-----|-------|-------|-------|

| —       | —   | RA5   | RA4   | RA3 | RA2   | RA1   | RA0   |

| bit 7   |     |       |       |     |       |       | bit 0 |

|         |     |       |       |     |       |       |       |

| Legend: |     |       |       |     |       |       |       |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | '0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                        |

|---------|-------------------------------------------------------------------|

| bit 5-0 | <b>RA&lt;5:0&gt;</b> : PORTA I/O Pin bit<br>1 = Port pin is > VIH |

|         | 0 = Port pin is < VIL                                             |

#### **REGISTER 4-2:** TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

TRISA<5:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

Note 1: TRISA<3> always reads '1'.

bit 5-0

TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes. 2:

## 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

## EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL        | TMR0                       | ;                             |

|----------------|----------------------------|-------------------------------|

| CLRWDT         |                            | ;Clear WDT                    |

| CLRF           | TMR0                       | ;Clear TMR0 and               |

|                |                            | ;prescaler                    |

| BANKSEL        | OPTION_REG                 | ;                             |

| BSF            | OPTION_REG,                | PSA;Select WDT                |

| CLRWDT         |                            | ;                             |

|                |                            |                               |

|                |                            | i                             |

| MOVLW          | b'11111000'                | ;<br>;Mask prescaler          |

| MOVLW<br>ANDWF | b'11111000'<br>OPTION_REG, | -                             |

|                | OPTION_REG,                | -                             |

| ANDWF          | OPTION_REG,                | W; bits<br>;Set WDT prescaler |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

## EXAMPLE 5-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT  | ;Clear WDT and                   |

|---------|----------------------------------|

|         | ;prescaler                       |

| BANKSEL | OPTION_REG ;                     |

| MOVLW   | b'11110000';Mask TMR0 select and |

| ANDWF   | OPTION_REG,W; prescaler bits     |

| IORLW   | b'00000011';Set prescale to 1:16 |

| MOVWF   | OPTION_REG ;                     |

|         |                                  |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

## 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in Section 17.0 "Electrical Specifications".

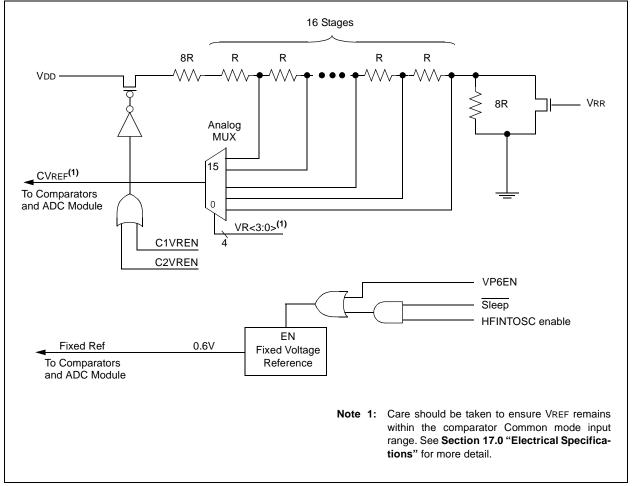

### 8.10 Comparator Voltage Reference

The comparator voltage reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- · Output clamped to Vss

- Ratiometric with VDD

- Fixed Reference (0.6)

The VRCON register (Register 8-5) controls the Voltage Reference module shown in Figure 8-8.

#### 8.10.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 8.10.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has two ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### EQUATION 8-1: CVREF OUTPUT VOLTAGE

VRR = 1 (low range):  $CVREF = (VR < 3:0 > /24) \times VDD$  VRR = 0 (high range):  $CVREF = (VDD/4) + (VR < 3:0 > \times VDD/32)$

The full range of Vss to VDD cannot be realized due to the construction of the module. See Figure 8-8.

#### 8.10.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by clearing the VP6EN bit of the VRCON register.

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 8.10.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 17.0 "Electrical Specifications"**.

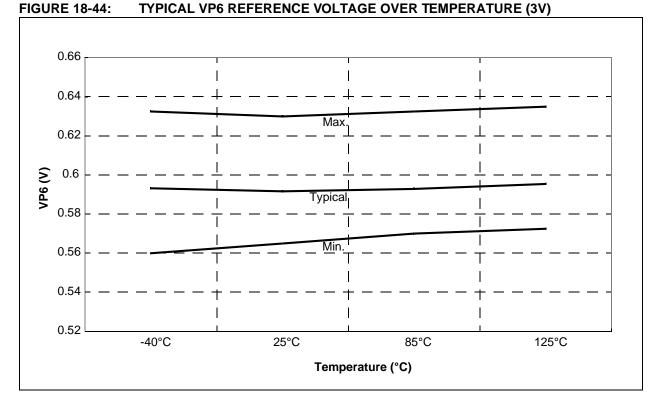

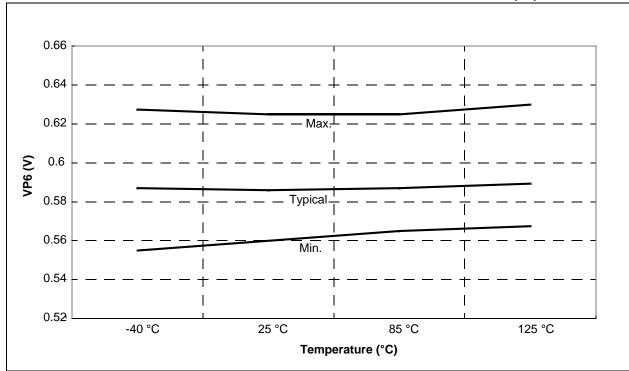

#### 8.10.5 FIXED VOLTAGE REFERENCE

The Fixed Voltage Reference is independent of VDD, with a nominal output voltage of 0.6V. This reference can be enabled by setting the VP6EN bit of the VRCON register to '1'. This reference is always enabled when the HFINTOSC oscillator is active.

#### 8.10.6 FIXED VOLTAGE REFERENCE STABILIZATION PERIOD

When the Fixed Voltage Reference module is enabled, it will require some time for the reference and its amplifier circuits to stabilize. The user program must include a small delay routine to allow the module to settle. See the electrical specifications section for the minimum delay requirement.

#### 8.10.7 VOLTAGE REFERENCE SELECTION

Multiplexers on the output of the Voltage Reference module enable selection of either the CVREF or Fixed Voltage Reference for use by the comparators.

Setting the C1VREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C1. Clearing the C1VREN bit selects the fixed voltage for use by C1.

Setting the C2VREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C2. Clearing the C2VREN bit selects the fixed voltage for use by C2.

When both the C1VREN and C2VREN bits are cleared, current flow in the CVREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

#### FIGURE 8-8: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| U-0                                                                  | R/W-0                           | R/W-0            | R/W-0 | U-0              | U-0  | U-0             | U-0   |  |  |  |

|----------------------------------------------------------------------|---------------------------------|------------------|-------|------------------|------|-----------------|-------|--|--|--|

| _                                                                    | ADCS2                           | ADCS1            | ADCS0 | —                |      | —               | _     |  |  |  |

| bit 7                                                                |                                 |                  |       |                  |      |                 | bit 0 |  |  |  |

|                                                                      |                                 |                  |       |                  |      |                 |       |  |  |  |

| Legend:                                                              |                                 |                  |       |                  |      |                 |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                 |                  |       |                  |      |                 |       |  |  |  |

| -n = Value at P                                                      | OR                              | '1' = Bit is set |       | '0' = Bit is cle | ared | x = Bit is unkn | iown  |  |  |  |

| bit 7<br>bit 6-4                                                     | it 7 Unimplemented: Read as '0' |                  |       |                  |      |                 |       |  |  |  |

| bit 3-0                                                              | Unimplemen                      | ted: Read as '   | 0'    |                  |      |                 |       |  |  |  |

|                                                                      |                                 |                  |       |                  |      |                 |       |  |  |  |

### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### 10.1.2 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDAT register; therefore, it can be read in the next instruction. EEDAT will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 10-1: DATA EEPROM READ

| BANKSEL | EEADR ;     |                         |

|---------|-------------|-------------------------|

| MOVF    | DATA_EE_ADD | R, W;                   |

| MOVWF   | EEADR       | ;Data Memory            |

|         |             | ;Address to read        |

| BANKSEL | EECON1      | ;                       |

| BCF     | EECON1, EEP | GD;Point to DATA memory |

| BSF     | EECON1, RD  | ;EE Read                |

| BANKSEL | EEDAT       | ;                       |

| MOVF    | EEDAT, W    | ;W = EEDAT              |

| BANKSEL | PORTA       | ;Bank 0                 |

|         |             |                         |

## 10.1.3 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDAT register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the specific sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

#### BANKSELEEADR MOVFDATA\_EE\_ADDR, W; MOVWFEEADR ;Data Memory Address to write MOVFDATA\_EE\_DATA, W; MOVWFEEDAT ;Data Memory Value to write BANKSELEECON1 ; BCF EECON1, EEPGD; Point to DATA memory BSF EECON1, WREN; Enable writes BCF INTCON, GIE ; Disable INTs. BTFSCINTCON, GIE;SEE AN576 GOTO\$-2 MOVLW55h ; Required Sequence MOVWFEECON2 ;Write 55h MOVLWAAh ; MOVWFEECON2 ;Write AAh BSF EECON1, WR ;Set WR bit to begin write BSF INTCON, GIE ; Enable INTs. SLEEP ;Wait for interrupt to signal write complete (optional) BCF EECON1, WREN; Disable writes BANKSEL0x00 ;Bank 0

#### EXAMPLE 10-2: DATA EEPROM WRITE

#### **TABLE 10-1:** SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name                  | Bit 7                 | Bit 6        | Bit 5           | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------|--------------|-----------------|---------------|---------|---------|---------|---------|----------------------|---------------------------------|

| EECON1                | EEPGD <sup>(1)</sup>  | —            | _               |               | WRERR   | WREN    | WR      | RD      | x x000               | 0 q000                          |

| EECON2                | EEPROM C              | ontrol Regis | ster 2 (not a p | hysical regis | ter)    |         |         |         |                      |                                 |

| EEADR                 | EEADR7 <sup>(2)</sup> | EEADR6       | EEADR5          | EEADR4        | EEADR3  | EEADR2  | EEADR1  | EEADR0  | 0000 0000            | 0000 0000                       |

| EEADRH <sup>(1)</sup> | _                     | -            | _               | _             | EEADRH3 | EEADRH2 | EEADRH1 | EEADRH0 | 0000                 | 0000                            |

| EEDAT                 | EEDAT7                | EEDAT6       | EEDAT5          | EEDAT4        | EEDAT3  | EEDAT2  | EEDAT1  | EEDAT0  | 0000 0000            | 0000 0000                       |

| EEDATH <sup>(1)</sup> | _                     | _            | EEDATH5         | EEDATH4       | EEDATH3 | EEDATH2 | EEDATH1 | EEDATH0 | 00 0000              | 00 0000                         |

| INTCON                | GIE                   | PEIE         | TOIE            | INTE          | RABIE   | T0IF    | INTF    | RABIF   | 0000 0000            | 0000 0000                       |

| PIE2                  | OSFIE                 | C2IE         | C1IE            | EEIE          | _       | _       | _       | _       | 0000                 | 0000                            |

| PIR2                  | OSFIF                 | C2IF         | C1IF            | EEIF          | -       | _       | _       | _       | 0000                 | 0000                            |

${\bf x}$  = unknown,  ${\bf u}$  = unchanged, – = unimplemented read as '0',  ${\bf q}$  = value depends upon condition. Shaded cells are not used by data EEPROM module. PIC16F685/PIC16F689/PIC16F690 only. Legend:

Note 1:

PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only. 2:

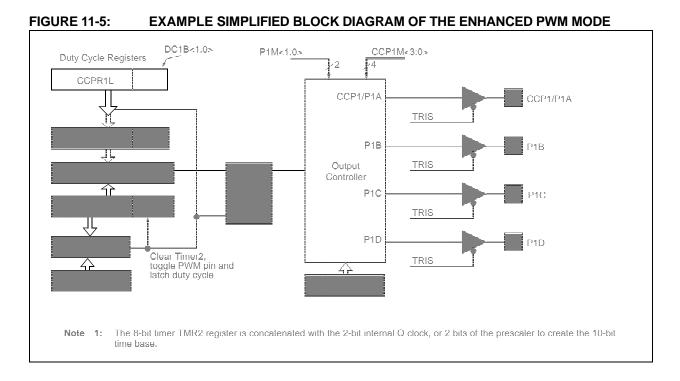

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- **3:** Any pin not used by an Enhanced PWM mode is available for alternate pin functions

#### TABLE 11-4: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M<1:0> | CCP1/P1A           | P1B                | P1C                | P1D                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

Note 1: Pulse Steering enables outputs in Single mode.

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                    |            |                             |                  |            |                             |  |  |

|--------|-------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 20.000 MHz |                                                      |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             | Fosc = 8.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 300.0             | 0.00                                                 | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        | 300.0            | 0.00       | 6666                        |  |  |

| 1200   | 1200              | -0.01                                                | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        | 1200             | -0.02      | 1666                        |  |  |

| 2400   | 2400              | 0.02                                                 | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        | 2401             | 0.04       | 832                         |  |  |

| 9600   | 9597              | -0.03                                                | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         | 9615             | 0.16       | 207                         |  |  |

| 10417  | 10417             | 0.00                                                 | 479                         | 10425             | 0.08       | 441                         | 10433              | 0.16       | 264                         | 10417            | 0          | 191                         |  |  |

| 19.2k  | 19.23k            | 0.16                                                 | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         | 19.23k           | 0.16       | 103                         |  |  |

| 57.6k  | 57.47k            | -0.22                                                | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          | 57.14k           | -0.79      | 34                          |  |  |

| 115.2k | 116.3k            | 0.94                                                 | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          | 117.6k           | 2.12       | 16                          |  |  |

|        |                  |            | BRG16 = 1                   |                   |            |                             |                  |            |                             |                  |            |                             |

|--------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 2.000 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 299.9            | -0.02      | 1666                        | 300.1            | 0.04       | 832                         |

| 1200   | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1199             | -0.08      | 416                         | 1202             | 0.16       | 207                         |

| 2400   | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         |

| 9600   | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          |

| 10417  | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          |

| 19.2k  | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 25                          | 19.23k           | 0.16       | 12                          |

| 57.6k  | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | 55.56k           | -3.55      | 8                           | —                | —          | _                           |

| 115.2k | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                | _          | —                           | _                | —          | —                           |

### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

### REGISTER 13-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0                                                                                                                      | R-0                                                                           | R-0                                               | R-0                | R-0                | R-0                 | R-0           |

|------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------|--------------------|--------------------|---------------------|---------------|

| SMP              | CKE                                                                                                                        | D/A                                                                           | Р                                                 | S                  | R/W                | UA                  | BF            |

| bit 7            |                                                                                                                            |                                                                               |                                                   |                    |                    |                     | bit (         |

|                  |                                                                                                                            |                                                                               |                                                   |                    |                    |                     |               |

| Legend:          |                                                                                                                            |                                                                               |                                                   |                    |                    | (                   |               |

| R = Readable b   |                                                                                                                            | W = Writable bit                                                              |                                                   |                    | iented bit, read a |                     |               |

| -n = Value at PC | DR                                                                                                                         | '1' = Bit is set                                                              |                                                   | '0' = Bit is clea  | ared               | x = Bit is unkno    | wn            |

| bit 7            | SPI Master mo<br>1 = Input data =<br>0 = Input data =<br>SPI Slave mod<br>SMP must be o<br>$I^2C^{TM}$ mode:               | sampled at end of sampled at middle                                           | data output ti<br>of data outpu<br>is used in Sla | ut time (Microwire | e)                 |                     |               |

| bit 6            | SPI mode. CKI<br>1 = Data transi<br>0 = Data transi<br>SPI mode. CKI<br>1 = Data transi<br>0 = Data transi<br>$l^2C$ mode: | mitted on rising ed<br>mitted on falling ed                                   | dge of SCK<br>dge of SCK (N<br>lge of SCK         |                    |                    |                     |               |

| bit 5            | 1 = Indicates the                                                                                                          | DRESS bit (I <sup>2</sup> C m<br>nat the last byte re<br>nat the last byte re | eceived or trar                                   |                    |                    |                     |               |

| bit 4            | SSPEN is clea<br>1 = Indicates th                                                                                          | red when the SSP                                                              | been detected                                     |                    |                    | tected last.        |               |

| bit 3            | SSPEN is clea<br>1 = Indicates th                                                                                          | red when the SSP                                                              | been detected                                     |                    |                    | ected last.         |               |

| bit 2            | This bit holds th                                                                                                          | RITE bit Information<br>ne R/W bit informa<br>rt bit, Stop bit or A           | tion following                                    |                    | match. This bit is | only valid from the | address match |

| bit 1            | 1 = Indicates th                                                                                                           | ldress bit (10-bit l <sup>2</sup><br>nat the user needs<br>bes not need to be | s to update the                                   |                    | SSPADD registe     | r                   |               |

| bit 0            | 1 = Receive co<br>0 = Receive not<br>$\frac{\text{Transmit (I}^2\text{C r})}{1 = \text{Transmit in}}$                      | and I <sup>2</sup> C modes):<br>omplete, SSPBUF<br>ot complete, SSPE          | BUF is empty<br>JF is full                        |                    |                    |                     |               |

|                  |                                                                                                                            | 689/PIC16F690 or                                                              | •                                                 |                    |                    |                     |               |

2: Does not update if receive was ignored.

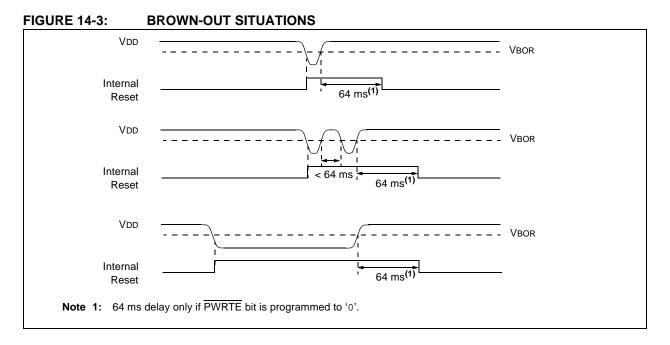

#### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

| RETFIE              | Return from Interrupt                                                                                                                                            | RETLW            | Return with literal in W                                                                                                                                                      |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ label ] RETFIE                                                                                                                                                 | Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      |

| Operands:           | None                                                                                                                                                             | Operands:        | $0 \le k \le 255$                                                                                                                                                             |

| Operation:          | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                          | Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  |

| Status Affected:    | None                                                                                                                                                             | Status Affected: | None                                                                                                                                                                          |

| Description:        | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE | Description:     | The W register is loaded with the<br>8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction. |

|                     | (INTCON<7>). This is a 2-cycle instruction.                                                                                                                      | Words:           | 1                                                                                                                                                                             |

| Words:              | instruction.<br>1                                                                                                                                                | Cycles:          | 2                                                                                                                                                                             |

| Cycles:<br>Example: | 2<br>RETFIE                                                                                                                                                      | Example:         | CALL TABLE;W contains<br>table<br>;offset value                                                                                                                               |

|                     | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                           | TABLE            | <pre>% now has<br/>;table value<br/>*<br/>ADDWF PC;W = offset<br/>RETLW k1;Begin table</pre>                                                                                  |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle instruc-<br>tion. |  |  |  |  |  |

RETLW k2 ;

**Before Instruction**

After Instruction

RETLW kn ; End of table

W = 0x07

W = value of k8

•

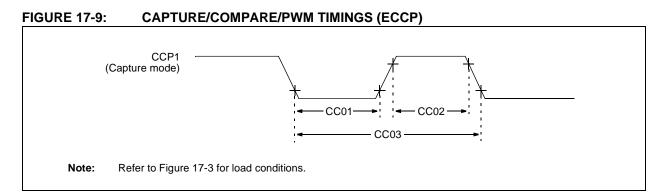

### TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                      |                |                       |      |      |       |                                       |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------------|--|--|--|

| Param<br>No. | Sym.                                                                                                                 | Character            | istic          | Min.                  | Тур† | Max. | Units | Conditions                            |  |  |  |

| CC01*        | TccL                                                                                                                 | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                       |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | —    | —    | ns    |                                       |  |  |  |

| CC02*        | ТссН                                                                                                                 | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                       |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | _    | —    | ns    |                                       |  |  |  |

| CC03*        | TccP                                                                                                                 | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale<br>value (1, 4 or<br>16) |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

© 2005-2015 Microchip Technology Inc.

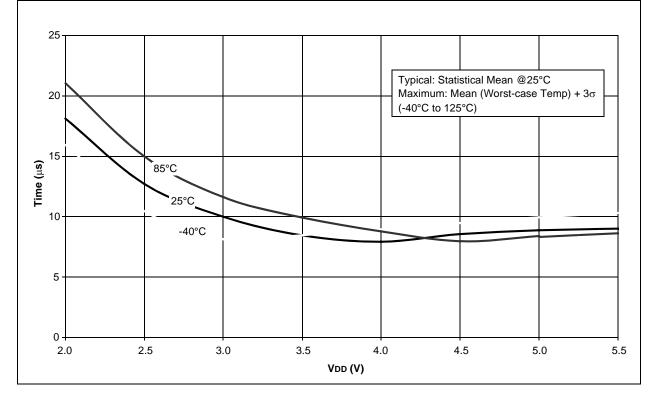

#### 16 Typical: Statistical Mean @25°C 14 Maximum: Mean (Worst-case Temp) + 3o (-40°C to 125°C) 85°C 12 25°C 10-Time (µs) -40°C 8 6 4 2 0 2.5 3.0 3.5 4.5 5.0 5.5 2.0 4.0 VDD (V)

#### FIGURE 18-36: TYPICAL HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

#### FIGURE 18-45: TYPICAL VP6 REFERENCE VOLTAGE OVER TEMPERATURE (5V)