Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f689-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table of Contents

| 1.0   | Device Overview                                                           | 9   |

|-------|---------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                       | 24  |

| 3.0   | Oscillator Module (With Fail-Safe Clock Monitor)                          | 45  |

| 4.0   | I/O Ports                                                                 |     |

| 5.0   | Timer0 Module                                                             | 79  |

| 6.0   | Timer1 Module with Gate Control                                           | 82  |

| 7.0   | Timer2 Module                                                             | 89  |

| 8.0   | Comparator Module                                                         | 91  |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                  |     |

| 10.0  | Data EEPROM and Flash Program Memory Control                              | 117 |

| 11.0  | Enhanced Capture/Compare/PWM Module                                       | 125 |

| 12.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 148 |

| 13.0  | SSP Module Overview                                                       | 175 |

| 14.0  | Special Features of the CPU                                               | 193 |

| 15.0  | Instruction Set Summary                                                   | 212 |

| 16.0  | Development Support                                                       |     |

| 17.0  | Electrical Specifications                                                 |     |

| 18.0  | DC and AC Characteristics Graphs and Tables                               | 258 |

| 19.0  | Packaging Information                                                     | 285 |

| The M | Vicrochip Web Site                                                        | 295 |

|       | omer Change Notification Service                                          |     |

| Custo | omer Support                                                              | 295 |

| Produ | uct Identification System                                                 | 296 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via Email at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Description                                          |  |  |

|------------------------------------------------------|--|--|

| dividually controlled interrupt-on-<br>bled pull-up. |  |  |

|                                                      |  |  |

|                                                      |  |  |

| dividually controlled interrupt-on-<br>bled pull-up. |  |  |

| output.                                              |  |  |

| lock.                                                |  |  |

|                                                      |  |  |

|                                                      |  |  |

| input.                                               |  |  |

|                                                      |  |  |

|                                                      |  |  |

| egative input.                                       |  |  |

|                                                      |  |  |

|                                                      |  |  |

| egative input.                                       |  |  |

|                                                      |  |  |

|                                                      |  |  |

| egative input.                                       |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

|                                                      |  |  |

| c                                                    |  |  |

#### **TABLE 1-4:** PINOUT DESCRIPTION - PIC16F687/PIC16F689 (CONTINUED)

| GURE 2-7:                              | File                       | F687/PIC16F68                                          | File              |                                                          |               |                       | File         |

|----------------------------------------|----------------------------|--------------------------------------------------------|-------------------|----------------------------------------------------------|---------------|-----------------------|--------------|

|                                        |                            |                                                        |                   |                                                          | File          |                       | File         |

| Indirect addr. (1)                     | Address                    | ladias et e dela (1)                                   | Address           | ladias et e dala (1)                                     | Address       | Indinent ender (1)    | Addres       |

|                                        |                            | Indirect addr. <sup>(1)</sup>                          |                   | Indirect addr. <sup>(1)</sup>                            |               | Indirect addr. (1)    |              |

| TMR0<br>PCL                            | 01h                        | OPTION_REG<br>PCL                                      | 81h<br>82b        | TMR0<br>PCL                                              | 101h<br>102h  | OPTION_REG<br>PCL     | 181h         |

| STATUS                                 | 02h<br>03h                 | STATUS                                                 | 82h<br>83h        | STATUS                                                   | 102h<br>103h  | STATUS                | 182h<br>183h |

| FSR                                    | -                          | FSR                                                    |                   | FSR                                                      |               | FSR                   |              |

|                                        | 04h                        |                                                        | 84h               | PORTA                                                    | 104h<br>105h  |                       | 184h         |

| PORTA<br>PORTB                         | 05h<br>06h                 | TRISA<br>TRISB                                         | 85h<br>86h        | PORTA                                                    | 105h<br>106h  | TRISA<br>TRISB        | 185h<br>186h |

| PORTE                                  | 00n<br>07h                 | TRISE                                                  | 87h               | PORTE                                                    | 106h<br>107h  | TRISE                 | 187h         |

| FURIC                                  | 0711<br>08h                | TRIBC                                                  | 88h               | FORTC                                                    | 107h<br>108h  | TRISC                 | 188h         |

|                                        | 09h                        |                                                        | 89h               |                                                          | 109h          |                       | 189h         |

| PCLATH                                 | 0Ah                        | PCLATH                                                 | 8Ah               | PCLATH                                                   | 10911<br>10Ah | PCLATH                | 18Ah         |

| INTCON                                 | 0Bh                        | INTCON                                                 | 8Bh               | INTCON                                                   | 10An<br>10Bh  | INTCON                | 18Bh         |

| PIR1                                   | 0Ch                        | PIE1                                                   | 8Ch               | EEDAT                                                    | 10Dh          | EECON1                | 18Ch         |

|                                        | -                          |                                                        |                   |                                                          |               | EECON2 <sup>(1)</sup> |              |

| PIR2                                   | 0Dh                        | PIE2                                                   | 8Dh               | EEADR                                                    | 10Dh          | EECONZY               | 18Dh         |

| TMR1L                                  | 0Eh                        | PCON                                                   | 8Eh               | EEDATH <sup>(3)</sup>                                    | 10Eh          |                       | 18Eh         |

| TMR1H                                  | 0Fh                        | OSCCON                                                 | 8Fh               | EEADRH <sup>(3)</sup>                                    | 10Fh          |                       | 18Fh         |

| T1CON                                  | 10h                        | OSCTUNE                                                | 90h               |                                                          | 110h          |                       | 190h         |

|                                        | 11h                        |                                                        | 91h               |                                                          | 111h          |                       | 191h         |

|                                        | 12h                        | (2)                                                    | 92h               |                                                          | 112h          |                       | 192h         |

| SSPBUF                                 | 13h                        | SSPADD <sup>(2)</sup>                                  | 93h               |                                                          | 113h          |                       | 193h         |

| SSPCON                                 | 14h                        | SSPSTAT                                                | 94h               |                                                          | 114h          |                       | 194h         |

|                                        | 15h                        | WPUA                                                   | 95h               | WPUB                                                     | 115h          |                       | 195h         |

|                                        | 16h                        | IOCA                                                   | 96h               | IOCB                                                     | 116h          |                       | 196h         |

|                                        | 17h                        | WDTCON                                                 | 97h               |                                                          | 117h          |                       | 197h         |

| RCSTA                                  | 18h                        | TXSTA                                                  | 98h               | VRCON                                                    | 118h          |                       | 198h         |

| TXREG                                  | 19h                        | SPBRG                                                  | 99h               | CM1CON0                                                  | 119h          |                       | 199h         |

| RCREG                                  | 1Ah                        | SPBRGH                                                 | 9Ah               | CM2CON0                                                  | 11Ah          |                       | 19Ah         |

|                                        | 1Bh                        | BAUDCTL                                                | 9Bh               | CM2CON1                                                  | 11Bh          |                       | 19Bh         |

|                                        | 1Ch                        |                                                        | 9Ch               |                                                          | 11Ch          |                       | 19Ch         |

|                                        | 1Dh                        |                                                        | 9Dh               |                                                          | 11Dh          | 00001                 | 19Dh         |

| ADRESH                                 | 1Eh                        | ADRESL                                                 | 9Eh               | ANSEL                                                    | 11Eh          | SRCON                 | 19Eh         |

| ADCON0                                 | 1Fh                        | ADCON1                                                 | 9Fh               | ANSELH                                                   | 11Fh          |                       | 19Fh         |

| General<br>Purpose<br>Register         | 20h                        | General<br>Purpose<br>Register<br>32 Bytes<br>48 Bytes | A0h<br>BFh<br>C0h | General<br>Purpose<br>Register<br>80 Bytes<br>(PIC16F689 | 120h          |                       | 1A0h         |

| 96 Bytes                               |                            | (PIC16F689<br>only)                                    | EFh               | only)                                                    |               |                       |              |

|                                        | 7Fh                        | accesses<br>70h-7Fh                                    | F0h<br>FFh        | accesses<br>70h-7Fh                                      | 170h<br>17Fh  | accesses<br>70h-7Fh   | 1F0h<br>1FFh |

| Bank 0                                 | 1                          | Bank 1                                                 | I                 | Bank 2                                                   | I             | Bank 3                |              |

| lote 1: Not a p<br>2: Addres<br>See Re | ohysical reg<br>s 93h also | •                                                      | P Mask (SS        | as '0'.<br>SPMSK) register u                             | nder certai   | n conditions.         |              |

#### 4.0 I/O PORTS

There are as many as eighteen general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

#### 4.1 **PORTA and the TRISA Registers**

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 4-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Reading the PORTA register (Register 4-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write

#### **REGISTER 4-1:** PORTA: PORTA REGISTER

operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

The ANSEL register must be initialized to Note: configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### EXAMPLE 4-1: **INITIALIZING PORTA**

| BCF   | STATUS, RP0; Bank 0        |

|-------|----------------------------|

| BCF   | STATUS, RP1;               |

| CLRF  | PORTA ;Init PORTA          |

| BSF   | STATUS, RP1; Bank 2        |

| CLRF  | ANSEL ;digital I/O         |

| BSF   | STATUS, RP0; Bank 1        |

| BCF   | STATUS, RP1;               |

| MOVLW | 0Ch ;Set RA<3:2> as inputs |

| MOVWF | TRISA ;and set RA<5:4,1:0> |

|       | ;as outputs                |

| BCF   | STATUS, RP0; Bank 0        |

|       |                            |

| U-0     | U-0 U-0 |     | R/W-x | R-x | R/W-x | R/W-x | R/W-x |

|---------|---------|-----|-------|-----|-------|-------|-------|

| —       | —       | RA5 | RA4   | RA3 | RA2   | RA1   | RA0   |

| bit 7   |         |     |       |     |       |       | bit 0 |

|         |         |     |       |     |       |       |       |

| Legend: |         |     |       |     |       |       |       |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                        |

|---------|-------------------------------------------------------------------|

| bit 5-0 | <b>RA&lt;5:0&gt;</b> : PORTA I/O Pin bit<br>1 = Port pin is > VIH |

|         | 0 = Port pin is < VIL                                             |

#### **REGISTER 4-2:** TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 R/W- |        | R/W-1 R/W-1 R· |        | R/W-1  | R/W-1  | R/W-1  |  |

|-------|----------|--------|----------------|--------|--------|--------|--------|--|

|       |          | TRISA5 | TRISA4         | TRISA3 | TRISA2 | TRISA1 | TRISA0 |  |

| bit 7 |          |        |                |        |        |        | bit 0  |  |

| Legend:           |                  |                           |                                    |  |  |

|-------------------|------------------|---------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown                 |  |  |

bit 7-6 Unimplemented: Read as '0'

TRISA<5:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

Note 1: TRISA<3> always reads '1'.

bit 5-0

TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes. 2:

| U-0               | R/W-0                        | R/W-0                 | R/W-0          | R/W-0             | R/W-0  | R/W-0           | R/W-0   |  |  |

|-------------------|------------------------------|-----------------------|----------------|-------------------|--------|-----------------|---------|--|--|

| —                 | TOUTPS3                      | TOUTPS2               | TOUTPS1        | TOUTPS0           | TMR2ON | T2CKPS1         | T2CKPS0 |  |  |

| oit 7             |                              |                       |                |                   |        |                 | bit     |  |  |

|                   |                              |                       |                |                   |        |                 |         |  |  |

| egend:            |                              |                       |                |                   |        |                 |         |  |  |

| R = Readable      | e bit                        | W = Writable          | oit            | U = Unimplen      |        | id as '0'       |         |  |  |

| -n = Value at POR |                              | '1' = Bit is set      |                | '0' = Bit is clea | ared   | x = Bit is unkr | nown    |  |  |

| oit 7             | Unimplemen                   | ted: Read as '        | ז'             |                   |        |                 |         |  |  |

| oit 6-3           | -                            | >: Timer2 Outp        |                | Select hits       |        |                 |         |  |  |

|                   | 0000 =1:1 Pc                 | •                     |                |                   |        |                 |         |  |  |

|                   | 0000 =1:1 PC                 |                       |                |                   |        |                 |         |  |  |

|                   | 0010 =1:2 PC                 |                       |                |                   |        |                 |         |  |  |

|                   | 0010 = 1.3 Postscaler        |                       |                |                   |        |                 |         |  |  |

|                   | 0100 = 1.5 Postscaler        |                       |                |                   |        |                 |         |  |  |

|                   | 0101 = 1:6 Postscaler        |                       |                |                   |        |                 |         |  |  |

|                   | 0110 <b>=1:7 Pc</b>          | 0110 =1:7 Postscaler  |                |                   |        |                 |         |  |  |

|                   | 0111 <b>=1:8 Pc</b>          | ostscaler             |                |                   |        |                 |         |  |  |

|                   | 1000 <b>=1:9 Pc</b>          | ostscaler             |                |                   |        |                 |         |  |  |

|                   | 1001 =1:10 F                 |                       |                |                   |        |                 |         |  |  |

|                   | 1010 <b>=1:11 P</b>          |                       |                |                   |        |                 |         |  |  |

|                   |                              | 1011 =1:12 Postscaler |                |                   |        |                 |         |  |  |

|                   | 1100 =1:13 F                 |                       |                |                   |        |                 |         |  |  |

|                   | 1101 =1:14 F                 |                       |                |                   |        |                 |         |  |  |

|                   | 1110 =1:15 P<br>1111 =1:16 P |                       |                |                   |        |                 |         |  |  |

| oit 2             | TMR2ON: Timer2 On bit        |                       |                |                   |        |                 |         |  |  |

|                   | 1 = Timer2 is                | son                   |                |                   |        |                 |         |  |  |

|                   | 0 = Timer2 is                | off                   |                |                   |        |                 |         |  |  |

| oit 1-0           | T2CKPS<1:0                   | >: Timer2 Cloc        | k Prescale Sel | lect bits         |        |                 |         |  |  |

|                   | 00 =Prescale                 | ris 1                 |                |                   |        |                 |         |  |  |

|                   | 01 =Prescale                 | r is 4                |                |                   |        |                 |         |  |  |

|                   | 1x =Prescale                 | r is 16               |                |                   |        |                 |         |  |  |

| lote 1: PI        | IC16F685/PIC16               | E600 only             |                |                   |        |                 |         |  |  |

#### T2CON: TIMER 2 CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-1:**

## TABLE 7-1: SUMMARY OF ASSOCIATED TIMER2<sup>(1)</sup> REGISTERS

| Name   | Bit 7                                        | Bit 6         | Bit 5    | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------|---------------|----------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE                                          | PEIE          | TOIE     | INTE    | RABIE   | T0IF   | INTF    | RABIF   | 0000 000x            | 0000 000x                       |

| PIE1   | _                                            | ADIE          | RCIE     | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | -000 0000            | -000 0000                       |

| PIR1   | _                                            | ADIF          | RCIF     | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | -000 0000            | -000 0000                       |

| PR2    | Timer2 M                                     | lodule Period | Register |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Register for the 8-bit TMR2 Register |               |          |         |         |        |         |         |                      | 0000 0000                       |

| T2CON  | —                                            | TOUTPS3       | TOUTPS2  | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

|        |                                              |               |          |         |         |        |         |         |                      |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

Note

1:

PIC16F685/PIC16F690 only.

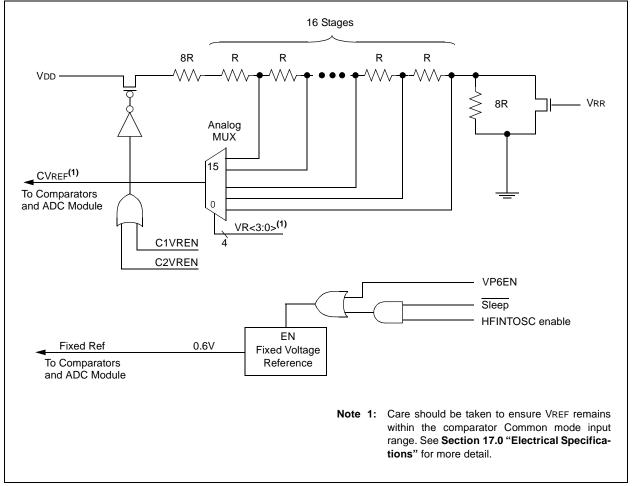

#### 8.10.5 FIXED VOLTAGE REFERENCE

The Fixed Voltage Reference is independent of VDD, with a nominal output voltage of 0.6V. This reference can be enabled by setting the VP6EN bit of the VRCON register to '1'. This reference is always enabled when the HFINTOSC oscillator is active.

#### 8.10.6 FIXED VOLTAGE REFERENCE STABILIZATION PERIOD

When the Fixed Voltage Reference module is enabled, it will require some time for the reference and its amplifier circuits to stabilize. The user program must include a small delay routine to allow the module to settle. See the electrical specifications section for the minimum delay requirement.

#### 8.10.7 VOLTAGE REFERENCE SELECTION

Multiplexers on the output of the Voltage Reference module enable selection of either the CVREF or Fixed Voltage Reference for use by the comparators.

Setting the C1VREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C1. Clearing the C1VREN bit selects the fixed voltage for use by C1.

Setting the C2VREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C2. Clearing the C2VREN bit selects the fixed voltage for use by C2.

When both the C1VREN and C2VREN bits are cleared, current flow in the CVREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

### FIGURE 8-8: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| Name   | Bit 7     | Bit 6        | Bit 5     | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|--------------|-----------|--------|--------|--------|---------|--------|----------------------|---------------------------------|

| ADCON0 | ADFM      | VCFG         | CHS3      | CHS2   | CHS1   | CHS0   | GO/DONE | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 | —         | ADCS2        | ADCS1     | ADCS0  | _      | _      | _       | -      | -000                 | -000                            |

| ANSEL  | ANS7      | ANS6         | ANS5      | ANS4   | ANS3   | ANS2   | ANS1    | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH | —         | —            | —         | —      | ANS11  | ANS10  | ANS9    | ANS8   | 1111                 | 1111                            |

| ADRESH | A/D Resul | t Register H | ligh Byte |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul | t Register L | ow Byte   |        |        |        |         |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE       | PEIE         | TOIE      | INTE   | RABIE  | T0IF   | INTF    | RABIF  | 0000 000x            | x000 000x                       |

| PIE1   | —         | ADIE         | RCIE      | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | -000 0000            | -000 0000                       |

| PIR1   | _         | ADIF         | RCIF      | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | -000 0000            | -000 0000                       |

| PORTA  | —         | —            | RA5       | RA4    | RA3    | RA2    | RA1     | RA0    | xx xxxx              | uu uuuu                         |

| PORTB  | RB7       | RB6          | RB5       | RB4    | _      | _      | _       | -      | xxxx                 | uuuu                            |

| PORTC  | RC7       | RC6          | RC5       | RC4    | RC3    | RC2    | RC1     | RC0    | xxxx xxxx            | uuuu uuuu                       |

| TRISA  | —         | _            | TRISA5    | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 11 1111              | 11 1111                         |

| TRISB  | TRISB7    | TRISB6       | TRISB5    | TRISB4 | —      | —      | —       | —      | 1111                 | 1111                            |

| TRISC  | TRISC7    | TRISC6       | TRISC5    | TRISC4 | TRISC3 | TRISC2 | TRISC1  | TRISC0 | 1111 1111            | 1111 1111                       |

### TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

## 10.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

Data EEPROM memory is readable and writable and the Flash program memory (PIC16F685/PIC16F689/ PIC16F690 only) is readable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDAT

- EEDATH (PIC16F685/PIC16F689/PIC16F690 only)

- EEADR

- EEADRH (PIC16F685/PIC16F689/PIC16F690 only)

When interfacing the data memory block, EEDAT holds the 8-bit data for read/write, and EEADR holds the address of the EEDAT location being accessed. These devices, except for the PIC16F631, have 256 bytes of data EEPROM with an address range from 0h to 0FFh. The PIC16F631 has 128 bytes of data EEPROM with an address range from 0h to 07Fh.

When accessing the program memory block of the PIC16F685/PIC16F689/PIC16F690 devices, the EEDAT and EEDATH registers form a 2-byte word that holds the 14-bit data for read/write, and the EEADR and EEADRH registers form a 2-byte word that holds the 12-bit address of the EEPROM location being read. These devices (PIC16F685/PIC16F689/PIC16F690) have 4K words of program EEPROM with an address range from 0h to 0FFFh. The program memory allows one-word reads.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

When the device is code-protected, the CPU may continue to read and write the data EEPROM memory and read the program memory. When code-protected, the device programmer can no longer access data or program memory.

#### 10.1 EEADR and EEADRH Registers

The EEADR and EEADRH registers can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 4K words of program EEPROM.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADR register. When selecting a data address value, only the LSB of the address is written to the EEADR register.

#### 10.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD (PIC16F685/PIC16F689/PIC16F690) determines if the access will be a program or data memory access. When clear, as it is when reset, any subsequent operations will operate on the data memory. When set, any subsequent operations will operate on the program memory. Program memory can only be read.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to data EEPROM. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

#### **TABLE 10-1:** SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name                  | Bit 7                 | Bit 6        | Bit 5           | Bit 4         | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------|--------------|-----------------|---------------|---------|---------|---------|---------|----------------------|---------------------------------|

| EECON1                | EEPGD <sup>(1)</sup>  | —            | _               |               | WRERR   | WREN    | WR      | RD      | x x000               | 0 q000                          |

| EECON2                | EEPROM C              | ontrol Regis | ster 2 (not a p | hysical regis | ter)    |         |         |         |                      |                                 |

| EEADR                 | EEADR7 <sup>(2)</sup> | EEADR6       | EEADR5          | EEADR4        | EEADR3  | EEADR2  | EEADR1  | EEADR0  | 0000 0000            | 0000 0000                       |

| EEADRH <sup>(1)</sup> | _                     | -            | _               | _             | EEADRH3 | EEADRH2 | EEADRH1 | EEADRH0 | 0000                 | 0000                            |

| EEDAT                 | EEDAT7                | EEDAT6       | EEDAT5          | EEDAT4        | EEDAT3  | EEDAT2  | EEDAT1  | EEDAT0  | 0000 0000            | 0000 0000                       |

| EEDATH <sup>(1)</sup> | _                     | _            | EEDATH5         | EEDATH4       | EEDATH3 | EEDATH2 | EEDATH1 | EEDATH0 | 00 0000              | 00 0000                         |

| INTCON                | GIE                   | PEIE         | TOIE            | INTE          | RABIE   | T0IF    | INTF    | RABIF   | 0000 0000            | 0000 0000                       |

| PIE2                  | OSFIE                 | C2IE         | C1IE            | EEIE          | _       | _       | _       | _       | 0000                 | 0000                            |

| PIR2                  | OSFIF                 | C2IF         | C1IF            | EEIF          | -       | _       | _       | _       | 0000                 | 0000                            |

${\bf x}$  = unknown,  ${\bf u}$  = unchanged, – = unimplemented read as '0',  ${\bf q}$  = value depends upon condition. Shaded cells are not used by data EEPROM module. PIC16F685/PIC16F689/PIC16F690 only. Legend:

Note 1:

PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only. 2:

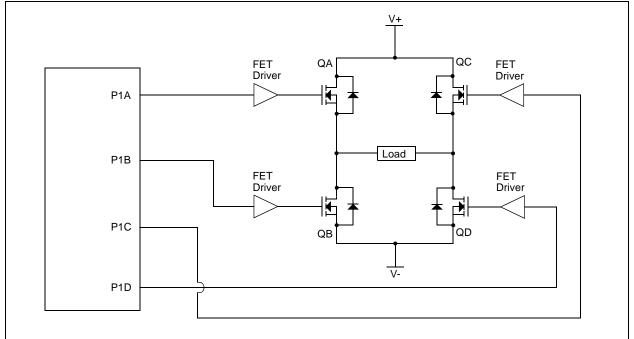

### 11.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 11-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 11-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 11-11.

P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

## FIGURE 11-10: EXAMPLE OF FULL-BRIDGE APPLICATION

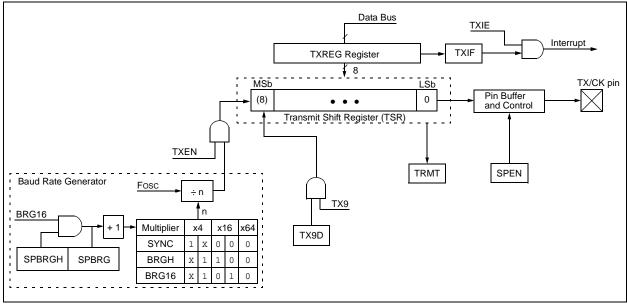

## 12.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

Block diagrams of the EUSART transmitter and receiver are shown in Figure 12-1 and Figure 12-2.

### FIGURE 12-1: EUSART TRANSMIT BLOCK DIAGRAM

| Name    | Bit 7      | Bit 6        | Bit 5        | Bit 4               | Bit 3       | Bit 2        | Bit 1      | Bit 0      | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|--------------|--------------|---------------------|-------------|--------------|------------|------------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF     | RCIDL        | —            | SCKP                | BRG16       | _            | WUE        | ABDEN      | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE        | PEIE         | TOIE         | INTE                | RABIE       | T0IF         | INTF       | RABIF      | x000 000x            | 0000 000x                       |

| PIE1    | —          | ADIE         | RCIE         | TXIE                | SSPIE       | CCP1IE       | TMR2IE     | TMR1IE     | -000 0000            | -000 0000                       |

| PIR1    | —          | ADIF         | RCIF         | TXIF                | SSPIF       | CCP1IF       | TMR2IF     | TMR1IF     | -000 0000            | -000 0000                       |

| RCREG   | EUSART F   | Receive Da   | ta Register  |                     |             |              |            |            | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN       | RX9          | SREN         | CREN                | ADDEN       | FERR         | OERR       | RX9D       | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7       | BRG6         | BRG5         | BRG4                | BRG3        | BRG2         | BRG1       | BRG0       | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15      | BRG14        | BRG13        | BRG12               | BRG11       | BRG10        | BRG9       | BRG8       | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7     | TRISB6       | TRISB5       | TRISB4              |             |              |            |            | 1111                 | 1111                            |

| TXREG   | EUSART 1   | Transmit Da  | ata Register |                     |             |              |            |            | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC       | TX9          | TXEN         | SYNC                | SENDB       | BRGH         | TRMT       | TX9D       | 0000 0010            | 0000 0010                       |

| Legend: | x = unknov | vn, – = unir | nplemented   | <b>I read as</b> '0 | '. Shaded c | ells are not | used for A | synchronou | is Transmission      | ۱.                              |

### TABLE 12-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

|        |                |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 0, BRC         | <b>616 =</b> 0 |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc           | ; = 20.00  | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |                |                             | Fosc = 8.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _              |            | _                           |                   | _          | _                           | _                  | _              | _                           | _                | _          | _                           |

| 1200   | 1221           | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1200               | 0.00           | 143                         | 1202             | 0.16       | 103                         |

| 2400   | 2404           | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2400               | 0.00           | 71                          | 2404             | 0.16       | 51                          |

| 9600   | 9470           | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9600               | 0.00           | 17                          | 9615             | 0.16       | 12                          |

| 10417  | 10417          | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10165              | -2.42          | 16                          | 10417            | 0.00       | 11                          |

| 19.2k  | 19.53k         | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.20k             | 0.00           | 8                           | _                | _          | _                           |

| 57.6k  | —              | —          | _                           | 57.60k            | 0.00       | 7                           | 57.60k             | 0.00           | 2                           | —                | —          | —                           |

| 115.2k | —              |            | _                           | —                 | _          | _                           | _                  |                | _                           | _                | _          | _                           |

#### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                | SYNC       | <b>C =</b> 0, BRGH          | l = 0, BRG       | <b>616 =</b> 0 |                             |                  |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 4.000 MHz |            |                             | Fosc           | = 3.686    | 4 MHz                       | Fosc = 2.000 MHz |                |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300              | 0.16       | 207                         | 300            | 0.00       | 191                         | 300              | 0.16           | 103                         | 300              | 0.16       | 51                          |

| 1200   | 1202             | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202             | 0.16           | 25                          | 1202             | 0.16       | 12                          |

| 2400   | 2404             | 0.16       | 25                          | 2400           | 0.00       | 23                          | 2404             | 0.16           | 12                          | —                | _          | _                           |

| 9600   | —                | _          | _                           | 9600           | 0.00       | 5                           | _                | _              | _                           | —                | _          | _                           |

| 10417  | 10417            | 0.00       | 5                           | —              | _          | _                           | 10417            | 0.00           | 2                           | _                | _          | _                           |

| 19.2k  | —                | _          | _                           | 19.20k         | 0.00       | 2                           | _                | _              | _                           | —                | _          | _                           |

| 57.6k  | —                | —          | —                           | 57.60k         | 0.00       | 0                           | —                | —              | —                           | —                | —          | —                           |

| 115.2k | —                | —          | _                           | _              | _          | —                           | _                | —              | _                           | —                | —          | —                           |

|        |                |            |                             |                   | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC         | <b>616 =</b> 0 |                             |                  |            |                             |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|----------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc           | = 20.00    | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |                |                             | Fosc = 8.000 MHz |            |                             |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —              |            | _                           | _                 |            | _                           |                    | —              | _                           |                  | —          |                             |

| 1200   | —              | —          | —                           | —                 | _          | —                           | —                  | —              | —                           | —                | —          | —                           |

| 2400   | _              | _          | _                           | —                 | _          | _                           | —                  | _              | _                           | 2404             | 0.16       | 207                         |

| 9600   | 9615           | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600               | 0.00           | 71                          | 9615             | 0.16       | 51                          |

| 10417  | 10417          | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473              | 0.53           | 65                          | 10417            | 0.00       | 47                          |

| 19.2k  | 19.23k         | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k             | 0.00           | 35                          | 19231            | 0.16       | 25                          |

| 57.6k  | 56.82k         | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k             | 0.00           | 11                          | 55556            | -3.55      | 8                           |

| 115.2k | 113.64k        | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k             | 0.00           | 5                           | —                | —          | _                           |

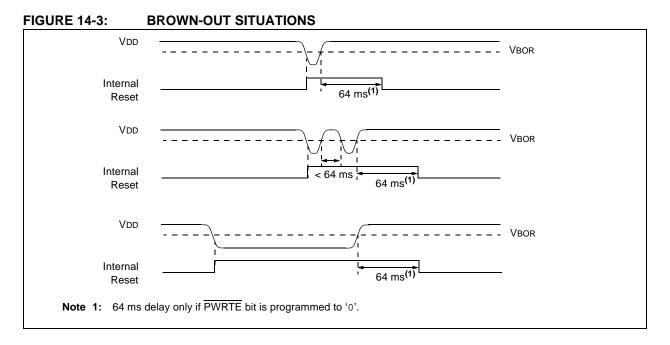

### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

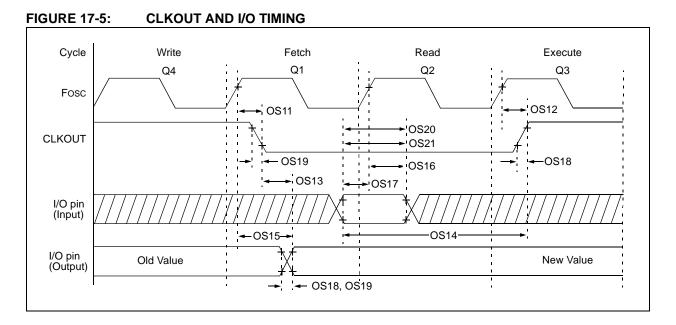

### TABLE 17-3: CLKOUT AND I/O TIMING PARAMETERS

|              |          | Conditions (unless otherwise stated) re -40°C $\leq$ TA $\leq$ +125°C |               |          |          |       |                          |

|--------------|----------|-----------------------------------------------------------------------|---------------|----------|----------|-------|--------------------------|

| Param<br>No. | Sym.     | Characteristic                                                        | Min.          | Тур†     | Max.     | Units | Conditions               |

| OS11         | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                                       | —             | —        | 70       | ns    | VDD = 5.0V               |

| OS12         | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                                       | _             | _        | 72       | ns    | VDD = 5.0V               |

| OS13         | TckL2IoV | CLKOUT↓ to port out valid <sup>(1)</sup>                              | _             | _        | 20       | ns    |                          |

| OS14         | ТюV2скН  | Port input valid before CLKOUT↑ <sup>(1)</sup>                        | Tosc + 200 ns | _        |          | ns    |                          |

| OS15         | TosH2IoV | Fosc↑ (Q1 cycle) to port out valid                                    | —             | 50       | 70*      | ns    | VDD = 5.0V               |

| OS16         | TosH2iol | Fosc↑ (Q2 cycle) to port input invalid (I/O in hold time)             | 50            |          |          | ns    | VDD = 5.0V               |

| OS17         | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)           | 20            |          | _        | ns    |                          |

| OS18         | TIOR     | Port output rise time <sup>(2)</sup>                                  |               | 15<br>40 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS19         | TIOF     | Port output fall time <sup>(2)</sup>                                  |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS20*        | TINP     | INT pin input high or low time                                        | 25            | —        | _        | ns    |                          |

| OS21*        | Trap     | PORTA interrupt-on-change new input level time                        | Тсү           | —        | _        | ns    |                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

2: Includes OSC2 in CLKOUT mode.

# TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

|              | d Operating Tempe | ting Conditions (unless otherwise rature $-40^{\circ}C \le TA \le +125^{\circ}C$ | se state | ed)      |          |          |                                      |

|--------------|-------------------|----------------------------------------------------------------------------------|----------|----------|----------|----------|--------------------------------------|

| Param<br>No. | Sym.              | Characteristic                                                                   | Min.     | Тур†     | Max.     | Units    | Conditions                           |

| 30           | TMCL              | MCLR Pulse Width (low)                                                           | 2<br>5   |          | _        | μs<br>μs | VDD = 5V, -40°C to +85°C<br>VDD = 5V |

| 31           | Twdt              | Watchdog Timer Time-out<br>Period (No Prescaler)                                 | 10<br>10 | 17<br>17 | 25<br>30 | ms<br>ms | VDD = 5V, -40°C to +85°C<br>VDD = 5V |

| 32           | Tost              | Oscillation Start-up Timer<br>Period <sup>(1, 2)</sup>                           | _        | 1024     | —        | Tosc     | (Note 3)                             |

| 33*          | TPWRT             | Power-up Timer Period                                                            | 40       | 65       | 140      | ms       |                                      |

| 34*          | Tioz              | I/O High-impedance from<br>MCLR Low or Watchdog Timer<br>Reset                   | —        | _        | 2.0      | μS       |                                      |

| 35           | VBOR              | Brown-out Reset Voltage                                                          | 2.0      | _        | 2.2      | V        | (Note 4)                             |

| 36*          | VHYST             | Brown-out Reset Hysteresis                                                       | _        | 50       | —        | mV       |                                      |

| 37*          | TBOR              | Brown-out Reset Minimum<br>Detection Period                                      | 100      | _        |          | μS       | $VDD \leq VBOR$                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at 'min' values with an external clock applied to the OSC1 pin. When an external clock input is used, the 'max' cycle time limit is 'DC' (no clock) for all devices.

- 2: By design.

- 3: Period of the slower clock.

- **4:** To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

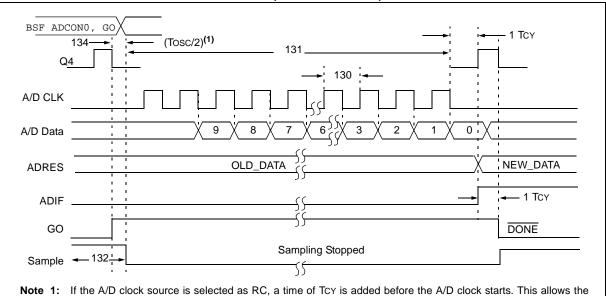

#### FIGURE 17-18: A/D CONVERSION TIMING (NORMAL MODE)

## TABLE 17-16: A/D CONVERSION REQUIREMENTS

SLEEP instruction to be executed.

| Param<br>No. | Sym. | Characteristic                                                        | Min. | Тур†   | Max. | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|-----------------------------------------------------------------------|------|--------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130*         | Tad  | A/D Clock Period                                                      | 1.5  | —      | _    | μS    | Tosc-based, VREF $\ge$ 2.5V                                                                                                                                                                                                |

|              |      |                                                                       | 3.0* | —      | —    | μs    | Tosc-based, VREF full range                                                                                                                                                                                                |

|              |      | A/D Internal RC<br>Oscillator Period                                  | 3.0* | 6.0    | 9.0* | μs    | ADCS<1:0> = 11 (RC mode)<br>At VDD = 2.5V                                                                                                                                                                                  |

|              |      |                                                                       | 2.0* | 4.0    | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                                              |

| 131          | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _    | 11     | _    | TAD   | Set GO bit to new data in A/D Result register                                                                                                                                                                              |

| 132*         | TACQ | Acquisition Time                                                      | (2)  | 11.5   |      | μs    |                                                                                                                                                                                                                            |

|              |      |                                                                       | 5*   | _      | _    | μS    | The minimum time is the amplifier<br>settling time. This may be used if the<br>"new" input voltage has not changed<br>by more than 1 LSb (i.e., 4.1 mV @<br>4.096V) from the last sampled<br>voltage (as stored on CHOLD). |

| 134          | TGO  | Q4 to A/D Clock<br>Start                                              |      | Tosc/2 | _    | _     | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRESH and ADRESL registers may be read on the following TCY cycle.

2: See Table 9-1 for minimum conditions.

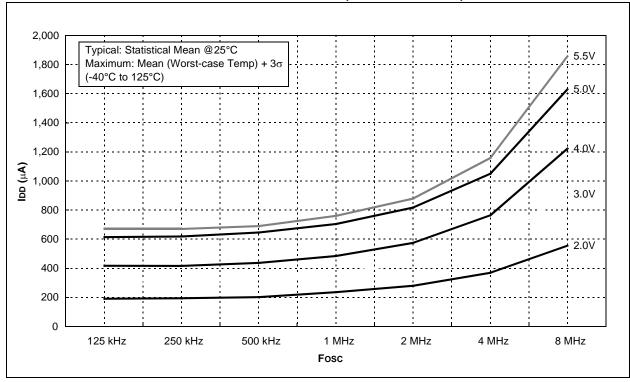

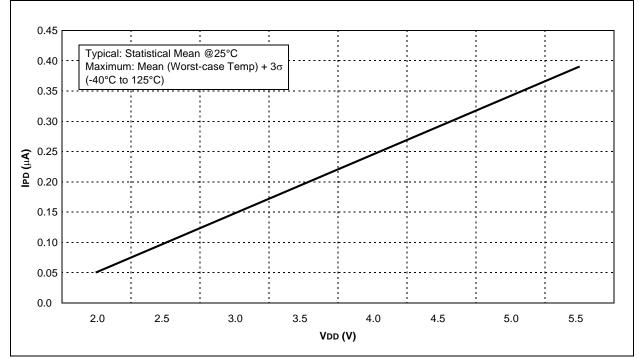

#### FIGURE 18-12: MAXIMUM IDD vs. Fosc OVER VDD (HFINTOSC MODE)

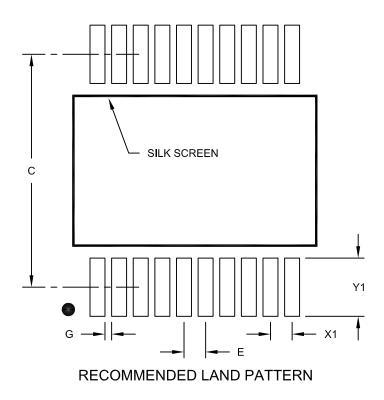

20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | MILLIMETERS |          |      |  |  |

|--------------------------|----------|-------------|----------|------|--|--|

| Dimensior                | n Limits | MIN         | NOM      | MAX  |  |  |

| Contact Pitch            | E        |             | 0.65 BSC |      |  |  |

| Contact Pad Spacing      | С        |             | 7.20     |      |  |  |

| Contact Pad Width (X20)  | X1       |             |          | 0.45 |  |  |

| Contact Pad Length (X20) | Y1       |             |          | 1.75 |  |  |

| Distance Between Pads    | G        | 0.20        |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072A

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2005-2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63277-235-0

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.