Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f689-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-3: PINOUT DESCRIPTION - PIC16F685

| Name                            | Function | Input<br>Type | Output<br>Type | Description                                                                                         |

|---------------------------------|----------|---------------|----------------|-----------------------------------------------------------------------------------------------------|

| RA0/AN0/C1IN+/ICSPDAT/<br>ULPWU | RA0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | AN0      | AN            | _              | A/D Channel 0 input.                                                                                |

|                                 | C1IN+    | AN            | _              | Comparator C1 positive input.                                                                       |

|                                 | ICSPDAT  | TTL           | CMOS           | ICSP™ Data I/O.                                                                                     |

|                                 | ULPWU    | AN            | _              | Ultra Low-Power Wake-up input.                                                                      |

| RA1/AN1/C12IN0-/VREF/ICSPCLK    | RA1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | AN1      | AN            | _              | A/D Channel 1 input.                                                                                |

|                                 | C12IN0-  | AN            | _              | Comparator C1 or C2 negative input.                                                                 |

|                                 | VREF     | AN            | _              | External Voltage Reference for A/D.                                                                 |

|                                 | ICSPCLK  | ST            | _              | ICSP™ clock.                                                                                        |

| RA2/AN2/T0CKI/INT/C1OUT         | RA2      | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | AN2      | AN            | _              | A/D Channel 2 input.                                                                                |

|                                 | T0CKI    | ST            | _              | Timer0 clock input.                                                                                 |

|                                 | INT      | ST            | _              | External interrupt pin.                                                                             |

|                                 | C10UT    | _             | CMOS           | Comparator C1 output.                                                                               |

| RA3/MCLR/VPP                    | RA3      | TTL           | _              | General purpose input. Individually controlled interrupt-on-<br>change.                             |

|                                 | MCLR     | ST            | _              | Master Clear with internal pull-up.                                                                 |

|                                 | VPP      | HV            | _              | Programming voltage.                                                                                |

| RA4/AN3/T1G/OSC2/CLKOUT         | RA4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | AN3      | AN            | _              | A/D Channel 3 input.                                                                                |

|                                 | T1G      | ST            | _              | Timer1 gate input.                                                                                  |

|                                 | OSC2     | _             | XTAL           | Crystal/Resonator.                                                                                  |

|                                 | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                      |

| RA5/T1CKI/OSC1/CLKIN            | RA5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | T1CKI    | ST            | _              | Timer1 clock input.                                                                                 |

|                                 | OSC1     | XTAL          | _              | Crystal/Resonator.                                                                                  |

|                                 | CLKIN    | ST            | _              | External clock input/RC oscillator connection.                                                      |

| RB4/AN10                        | RB4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | AN10     | AN            | _              | A/D Channel 10 input.                                                                               |

| RB5/AN11                        | RB5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

|                                 | AN11     | AN            | _              | A/D Channel 11 input.                                                                               |

| RB6                             | RB6      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up.     |

| RB7                             | RB7      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |

| RC0/AN4/C2IN+                   | RC0      | ST            | CMOS           | General purpose I/O.                                                                                |

|                                 | AN4      | AN            | _              | A/D Channel 4 input.                                                                                |

|                                 | C2IN+    | AN            | _              | Comparator C2 positive input.                                                                       |

**Legend:** AN = Analog input or output

CMOS=CMOS compatible input or output

TTL = TTL compatible input

ST= Schmitt Trigger input with CMOS levels

HV = High Voltage

XTAL= Crystal

#### 2.2.2.8 PCON Register

The Power Control (PCON) register (see Register 2-8) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the <u>Ultra Low-Power</u> Wake-up and software enable of the BOR.

### REGISTER 2-8: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1                 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|-----------------------|-----|-----|-------|-------|

| _     | _   | ULPWUE | SBOREN <sup>(1)</sup> | _   | _   | POR   | BOR   |

| bit 7 |     | •      | •                     |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5 **ULPWUE:** Ultra Low-Power Wake-up Enable bit

1 = Ultra Low-Power Wake-up enabled0 = Ultra Low-Power Wake-up disabled

bit 4 SBOREN: Software BOR Enable bit<sup>(1)</sup>

1 = BOR enabled 0 = BOR disabled

bit 3-2 Unimplemented: Read as '0'

bit 1 POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOR: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

**Note 1:** BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{BOR}$ .

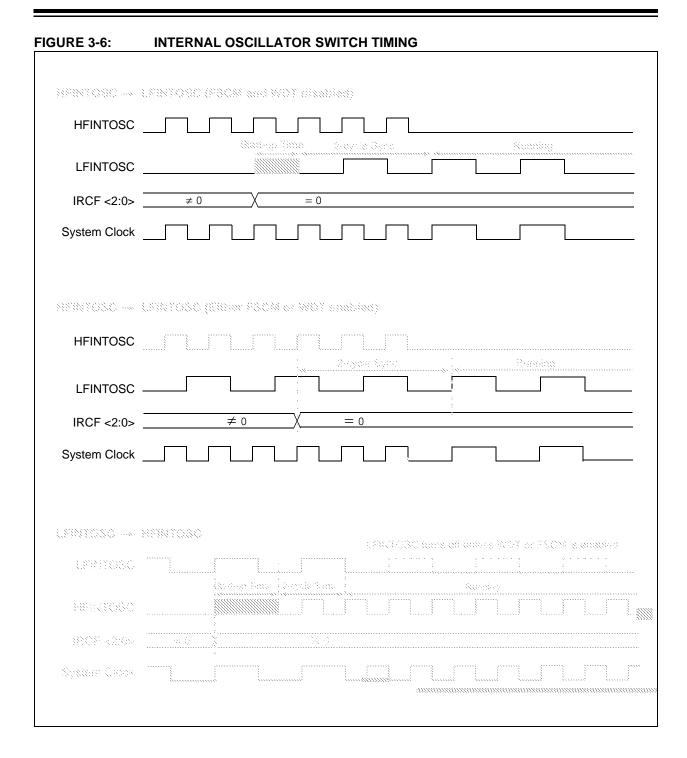

# 3.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or the internal oscillator.

TABLE 4-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name                   | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|--------|--------|--------|---------|--------|--------|--------|--------|----------------------|---------------------------------|

| ANSEL                  | ANS7   | ANS6   | ANS5   | ANS4    | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| ANSELH                 | _      | _      | _      | _       | ANS11  | ANS10  | ANS9   | ANS8   | 1111                 | 1111                            |

| CCP1CON <sup>(2)</sup> | P1M1   | P1M0   | DC1B1  | DC1B0   | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 | 0000 0000            | 0000 0000                       |

| CM2CON0                | C2ON   | C2OUT  | C2OE   | C2POL   | _      | C2R    | C2CH1  | C2CH0  | 0000 -000            | 0000 -000                       |

| CM2CON1                | MC1OUT | MC2OUT | _      | _       | _      | _      | T1GSS  | C2SYNC | 0010                 | 0010                            |

| PORTC                  | RC7    | RC6    | RC5    | RC4     | RC3    | RC2    | RC1    | RC0    | xxxx xxxx            | uuuu uuuu                       |

| PSTRCON                | _      | _      | _      | STRSYNC | STRD   | STRC   | STRB   | STRA   | 0 0001               | 0 0001                          |

| SRCON                  | SR1    | SR0    | C1SEN  | C2REN   | PULSS  | PULSR  | 1      | _      | 0000 00              | 0000 00                         |

| SSPCON <sup>(1)</sup>  | WCOL   | SSPOV  | SSPEN  | CKP     | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| TRISC                  | TRISC7 | TRISC6 | TRISC5 | TRISC4  | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| VRCON                  | C1VREN | C2VREN | VRR    | VP6EN   | VR3    | VR2    | VR1    | VR0    | 0000 0000            | 0000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16F687/PIC16F689/PIC16F690 only.

2: PIC16F685/PIC16F690 only.

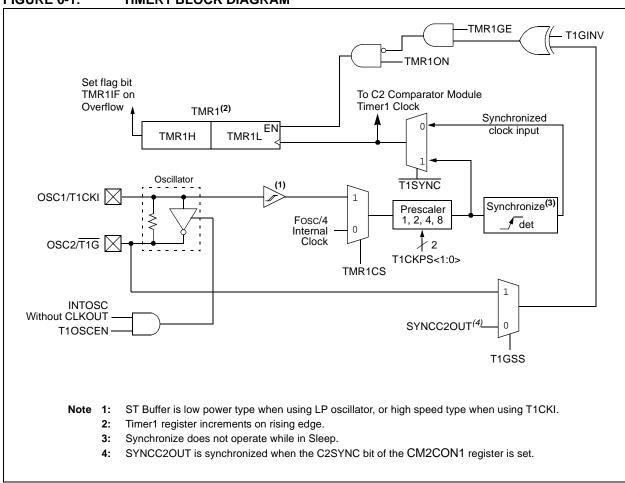

FIGURE 6-1: TIMER1 BLOCK DIAGRAM

TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD  $\geq$  3.0V, VREF  $\geq$  2.5V)

| ADC Clock P      | eriod (TAD) | Device Frequency (Fosc) |                         |                         |                         |  |  |

|------------------|-------------|-------------------------|-------------------------|-------------------------|-------------------------|--|--|

| ADC Clock Source | ADCS<2:0>   | 20 MHz                  | 8 MHz                   | 4 MHz                   | 1 MHz                   |  |  |

| Fosc/2           | 000         | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 2.0 μs                  |  |  |

| Fosc/4           | 100         | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 4.0 μs                  |  |  |

| Fosc/8           | 001         | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                  | 8.0 μs <sup>(3)</sup>   |  |  |

| Fosc/16          | 101         | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                  | 16.0 μs <sup>(3)</sup>  |  |  |

| Fosc/32          | 010         | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>   | 32.0 μs <sup>(3)</sup>  |  |  |

| Fosc/64          | 110         | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <sup>(3)</sup>  | 64.0 μs <sup>(3)</sup>  |  |  |

| FRC              | x11         | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

- **Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- **4:** When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

#### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

**Note:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the interrupt service routine.

Please see **Section 9.1.5** "Interrupts" for more information.

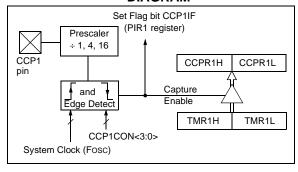

#### 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCP1IF of the PIR1 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPR1H, CCPR1L register pair is read, the old captured value is overwritten by the new captured value (see Figure 11-1).

#### 11.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the associated TRIS control bit.

**Note:** If the CCP1 pin is configured as an output, a write to the port can cause a capture condition.

# FIGURE 11-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit of the PIE1 register clear to avoid false interrupts. Additionally, the user should clear the CCP1IF interrupt flag bit of the PIR1 register following any change in operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCP1M<3:0> bits of the CCP1CON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCP1CON register before changing the prescaler (see Example 11-1).

### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ; to CCP1CON            |

| CLRF    | CCP1CON     | Turn CCP module off     |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

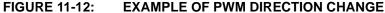

### 11.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction

- PWM modulation resumes at the beginning of the next period.

See Figure 11-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn-off time of the power switch, including the power device and driver circuit, is greater than the turn-on time.

Figure 11-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current will flow through power devices QC and QD (see Figure 11-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

- Note 1: The direction bit P1M1 of the CCP1CON register is written any time during the PWM cycle.

- 2: When changing directions, the P1A and P1C signals switch before the end of the current PWM cycle. The modulated P1B and P1D signals are inactive at this time. The length of this time is (1/Fosc) TMR2 prescale value.

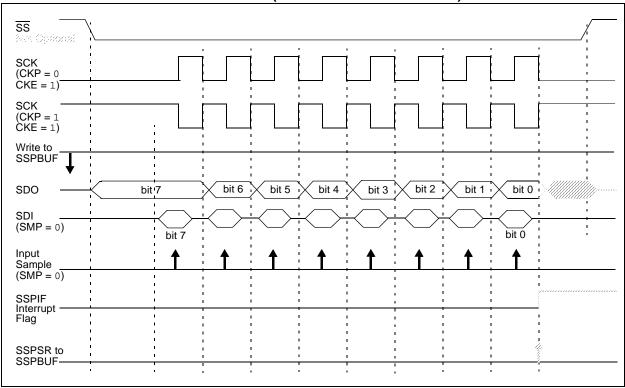

#### 13.2 Operation

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Status bit BF of the SSPSTAT register, and the interrupt flag bit SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit BF of the SSPSTAT register indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the SSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 13-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSP Status register (SSPSTAT) indicates the various status conditions.

### **EXAMPLE 13-1: LOADING THE SSPBUF (SSPSR) REGISTER**

|      |            |                          | , ,                                         |

|------|------------|--------------------------|---------------------------------------------|

|      | BSF<br>BCF | STATUS,RP0<br>STATUS,RP1 | ;Bank 1<br>;                                |

| LOOP | BTFSS      | SSPSTAT, BF              | ;Has data been received(transmit complete)? |

|      | GOTO       | LOOP                     | ; No                                        |

|      | BCF        | STATUS, RPO              | ;Bank 0                                     |

|      | MOVF       | SSPBUF, W                | ;WREG reg = contents of SSPBUF              |

|      | MOVWF      | RXDATA                   | ;Save in user RAM, if data is meaningful    |

|      | MOVF       | TXDATA, W                | ;W reg = contents of TXDATA                 |

|      | MOVWF      | SSPBUF                   | ;New data to xmit                           |

| 1    |            |                          |                                             |

FIGURE 13-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

FIGURE 13-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

### 13.8 Sleep Operation

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to Normal mode, the module will continue to transmit/receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

### 13.9 Effects of a Reset

A Reset disables the SSP module and terminates the current transfer.

### 13.10 Bus Mode Compatibility

Table 13-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

TABLE 13-1: SPI BUS MODES

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | CKP                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also a SMP bit which controls when the data is sampled.

TABLE 13-2: REGISTERS ASSOCIATED WITH SPI OPERATION<sup>(1)</sup>

| Address               | Name    | Bit 7     | Bit 6         | Bit 5       | Bit 4        | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|-----------------------|---------|-----------|---------------|-------------|--------------|--------------|--------|--------|--------|-------------------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON  | GIE       | PEIE          | TOIE        | INTE         | RABIE        | TOIF   | INTF   | RABIF  | 0000 000x               | 0000 000x                       |

| 0Ch                   | PIR1    | _         | ADIF          | RCIF        | TXIF         | SSPIF        | CCP1IF | TMR2IF | TMR1IF | -000 0000               | -000 0000                       |

| 13h                   | SSPBUF  | Synchrono | ous Serial Po | ort Receive | Buffer/Trans | smit Registe | r      |        |        | xxxx xxxx               | uuuu uuuu                       |

| 14h                   | SSPCON  | WCOL      | SSPOV         | SSPEN       | CKP          | SSPM3        | SSPM2  | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                       |

| 86h/186h              | TRISB   | TRISB7    | TRISB6        | TRISB5      | TRISB4       | _            | _      | _      | _      | 1111                    | 1111                            |

| 87h/187h              | TRISC   | TRISC7    | TRISC6        | TRISC5      | TRISC4       | TRISC3       | TRISC2 | TRISC1 | TRISC0 | 1111 1111               | 1111 1111                       |

| 8Ch                   | PIE1    | _         | ADIE          | RCIE        | TXIE         | SSPIE        | CCP1IE | TMR2IE | TMR1IE | -000 0000               | -000 0000                       |

| 94h                   | SSPSTAT | SMP       | CKE           | D/A         | Р            | S            | R/W    | UA     | BF     | 0000 0000               | 0000 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

#### REGISTER 14-1: CONFIG: CONFIGURATION WORD REGISTER

| Reserved | Reserved | FCMEN | IESO | BOREN1 <sup>(1)</sup> | BORENO <sup>(1)</sup> | CPD <sup>(2</sup> |

|----------|----------|-------|------|-----------------------|-----------------------|-------------------|

| bit 13   |          |       |      |                       |                       | bit 7             |

| <u>CP</u> (3) | MCLRE <sup>(4)</sup> | PWRTE | WDTE | FOSC2 | FOSC1 | FOSC0 |

|---------------|----------------------|-------|------|-------|-------|-------|

| bit 6         |                      |       |      |       |       | bit 0 |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | P = Programmable'    | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

bit 13-12 Reserved: Reserved bits. Do Not Use. FCMEN: Fail-Safe Clock Monitor Enabled bit bit 11 1 = Fail-Safe Clock Monitor is enabled 0 = Fail-Safe Clock Monitor is disabled IESO: Internal External Switchover bit bit 10 1 = Internal External Switchover mode is enabled 0 = Internal External Switchover mode is disabled BOREN<1:0>: Brown-out Reset Selection bits(1) bit 9-8 11 = BOR enabled 10 = BOR enabled during operation and disabled in Sleep 01 = BOR controlled by SBOREN bit of the PCON register 00 = BOR disabled CPD: Data Code Protection bit(2) bit 7 1 = Data memory code protection is disabled 0 = Data memory code protection is enabled CP: Code Protection bit(2) bit 6 1 = Program memory code protection is disabled 0 = Program memory code protection is enabled MCLRE: MCLR Pin Function Select bit(4) bit 5  $1 = \overline{\text{MCLR}} \text{ pin function is } \overline{\text{MCLR}}$ 0 = MCLR pin function is digital input, MCLR internally tied to VDD **PWRTE**: Power-up Timer Enable bit bit 4 1 = PWRT disabled 0 = PWRT enabled bit 3 WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 2-0 FOSC<2:0>: Oscillator Selection bits 110 =RCIO oscillator: I/O function on RA4/OSC2/CLKOUT pin, RC on RA5/OSC1/CLKIN 101 =INTOSC oscillator: CLKOUT function on RA4/OSC2/CLKOUT pin,

111 =RC oscillator: CLKOUT function on RA4/OSC2/CLKOUT pin, RC on RA5/OSC1/CLKIN

I/O function on RA5/OSC1/CLKIN

100 = INTOSCIO oscillator: I/O function on RA4/OSC2/CLKOUT pin,

I/O function on RA5/OSC1/CLKIN

011 =EC: I/O function on RA4/OSC2/CLKOUT pin, CLKIN on RA5/OSC1/CLKIN

010 =HS oscillator: High-speed crystal/resonator on RA4/OSC2/CLKOUT and RA5/OSC1/CLKIN

001 = XT oscillator: Crystal/resonator on RA4/OSC2/CLKOUT and RA5/OSC1/CLKIN

000 = LP oscillator: Low-power crystal on RA4/OSC2/CLKOUT and RA5/OSC1/CLKIN

Note Enabling Brown-out Reset does not automatically enable Power-up Timer. 1:

The entire data EEPROM will be erased when the code protection is turned off.

The entire program memory will be erased when the code protection is turned off.

When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                        |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', a NOP is executed instead, making it a 2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                        |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] GOTO k                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                        |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                             |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                        |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The 11-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a 2-cycle instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                          |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                            |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |

| INCF             | Increment t                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCF f,d                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                            |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                             |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |

#### 16.0 DEVELOPMENT SUPPORT

The PIC® microcontrollers (MCU) and dsPIC® digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 16.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

#### 16.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 16.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 16.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 16.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 16.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# 17.2 DC Characteristics: PIC16F631/677/685/687/689/690-I (Industrial) PIC16F631/677/685/687/689/690-E (Extended) (Continued)

| DC CHA                       | RACTERISTICS                | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |        |       |     |                                               |  |

|------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|-------|-----|-----------------------------------------------|--|

| Param Device Characteristics |                             | Min.                                                                                                                                                                                                                               | T 4  | Max.   | Units |     | Conditions                                    |  |

| No.                          | Device Characteristics      | IVIII.                                                                                                                                                                                                                             | Тур† | IVIAX. | Units | VDD | Note                                          |  |

| D020                         | Power-down Base             | _                                                                                                                                                                                                                                  | 0.05 | 1.2    | μА    | 2.0 | WDT, BOR, Comparators, VREF and               |  |

|                              | Current(IPD) <sup>(2)</sup> | _                                                                                                                                                                                                                                  | 0.15 | 1.5    | μА    | 3.0 | T1OSC disabled                                |  |

|                              |                             | _                                                                                                                                                                                                                                  | 0.35 | 1.8    | μА    | 5.0 |                                               |  |

|                              |                             | _                                                                                                                                                                                                                                  | 90   | 500    | nA    | 3.0 | -40°C ≤ TA ≤ +25°C                            |  |

| D021                         |                             | _                                                                                                                                                                                                                                  | 1.0  | 2.2    | μА    | 2.0 | WDT Current <sup>(1)</sup>                    |  |

|                              |                             | _                                                                                                                                                                                                                                  | 2.0  | 4.0    | μΑ    | 3.0 |                                               |  |

|                              |                             | _                                                                                                                                                                                                                                  | 3.0  | 7.0    | μΑ    | 5.0 |                                               |  |

| D022                         |                             | _                                                                                                                                                                                                                                  | 42   | 60     | μΑ    | 3.0 | BOR Current <sup>(1)</sup>                    |  |

|                              |                             | _                                                                                                                                                                                                                                  | 85   | 122    | μΑ    | 5.0 |                                               |  |

| D023                         |                             | _                                                                                                                                                                                                                                  | 32   | 45     | μΑ    | 2.0 | Comparator Current <sup>(1)</sup> , both      |  |

|                              |                             | _                                                                                                                                                                                                                                  | 60   | 78     | μΑ    | 3.0 | comparators enabled                           |  |

|                              |                             | _                                                                                                                                                                                                                                  | 120  | 160    | μΑ    | 5.0 |                                               |  |

| D024                         |                             | _                                                                                                                                                                                                                                  | 30   | 36     | μΑ    | 2.0 | CVREF Current <sup>(1)</sup> (high range)     |  |

|                              |                             | _                                                                                                                                                                                                                                  | 45   | 55     | μΑ    | 3.0 |                                               |  |

|                              |                             | _                                                                                                                                                                                                                                  | 75   | 95     | μΑ    | 5.0 |                                               |  |

| D024a*                       |                             | _                                                                                                                                                                                                                                  | 39   | 47     | μΑ    | 2.0 | CVREF Current <sup>(1)</sup> (low range)      |  |

|                              |                             | _                                                                                                                                                                                                                                  | 59   | 72     | μΑ    | 3.0 |                                               |  |

|                              |                             | _                                                                                                                                                                                                                                  | 98   | 124    | μΑ    | 5.0 |                                               |  |

| D025                         |                             |                                                                                                                                                                                                                                    | 2.0  | 5.0    | μΑ    | 2.0 | T1OSC Current, 32.768 kHz                     |  |

|                              |                             | _                                                                                                                                                                                                                                  | 2.5  | 5.5    | μΑ    | 3.0 |                                               |  |

|                              |                             | _                                                                                                                                                                                                                                  | 3.0  | 7.0    | μΑ    | 5.0 |                                               |  |

| D026                         |                             | _                                                                                                                                                                                                                                  | 0.30 | 1.6    | μΑ    | 3.0 | A/D Current <sup>(1)</sup> , no conversion in |  |

|                              |                             | _                                                                                                                                                                                                                                  | 0.36 | 1.9    | μΑ    | 5.0 | progress                                      |  |

| D027                         |                             | _                                                                                                                                                                                                                                  | 90   | 125    | μΑ    | 3.0 | VP6 Current                                   |  |

|                              |                             | _                                                                                                                                                                                                                                  | 125  | 162    | μА    | 5.0 |                                               |  |

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral Δ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

- 5: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

### 17.5 Thermal Considerations

| Param<br>No. | Sym.   Characteristic |                            | Тур.  | Units | Conditions                                               |  |  |  |

|--------------|-----------------------|----------------------------|-------|-------|----------------------------------------------------------|--|--|--|

| TH01         | θЈА                   | Thermal Resistance         | 62.4  | C/W   | 20-pin PDIP package                                      |  |  |  |

|              |                       | Junction to Ambient        | 85.2  | C/W   | 20-pin SOIC package                                      |  |  |  |

|              |                       |                            | 108.1 | C/W   | 20-pin SSOP package                                      |  |  |  |

|              |                       |                            | 40    | C/W   | 20-pin QFN 4x4mm package                                 |  |  |  |

| TH02 θJC     |                       | Thermal Resistance         | 28.1  | C/W   | 20-pin PDIP package                                      |  |  |  |

|              |                       | Junction to Case           | 24.2  | C/W   | 20-pin SOIC package                                      |  |  |  |

|              |                       |                            | 32.2  | C/W   | 20-pin SSOP package                                      |  |  |  |

|              |                       |                            | 2.5   | C/W   | 20-pin QFN 4x4mm package                                 |  |  |  |

| TH03         | TDIE                  | Die Temperature            | 150   | С     | For derated power calculations                           |  |  |  |

| TH04         | PD                    | Power Dissipation          | _     | W     | PD = PINTERNAL + PI/O                                    |  |  |  |

| TH05         | PINTERNAL             | Internal Power Dissipation | _     | W     | PINTERNAL = IDD x VDD (Note 1)                           |  |  |  |

| TH06         | Pı/o                  | I/O Power Dissipation      | _     | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |  |

| TH07         | PDER                  | Derated Power              | _     | W     | PDER = PDMAX (TDIE - TA)/ $\theta$ JA (Note 2, 3)        |  |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

**<sup>2:</sup>** TA = Ambient Temperature.

**<sup>3:</sup>** Maximum allowable power dissipation is the lower value of either the absolute maximum total power dissipation or derated power.

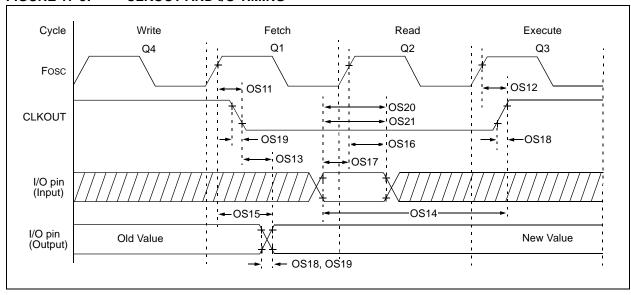

FIGURE 17-5: CLKOUT AND I/O TIMING

**TABLE 17-3: CLKOUT AND I/O TIMING PARAMETERS**

Standard Operating Conditions (unless otherwise stated)

Operating Temperature -40°C < TA < +125°C

| Operating Lemperature -40°C ≤ LA ≤ +125°C |          |                                                           |               |          |          |       |                          |

|-------------------------------------------|----------|-----------------------------------------------------------|---------------|----------|----------|-------|--------------------------|

| Param<br>No.                              | Sym.     | Characteristic                                            | Min.          | Тур†     | Max.     | Units | Conditions               |

| OS11                                      | TosH2cĸL | Fosc↑ to CLKOUT↓ (1)                                      | _             | _        | 70       | ns    | VDD = 5.0V               |

| OS12                                      | TosH2ckH | Fosc↑ to CLKOUT↑ (1)                                      | _             | _        | 72       | ns    | VDD = 5.0V               |

| OS13                                      | TCKL2IOV | CLKOUT↓ to port out valid <sup>(1)</sup>                  | _             | _        | 20       | ns    |                          |

| OS14                                      | TioV2ckH | Port input valid before CLKOUT <sup>(1)</sup>             | Tosc + 200 ns | _        | _        | ns    |                          |

| OS15                                      | TosH2IOV | Fosc↑ (Q1 cycle) to port out valid                        | _             | 50       | 70*      | ns    | VDD = 5.0V               |

| OS16                                      | TosH2iol | Fosc↑ (Q2 cycle) to port input invalid (I/O in hold time) | 50            | _        | _        | ns    | VDD = 5.0V               |

| OS17                                      | TioV2osH | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)  | 20            | _        | _        | ns    |                          |

| OS18                                      | TioR     | Port output rise time <sup>(2)</sup>                      |               | 15<br>40 | 72<br>32 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS19                                      | TioF     | Port output fall time <sup>(2)</sup>                      |               | 28<br>15 | 55<br>30 | ns    | VDD = 2.0V<br>VDD = 5.0V |

| OS20*                                     | TINP     | INT pin input high or low time                            | 25            | _        | _        | ns    |                          |

| OS21*                                     | TRAP     | PORTA interrupt-on-change new input level time            | Tcy           | _        | _        | ns    |                          |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>2:</sup> Includes OSC2 in CLKOUT mode.

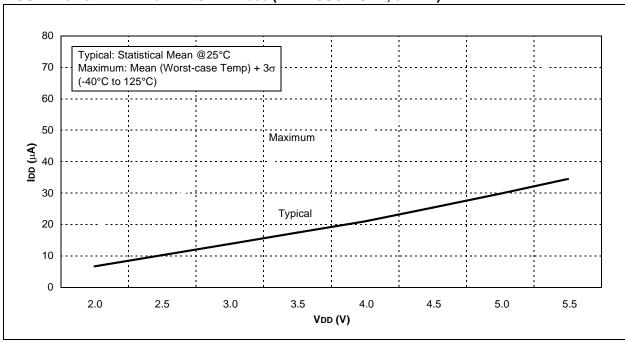

FIGURE 18-10: IDD vs. VDD OVER FOSC (LFINTOSC MODE, 31 kHz)

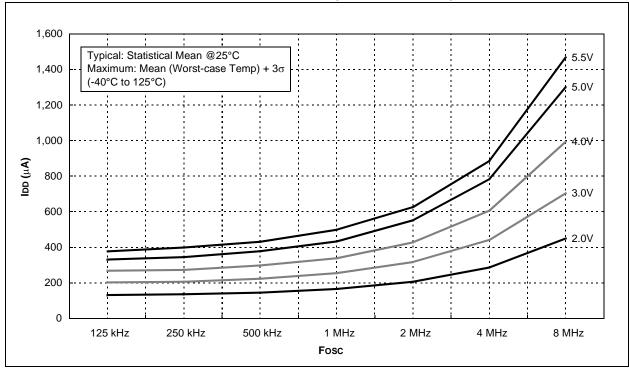

FIGURE 18-11: TYPICAL IDD vs. FOSC OVER VDD (HFINTOSC MODE)