Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

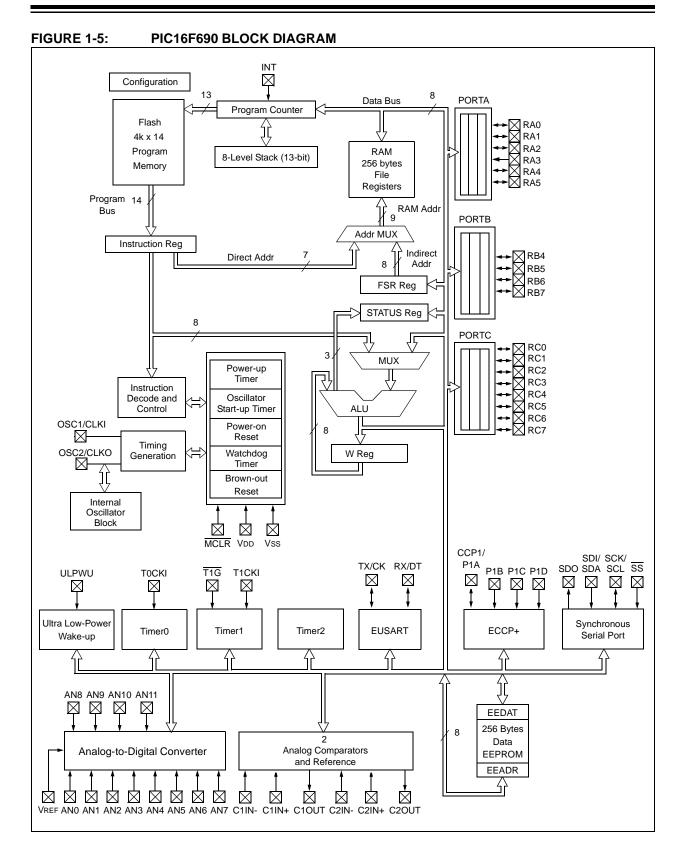

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f689t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-5: PINOUT DESCRIPTION – PIC16F690

| Name                            | Function | Input<br>Type | Output<br>Type | Description                                                                                         |  |  |  |

|---------------------------------|----------|---------------|----------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| RA0/AN0/C1IN+/ICSPDAT/<br>ULPWU | RA0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | AN0      | AN            | —              | A/D Channel 0 input.                                                                                |  |  |  |

|                                 | C1IN+    | AN            | —              | Comparator C1 positive input.                                                                       |  |  |  |

|                                 | ICSPDAT  | TTL           | CMOS           | ICSP™ Data I/O.                                                                                     |  |  |  |

|                                 | ULPWU    | AN            | —              | Ultra Low-Power Wake-up input.                                                                      |  |  |  |

| RA1/AN1/C12IN0-/VREF/ICSPCLK    | RA1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | AN1      | AN            | —              | A/D Channel 1 input.                                                                                |  |  |  |

|                                 | C12IN0-  | AN            | —              | Comparator C1 or C2 negative input.                                                                 |  |  |  |

|                                 | VREF     | AN            | —              | External Voltage Reference for A/D.                                                                 |  |  |  |

|                                 | ICSPCLK  | ST            | —              | ICSP™ clock.                                                                                        |  |  |  |

| RA2/AN2/T0CKI/INT/C1OUT         | RA2      | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | AN2      | AN            | —              | A/D Channel 2 input.                                                                                |  |  |  |

|                                 | T0CKI    | ST            | _              | Timer0 clock input.                                                                                 |  |  |  |

|                                 | INT      | ST            | —              | External interrupt.                                                                                 |  |  |  |

|                                 | C1OUT    | _             | CMOS           | Comparator C1 output.                                                                               |  |  |  |

| RA3/MCLR/Vpp                    | RA3      | TTL           | —              | General purpose input. Individually controlled interrupt-on-<br>change.                             |  |  |  |

|                                 | MCLR     | ST            | —              | Master Clear with internal pull-up.                                                                 |  |  |  |

|                                 | Vpp      | ΗV            | —              | Programming voltage.                                                                                |  |  |  |

| RA4/AN3/T1G/OSC2/CLKOUT         | RA4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | AN3      | AN            | —              | A/D Channel 3 input.                                                                                |  |  |  |

|                                 | T1G      | ST            | _              | Timer1 gate input.                                                                                  |  |  |  |

|                                 | OSC2     |               | XTAL           | Crystal/Resonator.                                                                                  |  |  |  |

|                                 | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                      |  |  |  |

| RA5/T1CKI/OSC1/CLKIN            | RA5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | T1CKI    | ST            | —              | Timer1 clock input.                                                                                 |  |  |  |

|                                 | OSC1     | XTAL          | _              | Crystal/Resonator.                                                                                  |  |  |  |

|                                 | CLKIN    | ST            | _              | External clock input/RC oscillator connection.                                                      |  |  |  |

| RB4/AN10/SDI/SDA                | RB4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | AN10     | AN            | _              | A/D Channel 10 input.                                                                               |  |  |  |

|                                 | SDI      | ST            | _              | SPI data input.                                                                                     |  |  |  |

|                                 | SDA      | ST            | OD             | I <sup>2</sup> C™ data input/output.                                                                |  |  |  |

| RB5/AN11/RX/DT                  | RB5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-<br>change. Individually enabled pull-up. |  |  |  |

|                                 | AN11     | AN            | —              | A/D Channel 11 input.                                                                               |  |  |  |

|                                 | RX       | ST            | _              | EUSART asynchronous input.                                                                          |  |  |  |

|                                 | 10/      | -             |                | EUSART synchronous data.                                                                            |  |  |  |

XTAL= Crystal

| R/W-0         | R-0                                                              | R/W-0                                                                                                        | R/W-0                                    | U-0              | R/W-0            | R/W-0            | R/W-0    |

|---------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|------------------|----------|

| C2ON          | C2OUT                                                            | C2OE                                                                                                         | C2POL                                    | —                | C2R              | C2CH1            | C2CH0    |

| bit 7         |                                                                  |                                                                                                              |                                          |                  |                  |                  | bit 0    |

| Legend:       |                                                                  |                                                                                                              |                                          |                  |                  |                  |          |

| R = Readabl   | e bit                                                            | W = Writable                                                                                                 | bit                                      | U = Unimple      | emented bit, rea | ad as '0'        |          |

| -n = Value at | POR                                                              | '1' = Bit is set                                                                                             |                                          | '0' = Bit is cl  | eared            | x = Bit is unk   | nown     |

| bit 7         | C2ON: Com                                                        | parator C2 Ena                                                                                               | ble bit                                  |                  |                  |                  |          |

|               | 1 = Compara                                                      | ator C2 is enabl<br>ator C2 is disab                                                                         | ed                                       |                  |                  |                  |          |

| bit 6         | C2OUT: Com                                                       | nparator C2 Ou                                                                                               | tput bit                                 |                  |                  |                  |          |

|               | C2OUT = 0 v<br>C2OUT = 1 v<br><u>If C2POL = 0</u><br>C2OUT = 1 v | <u>_ (inverted pola</u><br>when C2VIN+ ><br>when C2VIN+ <<br>(non-inverted<br>when C2VIN+ ><br>when C2VIN+ < | C2VIN-<br>C2VIN-<br>polarity):<br>C2VIN- |                  |                  |                  |          |

| bit 5         | C2OE: Comp                                                       | parator C2 Out                                                                                               | out Enable bit                           |                  |                  |                  |          |

|               |                                                                  | s present on C<br>s internal only                                                                            | 20UT pin <sup>(1)</sup>                  |                  |                  |                  |          |

| bit 4         | C1POL: Con                                                       | nparator C1 Ou                                                                                               | tput Polarity S                          | elect bit        |                  |                  |          |

|               |                                                                  | ogic is inverted<br>ogic is not inve                                                                         |                                          |                  |                  |                  |          |

| bit 3         | Unimplemer                                                       | nted: Read as '                                                                                              | 0'                                       |                  |                  |                  |          |

| bit 2         | C2R: Compa                                                       | arator C2 Refer                                                                                              | ence Select bi                           | ts (non-invertii | ng input)        |                  |          |

|               |                                                                  | connects to C2<br>connects to C2                                                                             |                                          |                  |                  |                  |          |

| bit 1-0       | C2CH<1:0>:                                                       | Comparator C                                                                                                 | 2 Channel Sel                            | ect bits         |                  |                  |          |

|               | 01 = C2VIN-<br>10 = C2VIN-                                       | of C2 connects<br>of C2 connects<br>of C2 connects<br>of C2 connects                                         | to C12IN1- pi<br>to C12IN2- pi           | n<br>n           |                  |                  |          |

|               | TT = CZVIN                                                       | ut requires the f                                                                                            |                                          |                  | 20E = 1, C20I    | N = 1 and corres | sponding |

# REGISTER 8-2: CM2CON0: COMPARATOR C2 CONTROL REGISTER 0

PORT TRIS bit = 0.

| R/W-0              | R/W-0                                | R/W-0                                                   | R/W-0                               | R/S-0            | R/S-0            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0  |

|--------------------|--------------------------------------|---------------------------------------------------------|-------------------------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| SR1 <sup>(2)</sup> | SR0 <sup>(2)</sup>                   | C1SEN                                                   | C2REN                               | PULSS            | PULSR            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _    |

| bit 7              |                                      |                                                         |                                     |                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit  |

|                    |                                      |                                                         |                                     |                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Legend: S          | = Bit is set only                    | ,                                                       |                                     |                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| R = Readable       | e bit                                | W = Writable                                            | bit                                 | U = Unimplei     | mented bit, rea  | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| -n = Value at      | POR                                  | '1' = Bit is set                                        |                                     | '0' = Bit is cle | eared            | x = Bit is unki                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nown |

| bit 7              | 1 = C2OUT                            | ch Configuratio<br>pin is the latch<br>pin is the C2 co | Q output                            | out              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| bit 6              | 1 = C1OUT                            | ch Configuratio<br>pin is the latch<br>pin is the Comp  | Q output                            | out              |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| bit 5              | 1 = C1 com                           | Set Enable bit<br>parator output s<br>parator output h  |                                     | n SR latch       |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| bit 4              | 1 = C2 com                           | Reset Enable b<br>parator output re<br>parator output h | esets SR latch                      |                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| bit 3              | <b>PULSS:</b> Puls<br>1 = Triggers   | se the SET Inpu<br>pulse generato<br>t trigger pulse g  | it of the SR La<br>or to set SR lat | tch bit          | diately reset by | / hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| bit 2              | 1 = Triggers                         | se the Reset In<br>pulse generato<br>t trigger pulse g  | or to reset SR I                    |                  | nediately reset  | by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| bit 1-0            | Unimpleme                            | nted: Read as '                                         | 0'                                  |                  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| th                 | ne CxOUT bit in<br>e pin), regardles | ss of the SR late                                       | h operation.                        | -                |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| O. T.              |                                      | 1 - 4 - 1 4 4 - 4 - 4                                   | le a setter Alle a service          |                  |                  | and the state of the second state of the secon |      |

# REGISTER 8-4: SRCON: SR LATCH CONTROL REGISTER

2: To enable an SR latch output to the pin, the appropriate CxOE and TRIS bits must be properly configured.

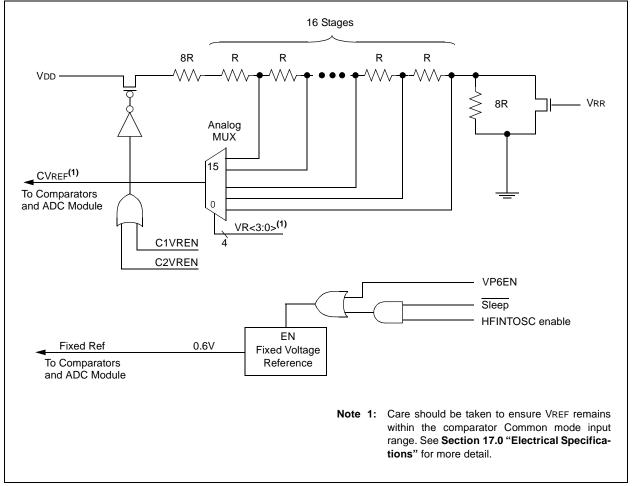

# 8.10.5 FIXED VOLTAGE REFERENCE

The Fixed Voltage Reference is independent of VDD, with a nominal output voltage of 0.6V. This reference can be enabled by setting the VP6EN bit of the VRCON register to '1'. This reference is always enabled when the HFINTOSC oscillator is active.

#### 8.10.6 FIXED VOLTAGE REFERENCE STABILIZATION PERIOD

When the Fixed Voltage Reference module is enabled, it will require some time for the reference and its amplifier circuits to stabilize. The user program must include a small delay routine to allow the module to settle. See the electrical specifications section for the minimum delay requirement.

# 8.10.7 VOLTAGE REFERENCE SELECTION

Multiplexers on the output of the Voltage Reference module enable selection of either the CVREF or Fixed Voltage Reference for use by the comparators.

Setting the C1VREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C1. Clearing the C1VREN bit selects the fixed voltage for use by C1.

Setting the C2VREN bit of the VRCON register enables current to flow in the CVREF voltage divider and selects the CVREF voltage for use by C2. Clearing the C2VREN bit selects the fixed voltage for use by C2.

When both the C1VREN and C2VREN bits are cleared, current flow in the CVREF voltage divider is disabled minimizing the power drain of the voltage reference peripheral.

# FIGURE 8-8: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

# EXAMPLE 9-1: A/D CONVERSION

;This code block configures the ADC ; for polling, Vdd reference, Frc clock ;and AN0 input. ; ;Conversion start & polling for completion ; are included. BANKSELADCON1; MOVLWB'01110000'; ADC Frc clock MOVWFADCON1; BANKSELTRISA; BSF TRISA,0;Set RA0 to input BANKSELANSEL; BSF ANSEL, 0; Set RA0 to analog BANKSELADCON0; MOVLWB'10000001';Right justify, MOVWFADCON0; Vdd Vref, AN0, On CALLSampleTime;Acquisiton delay BSF ADCON0,GO;Start conversion BTFSCADCON0,GO;Is conversion done? GOTO\$-1;No, test again BANKSELADRESH; MOVFADRESH, W; Read upper 2 bits MOVWFRESULTHI; store in GPR space BANKSELADRESL; MOVFADRESL,W;Read lower 8 bits MOVWFRESULTLO; Store in GPR space

### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

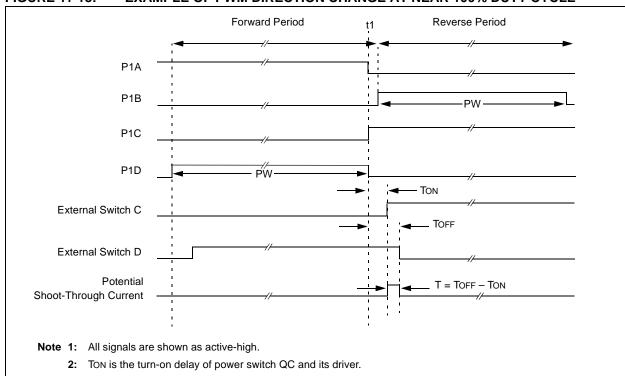

# FIGURE 11-13: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

**3:** TOFF is the turn-off delay of power switch QD and its driver.

# 11.4.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

| Note: | When the microcontroller is released from     |

|-------|-----------------------------------------------|

|       | Reset, all of the I/O pins are in the high-   |

|       | impedance state. The external circuits        |

|       | must keep the power switch devices in the     |

|       | OFF state until the microcontroller drives    |

|       | the I/O pins with the proper signal levels or |

|       | activates the PWM output(s).                  |

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pin output drivers are enabled. Changing the polarity configuration while the PWM pin output drivers are enabled is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pin output drivers at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before enabling the PWM pin output drivers. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

# 11.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Figure 11-19.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 11.4.4** "**Enhanced PWM Auto-shutdown mode**". An autoshutdown event will only affect pins that have PWM outputs enabled.

# **REGISTER 11-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0          | U-0                | U-0              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-1 |

|--------------|--------------------|------------------|------------------|------------------|------------------|-----------------|-------|

| _            |                    | _                | STRSYNC          | STRD             | STRC             | STRB            | STRA  |

| bit 7        |                    | ·                |                  |                  |                  |                 | bit ( |

| Legend:      |                    |                  |                  |                  |                  |                 |       |

| R = Readat   | ole bit            | W = Writable     | bit              | U = Unimpler     | nented bit, read | d as '0'        |       |

| -n = Value a | at POR             | '1' = Bit is se  | t                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                    |                  |                  |                  |                  |                 |       |

| bit 7-5      | Unimpleme          | ented: Read as   | '0'              |                  |                  |                 |       |

| bit 4        | STRSYNC:           | Steering Sync I  | pit              |                  |                  |                 |       |

|              | 1 = Output         | steering update  | occurs on next   | PWM period       |                  |                 |       |

|              | 0 = Output         | steering update  | occurs at the be | eginning of the  | instruction cyc  | le boundary     |       |

| bit 3        | STRD: Stee         | ering Enable bit | D                |                  |                  |                 |       |

|              |                    | has the PWM      |                  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1D pir        | n is assigned to | port pin         |                  |                  |                 |       |

| bit 2        | STRC: Stee         | ering Enable bit | С                |                  |                  |                 |       |

|              | 1 = P1C pir        | has the PWM      | waveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1C pir        | n is assigned to | port pin         |                  |                  |                 |       |

| bit 1        | STRB: Stee         | ering Enable bit | В                |                  |                  |                 |       |

|              | 1 <b>= P1B pir</b> | has the PWM      | vaveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1B pir        | is assigned to p | oort pin         |                  |                  |                 |       |

| bit 0        | STRA: Stee         | ering Enable bit | A                |                  |                  |                 |       |

|              | 1 = P1A pir        | has the PWM      | vaveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |

|              | 0 = P1A pir        | n is assigned to | port pin         |                  |                  |                 |       |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

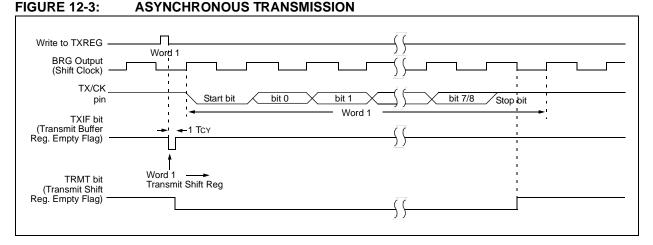

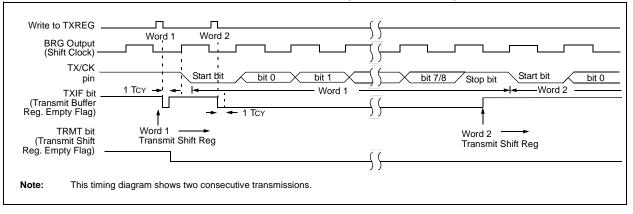

# 12.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

### 12.1.1.5 Transmitting 9-Bit Characters

The EUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set the EUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 12.1.2.7** "Address **Detection**" for more information on the Address mode.

### 12.1.1.6 Asynchronous Transmission Set-up:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 7. Load 8-bit data into the TXREG register. This will start the transmission.

# FIGURE 12-4: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

| Name    | Bit 7      | Bit 6        | Bit 5        | Bit 4               | Bit 3       | Bit 2        | Bit 1      | Bit 0      | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|--------------|--------------|---------------------|-------------|--------------|------------|------------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF     | RCIDL        | —            | SCKP                | BRG16       | _            | WUE        | ABDEN      | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE        | PEIE         | TOIE         | INTE                | RABIE       | T0IF         | INTF       | RABIF      | x000 000x            | 0000 000x                       |

| PIE1    | —          | ADIE         | RCIE         | TXIE                | SSPIE       | CCP1IE       | TMR2IE     | TMR1IE     | -000 0000            | -000 0000                       |

| PIR1    | —          | ADIF         | RCIF         | TXIF                | TMR1IF      | -000 0000    | -000 0000  |            |                      |                                 |

| RCREG   | EUSART F   | Receive Da   | ta Register  |                     |             |              |            |            | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN       | RX9          | SREN         | CREN                | ADDEN       | FERR         | OERR       | RX9D       | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7       | BRG6         | BRG5         | BRG4                | BRG3        | BRG2         | BRG1       | BRG0       | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15      | BRG14        | BRG13        | BRG12               | BRG11       | BRG10        | BRG9       | BRG8       | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7     | TRISB6       | TRISB5       | TRISB4              |             |              |            |            | 1111                 | 1111                            |

| TXREG   | EUSART     | Fransmit Da  | ata Register |                     |             |              |            |            | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC       | TX9          | TXEN         | SYNC                | SENDB       | BRGH         | TRMT       | TX9D       | 0000 0010            | 0000 0010                       |

| Legend: | x = unknow | vn, – = unir | nplemented   | <b>I read as</b> '0 | '. Shaded c | ells are not | used for A | synchronou | is Transmission      | 1.                              |

# TABLE 12-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

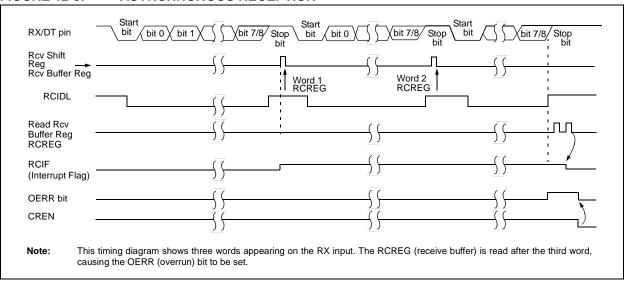

### 12.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 12.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRG register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 12.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

# FIGURE 12-5: ASYNCHRONOUS RECEPTION

# 12.3.2 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCTL register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 12-7), and asynchronously if the device is in Sleep mode (Figure 12-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

### 12.3.2.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

# FIGURE 12-7: AUTO-WAKE-UP BIT (WUE) TIMING DURING NORMAL OPERATION

| 0400      | nininin     | punuinuinu | pinnin. | 9.1        | n na na shi       | uhuhu         | ЪĮ,          | ununun. | punun.                                   | nupunun              | 1. N.    | punununy | րարարա      |

|-----------|-------------|------------|---------|------------|-------------------|---------------|--------------|---------|------------------------------------------|----------------------|----------|----------|-------------|

|           | BR set by p | 98 ·····   | s<br>   | :          | ;                 | :<br>         | ;            |         | :                                        | ;<br>; ;             | :<br>    |          | Osaced      |

| 9863 b8   |             |            | **<br>5 | 1          |                   | 5<br>5        |              |         | -                                        |                      |          | ×        |             |

| 8X3211338 |             | :<br>;     | ;<br>;; | :<br>:     | :<br>annaannain   | Herene        | 2<br>5       |         | 1<br>1                                   | , :<br>.aaaaaaaaaaaa | di Santa | ·        |             |

|           |             |            | :<br>:  | : ?<br>: ? | 444444444444<br>: | 969ilite.<br> | анта<br>29 с |         | \$                                       | yaaqaaaaaaa<br>t     |          | :        |             |

| 8081      |             |            | ·       | · /        |                   |               |              | ·····   |                                          | t                    |          |          |             |

|           |             |            | :       | ÷          |                   |               | ÷            |         | pares dos                                | ાંગ ફેલ્લ્સ શેલ્થ    | C C (    | KCREG)   |             |

| 377       |             | ANGAN MANA | MAMAMA  | Ille       | UMANNANNA         | MAANAA        | MA           |         | HAANAAN AN | CANTAN MAN           | aan      |          | UNICH MANDA |

### 13.12.3 SSP MASK REGISTER

An SSP Mask (SSPMSK) register is available in  $I^2C$ Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit in the SSPSR register a 'don't care'.

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

This register must be initiated prior to setting SSPM<3:0> bits to select the  $I^2C$  Slave mode (7-bit or 10-bit address).

This register can only be accessed when the appropriate mode is selected by bits (SSPM<3:0> of SSPCON).

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

# REGISTER 13-3: SSPMSK: SSP MASK REGISTER<sup>(1)</sup>

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 |       |       |       |       | •     |       | bit 0               |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-1 MSK<7:1>: Mask bits

- 1 = The received address bit n is compared to SSPADD<n> to detect  $I^2C$  address match

- 0 = The received address bit n is not used to detect I<sup>2</sup>C address match

### bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave mode, 10-bit Address<sup>(2)</sup>

- I<sup>2</sup>C Slave mode, 10-bit Address (SSPM<3:0> = 0111):

- 1 = The received address bit 0 is compared to SSPADD<0> to detect  $I^2C$  address match

- 0 = The received address bit 0 is not used to detect  $I^2C$  address match

- **Note 1:** When SSPCON bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. The SSPEN bit of the SSPCON register should be zero when accessing the SSPMSK register.

- 2: In all other SSP modes, this bit has no effect.

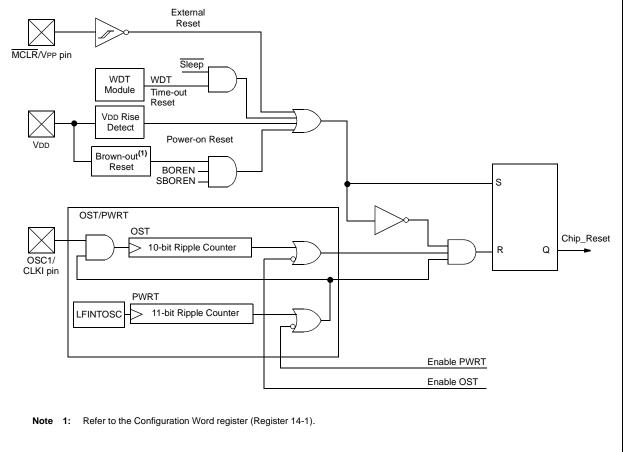

#### 14.2 Reset

The PIC16F631/677/685/687/689/690 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- WDT Reset during Sleep C)

- MCLR Reset during normal operation d)

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

**FIGURE 14-1:**

Brown-out Reset (BOR)

They are not affected by a WDT Wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 14-2. These bits are used in software to determine the nature of the Reset. See Table 14-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 14-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Section 17.0 "Electrical Specifications" for pulse-width specifications.

# External Reset

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

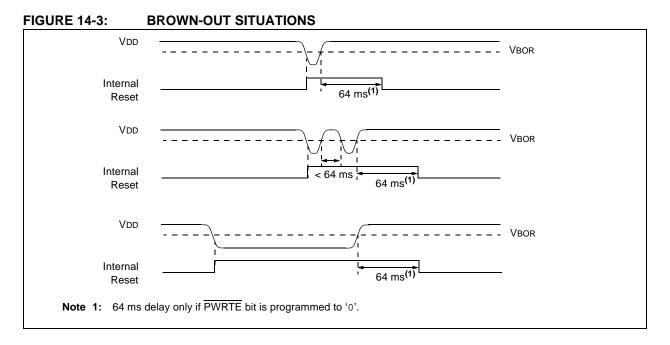

# 14.2.4 BROWN-OUT RESET (BOR)