Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f690-e-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name            | Function | Input<br>Type | Output<br>Type | Description                                                                                        |

|-----------------|----------|---------------|----------------|----------------------------------------------------------------------------------------------------|

| RB7             | RB7      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

| RC0/AN4/C2IN+   | RC0      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN4      | AN            | —              | A/D Channel 4 input.                                                                               |

|                 | C2IN+    | AN            | —              | Comparator C2 non-inverting input.                                                                 |

| RC1/AN5/C12IN1- | RC1      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN5      | AN            | —              | A/D Channel 5 input.                                                                               |

|                 | C12IN1-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC2/AN6/C12IN2- | RC2      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN6      | AN            | —              | A/D Channel 6 input.                                                                               |

|                 | C12IN2-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC3/AN7/C12IN3- | RC3      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN7      | AN            | —              | A/D Channel 7 input.                                                                               |

|                 | C12IN3-  | AN            | —              | Comparator C1 or C2 inverting input.                                                               |

| RC4/C2OUT       | RC4      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | C2OUT    | —             | CMOS           | Comparator C2 output.                                                                              |

| RC5             | RC5      | ST            | CMOS           | General purpose I/O.                                                                               |

| RC6/AN8/SS      | RC6      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN8      | AN            | —              | A/D Channel 8 input.                                                                               |

|                 | SS       | ST            | —              | Slave Select input.                                                                                |

| RC7/AN9/SDO     | RC7      | ST            | CMOS           | General purpose I/O.                                                                               |

|                 | AN9      | AN            | —              | A/D Channel 9 input.                                                                               |

|                 | SDO      | —             | CMOS           | SPI data output.                                                                                   |

| Vss             | Vss      | Power         | _              | Ground reference.                                                                                  |

| Vdd             | Vdd      | Power         | _              | Positive supply.                                                                                   |

#### TABLE 1-2: PINOUT DESCRIPTION – PIC16F677 (CONTINUED)

**Legend:** AN = Analog input or output

TTL = TTL compatible input

HV = High Voltage

XTAL= Crystal

CMOS=CMOS compatible input or output

ST= Schmitt Trigger input with CMOS levels

### FIGURE 2-8: PIC16F690 SPECIAL FUNCTION REGISTERS

|                    | File    |                       | File    |                     | File    |                       | File    |

|--------------------|---------|-----------------------|---------|---------------------|---------|-----------------------|---------|

|                    | Address |                       | Address |                     | Address |                       | Address |

| Indirect addr. (1) | 00h     | Indirect addr. (1)    | 80h     | Indirect addr. (1)  | 100h    | Indirect addr. (1)    | 180h    |

| TMR0               | 01h     | OPTION_REG            | 81h     | TMR0                | 101h    | OPTION_REG            | 181h    |

| PCL                | 02h     | PCL                   | 82h     | PCL                 | 102h    | PCL                   | 182h    |

| STATUS             | 03h     | STATUS                | 83h     | STATUS              | 103h    | STATUS                | 183h    |

| FSR                | 04h     | FSR                   | 84h     | FSR                 | 104h    | FSR                   | 184h    |

| PORTA              | 05h     | TRISA                 | 85h     | PORTA               | 105h    | TRISA                 | 185h    |

| PORTB              | 06h     | TRISB                 | 86h     | PORTB               | 106h    | TRISB                 | 186h    |

| PORTC              | 07h     | TRISC                 | 87h     | PORTC               | 107h    | TRISC                 | 187h    |

|                    | 08h     |                       | 88h     |                     | 108h    |                       | 188h    |

|                    | 09h     |                       | 89h     |                     | 109h    |                       | 189h    |

| PCLATH             | 0Ah     | PCLATH                | 8Ah     | PCLATH              | 10Ah    | PCLATH                | 18Ah    |

| INTCON             | 0Bh     | INTCON                | 8Bh     | INTCON              | 10Bh    | INTCON                | 18Bh    |

| PIR1               | 0Ch     | PIE1                  | 8Ch     | EEDAT               | 10Ch    | EECON1                | 18Ch    |

| PIR2               | 0Dh     | PIE2                  | 8Dh     | EEADR               | 10Dh    | EECON2 <sup>(1)</sup> | 18Dh    |

| TMR1L              | 0Eh     | PCON                  | 8Eh     | EEDATH              | 10Eh    |                       | 18Eh    |

| TMR1H              | 0Fh     | OSCCON                | 8Fh     | EEADRH              | 10Fh    |                       | 18Fh    |

| T1CON              | 10h     | OSCTUNE               | 90h     |                     | 110h    |                       | 190h    |

| TMR2               | 11h     |                       | 91h     |                     | 111h    |                       | 191h    |

| T2CON              | 12h     | PR2                   | 92h     |                     | 112h    |                       | 192h    |

| SSPBUF             | 13h     | SSPADD <sup>(2)</sup> | 93h     |                     | 113h    |                       | 193h    |

| SSPCON             | 14h     | SSPSTAT               | 94h     |                     | 114h    | -                     | 194h    |

| CCPR1L             | 15h     | WPUA                  | 95h     | WPUB                | 115h    | -                     | 195h    |

| CCPR1H             | 16h     | IOCA                  | 96h     | IOCB                | 116h    | -                     | 196h    |

| CCP1CON            | 17h     | WDTCON                | 97h     |                     | 117h    | -                     | 197h    |

| RCSTA              | 18h     | TXSTA                 | 98h     | VRCON               | 118h    | -                     | 198h    |

| TXREG              | 19h     | SPBRG                 | 99h     | CM1CON0             | 119h    |                       | 199h    |

| RCREG              | 1Ah     | SPBRGH                | 9Ah     | CM2CON0             | 11Ah    |                       | 19Ah    |

|                    | 1Bh     | BAUDCTL               | 9Bh     | CM2CON1             | 11Bh    |                       | 19Bh    |

| PWM1CON            | 1Ch     |                       | 9Ch     |                     | 11Ch    |                       | 19Ch    |

| ECCPAS             | 1Dh     |                       | 9Dh     |                     | 11Dh    | PSTRCON               | 19Dh    |

| ADRESH             | 1Eh     | ADRESL                | 9Eh     | ANSEL               | 11Eh    | SRCON                 | 19Eh    |

| ADCON0             | 1Fh     | ADCON1                | 9Fh     | ANSELH              | 11Fh    |                       | 19Fh    |

|                    | 20h     |                       | A0h     |                     | 120h    |                       | 1A0h    |

|                    |         |                       |         |                     |         |                       |         |

| General            |         | General               |         | General             |         |                       |         |

| General<br>Purpose |         | Purpose<br>Register   |         | Purpose<br>Register |         |                       |         |

| Register           |         | register              |         | register            |         |                       |         |

| -                  |         | 80 Bytes              |         | 80 Bytes            |         |                       |         |

| 96 Bytes           |         |                       | EFh     |                     | 16Fh    |                       |         |

|                    |         | accesses              | F0h     | accesses            | 170h    | accesses              | 1F0h    |

|                    | 7Fh     | 70h-7Fh               | FFh     | 70h-7Fh             | 17Fh    | 70h-7Fh               | 1FFh    |

| Bank 0             | 1       | Bank 1                | 1       | Bank 2              | I       | Bank 3                | I       |

Unimplemented data memory locations, read as '0'.

**Note 1:** Not a physical register.

2: Address 93h also accesses the SSP Mask (SSPMSK) register under certain conditions. See Registers 13-2 and 13-3 for more details.

## 3.2 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 3-1) controls the system clock and frequency selection options. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Frequency Status bits (HTS, LTS)

- System clock control bits (OSTS, SCS)

#### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | R/W-1 | R/W-1 | R/W-0 | R-1                 | R-0 | R-0 | R/W-0 |

|---------|-------|-------|-------|---------------------|-----|-----|-------|

| —       | IRCF2 | IRCF1 | IRCF0 | OSTS <sup>(1)</sup> | HTS | LTS | SCS   |

| bit 7   |       |       |       |                     |     |     | bit 0 |

|         |       |       |       |                     |     |     |       |

| Legend: |       |       |       |                     |     |     |       |

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7   | Unimplemented: Read as '0'                                                                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | IRCF<2:0>: Internal Oscillator Frequency Select bits<br>111 = 8 MHz<br>110 = 4 MHz (default)<br>101 = 2 MHz<br>100 = 1 MHz<br>011 = 500 kHz<br>010 = 250 kHz<br>001 = 125 kHz<br>000 = 31 kHz (LFINTOSC)                             |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup><br>1 = Device is running from the clock defined by FOSC<2:0> of the CONFIG register<br>0 = Device is running from the internal oscillator (HFINTOSC or LFINTOSC) |

| bit 2   | <ul> <li>HTS: HFINTOSC Status bit (High Frequency – 8 MHz to 125 kHz)</li> <li>1 = HFINTOSC is stable</li> <li>0 = HFINTOSC is not stable</li> </ul>                                                                                 |

| bit 1   | LTS: LFINTOSC Stable bit (Low Frequency – 31 kHz)<br>1 = LFINTOSC is stable<br>0 = LFINTOSC is not stable                                                                                                                            |

| bit 0   | <ul> <li>SCS: System Clock Select bit</li> <li>1 = Internal oscillator is used for system clock</li> <li>0 = Clock source defined by FOSC&lt;2:0&gt; of the CONFIG register</li> </ul>                                               |

| Note 1. | Discrete to (o) with Two Greed Oters up and LD VT or LIC collected on the Opeillater mode on Feil                                                                                                                                    |

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

### 3.5.2.1 OSCTUNE Register

-n = Value at POR

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

x = Bit is unknown

### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

'1' = Bit is set

| U-0                               | U-0 | U-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------------------------|-----|-----|-------|------------------------------------|-------|-------|-------|--|

| —                                 | —   | —   | TUN4  | TUN3                               | TUN2  | TUN1  | TUN0  |  |

| bit 7                             |     |     |       |                                    |       |       | bit 0 |  |

|                                   |     |     |       |                                    |       |       |       |  |

| Legend:                           |     |     |       |                                    |       |       |       |  |

| R = Readable bit W = Writable bit |     |     | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |

'0' = Bit is cleared

| bit 7-5 | Unimplemented: Read as '0'                                                |

|---------|---------------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                           |

|         | 01111 = Maximum frequency                                                 |

|         | 01110 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 00001 =                                                                   |

|         | 00000 = Oscillator module is running at the factory-calibrated frequency. |

|         | 11111 =                                                                   |

|         | •                                                                         |

|         | •                                                                         |

|         | •                                                                         |

|         | 10000 = Minimum frequency                                                 |

|         |                                                                           |

# 4.2 Additional Pin Functions

Every PORTA pin on this device family has an interrupton-change option and a weak pull-up option. RA0 also has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

## 4.2.1 ANSEL AND ANSELH REGISTERS

The ANSEL and ANSELH registers are used to disable the input buffers of I/O pins, which allow analog voltages to be applied to those pins without causing excessive current. Setting the ANSx bit of a corresponding pin will cause all digital reads of that pin to return '0' and also permit analog functions of that pin to operate correctly.

The state of the ANSx bit has no effect on the digital output function of its corresponding pin. A pin with the TRISx bit clear and ANSx bit set will operate as a digital output, together with the analog input function of that pin. Pins with the ANSx bit set always read '0', which can cause unexpected behavior when executing read or write operations on the port due to the read-modifywrite sequence of all such operations.

## 4.2.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-4. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RABPU bit of the OPTION register. A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an I/O. There is no software control of the MCLR pull-up.

## 4.2.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCAx enable or disable the interrupt function for each pin. Refer to Register 4-6. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (RABIF) in the INTCON register (Register 2-6).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTA. This will end the mismatch condition, then,

- b) Clear the flag bit RABIF.

A mismatch condition will continue to set flag bit RABIF. Reading PORTA will end the mismatch condition and allow flag bit RABIF to be cleared. The latch holding the last read value is not affected by a MCLR nor BOR Reset. After these Resets, the RABIF flag will continue to be set if a mismatch is present.

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RABIF interrupt flag may not get set.

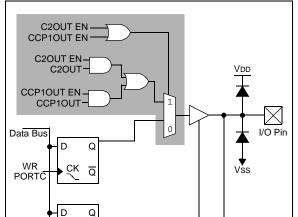

## 4.5.5 RC4/C2OUT/P1B

The RC4/C2OUT/P1B<sup>(1, 2)</sup> is configurable to function as one of the following:

- a general purpose I/O

- a digital output from Comparator C2

- a PWM output

WR

TRISC

RD TRISC RD PORTC

<u>CK</u> Q

- Note 1: Enabling both C2OUT and P1B will cause a conflict on RC4 and create unpredictable results. Therefore, if C2OUT is enabled, the ECCP+ can not be used in Half-Bridge or Full-Bridge mode and vise-versa.

- 2: P1B is available on PIC16F685/ PIC16F690 only.

Available on PIC16F685/PIC16F690 only.

### FIGURE 4-13: BLOCK DIAGRAM OF RC4

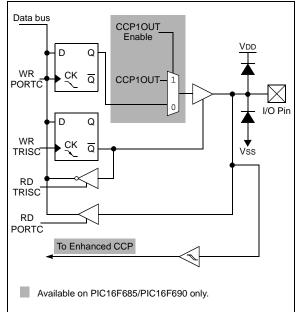

## 4.5.6 RC5/CCP1/P1A

The RC5/CCP1/P1A<sup>(1)</sup> is configurable to function as one of the following:

- a general purpose I/O

- a digital input/output for the Enhanced CCP

- a PWM output

Note 1: CCP1 and P1A are available on PIC16F685/PIC16F690 only.

#### FIGURE 4-14: BLOCK DIAGRAM OF RC5

# 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

### REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0                                                                                                            | R/W-0                                                  | R/W-0            | R/W-0                                                                                                                  | R/W-0             | R/W-0         | R/W-0           | R/W-0      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|-----------------|------------|--|--|--|--|

| T1GINV <sup>(1)</sup>                                                                                            | ) TMR1GE <sup>(2)</sup>                                | T1CKPS1          | T1CKPS0                                                                                                                | T1OSCEN           | T1SYNC        | TMR1CS          | TMR10N     |  |  |  |  |

| bit 7                                                                                                            |                                                        |                  |                                                                                                                        |                   |               |                 | bit 0      |  |  |  |  |

|                                                                                                                  |                                                        |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| Legend:                                                                                                          |                                                        |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| R = Readab                                                                                                       |                                                        | W = Writable     |                                                                                                                        | U = Unimplen      |               |                 |            |  |  |  |  |

| -n = Value a                                                                                                     | IT POR                                                 | '1' = Bit is set |                                                                                                                        | '0' = Bit is clea | ared          | x = Bit is unki | nown       |  |  |  |  |

| bit 7                                                                                                            | T1GINV: Time                                           | er1 Gate Invert  | bit(1)                                                                                                                 |                   |               |                 |            |  |  |  |  |

|                                                                                                                  |                                                        |                  |                                                                                                                        | ints when Timer   | 1 gate signal | is high)        |            |  |  |  |  |

|                                                                                                                  |                                                        |                  | te is active-high (Timer1 counts when Timer1 gate signal is high)<br>te is active-low (Timer1 counts when gate is low) |                   |               |                 |            |  |  |  |  |

| bit 6                                                                                                            | TMR1GE: Tin                                            | ner1 Gate Ena    | ble bit <sup>(2)</sup>                                                                                                 |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | If TMR1ON =                                            |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | This bit is igno                                       |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | <u>If TMR1ON =</u><br>1 = Timer1 co                    |                  | olled by the Ti                                                                                                        | mer1 Gate fund    | tion          |                 |            |  |  |  |  |

|                                                                                                                  |                                                        | always countir   |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| bit 5-4                                                                                                          | T1CKPS<1:0                                             | >: Timer1 Inpu   | t Clock Presca                                                                                                         | ale Select bits   |               |                 |            |  |  |  |  |

|                                                                                                                  | 11 = 1:8 Pres                                          | cale Value       |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 10 = 1:4 Pres                                          |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 01 = 1:2 Pres<br>00 = 1:1 Pres                         |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| bit 3                                                                                                            |                                                        | P Oscillator En  | able Control b                                                                                                         | it                |               |                 |            |  |  |  |  |

|                                                                                                                  | If INTOSC wit                                          | thout CLKOUT     | oscillator is a                                                                                                        | <u>ctive:</u>     |               |                 |            |  |  |  |  |

|                                                                                                                  |                                                        | tor is enabled   | for Timer1 cloc                                                                                                        | ck                |               |                 |            |  |  |  |  |

|                                                                                                                  | 0 = LP oscilla<br><u>Else:</u>                         | tor is off       |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | This bit is igno                                       | ored             |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| bit 2                                                                                                            | 0                                                      |                  | lock Input Syr                                                                                                         | hchronization Co  | ontrol bit    |                 |            |  |  |  |  |

|                                                                                                                  | <u>TMR1CS = 1</u> :                                    |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  |                                                        | nchronize exte   |                                                                                                                        | ıt                |               |                 |            |  |  |  |  |

|                                                                                                                  |                                                        | ize external clo | ock input                                                                                                              |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | <u>TMR1CS = 0:</u><br>This bit is igne                 | ored. Timer1 u   | ses the interna                                                                                                        | al clock          |               |                 |            |  |  |  |  |

| bit 1                                                                                                            | 0                                                      | ner1 Clock Sou   |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 1 = External clock from T1CKI pin (on the rising edge) |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 0 = Internal clock (Fosc/4)                            |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| bit 0                                                                                                            | TMR1ON: Tin                                            | ner1 On bit      |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 1 = Enables Timer1                                     |                  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 0 = Stops Tim                                          | ner1             |                                                                                                                        |                   |               |                 |            |  |  |  |  |

|                                                                                                                  | 1GINV bit inverts                                      | -                |                                                                                                                        |                   |               |                 |            |  |  |  |  |

| 2: TMR1GE bit must be set to use either $\overline{T1G}$ pin or C2OUT, as selected by the T1GSS bit of the CM2CO |                                                        |                  |                                                                                                                        |                   |               |                 | ne CM2CON1 |  |  |  |  |

| r                                                                                                                | egister, as a Time                                     | era gate source  |                                                                                                                        |                   |               |                 |            |  |  |  |  |

# 8.5 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in the **Section 17.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. Each comparator is turned off by clearing the CxON bit of the CMxCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CxIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

## 8.6 Effects of a Reset

A device Reset forces the CMxCON0 and CM2CON1 registers to their Reset states. This forces both comparators and the voltage references to their OFF states.

| R/W-0        | R-0                                                                       | R/W-0                                                                    | R/W-0           | U-0               | R/W-0           | R/W-0            | R/W-0    |  |  |  |  |

|--------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------|-------------------|-----------------|------------------|----------|--|--|--|--|

| C10N         | C1OUT                                                                     | C1OE                                                                     | C1POL           |                   | C1R             | C1CH1            | C1CH0    |  |  |  |  |

| bit 7        | ·                                                                         | ·                                                                        |                 |                   | ·               |                  | bit      |  |  |  |  |

| Legend:      |                                                                           |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

| R = Readal   | hle hit                                                                   | W = Writable                                                             | bit             | LI = Unimple      | mented bit, rea | ad as 'O'        |          |  |  |  |  |

| -n = Value a |                                                                           | '1' = Bit is se                                                          |                 | '0' = Bit is cle  |                 | x = Bit is unk   | nown     |  |  |  |  |

|              |                                                                           |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

| bit 7        | C1ON: Con                                                                 | nparator C1 Ena                                                          | ble bit         |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | rator C1 is enab                                                         |                 |                   |                 |                  |          |  |  |  |  |

| h:+ C        | •                                                                         | rator C1 is disab                                                        |                 |                   |                 |                  |          |  |  |  |  |

| bit 6        |                                                                           | mparator C1 Ou                                                           | •               |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | $\frac{\text{If C1POL} = 1}{\text{(inverted polarity)}}$                 |                 |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | C1OUT = 0 when $C1VIN + > C1VIN$ -<br>C1OUT = 1 when $C1VIN + < C1VIN$ - |                 |                   |                 |                  |          |  |  |  |  |

|              | $\frac{1601}{1600} = 1 \text{ when } C1010 + < C1010 - \frac{1600}{1600}$ |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | C1OUT = 1  when  C1VIN+ > C1VIN-                                         |                 |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | DUT = 0 when $C1VIN + < C1VIN$ -                                         |                 |                   |                 |                  |          |  |  |  |  |

| bit 5        | C1OE: Com                                                                 | nparator C1 Out                                                          | put Enable bit  |                   |                 |                  |          |  |  |  |  |

|              | 1 = C1OUT                                                                 | C1OUT is present on the C1OUT pin <sup>(1)</sup>                         |                 |                   |                 |                  |          |  |  |  |  |

|              | 0 = C1OUT                                                                 | = C1OUT is internal only                                                 |                 |                   |                 |                  |          |  |  |  |  |

| bit 4        | C1POL: Co                                                                 | POL: Comparator C1 Output Polarity Select bit                            |                 |                   |                 |                  |          |  |  |  |  |

|              | 1 = C1OUT logic is inverted                                               |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

|              | 0 = C1OUT                                                                 | = C1OUT logic is not inverted                                            |                 |                   |                 |                  |          |  |  |  |  |

| bit 3        | Unimpleme                                                                 | ented: Read as                                                           | '0'             |                   |                 |                  |          |  |  |  |  |

| bit 2        | C1R: Comp                                                                 | arator C1 Refer                                                          | ence Select bi  | it (non-inverting | g input)        |                  |          |  |  |  |  |

|              | 1 = C1VIN+ connects to C1VREF output                                      |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

|              | 0 = C1VIN+ connects to C1IN+ pin                                          |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

| bit 1-0      | C1CH<1:0>                                                                 | C1CH<1:0>: Comparator C1 Channel Select bit                              |                 |                   |                 |                  |          |  |  |  |  |

|              | 00 = C1VIN- of C1 connects to C12IN0- pin                                 |                                                                          |                 |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | - of C1 connects                                                         |                 |                   |                 |                  |          |  |  |  |  |

|              |                                                                           | <ul> <li>of C1 connects</li> </ul>                                       |                 |                   |                 |                  |          |  |  |  |  |

|              | 11 = C1VIN                                                                | - of C1 connects                                                         | s to C12IN3- p  | in                |                 |                  |          |  |  |  |  |

| Note 1:      | Comparator outp                                                           | out requires the                                                         | following three | e conditions: C1  | 10E = 1. C10N   | N = 1 and corres | spondina |  |  |  |  |

|              |                                                                           |                                                                          | 5               |                   | ,               |                  |          |  |  |  |  |

## REGISTER 8-1: CM1CON0: COMPARATOR C1 CONTROL REGISTER 0

**Note 1:** Comparator output requires the following three conditions: C1OE = 1, C1ON = 1 and corresponding PORT TRIS bit = 0.

## 11.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 11.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 3.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for additional details.

#### 11.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

#### 11.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Disable the PWM pin (CCP1) output driver by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- Set the PWM duty cycle by loading the CCPR1L register and DC1B<1:0> bits of the CCP1CON register.

- 5. Configure and start Timer2:

- •Clear the TMR2IF interrupt flag bit of the PIR1 register.

•Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

•Enable Timer2 by setting the TMR2ON bit of the T2CON register.

6. Enable PWM output after a new PWM cycle has started:

•Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

• Enable the CCP1 pin output driver by clearing the associated TRIS bit.

## 11.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to ten bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 11-4 shows the pin assignments for each Enhanced PWM mode.

Figure 11-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Note: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

### 11.4.7 PULSE STEERING MODE

In Single Output mode, pulse steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCP1M<3:2> = 11 and P1M<1:0> = 00 of the CCP1CON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STR<D:A> bits of the PSTRCON register, as shown in Figure 11-19.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCP1M<1:0> bits of the CCP1CON register select the PWM output polarity for the P1<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 11.4.4** "**Enhanced PWM Auto-shutdown mode**". An autoshutdown event will only affect pins that have PWM outputs enabled.

## **REGISTER 11-4: PSTRCON: PULSE STEERING CONTROL REGISTER<sup>(1)</sup>**

| U-0          | U-0                | U-0                                                                    | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-1 |  |  |  |  |

|--------------|--------------------|------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _            |                    | _                                                                      | STRSYNC          | STRD             | STRC             | STRB            | STRA  |  |  |  |  |

| bit 7        |                    | ·                                                                      |                  |                  |                  |                 | bit ( |  |  |  |  |

| Legend:      |                    |                                                                        |                  |                  |                  |                 |       |  |  |  |  |

| R = Readat   | ole bit            | W = Writable                                                           | bit              | U = Unimpler     | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | at POR             | '1' = Bit is se                                                        | t                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|              |                    |                                                                        |                  |                  |                  |                 |       |  |  |  |  |

| bit 7-5      | Unimpleme          | ented: Read as                                                         | '0'              |                  |                  |                 |       |  |  |  |  |

| bit 4        | STRSYNC:           | Steering Sync I                                                        | pit              |                  |                  |                 |       |  |  |  |  |

|              | 1 = Output         | L = Output steering update occurs on next PWM period                   |                  |                  |                  |                 |       |  |  |  |  |

|              | 0 = Output         | steering update                                                        | occurs at the be | eginning of the  | instruction cyc  | le boundary     |       |  |  |  |  |

| bit 3        | STRD: Stee         | STRD: Steering Enable bit D                                            |                  |                  |                  |                 |       |  |  |  |  |

|              |                    | has the PWM                                                            |                  | olarity control  | from CCP1M<      | 1:0>            |       |  |  |  |  |

|              | 0 = P1D pir        | n is assigned to                                                       | port pin         |                  |                  |                 |       |  |  |  |  |

| bit 2        | STRC: Stee         | ering Enable bit                                                       | С                |                  |                  |                 |       |  |  |  |  |

|              | 1 = P1C pir        | has the PWM                                                            | waveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |  |  |  |  |

|              | 0 = P1C pir        | 0 = P1C pin is assigned to port pin                                    |                  |                  |                  |                 |       |  |  |  |  |

| bit 1        | STRB: Stee         | STRB: Steering Enable bit B                                            |                  |                  |                  |                 |       |  |  |  |  |

|              | 1 <b>= P1B pir</b> | 1 = P1B pin has the PWM waveform with polarity control from CCP1M<1:0> |                  |                  |                  |                 |       |  |  |  |  |

|              | 0 = P1B pir        | 0 = P1B pin is assigned to port pin                                    |                  |                  |                  |                 |       |  |  |  |  |

| bit 0        | STRA: Stee         | STRA: Steering Enable bit A                                            |                  |                  |                  |                 |       |  |  |  |  |

|              | 1 = P1A pir        | has the PWM                                                            | vaveform with p  | olarity control  | from CCP1M<      | 1:0>            |       |  |  |  |  |

|              | 0 = P1A pir        | n is assigned to                                                       | port pin         |                  |                  |                 |       |  |  |  |  |

Note 1: The PWM Steering mode is available only when the CCP1CON register bits CCP1M<3:2> = 11 and P1M<1:0> = 00.

### 13.12.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address <u>byte</u> overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON register is set. This is an error condition due to the user's firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF of the PIR1 register must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

| FIGURE 13-8: | I <sup>2</sup> C <sup>™</sup> WAVEFORMS FOR RECEPTION (7-BIT ADDRESS) |

|--------------|-----------------------------------------------------------------------|

|              |                                                                       |

| - R/                                                         | $\overline{V} = 0$ |                    |                                |                                                        |   |

|--------------------------------------------------------------|--------------------|--------------------|--------------------------------|--------------------------------------------------------|---|

| Receiving Address                                            | ACK Receivi        | ng Data AC         | CK Receiving Data              | ACK                                                    |   |

| SDA 1 / A7 XA6 XA5 XA4 XA3 XA2 XA1                           | /D7/D6/D5/D4       | D3/D2/D1/D0/       | /D7/D6/D5/D4/D3/D2/            |                                                        |   |

|                                                              |                    |                    |                                |                                                        |   |

| SCL <u>'IS</u> ! <u>1</u> 2 <u>3</u> 4 <u>5</u> 6 <u>7</u> 8 | 9 - 1 / 3 / 4      | 5 6 7 8 9          |                                | /7\_/8 <del>\</del> _/9\ / <sup> </sup> P <sup> </sup> |   |

|                                                              |                    |                    |                                |                                                        |   |

|                                                              |                    |                    | 1                              | <u>i   T</u>                                           |   |

| SSPIF (PIR1<3>)                                              | Cleare             | d in software      |                                | Bus Maste                                              |   |

|                                                              |                    | 1                  |                                | terminates                                             | s |

| BF (SSPSTAT<0>)                                              | SSPBUF r           | egister is read    |                                |                                                        |   |

|                                                              |                    | giotorioredu       |                                | I I                                                    |   |

|                                                              |                    |                    |                                | I I                                                    |   |

| SSPOV (SSPCON<6>)                                            |                    |                    |                                |                                                        |   |

|                                                              | Dit                |                    | se the SSPBUF register is stil | U 6.0                                                  |   |

|                                                              | DIL                | SSPOV is set becau | 8                              |                                                        |   |

|                                                              |                    |                    | ACK is not                     | t sent.                                                |   |

|                                                              |                    |                    |                                |                                                        |   |

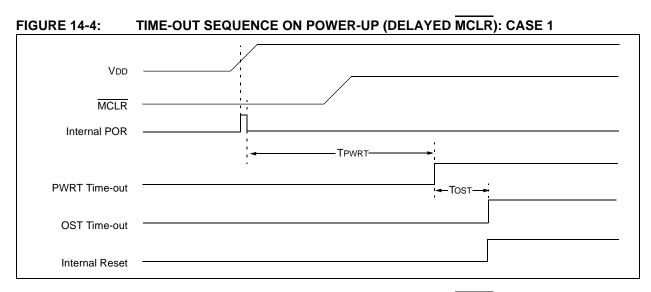

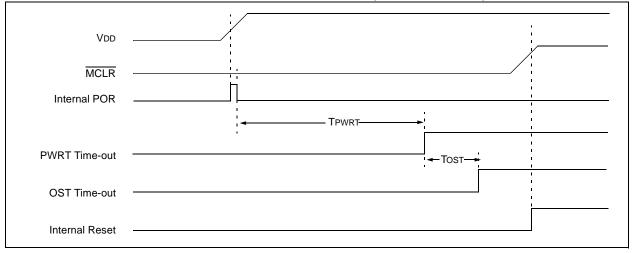

### FIGURE 14-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 2

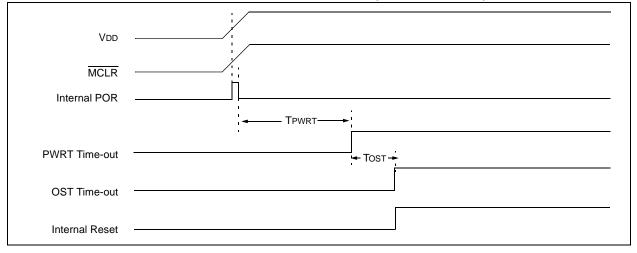

#### FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD)

© 2005-2015 Microchip Technology Inc.

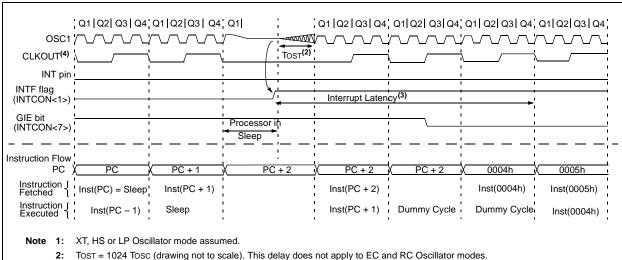

- **3:** GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

- 4. CLKOLIT is not subject to VT HS LD as EC Oscillator mades but a base for their sectors

- 4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

WAKE-UP FROM SLEEP THROUGH INTERRUPT

# 14.7 Code Protection

FIGURE 14-10:

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using  $\text{ICSP}^{\text{TM}}$  for verification purposes.

| Note: | The entire data EEPROM and Flash            |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | program memory will be erased when the      |  |  |  |  |  |

|       | code protection is switched from on to off. |  |  |  |  |  |

|       | See the "PIC12F6XX/16F6XX Memory            |  |  |  |  |  |

|       | Programming Specification" (DS41204)        |  |  |  |  |  |

|       | for more information.                       |  |  |  |  |  |

# 14.8 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify mode. Only the Least Significant seven bits of the ID locations are used.

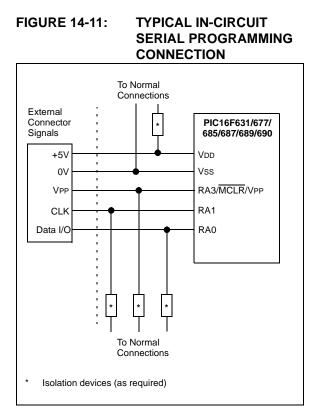

# 14.9 In-Circuit Serial Programming

The PIC16F631/677/685/687/689/690 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RA0/AN0/C1IN+/ICSPDAT/ULPWU and RA1/AN1/C12IN-/VREF/ICSPCLK pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information. RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Program/Verify mode, the Program Counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the "*PIC12F6XX/16F6XX Memory Programming Specification*" (DS41204).

A typical In-Circuit Serial Programming connection is shown in Figure 14-11.

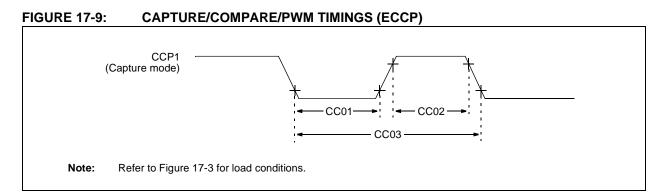

## TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |      |      |       |                                       |  |  |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------------|--|--|

| Param<br>No.                                                                                                         | Sym. | Characteristic       |                | Min.                  | Тур† | Max. | Units | Conditions                            |  |  |

| CC01*                                                                                                                | TccL | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                       |  |  |

|                                                                                                                      |      |                      | With Prescaler | 20                    | —    | —    | ns    |                                       |  |  |

| CC02*                                                                                                                | ТссН | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | _    | —    | ns    |                                       |  |  |

|                                                                                                                      |      |                      | With Prescaler | 20                    | _    | —    | ns    |                                       |  |  |

| CC03*                                                                                                                | TccP | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —    | ns    | N = prescale<br>value (1, 4 or<br>16) |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

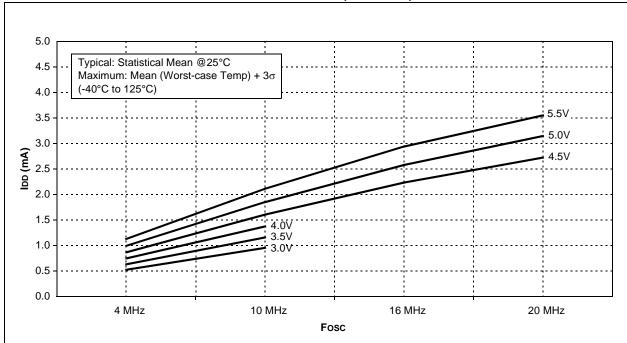

#### FIGURE 18-12: MAXIMUM IDD vs. Fosc OVER VDD (HFINTOSC MODE)

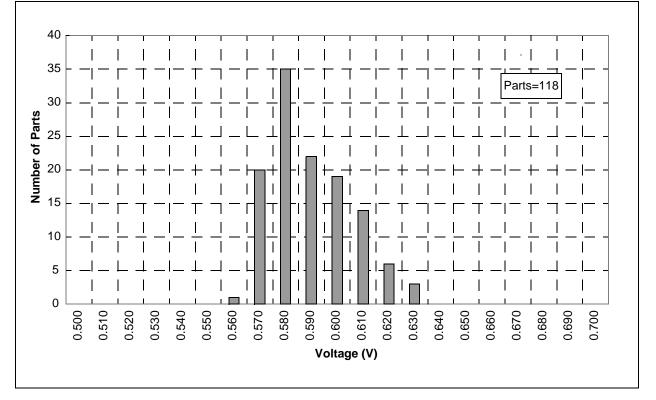

FIGURE 18-47: TYPICAL VP6 REFERENCE VOLTAGE DISTRIBUTION (3V, 85°C)