Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 18                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 20-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f690-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

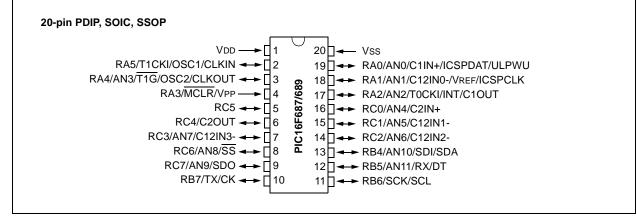

#### PIC16F687/689 Pin Diagram

#### TABLE 4: PIC16F687/689 PIN SUMMARY

| I/O | Pin | Analog    | Comparators | Timers | EUSART | SSP     | Interrupt | Pull-up | Basic       |

|-----|-----|-----------|-------------|--------|--------|---------|-----------|---------|-------------|

| RA0 | 19  | AN0/ULPWU | C1IN+       |        | —      | _       | IOC       | Y       | ICSPDAT     |

| RA1 | 18  | AN1/VREF  | C12IN0-     | —      | —      | —       | IOC       | Y       | ICSPCLK     |

| RA2 | 17  | AN2       | C1OUT       | T0CKI  | —      | —       | IOC/INT   | Y       |             |

| RA3 | 4   | —         | —           | —      | —      |         | IOC       | Y(1)    | MCLR/Vpp    |

| RA4 | 3   | AN3       | —           | T1G    | —      | _       | IOC       | Y       | OSC2/CLKOUT |

| RA5 | 2   | —         | —           | T1CKI  | —      | _       | IOC       | Y       | OSC1/CLKIN  |

| RB4 | 13  | AN10      | —           | _      | —      | SDI/SDA | IOC       | Y       | —           |

| RB5 | 12  | AN11      | —           | —      | RX/DT  |         | IOC       | Y       | —           |

| RB6 | 11  | —         | —           | —      | —      | SCL/SCK | IOC       | Y       | —           |

| RB7 | 10  | —         | —           | _      | TX/CK  |         | IOC       | Y       | —           |

| RC0 | 16  | AN4       | C2IN+       | —      | _      |         |           |         | —           |

| RC1 | 15  | AN5       | C12IN1-     | _      | _      |         |           |         | —           |

| RC2 | 14  | AN6       | C12IN2-     | —      | —      |         |           | _       | —           |

| RC3 | 7   | AN7       | C12IN3-     | —      | —      |         |           | —       | —           |

| RC4 | 6   | _         | C2OUT       | —      |        |         |           |         | —           |

| RC5 | 5   | _         | —           | _      | _      |         |           |         | —           |

| RC6 | 8   | AN8       | —           | —      | —      | SS      | —         |         | —           |

| RC7 | 9   | AN9       | —           |        | _      | SDO     | _         |         | —           |

| —   | 1   | —         | —           |        | _      |         | _         |         | Vdd         |

| —   | 20  | _         | —           |        |        |         | _         |         | Vss         |

Note 1: Pull-up activated only with external MCLR configuration.

#### 2.2.2.6 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-6.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-6: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R-0                 | R-0                 | R/W-0                | R/W-0                 | R/W-0                 | R/W-0  |

|-------|---------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|--------|

| —     | ADIF <sup>(5)</sup> | RCIF <sup>(3)</sup> | TXIF <sup>(3)</sup> | SSPIF <sup>(4)</sup> | CCP1IF <sup>(2)</sup> | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                     |                     |                      |                       |                       | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7 | Unimplemented: Read as '0'                                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit <sup>(5)</sup>                                                                                               |

|       | <ul> <li>1 = A/D conversion complete (must be cleared in software)</li> <li>0 = A/D conversion has not completed or has not been started</li> </ul> |

| bit 5 | RCIF: EUSART Receive Interrupt Flag bit <sup>(3)</sup>                                                                                              |

|       | <ul> <li>1 = The EUSART receive buffer is full (cleared by reading RCREG)</li> <li>0 = The EUSART receive buffer is not full</li> </ul>             |

| bit 4 | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit <sup>(3)</sup>                                                                                      |

|       | <ul> <li>1 = The EUSART transmit buffer is empty (cleared by writing to TXREG)</li> <li>0 = The EUSART transmit buffer is full</li> </ul>           |

| bit 3 | SSPIF: Synchronous Serial Port (SSP) Interrupt Flag bit <sup>(4)</sup>                                                                              |

|       | <ul> <li>1 = The Transmission/Reception is complete (must be cleared in software)</li> <li>0 = Waiting to Transmit/Receive</li> </ul>               |

| bit 2 | CCP1IF: CCP1 Interrupt Flag bit <sup>(2)</sup>                                                                                                      |

|       | Capture mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> </ul>               |

|       | Compare mode:                                                                                                                                       |

|       | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul>   |

|       | <u>PWM mode:</u>                                                                                                                                    |

|       | Unused in this mode                                                                                                                                 |

| bit 1 | TMR2IF: Timer2 to PR2 Interrupt Flag bit <sup>(1)</sup>                                                                                             |

|       | <ul> <li>1 = A Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No Timer2 to PR2 match occurred</li> </ul>                   |

| bit 0 | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                                          |

|       | <ul> <li>1 = The TMR1 register overflowed (must be cleared in software)</li> <li>0 = The TMR1 register did not overflow</li> </ul>                  |

| Note  | 1: PIC16F685/PIC16F690 only.                                                                                                                        |

|       | 2: PIC16F685/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 3: PIC16F687/PIC16F689/PIC16F690 only.                                                                                                              |

|       | 4: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.                                                                                                    |

|       | 5: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.                                                                                          |

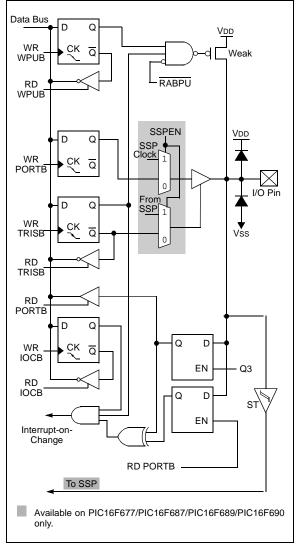

#### 4.4.3.3 RB6/SCK/SCL

Figure 4-9 shows the diagram for this pin. The RB6/ SCK/SCL<sup>(1)</sup> pin is configurable to function as one of the following:

- a general purpose I/O

- a SPI clock

- an l<sup>2</sup>C<sup>™</sup> clock

| Note 1: | SCK                            | and    | SCL   | are | available | on |  |  |  |

|---------|--------------------------------|--------|-------|-----|-----------|----|--|--|--|

|         | PIC16F677/PIC16F687/PIC16F689/ |        |       |     |           |    |  |  |  |

|         | PIC16                          | F690 ( | only. |     |           |    |  |  |  |

#### FIGURE 4-9:

### **BLOCK DIAGRAM OF RB6**

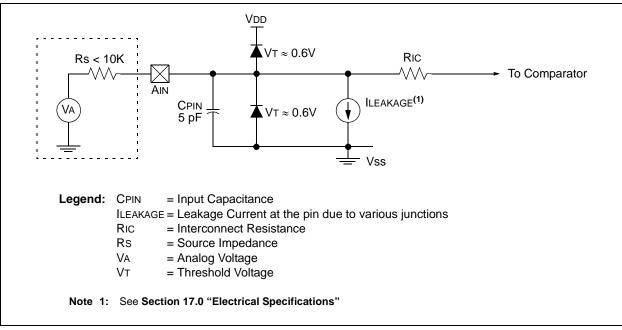

### 8.7 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 8-6. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 8-6: ANALOG INPUT MODEL

## 9.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

#### 9.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding port section for more information.

| Note: | Analog voltages on any pin that is defined  |

|-------|---------------------------------------------|

|       | as a digital input may cause the input buf- |

|       | fer to conduct excess current.              |

#### 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2 "ADC Operation"** for more information.

### 9.1.3 ADC VOLTAGE REFERENCE

The VCFG bit of the ADCON0 register provides control of the positive voltage reference. The positive voltage reference can be either VDD or an external voltage source. The negative voltage reference is always connected to the ground reference.

### 9.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11 TAD periods as shown in Figure 9-2.

For correct conversion, the appropriate TAD specification must be met. See A/D conversion requirements in **Section 17.0 "Electrical Specifications"** for more information. Table 9-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

# 12.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- Wake-up on Break reception

- 13-bit Break character transmit

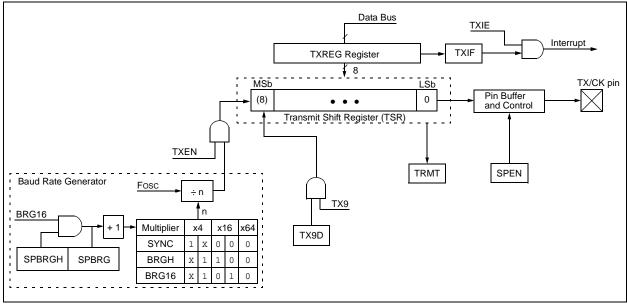

Block diagrams of the EUSART transmitter and receiver are shown in Figure 12-1 and Figure 12-2.

### FIGURE 12-1: EUSART TRANSMIT BLOCK DIAGRAM

#### 12.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 12-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 12.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the RX/DT I/O pin as an input. If the RX/DT pin is shared with an analog peripheral the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

| Note: | When the SPEN bit is set the TX/CK I/O         |

|-------|------------------------------------------------|

|       | pin is automatically configured as an          |

|       | output, regardless of the state of the         |

|       | corresponding TRIS bit and whether or          |

|       | not the EUSART transmitter is enabled.         |

|       | The PORT latch is disconnected from the        |

|       | output driver so it is not possible to use the |

|       | TX/CK pin as a general purpose output.         |

### 12.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 12.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | characters will be received until the overrun |  |  |  |  |  |

|       | condition is cleared. See Section 12.1.2.5    |  |  |  |  |  |

|       | "Receive Overrun Error" for more              |  |  |  |  |  |

|       | information on overrun errors.                |  |  |  |  |  |

#### 12.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

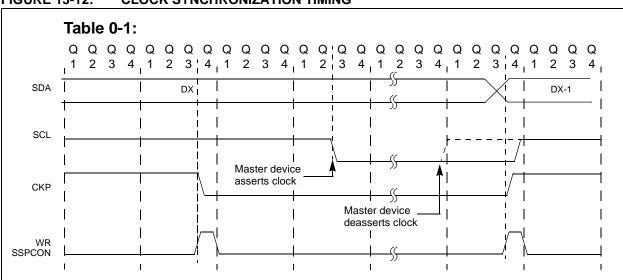

#### FIGURE 13-12: **CLOCK SYNCHRONIZATION TIMING**

| Addr                  | Name                  | Bit 7              | Bit 6              | Bit 5       | Bit 4        | Bit 3        | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|-----------------------|--------------------|--------------------|-------------|--------------|--------------|--------|--------|--------|----------------------|---------------------------------|

| 0Bh/8Bh/<br>10Bh/18Bh | INTCON                | GIE                | PEIE               | TOIE        | INTE         | RABIE        | TOIF   | INTF   | RABIF  | 0000 000x            | 0000 000x                       |

| 0Ch                   | PIR1                  | _                  | ADIF               | RCIF        | TXIF         | SSPIF        | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| 13h                   | SSPBUF                | Synchrono          | us Serial Po       | ort Receive | Buffer/Trans | smit Registe | r      |        |        | xxxx xxxx            | uuuu uuuu                       |

| 14h                   | SSPCON                | WCOL               | SSPOV              | SSPEN       | CKP          | SSPM3        | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| 86h                   | TRISB                 | TRISB7             | TRISB6             | TRISB5      | TRISB4       | _            | _      | _      | _      | 1111                 | 1111                            |

| 93h                   | SSPMSK <sup>(2)</sup> | MSK7               | MSK6               | MSK5        | MSK4         | MSK3         | MSK2   | MSK1   | MSK0   | 1111 1111            | 1111 1111                       |

| 94h                   | SSPSTAT               | SMP <sup>(3)</sup> | CKE <sup>(3)</sup> | D/A         | Р            | S            | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

| 8Ch                   | PIE1                  | _                  | ADIE               | RCIE        | TXIE         | SSPIE        | CCP1IE | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

- = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the SSP module. Legend:

Note 1: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

SSPMSK register (Register 13-3) can be accessed by reading or writing to SSPADD register with bits SSPM<3:0> = 1001. 2: See Registers 13-2 and 13-3 for more details.

3: Maintain these bits clear.

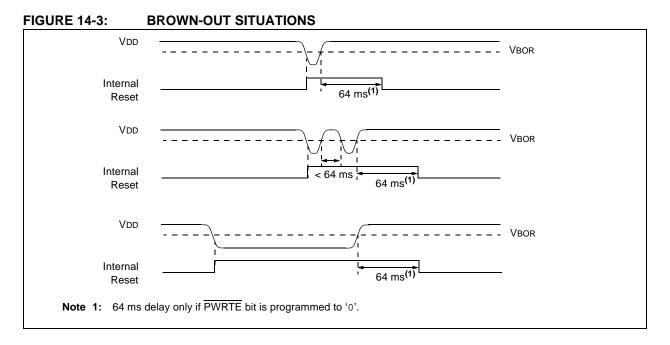

### 14.2.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of four BOR modes. Two modes have been added to allow software or hardware control of the BOR enable. When BOREN<1:0> = 01, the SBOREN bit (PCON<4>) enables/disables the BOR allowing it to be controlled in software. By selecting BOREN<1:0>, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. In this mode, the SBOREN bit is disabled. See Register 14-2 for the Configuration Word definition.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 17.0 "Electrical Specifications"**), the Brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not insured to occur if VDD falls below VBOR for less than parameter (TBOR).

On any Reset (Power-on, Brown-out Reset, Watchdog Timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 14-3). The Power-up Timer will now be invoked, if enabled and will keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

## 14.3 Interrupts

The PIC16F631/677/685/687/689/690 have multiple sources of interrupt:

- External Interrupt RA2/INT

- TMR0 Overflow Interrupt

- PORTA/PORTB Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt (except PIC16F631)

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt (PIC16F685/PIC16F690 only)

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- Enhanced CCP Interrupt (PIC16F685/PIC16F690 only)

- EUSART Receive and Transmit interrupts (PIC16F687/PIC16F689/PIC16F690 only)

The Interrupt Control register (INTCON) and Peripheral Interrupt Request Register 1 (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

A Global Interrupt Enable bit, GIE (INTCON<7>), enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON, PIE1 and PIE2 registers, respectively. GIE is cleared on Reset.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- PORTA/PORTB Change Interrupts

- TMR0 Overflow Interrupt

The peripheral interrupt flags are contained in the PIR1 and PIR2 registers. The corresponding interrupt enable bits are contained in PIE1 and PIE2 registers.

The following interrupt flags are contained in the PIR1 register:

- A/D Interrupt

- EUSART Receive and Transmit Interrupts

- Timer1 Overflow Interrupt

- Synchronous Serial Port (SSP) Interrupt

- Enhanced CCP1 Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

The following interrupt flags are contained in the PIR2 register:

- Fail-Safe Clock Monitor Interrupt

- 2 Comparator Interrupts

- EEPROM Data Write Interrupt

When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

For external interrupt events, such as the INT pin, PORTA/PORTB change interrupts, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 14-8). The latency is the same for one or 2-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, A/D, data EEPROM, EUSART, SSP or Enhanced CCP modules, refer to the respective peripheral section.

### 14.3.1 RA2/INT INTERRUPT

External interrupt on RA2/INT pin is edge-triggered; either rising if the INTEDG bit (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep, if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up (0004h). See Section 14.6 "Power-Down Mode (Sleep)" for details on Sleep and Figure 14-10 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL and CM2CON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

| Mnemonic,<br>Operands                  |         | Description                                   | Queles        |       | 14-Bit   | Opcode    | Status    | Natao        |         |

|----------------------------------------|---------|-----------------------------------------------|---------------|-------|----------|-----------|-----------|--------------|---------|

|                                        |         | Description                                   | Cycles        | MSb   |          |           | LSb       | Affected     | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |         |                                               |               |       |          |           |           |              |         |

| ADDWF                                  | f, d    | Add W and f                                   | 1             | 00    | 0111     | dfff      | ffff      | C, DC, Z     | 1, 2    |

| ANDWF                                  | f, d    | AND W with f                                  | 1             | 00    | 0101     | dfff      | ffff      | Z            | 1, 2    |

| CLRF                                   | f       | Clear f                                       | 1             | 00    | 0001     | lfff      | ffff      | Z            | 2       |

| CLRW                                   | _       | Clear W                                       | 1             | 00    | 0001     | 0xxx      | xxxx      | Z            |         |

| COMF                                   | f, d    | Complement f                                  | 1             | 00    | 1001     | dfff      | ffff      | Z            | 1, 2    |

| DECF                                   | f, d    | Decrement f                                   | 1             | 00    | 0011     | dfff      | ffff      | Z            | 1, 2    |

| DECFSZ                                 | f, d    | Decrement f, Skip if 0                        | 1 <b>(2)</b>  | 00    | 1011     | dfff      | ffff      |              | 1, 2, 3 |

| INCF                                   | f, d    | Increment f                                   | 1             | 00    | 1010     | dfff      | ffff      | Z            | 1, 2    |

| INCFSZ                                 | f, d    | Increment f, Skip if 0                        | 1 <b>(2)</b>  | 00    | 1111     | dfff      | ffff      |              | 1, 2, 3 |

| IORWF                                  | f, d    | Inclusive OR W with f                         | 1             | 00    | 0100     | dfff      | ffff      | Z            | 1, 2    |

| MOVF                                   | f, d    | Move f                                        | 1             | 00    | 1000     | dfff      | ffff      | Z            | 1, 2    |

| MOVWF                                  | f       | Move W to f                                   | 1             | 00    | 0000     | lfff      | ffff      |              |         |

| NOP                                    | _       | No Operation                                  | 1             | 00    | 0000     | 0xx0      | 0000      |              |         |

| RLF                                    | f, d    | Rotate Left f through Carry                   | 1             | 00    | 1101     | dfff      | ffff      | С            | 1, 2    |

| RRF                                    | f. d    | Rotate Right f through Carry                  | 1             | 00    | 1100     | dfff      | ffff      | С            | 1, 2    |

| SUBWF                                  | f, d    | Subtract W from f                             | 1             | 00    | 0010     | dfff      | ffff      | C, DC, Z     | 1, 2    |

| SWAPF                                  | f, d    | Swap nibbles in f                             | 1             | 00    | 1110     | dfff      | ffff      |              | 1, 2    |

| XORWF                                  | f, d    | Exclusive OR W with f                         | 1             | 00    | 0110     | dfff      | ffff      | Z            | 1, 2    |

|                                        |         | BIT-ORIENTED FILE                             | REGISTER OPER | RATIO | NS       |           |           |              |         |

| BCF                                    | f, b    | Bit Clear f                                   | 1             | 01    | 00bb     | bfff      | ffff      |              | 1, 2    |

| BSF                                    | f, b    | Bit Set f                                     | 1             | 01    | 01bb     | bfff      | ffff      |              | 1, 2    |

| BTFSC                                  | f, b    | Bit Test f, Skip if Clear                     | 1 <b>(2)</b>  | 01    | 10bb     | bfff      | ffff      |              | 3       |

| BTFSS                                  | f, b    | Bit Test f, Skip if Set                       | 1 (2)         | 01    | 11bb     | bfff      | ffff      |              | 3       |

|                                        |         | LITERAL AND CO                                | NTROL OPERAT  | IONS  |          |           |           |              |         |

| ADDLW                                  | k       | Add literal and W                             | 1             | 11    | 111x     | kkkk      | kkkk      | C, DC, Z     |         |

| ANDLW                                  | k       | AND literal with W                            | 1             | 11    | 1001     | kkkk      | kkkk      | Z            |         |

| CALL                                   | k       | Call Subroutine                               | 2             | 10    | 0kkk     | kkkk      | kkkk      |              |         |

| CLRWDT                                 | _       | Clear Watchdog Timer                          | 1             | 00    | 0000     | 0110      | 0100      | TO, PD       |         |

| GOTO                                   | k       | Go to address                                 | 2             | 10    | 1kkk     | kkkk      | kkkk      |              |         |

| IORLW                                  | k       | Inclusive OR literal with W                   | 1             | 11    | 1000     | kkkk      | kkkk      | Z            |         |

| MOVLW                                  | k       | Move literal to W                             | 1             | 11    | 00xx     | kkkk      | kkkk      |              |         |

| RETFIE                                 | _       | Return from interrupt                         | 2             | 00    | 0000     | 0000      | 1001      |              |         |

| RETLW                                  | k       | Return with literal in W                      | 2             | 11    | 01xx     | kkkk      | kkkk      |              |         |

| RETURN                                 | _       | Return from Subroutine                        | 2             | 00    | 0000     | 0000      | 1000      |              |         |

| SLEEP                                  | _       | Go into Standby mode                          | 1             | 00    | 0000     | 0110      | 0011      | TO, PD       |         |

| SUBLW                                  | k       | Subtract w from literal                       | 1             | 11    |          | kkkk      |           | C, DC, Z     |         |

| XORLW                                  | k       | Exclusive OR literal with W                   | 1             | 11    | 1010     |           | kkkk      | Ζ            |         |

| Note 1:                                | Whon on | I/O register is modified as a function of its |               |       | 1) tho y | عايره برو | od will b | o that value | proconí |

#### TABLE 15-2: PIC16F684 INSTRUCTION SET

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF GPIO, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### 17.4 DC Characteristics: PIC16F631/677/685/687/689/690-I (Industrial) PIC16F631/677/685/687/689/690-E (Extended)

|                   |      |                                            | Operating temperature -40 |       |          | tions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                                     |  |

|-------------------|------|--------------------------------------------|---------------------------|-------|----------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| Param<br>No. Sym. |      | Characteristic                             | Min.                      | Тур†  | Max.     | Units                                                                                                                        | Conditions                                                                                          |  |

|                   | VIL  | Input Low Voltage                          |                           |       |          |                                                                                                                              |                                                                                                     |  |

|                   |      | I/O Port:                                  |                           |       |          |                                                                                                                              |                                                                                                     |  |

| D030              |      | with TTL buffer                            | Vss                       | —     | 0.8      | V                                                                                                                            | $4.5V \leq V \text{DD} \leq 5.5V$                                                                   |  |

| D030A             |      |                                            | Vss                       | —     | 0.15 Vdd | V                                                                                                                            | $2.0V \leq V\text{DD} \leq 4.5V$                                                                    |  |

| D031              |      | with Schmitt Trigger buffer                | Vss                       | _     | 0.2 Vdd  | V                                                                                                                            | $2.0V \le VDD \le 5.5V$                                                                             |  |

| D032              |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>        | Vss                       | —     | 0.2 Vdd  | V                                                                                                                            |                                                                                                     |  |

| D033              |      | OSC1 (XT and LP modes)                     | Vss                       | _     | 0.3      | V                                                                                                                            |                                                                                                     |  |

| D033A             |      | OSC1 (HS mode)                             | Vss                       | —     | 0.3 Vdd  | V                                                                                                                            |                                                                                                     |  |

|                   | VIH  | Input High Voltage                         |                           |       |          |                                                                                                                              |                                                                                                     |  |

|                   |      | I/O Ports:                                 |                           | _     |          |                                                                                                                              |                                                                                                     |  |

| D040              |      | with TTL buffer                            | 2.0                       | _     | Vdd      | V                                                                                                                            | $4.5V \le VDD \le 5.5V$                                                                             |  |

| D040A             |      |                                            | 0.25 VDD + 0.8            | —     | Vdd      | V                                                                                                                            | $2.0V \le VDD \le 4.5V$                                                                             |  |

| D041              |      | with Schmitt Trigger buffer                | 0.8 Vdd                   | _     | Vdd      | V                                                                                                                            | $2.0V \le VDD \le 5.5V$                                                                             |  |

| D042              |      | MCLR                                       | 0.8 Vdd                   | _     | Vdd      | V                                                                                                                            |                                                                                                     |  |

| D043              |      | OSC1 (XT and LP modes)                     | 1.6                       | _     | Vdd      | V                                                                                                                            |                                                                                                     |  |

| D043A             |      | OSC1 (HS mode)                             | 0.7 Vdd                   | —     | Vdd      | V                                                                                                                            |                                                                                                     |  |

| D043B             |      | OSC1 (RC mode)                             | 0.9 Vdd                   | _     | Vdd      | V                                                                                                                            | (Note 1)                                                                                            |  |

|                   | lı∟  | Input Leakage Current <sup>(2)</sup>       |                           |       |          |                                                                                                                              |                                                                                                     |  |

| D060              |      | I/O ports                                  | _                         | ± 0.1 | ± 1      | μA                                                                                                                           | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                                       |  |

| D061              |      | MCLR <sup>(3)</sup>                        | —                         | ± 0.1 | ± 5      | μA                                                                                                                           | $VSS \leq VPIN \leq VDD$                                                                            |  |

| D063              |      | OSC1                                       | _                         | ± 0.1 | ± 5      | μA                                                                                                                           | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                  |  |

| D070*             | IPUR | PORTA Weak Pull-up Current                 | 50                        | 250   | 400      | μΑ                                                                                                                           | VDD = 5.0V, VPIN = VSS                                                                              |  |

|                   | Vol  | Output Low Voltage <sup>(5)</sup>          |                           |       |          |                                                                                                                              |                                                                                                     |  |

| D080              |      | I/O ports                                  | —                         | —     | 0.6      | V                                                                                                                            | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                                                     |  |

|                   | Voh  | Output High Voltage <sup>(5)</sup>         |                           |       |          |                                                                                                                              |                                                                                                     |  |

| D090              |      | I/O ports                                  | Vdd - 0.7                 | -     | _        | V                                                                                                                            | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                                                    |  |

| D100              | IULP | Ultra Low-Power Wake-up<br>Current         | _                         | 200   | _        | nA                                                                                                                           | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |  |

|                   |      | Capacitive Loading Specs on<br>Output Pins |                           |       |          |                                                                                                                              |                                                                                                     |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.2.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

| Param<br>No. | Symbol                | Characteristic                                        | Min.          | Тур† | Max. | Units | Conditions |  |

|--------------|-----------------------|-------------------------------------------------------|---------------|------|------|-------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input               | Тсү           |      | —    | ns    |            |  |

| 71*          | TscH                  | SCK input high time (Slave mode                       | Tcy + 20      |      | —    | ns    |            |  |

| 72*          | TscL                  | SCK input low time (Slave mode                        | TCY + 20      |      | —    | ns    |            |  |

| 73*          | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to S                     | 100           |      |      | ns    |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SO                     | 100           |      | —    | ns    |            |  |

| 75*          | TDOR                  | SDO data output rise time                             | 3.0-5.5V      | _    | 10   | 25    | ns         |  |

|              |                       |                                                       | 2.0-5.5V      | _    | 25   | 50    | ns         |  |

| 76*          | TDOF                  | SDO data output fall time                             |               | _    | 10   | 25    | ns         |  |

| 77*          | TssH2doZ              | SS↑ to SDO output high-impedance                      |               | 10   | _    | 50    | ns         |  |

| 78*          | TscR                  | SCK output rise time<br>(Master mode)                 | 3.0-5.5V      |      | 10   | 25    | ns         |  |

|              |                       |                                                       | 2.0-5.5V      | _    | 25   | 50    | ns         |  |

| 79*          | TscF                  | SCK output fall time (Master mo                       | /laster mode) |      | 10   | 25    | ns         |  |

| 80*          | TSCH2DOV,<br>TSCL2DOV | SDO data output valid after                           | 3.0-5.5V      |      | _    | 50    | ns         |  |

|              |                       | SCK edge                                              | 2.0-5.5V      | —    | _    | 145   | ns         |  |

| 81*          | TDOV2SCH,<br>TDOV2SCL | SDO data output setup to SCK e                        | Тсу           | _    | —    | ns    |            |  |

| 82*          | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ | _             | _    | 50   | ns    |            |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                   | 1.5Tcy + 40   |      | —    | ns    |            |  |

### TABLE 17-12: SPI MODE REQUIREMENTS

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

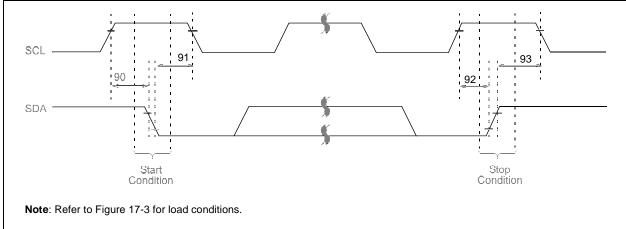

#### I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING FIGURE 17-16:

### TABLE 17-15: A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                      |            |      |         |       |                                                                     |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------------|------|---------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                       | Min.       | Тур† | Max.    | Units | Conditions                                                          |

| AD01                                                                                                                 | NR   | Resolution                                           | —          |      | 10 bits | bit   |                                                                     |

| AD02                                                                                                                 | EIL  | Integral Error                                       | —          |      | ±1      | LSb   | VREF = 5.12V                                                        |

| AD03                                                                                                                 | Edl  | Differential Error                                   | —          |      | ±1      | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |

| AD04                                                                                                                 | EOFF | Offset Error                                         | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |

| AD04A                                                                                                                |      |                                                      | —          | +1.5 | +3.0    | LSb   | (PIC16F677 only)                                                    |

| AD07                                                                                                                 | Egn  | Gain Error                                           | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |

| AD06<br>AD06A                                                                                                        | Vref | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.5 | _    | <br>Vdd | V     | Absolute minimum to ensure 1 LSb accuracy                           |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                     | Vss        | _    | Vref    | V     |                                                                     |

| AD08                                                                                                                 | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | _          | _    | 10      | kΩ    |                                                                     |

| AD09*                                                                                                                | IREF | VREF Input Current <sup>(3)</sup>                    | 10         | —    | 1000    | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |

|                                                                                                                      |      |                                                      | _          | _    | 50      | μA    | During A/D conversion cycle                                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- **2:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

- 4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

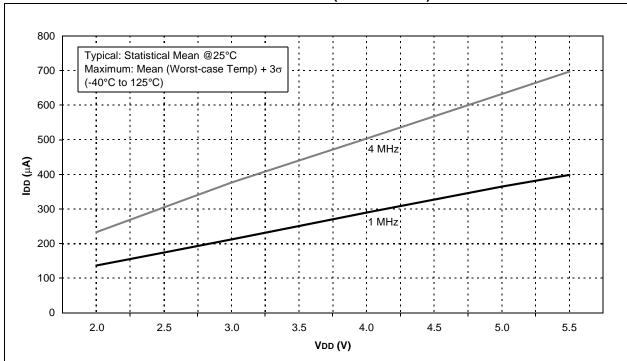

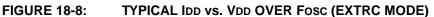

FIGURE 18-9: MAXIMUM IDD vs. VDD OVER Fosc (EXTRC MODE)

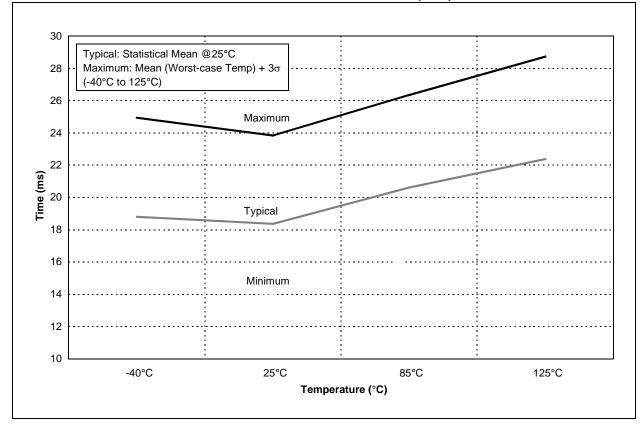

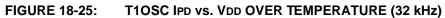

#### FIGURE 18-20: WDT PERIOD vs. TEMPERATURE OVER VDD (5.0V)

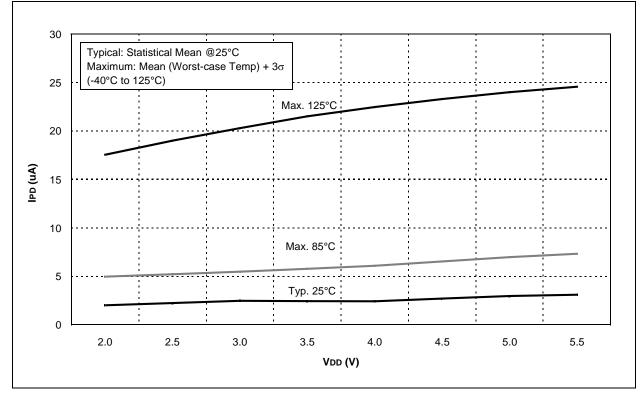

### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |      |      |  |  |

|--------------------------|------------------|----------|------|------|--|--|

| Dimensio                 | Dimension Limits |          |      | MAX  |  |  |

| Number of Pins           | Ν                | 20       |      |      |  |  |

| Pitch                    | е                | 0.65 BSC |      |      |  |  |

| Overall Height           | Α                | -        | -    | 2.00 |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75 | 1.85 |  |  |

| Standoff                 | A1               | 0.05     | -    | -    |  |  |

| Overall Width            | Е                | 7.40     | 7.80 | 8.20 |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30 | 5.60 |  |  |

| Overall Length           | D                | 6.90     | 7.20 | 7.50 |  |  |

| Foot Length              | L                | 0.55     | 0.75 | 0.95 |  |  |

| Footprint                | L1               | 1.25 REF |      |      |  |  |

| Lead Thickness           | с                | 0.09     | -    | 0.25 |  |  |

| Foot Angle               | φ                | 0°       | 4°   | 8°   |  |  |

| Lead Width               | b                | 0.22     | -    | 0.38 |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B

# THE MICROCHIP WEB SITE

Microchip provides online support via our web site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support