Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 18                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

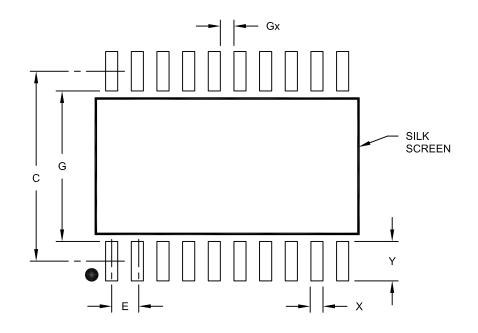

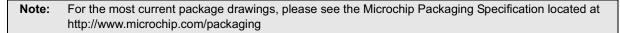

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f690t-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-8: PIC16F690 SPECIAL FUNCTION REGISTERS

|                    | File    |                       | File    |                     | File    |                       | File    |

|--------------------|---------|-----------------------|---------|---------------------|---------|-----------------------|---------|

|                    | Address |                       | Address |                     | Address |                       | Address |

| Indirect addr. (1) | 00h     | Indirect addr. (1)    | 80h     | Indirect addr. (1)  | 100h    | Indirect addr. (1)    | 180h    |

| TMR0               | 01h     | OPTION_REG            | 81h     | TMR0                | 101h    | OPTION_REG            | 181h    |

| PCL                | 02h     | PCL                   | 82h     | PCL                 | 102h    | PCL                   | 182h    |

| STATUS             | 03h     | STATUS                | 83h     | STATUS              | 103h    | STATUS                | 183h    |

| FSR                | 04h     | FSR                   | 84h     | FSR                 | 104h    | FSR                   | 184h    |

| PORTA              | 05h     | TRISA                 | 85h     | PORTA               | 105h    | TRISA                 | 185h    |

| PORTB              | 06h     | TRISB                 | 86h     | PORTB               | 106h    | TRISB                 | 186h    |

| PORTC              | 07h     | TRISC                 | 87h     | PORTC               | 107h    | TRISC                 | 187h    |

|                    | 08h     |                       | 88h     |                     | 108h    |                       | 188h    |

|                    | 09h     |                       | 89h     |                     | 109h    |                       | 189h    |

| PCLATH             | 0Ah     | PCLATH                | 8Ah     | PCLATH              | 10Ah    | PCLATH                | 18Ah    |

| INTCON             | 0Bh     | INTCON                | 8Bh     | INTCON              | 10Bh    | INTCON                | 18Bh    |

| PIR1               | 0Ch     | PIE1                  | 8Ch     | EEDAT               | 10Ch    | EECON1                | 18Ch    |

| PIR2               | 0Dh     | PIE2                  | 8Dh     | EEADR               | 10Dh    | EECON2 <sup>(1)</sup> | 18Dh    |

| TMR1L              | 0Eh     | PCON                  | 8Eh     | EEDATH              | 10Eh    |                       | 18Eh    |

| TMR1H              | 0Fh     | OSCCON                | 8Fh     | EEADRH              | 10Fh    |                       | 18Fh    |

| T1CON              | 10h     | OSCTUNE               | 90h     |                     | 110h    |                       | 190h    |

| TMR2               | 11h     |                       | 91h     |                     | 111h    |                       | 191h    |

| T2CON              | 12h     | PR2                   | 92h     |                     | 112h    |                       | 192h    |

| SSPBUF             | 13h     | SSPADD <sup>(2)</sup> | 93h     |                     | 113h    |                       | 193h    |

| SSPCON             | 14h     | SSPSTAT               | 94h     |                     | 114h    | -                     | 194h    |

| CCPR1L             | 15h     | WPUA                  | 95h     | WPUB                | 115h    | -                     | 195h    |

| CCPR1H             | 16h     | IOCA                  | 96h     | IOCB                | 116h    | -                     | 196h    |

| CCP1CON            | 17h     | WDTCON                | 97h     |                     | 117h    | -                     | 197h    |

| RCSTA              | 18h     | TXSTA                 | 98h     | VRCON               | 118h    | -                     | 198h    |

| TXREG              | 19h     | SPBRG                 | 99h     | CM1CON0             | 119h    |                       | 199h    |

| RCREG              | 1Ah     | SPBRGH                | 9Ah     | CM2CON0             | 11Ah    |                       | 19Ah    |

|                    | 1Bh     | BAUDCTL               | 9Bh     | CM2CON1             | 11Bh    |                       | 19Bh    |

| PWM1CON            | 1Ch     |                       | 9Ch     |                     | 11Ch    |                       | 19Ch    |

| ECCPAS             | 1Dh     |                       | 9Dh     |                     | 11Dh    | PSTRCON               | 19Dh    |

| ADRESH             | 1Eh     | ADRESL                | 9Eh     | ANSEL               | 11Eh    | SRCON                 | 19Eh    |

| ADCON0             | 1Fh     | ADCON1                | 9Fh     | ANSELH              | 11Fh    |                       | 19Fh    |

|                    | 20h     |                       | A0h     |                     | 120h    |                       | 1A0h    |

|                    |         |                       |         |                     |         |                       |         |

| General            |         | General               |         | General             |         |                       |         |

| General<br>Purpose |         | Purpose<br>Register   |         | Purpose<br>Register |         |                       |         |

| Register           |         | register              |         | register            |         |                       |         |

| -                  |         | 80 Bytes              |         | 80 Bytes            |         |                       |         |

| 96 Bytes           |         |                       | EFh     |                     | 16Fh    |                       |         |

|                    |         | accesses              | F0h     | accesses            | 170h    | accesses              | 1F0h    |

|                    | 7Fh     | 70h-7Fh               | FFh     | 70h-7Fh             | 17Fh    | 70h-7Fh               | 1FFh    |

| Bank 0             | 1       | Bank 1                | 1       | Bank 2              | I       | Bank 3                | I       |

Unimplemented data memory locations, read as '0'.

**Note 1:** Not a physical register.

2: Address 93h also accesses the SSP Mask (SSPMSK) register under certain conditions. See Registers 13-2 and 13-3 for more details.

| Addr | Name                     | Bit 7        | Bit 6                                         | Bit 5               | Bit 4               | Bit 3                | Bit 2                 | Bit 1                 | Bit 0                | Value on<br>POR, BOR | Page    |  |

|------|--------------------------|--------------|-----------------------------------------------|---------------------|---------------------|----------------------|-----------------------|-----------------------|----------------------|----------------------|---------|--|

| Bank | 0                        |              |                                               |                     |                     |                      |                       |                       |                      |                      |         |  |

| 00h  | INDF                     | Addressing   | this location                                 | uses conten         | ts of FSR to a      | address data         | memory (no            | t a physical r        | egister)             | xxxx xxxx            | 43,200  |  |

| 01h  | TMR0                     | Timer0 Mod   | mer0 Module Register xxxx xx                  |                     |                     |                      |                       |                       |                      |                      |         |  |

| 02h  | PCL                      | Program Co   | Program Counter's (PC) Least Significant Byte |                     |                     |                      |                       |                       |                      |                      |         |  |

| 03h  | STATUS                   | IRP          | RP1                                           | RP0                 | TO                  | PD                   | Z                     | DC                    | С                    | 0001 1xxx            | 35,200  |  |

| 04h  | FSR                      | Indirect Dat | a Memory A                                    | ddress Pointe       | ər                  |                      |                       |                       |                      | xxxx xxxx            | 43,200  |  |

| 05h  | PORTA <sup>(7)</sup>     | _            | _                                             | RA5                 | RA4                 | RA3                  | RA2                   | RA1                   | RA0                  | xx xxxx              | 57,200  |  |

| 06h  | PORTB <sup>(7)</sup>     | RB7          | RB6                                           | RB5                 | RB4                 | _                    | _                     | _                     | _                    | xxxx                 | 67,200  |  |

| 07h  | PORTC <sup>(7)</sup>     | RC7          | RC6                                           | RC5                 | RC4                 | RC3                  | RC2                   | RC1                   | RC0                  | xxxx xxxx            | 74,200  |  |

| 08h  | —                        | Unimpleme    | nted                                          |                     |                     |                      |                       |                       |                      | —                    | —       |  |

| 09h  | —                        | Unimpleme    | nted                                          |                     |                     |                      |                       |                       |                      | —                    | —       |  |

| 0Ah  | PCLATH                   |              | _                                             |                     | Write Buffer        | for upper 5 l        | oits of Progra        | am Counter            |                      | 0 0000               | 43,200  |  |

| 0Bh  | INTCON                   | GIE          | PEIE                                          | TOIE                | INTE                | RABIE                | TOIF                  | INTF                  | RABIF <sup>(1)</sup> | 0000 000x            | 37,200  |  |

| 0Ch  | PIR1                     | _            | ADIF <sup>(4)</sup>                           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF <sup>(5)</sup> | CCP1IF <sup>(3)</sup> | TMR2IF <sup>(3)</sup> | TMR1IF               | -000 0000            | 40,200  |  |

| 0Dh  | PIR2                     | OSFIF        | C2IF                                          | C1IF                | EEIF                | —                    | —                     | _                     | _                    | 0000                 | 41,200  |  |

| 0Eh  | TMR1L                    | Holding Re   | gister for the                                | Least Signifi       | cant Byte of        | the 16-bit TM        | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |  |

| 0Fh  | TMR1H                    | Holding Re   | gister for the                                | Most Signific       | cant Byte of t      | he 16-bit TM         | R1 Register           |                       |                      | xxxx xxxx            | 85,200  |  |

| 10h  | T1CON                    | T1GINV       | TMR1GE                                        | T1CKPS1             | T1CKPS0             | T1OSCEN              | T1SYNC                | TMR1CS                | TMR10N               | 0000 0000            | 87,200  |  |

| 11h  | TMR2 <sup>(3)</sup>      | Timer2 Mod   | ule Register                                  |                     |                     |                      |                       |                       |                      | 0000 0000            | 89,200  |  |

| 12h  | T2CON <sup>(3)</sup>     | -            | TOUTPS3                                       | TOUTPS2             | TOUTPS1             | TOUTPS0              | TMR2ON                | T2CKPS1               | T2CKPS0              | -000 0000            | 90,200  |  |

| 13h  | SSPBUF <sup>(5)</sup>    | Synchronou   | us Serial Port                                | Receive But         | ffer/Transmit       | Register             |                       |                       |                      | xxxx xxxx            | 178,200 |  |

| 14h  | SSPCON <sup>(5, 6)</sup> | WCOL         | SSPOV                                         | SSPEN               | CKP                 | SSPM3                | SSPM2                 | SSPM1                 | SSPM0                | 0000 0000            | 177,200 |  |

| 15h  | CCPR1L <sup>(3)</sup>    | Capture/Co   | mpare/PWM                                     | Register 1 (I       | LSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |  |

| 16h  | CCPR1H <sup>(3)</sup>    | Capture/Co   | mpare/PWM                                     | Register 1 (I       | MSB)                |                      |                       |                       |                      | xxxx xxxx            | 126,200 |  |

| 17h  | CCP1CON <sup>(3)</sup>   | P1M1         | P1M0                                          | DC1B1               | DC1B0               | CCP1M3               | CCP1M2                | CCP1M1                | CCP1M0               | 0000 0000            | 125,200 |  |

| 18h  | RCSTA <sup>(2)</sup>     | SPEN         | RX9                                           | SREN                | CREN                | ADDEN                | FERR                  | OERR                  | RX9D                 | 0000 000x            | 158,200 |  |

| 19h  | TXREG <sup>(2)</sup>     | EUSART T     | ransmit Data                                  | Register            |                     |                      |                       |                       |                      | 0000 0000            | 150     |  |

| 1Ah  | RCREG <sup>(2)</sup>     | EUSART R     | eceive Data                                   | Register            |                     |                      |                       |                       |                      | 0000 0000            | 155     |  |

| 1Bh  | _                        | Unimpleme    | nted                                          |                     |                     |                      |                       |                       |                      | _                    | _       |  |

| 1Ch  | PWM1CON <sup>(3)</sup>   | PRSEN        | PDC6                                          | PDC5                | PDC4                | PDC3                 | PDC2                  | PDC1                  | PDC0                 | 0000 0000            | 143,200 |  |

| 1Dh  | ECCPAS <sup>(3)</sup>    | ECCPASE      | ECCPAS2                                       | ECCPAS1             | ECCPAS0             | PSSAC1               | PSSAC0                | PSSBD1                | PSSBD0               | 0000 0000            | 140,200 |  |

| 1Eh  | ADRESH <sup>(4)</sup>    | A/D Result   | Register Hig                                  | h Byte              |                     |                      |                       |                       |                      | xxxx xxxx            | 113,200 |  |

| 1Fh  | ADCON0 <sup>(4)</sup>    | ADFM         | VCFG                                          | CHS3                | CHS2                | CHS1                 | CHS0                  | GO/DONE               | ADON                 | 0000 0000            | 111,200 |  |

| TABLE 2-1: | PIC16F631/677/685/687/689/690 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0 |

|------------|-------------------------------------------------------------------------|

|------------|-------------------------------------------------------------------------|

Legend:- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplementedNote1:MCLR and WDT Reset do not affect the previous value data latch. The RABIF bit will be cleared upon Reset but will set again if the

mismatch exists.

2: PIC16F687/PIC16F689/PIC16F690 only.

3: PIC16F685/PIC16F690 only.

4: PIC16F677/PIC16F685/PIC16F687/PIC16F689/PIC16F690 only.

5: PIC16F677/PIC16F687/PIC16F689/PIC16F690 only.

6: When SSPCON register bits SSPM<3:0> = 1001, any reads or writes to the SSPADD SFR address are accessed through the SSPMSK register. See Registers 13-2 and 13-3 for more detail.

7: Port pins with analog functions controlled by the ANSEL and ANSELH registers will read '0' immediately after a Reset even though the data latches are either undefined (POR) or unchanged (other Resets).

#### 4.2.5 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D Converter (ADC), refer to the appropriate section in this data sheet.

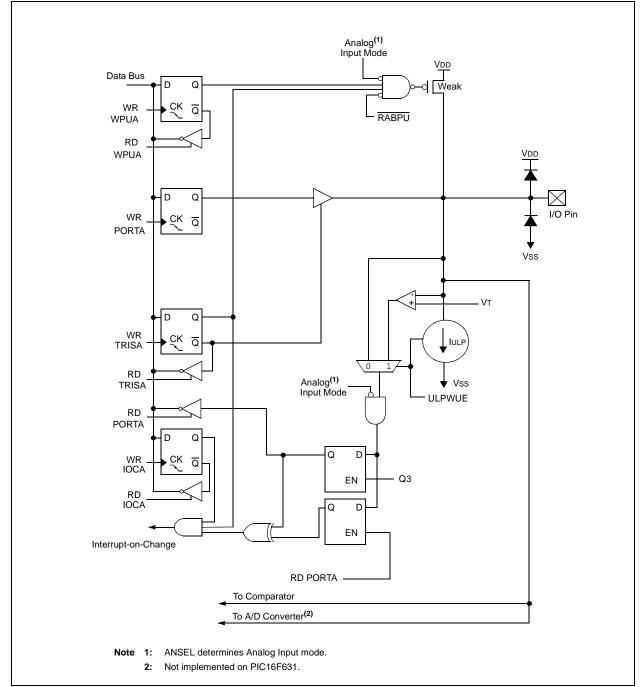

# 4.2.5.1 RA0/AN0/C1IN+/ICSPDAT/ULPWU

Figure 4-2 shows the diagram for this pin. The RA0/ AN0/C1IN+/ICSPDAT/ULPWU pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- an analog input to Comparator C1

- In-Circuit Serial Programming<sup>™</sup> data

- · an analog input for the Ultra Low-Power Wake-up

# FIGURE 4-1: BLOCK DIAGRAM OF RA0

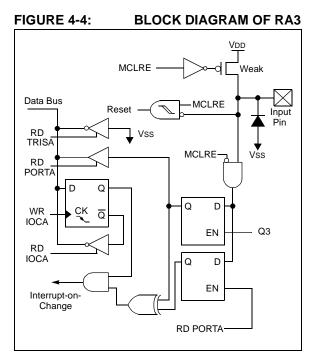

### 4.2.5.4 RA3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The RA3/ MCLR/VPP pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

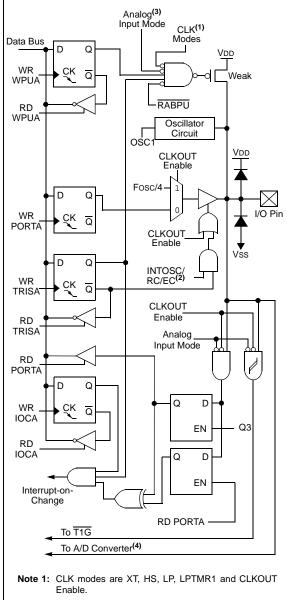

# 4.2.5.5 RA4/AN3/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The RA4/ AN3/T1G/OSC2/CLKOUT pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC (except PIC16F631)

- a Timer1 gate input

- a crystal/resonator connection

- · a clock output

- 2: With CLKOUT option.

- 3: ANSEL determines Analog Input mode.

- 4: Not implemented on PIC16F631.

# 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

### REGISTER 6-1: T1CON: TIMER 1 CONTROL REGISTER

| R/W-0                       | R/W-0                                 | R/W-0                                                                                                                                  | R/W-0           | R/W-0             | R/W-0          | R/W-0            | R/W-0      |  |  |  |  |  |  |

|-----------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|----------------|------------------|------------|--|--|--|--|--|--|

| T1GINV <sup>(1)</sup>       | ) TMR1GE <sup>(2)</sup>               | T1CKPS1                                                                                                                                | T1CKPS0         | T1OSCEN           | T1SYNC         | TMR1CS           | TMR10N     |  |  |  |  |  |  |

| bit 7                       |                                       |                                                                                                                                        |                 |                   |                |                  | bit 0      |  |  |  |  |  |  |

|                             |                                       |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

| Legend:                     |                                       |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

| R = Readab                  |                                       | W = Writable                                                                                                                           |                 | U = Unimplen      |                |                  |            |  |  |  |  |  |  |

| -n = Value a                | IT POR                                | '1' = Bit is set                                                                                                                       |                 | '0' = Bit is clea | ared           | x = Bit is unki  | nown       |  |  |  |  |  |  |

| bit 7                       | T1GINV: Time                          | er1 Gate Invert                                                                                                                        | bit(1)          |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | <b>T1GINV:</b> Timer1 Gate Invert bit <sup>(1)</sup><br>1 = Timer1 gate is active-high (Timer1 counts when Timer1 gate signal is high) |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                                         |                 |                   |                |                  |            |  |  |  |  |  |  |

| bit 6                       | TMR1GE: Tin                           | TMR1GE: Timer1 Gate Enable bit <sup>(2)</sup>                                                                                          |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | <u>If TMR1ON = 0:</u>                                                                                                                  |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | This bit is igno                      |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | <u>If TMR1ON = 1:</u><br>1 = Timer1 counting is controlled by the Timer1 Gate function                                                 |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | always countir                                                                                                                         |                 |                   |                |                  |            |  |  |  |  |  |  |

| bit 5-4                     | T1CKPS<1:0                            | >: Timer1 Inpu                                                                                                                         | t Clock Presca  | ale Select bits   |                |                  |            |  |  |  |  |  |  |

|                             | 11 = 1:8 Pres                         | 11 = 1:8 Prescale Value                                                                                                                |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 10 = 1:4 Prescale Value                                                                                                                |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                                                                     |                 |                   |                |                  |            |  |  |  |  |  |  |

| bit 3                       |                                       | TIOSCEN: LP Oscillator Enable Control bit                                                                                              |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | If INTOSC wit                         | If INTOSC without CLKOUT oscillator is active:                                                                                         |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 1 = LP oscillator is enabled for Timer1 clock                                                                                          |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 0 = LP oscillator is off                                                                                                               |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | Else:<br>This bit is ignored                                                                                                           |                 |                   |                |                  |            |  |  |  |  |  |  |

| bit 2                       | 0                                     |                                                                                                                                        | lock Input Syr  | hchronization Co  | ontrol bit     |                  |            |  |  |  |  |  |  |

|                             | <u>TMR1CS = 1</u> :                   |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 1 = Do not synchronize external clock input                                                                                            |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             |                                       | 0 = Synchronize external clock input                                                                                                   |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | <u>TMR1CS = 0:</u><br>This bit is ign |                                                                                                                                        | ses the interna | al clock          |                |                  |            |  |  |  |  |  |  |

| bit 1                       | 0                                     | his bit is ignored. Timer1 uses the internal clock <b>MR1CS:</b> Timer1 Clock Source Select bit                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | 1 = External o                        | clock from T1C                                                                                                                         | KI pin (on the  | rising edge)      |                |                  |            |  |  |  |  |  |  |

|                             | 0 = Internal cl                       |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

| bit 0 TMR10N: Timer1 On bit |                                       |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | 1 = Enables T                         |                                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | 0 = Stops Tim                         | ner1                                                                                                                                   |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | 1GINV bit inverts                     | -                                                                                                                                      |                 |                   |                |                  |            |  |  |  |  |  |  |

|                             | MR1GE bit must                        |                                                                                                                                        |                 | or C2OUT, as s    | elected by the | T1GSS bit of the | ne CM2CON1 |  |  |  |  |  |  |

| r                           | egister, as a Time                    | era gate source                                                                                                                        |                 |                   |                |                  |            |  |  |  |  |  |  |

# **REGISTER 10-4:** EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER<sup>(1)</sup> (CONTINUED)

Note 1: PIC16F685/PIC16F689/PIC16F690 only.

#### REGISTER 10-5: EECON1: EEPROM CONTROL REGISTER

| R/W-x                | U-0                                                                                                                          | U-0                                                                                                                           | U-0        | R/W-x              | R/W-0           | R/S-0            | R/S-0         |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|-----------------|------------------|---------------|--|--|--|--|

| EEPGD <sup>(1)</sup> |                                                                                                                              |                                                                                                                               | _          | WRERR              | WREN            | WR               | RD            |  |  |  |  |

| bit 7                |                                                                                                                              |                                                                                                                               |            |                    |                 |                  | bit C         |  |  |  |  |

|                      |                                                                                                                              |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

| Legend:              |                                                                                                                              |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

| S = Bit can or       | ly be set                                                                                                                    |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

| R = Readable         | bit                                                                                                                          | W = Writable b                                                                                                                | pit        | U = Unimpler       | nented bit, rea | d as '0'         |               |  |  |  |  |

| -n = Value at I      | POR                                                                                                                          | '1' = Bit is set                                                                                                              |            | '0' = Bit is cle   | ared            | x = Bit is unkr  | nown          |  |  |  |  |

|                      |                                                                                                                              |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

| bit 7                |                                                                                                                              | gram/Data EEPF                                                                                                                |            | bit <sup>(1)</sup> |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | s program mem                                                                                                                 | ory        |                    |                 |                  |               |  |  |  |  |

| bit 6-4              |                                                                                                                              | s data memory                                                                                                                 | ,          |                    |                 |                  |               |  |  |  |  |

|                      | -                                                                                                                            | ted: Read as '0                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

| bit 3                | <b>WRERR:</b> EEPROM Error Flag bit<br>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

|                      | normal operation or BOR Reset)                                                                                               |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | operation com                                                                                                                 |            |                    |                 |                  |               |  |  |  |  |

| bit 2                | WREN: EEPF                                                                                                                   | WREN: EEPROM Write Enable bit                                                                                                 |            |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | 1 = Allows write cycles                                                                                                       |            |                    |                 |                  |               |  |  |  |  |

|                      | 0 = Inhibits w                                                                                                               | rite to the data E                                                                                                            | EPROM      |                    |                 |                  |               |  |  |  |  |

| bit 1                | WR: Write Co                                                                                                                 | ontrol bit                                                                                                                    |            |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | EEPGD = 1:                                                                                                                    |            |                    |                 |                  |               |  |  |  |  |

|                      | This bit is ignored                                                                                                          |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | <u>EEPGD = 0</u> :<br>1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only |            |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | ot cleared, in so                                                                                                             |            | 5                  |                 | ·                |               |  |  |  |  |

|                      | 0 = Write cycle to the data EEPROM is complete                                                                               |                                                                                                                               |            |                    |                 |                  |               |  |  |  |  |

| bit 0                | RD: Read Co                                                                                                                  | ntrol bit                                                                                                                     |            |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              | •                                                                                                                             | (the RD is | cleared in har     | dware and car   | n only be set, r | ot cleared, i |  |  |  |  |

|                      | software.                                                                                                                    | )<br>initiate a memo                                                                                                          | ny read    |                    |                 |                  |               |  |  |  |  |

|                      |                                                                                                                              |                                                                                                                               | ny ieau    |                    |                 |                  |               |  |  |  |  |

Note 1: PIC16F685/PIC16F689/PIC16F690 only.

#### 10.1.4 READING THE FLASH PROGRAM MEMORY (PIC16F685/PIC16F689/ PIC16F690)

To read a program memory location, the user must write the Least and Most Significant address bits to the EEADR and EEADRH registers, set the EEPGD control bit of the EECON1 register, and then set control bit RD. Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDAT and EEDATH registers; therefore, it can be read as two bytes in the following instructions. EEDAT and EEDATH registers will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a 2-cycle instruction on the next instruction after the RD bit is set.

- If the WR bit is set when EEPGD = 1, it will be immediately reset to '0' and no operation will take place.

### EXAMPLE 10-3: FLASH PROGRAM READ

|                      | BANKSEL | EEADR            |     | ;                                                        |

|----------------------|---------|------------------|-----|----------------------------------------------------------|

|                      | MOVF    | MS_PROG_EE_ADDR, | W   | ;                                                        |

|                      | MOVWF   | EEADRH           |     | ;MS Byte of Program Address to read                      |

|                      | MOVF    | LS_PROG_EE_ADDR, | W   | ;                                                        |

|                      | MOVWF   | EEADR            |     | ;LS Byte of Program Address to read                      |

|                      | BANKSEL | EECON1           | ;   |                                                          |

|                      | BSF     | EECON1, EEPGD    |     | ;Point to PROGRAM memory                                 |

| <del>т</del> 8       | BSF     | EECON1, RD       |     | ;EE Read                                                 |

| Required<br>Sequence | NOP     |                  |     | ;First instruction after BSF EECON1,RD executes normally |

|                      | NOP     |                  |     | ;Any instructions here are ignored as program            |

| <b></b>              |         |                  |     | ;memory is read in second cycle after BSF EECON1,RD      |

| ;                    |         |                  |     |                                                          |

|                      | BANKSEL | EEDAT            | ;   |                                                          |

|                      | MOVF    | EEDAT, W         |     | ;W = LS Byte of Program Memory                           |

|                      | MOVWF   | LOWPMBYTE        |     | ;                                                        |

|                      | MOVF    | EEDATH, W        |     | ;W = MS Byte of Program EEDAT                            |

|                      | MOVWF   | HIGHPMBYTE       |     | ;                                                        |

|                      | BANKSEL | 0x00             | ;Ba | nk 0                                                     |

|                      |         |                  |     |                                                          |

### 12.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 12.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated If a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 12.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 12.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

| R/W-0         | R/W-0                                                                                                                                              | R/W-0                                                                                                     | R/W-0             | R/W-0            | R-0              | R-0             | R-x      |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------------|----------|--|--|--|--|--|--|

| SPEN          | RX9                                                                                                                                                | SREN                                                                                                      | CREN              | ADDEN            | FERR             | OERR            | RX9D     |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                    |                                                                                                           |                   |                  |                  |                 | bit 0    |  |  |  |  |  |  |

| <u> </u>      |                                                                                                                                                    |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

| Legend:       | • •                                                                                                                                                |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

| R = Readabl   |                                                                                                                                                    | W = Writable                                                                                              |                   | -                | mented bit, read |                 |          |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                | '1' = Bit is set                                                                                          |                   | '0' = Bit is cle | eared            | x = Bit is unkr | IOWN     |  |  |  |  |  |  |

| bit 7         | SPEN: Seria                                                                                                                                        | SPEN: Serial Port Enable bit                                                                              |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | ort enabled (cor<br>ort disabled (hel                                                                     | •                 | T and TX/CK p    | ins as serial po | rt pins)        |          |  |  |  |  |  |  |

| bit 6         | <b>RX9:</b> 9-bit R                                                                                                                                | eceive Enable b                                                                                           | oit               |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | 9-bit reception<br>8-bit reception                                                                        |                   |                  |                  |                 |          |  |  |  |  |  |  |

| bit 5         | SREN: Sing                                                                                                                                         | le Receive Enab                                                                                           | ole bit           |                  |                  |                 |          |  |  |  |  |  |  |

|               | SREN: Single Receive Enable bit<br>Asynchronous mode:                                                                                              |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | Don't care                                                                                                                                         | -                                                                                                         |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | •                                                                                                                                                  | Synchronous mode – Master:                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | 1 = Enables single receive                                                                                |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | <ul> <li>0 = Disables single receive</li> <li>This bit is cleared after reception is complete.</li> </ul> |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | Synchronous mode – Slave                                                                                                                           |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | Don't care                                                                                                                                         |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

| bit 4         | CREN: Cont                                                                                                                                         | CREN: Continuous Receive Enable bit                                                                       |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | Asynchronous mode:                                                                                                                                 |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | 1 = Enables                                                                                                                                        | 1 = Enables receiver                                                                                      |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | 0 = Disables receiver                                                                                     |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | -                                                                                                                                                  | Synchronous mode:                                                                                         |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | <ul> <li>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)</li> <li>0 = Disables continuous receive</li> </ul> |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

| bit 3         | ADDEN: Add                                                                                                                                         | ADDEN: Address Detect Enable bit                                                                          |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | Asynchronou                                                                                                                                        | us mode 9-bit (F                                                                                          | <u> X9 = 1)</u> : |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set            |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    | s address detec                                                                                           |                   | are received a   | nd ninth bit car | be used as pa   | rity bit |  |  |  |  |  |  |

|               |                                                                                                                                                    | us mode 8-bit (R                                                                                          | (X9 = 0):         |                  |                  |                 |          |  |  |  |  |  |  |

| <b>h</b> # 0  | Don't care                                                                                                                                         | in a Funan hit                                                                                            |                   |                  |                  |                 |          |  |  |  |  |  |  |

| bit 2         | FERR: Fram                                                                                                                                         | ing Error bit<br>gerror (can be u                                                                         | ndatad by ray     |                  | rogistor and rac |                 | huto)    |  |  |  |  |  |  |

|               | 1 = Framing<br>0 = No fram                                                                                                                         |                                                                                                           | poaled by rea     |                  | register and rec | eive next valid | byle)    |  |  |  |  |  |  |

| bit 1         | OERR: Overrun Error bit                                                                                                                            |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               | 1 = Overrun<br>0 = No over                                                                                                                         | n error (can be c<br>run error                                                                            | leared by clea    | aring bit CREN   | )                |                 |          |  |  |  |  |  |  |

| bit 0         | RX9D: Ninth                                                                                                                                        | bit of Received                                                                                           | Data              |                  |                  |                 |          |  |  |  |  |  |  |

|               | This can be address/data bit or a parity bit and must be calculated by user firmware.                                                              |                                                                                                           |                   |                  |                  |                 |          |  |  |  |  |  |  |

|               |                                                                                                                                                    |                                                                                                           | -                 |                  | -                |                 |          |  |  |  |  |  |  |

# REGISTER 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

| FIGURE 12-12                                    | : SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                 |

|-------------------------------------------------|-----------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)         | bit 0     bit 2     bit 3     bit 4     bit 5     bit 6     bit 7           |

| TX/CK pin<br>(SCKP = 1)<br>Write to<br>bit SREN |                                                                             |

| SREN bit                                        | ʻ0'                                                                         |

| RCIF bit<br>(Interrupt) ———<br>Read             |                                                                             |

| RXREG                                           | g diagram demonstrates Sync Master mode with bit SREN = 1 and bit BRGH = 0. |

### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7    | Bit 6                         | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------|-------------------------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF   | RCIDL                         |             | SCKP   | BRG16 |        | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE      | PEIE                          | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | _        | ADIE                          | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | _        | ADIF                          | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F | Receive Da                    | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN     | RX9                           | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG   | BRG7     | BRG6                          | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15    | BRG14                         | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7   | TRISB6                        | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART 1 | EUSART Transmit Data Register |             |        |       |        |        |        |                      | 0000 0000                       |

| TXSTA   | CSRC     | TX9                           | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

#### 12.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART. If the RX/DT or TX/CK pins are shared with an analog peripheral the analog I/O functions must be disabled by clearing the corresponding ANSEL bits.

#### 12.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 12.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- 4. After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 12.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 7. Start transmission by writing the Least Significant eight bits to the TXREG register.

| Name    | Bit 7                         | Bit 6      | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------|------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| BAUDCTL | ABDOVF                        | RCIDL      | —           | SCKP   | BRG16 | —      | WUE    | ABDEN  | 01-0 0-00            | 01-0 0-00                       |

| INTCON  | GIE                           | PEIE       | TOIE        | INTE   | RABIE | T0IF   | INTF   | RABIF  | x000 000x            | 0000 000x                       |

| PIE1    | —                             | ADIE       | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | -000 0000            | -000 0000                       |

| PIR1    | —                             | ADIF       | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | -000 0000            | -000 0000                       |

| RCREG   | EUSART F                      | Receive Da | ta Register |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA   | SPEN                          | RX9        | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| SPBRG   | BRG7                          | BRG6       | BRG5        | BRG4   | BRG3  | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| SPBRGH  | BRG15                         | BRG14      | BRG13       | BRG12  | BRG11 | BRG10  | BRG9   | BRG8   | 0000 0000            | 0000 0000                       |

| TRISB   | TRISB7                        | TRISB6     | TRISB5      | TRISB4 |       |        |        |        | 1111                 | 1111                            |

| TXREG   | EUSART Transmit Data Register |            |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                          | TX9        | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

|         |                               |            |             |        |       |        |        |        |                      |                                 |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

# 13.2 Operation

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSPBUF register. Then, the Buffer Full Status bit BF of the SSPSTAT register, and the interrupt flag bit SSPIF, are set. This double-buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer Full bit BF of the SSPSTAT register indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the SSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 13-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register. Additionally, the SSP Status register (SSPSTAT) indicates the various status conditions.

| EXAMPLE 13-1: | LOADING THE SSPBUF | (SSPSR) | REGISTER |

|---------------|--------------------|---------|----------|

|               |                    |         |          |

|      | BSF   | STATUS, RPO | ;Bank 1                                     |

|------|-------|-------------|---------------------------------------------|