Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm002-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                               |     |

|-------|-------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers         | 17  |

| 3.0   | CPU                                                                           |     |

| 4.0   | Memory Organization                                                           |     |

| 5.0   | Flash Program Memory                                                          | 83  |

| 6.0   | Resets                                                                        |     |

| 7.0   | Interrupt Controller                                                          |     |

| 8.0   | Direct Memory Access (DMA)                                                    | 109 |

| 9.0   | Oscillator Configuration                                                      | 123 |

| 10.0  | Power-Saving Features                                                         | 133 |

| 11.0  | I/O Ports                                                                     | 143 |

| 12.0  | Timer1                                                                        | 173 |

| 13.0  | Timer2/3 and Timer4/5                                                         | 175 |

| 14.0  | Deadman Timer (DMT)                                                           | 181 |

| 15.0  | Input Capture                                                                 | 189 |

| 16.0  | Output Compare                                                                | 193 |

| 17.0  | High-Speed PWM Module                                                         | 199 |

| 18.0  |                                                                               | 221 |

| 19.0  |                                                                               |     |

| 20.0  | Single-Edge Nibble Transmission (SENT)                                        | 237 |

| 21.0  | Universal Asynchronous Receiver Transmitter (UART)                            |     |

| 22.0  | Controller Area Network (CAN) Module (dsPIC33EVXXXGM10X Devices Only)         | 253 |

| 23.0  | Charge Time Measurement Unit (CTMU)                                           | 279 |

| 24.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                               |     |

| 25.0  | Op Amp/Comparator Module                                                      | 301 |

| 26.0  | Comparator Voltage Reference                                                  | 313 |

|       | Special Features                                                              |     |

| 28.0  | Instruction Set Summary                                                       | 327 |

| 29.0  |                                                                               |     |

|       |                                                                               |     |

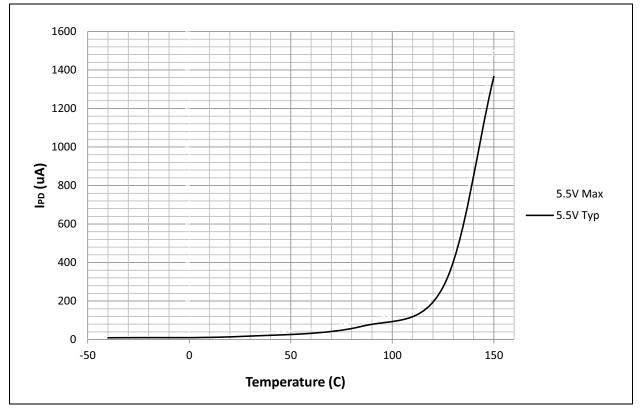

|       | High-Temperature Electrical Characteristics                                   |     |

|       | Characteristics for Industrial/Extended Temperature Devices (-40°C to +125°C) |     |

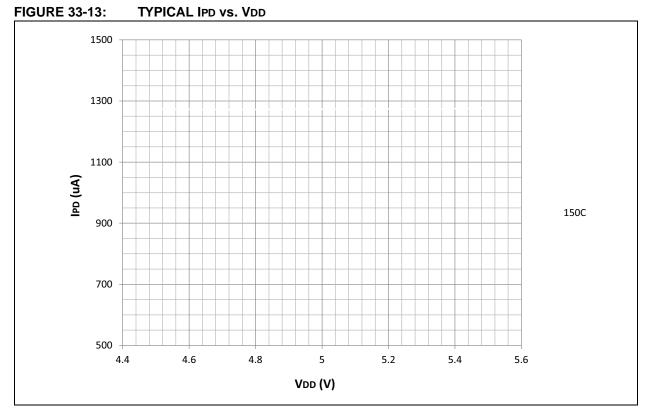

| 33.0  | Characteristics for High-Temperature Devices (+150°C)                         | 439 |

|       | Packaging Information                                                         |     |

|       | endix A: Revision History                                                     |     |

|       | Х                                                                             |     |

|       | Microchip Web Site                                                            |     |

|       | omer Change Notification Service                                              |     |

|       | omer Support                                                                  |     |

| Produ | luct Identification System                                                    | 497 |

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

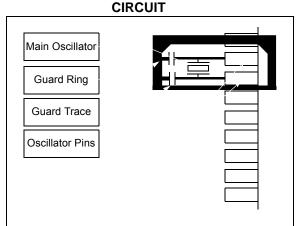

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

# FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

|             |       |        | -0.0.          |        |        |        | (0.0.1 |       | 0     |           |       |       |       | .0 (001 |       | ·)    |       |               |

|-------------|-------|--------|----------------|--------|--------|--------|--------|-------|-------|-----------|-------|-------|-------|---------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14         | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11SID  | 046C  | SID10  | SID9           | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | —     | EXIDE   | —     | EID17 | EID16 | xxxx          |

| C1RXF11EID  | 046E  |        |                |        |        |        |        |       | E     | EID<15:0> |       |       |       |         |       |       |       | xxxx          |

| C1RXF12SID  | 0470  | SID10  | SID9           | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF12EID  | 0472  |        |                |        |        |        |        |       | E     | EID<15:0> |       |       |       |         |       |       |       | xxxx          |

| C1RXF13SID  | 0474  | SID10  | SID9           | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF13EID  | 0476  |        |                |        |        |        |        |       | E     | EID<15:0> |       |       |       |         |       |       |       | xxxx          |

| C1RXF14SID  | 0478  | SID10  | SID9           | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | _     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF14EID  | 047A  |        |                |        |        |        |        |       | E     | ID<15:0>  |       |       |       |         |       |       |       | xxxx          |

| C1RXF15SID  | 047C  | SID10  | SID9           | SID8   | SID7   | SID6   | SID5   | SID4  | SID3  | SID2      | SID1  | SID0  | —     | EXIDE   | _     | EID17 | EID16 | xxxx          |

| C1RXF15EID  | 047E  |        | EID<15:0> xxxx |        |        |        |        |       |       |           |       |       |       |         |       |       |       |               |

|             |       |        |                |        |        |        |        |       |       |           |       |       |       |         |       |       |       |               |

#### TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-12: SENT1 RECEIVER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                                                          | Bit 13  | Bit 12 | Bit 11 | Bit 10    | Bit 9       | Bit 8      | Bit 7      | Bit 6     | Bit 5    | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0    | All<br>Resets |

|-------------|-------|--------|---------------------------------------------------------------------------------|---------|--------|--------|-----------|-------------|------------|------------|-----------|----------|-------|--------|---------|---------|----------|---------------|

| SENT1CON1   | 0500  | SNTEN  | —                                                                               | SNTSIDL | _      | RCVEN  | TXM       | TXPOL       | CRCEN      | PPP        | SPCEN     | _        | PS    | -      | NIBCNT2 | NIBCNT1 | NIBCNT0  | 0000          |

| SENT1CON2   | 0504  |        | TICKTIME<15:0> (Transmit modes) or SYNCMAX<15:0> (Receive mode) FFFF            |         |        |        |           |             |            |            |           |          |       |        |         |         |          |               |

| SENT1CON3   | 0508  |        |                                                                                 |         |        | FRAM   | ETIME<15: | :0> (Trans  | mit modes  | ) or SYNC  | MIN<15:0> | (Receive | mode) |        |         |         |          | FFFF          |

| SENT1STAT   | 050C  | _      | _                                                                               | _       | _      | _      | _         | _           | _          | PAUSE      | NIB2      | NIB1     | NIB0  | CRCERR | FRMERR  | RXIDLE  | SYNCTXEN | 0000          |

| SENT1SYNC   | 0510  |        |                                                                                 |         |        |        | Synchr    | onization - | Time Perio | d Register | (Transmit | mode)    |       |        |         |         |          | 0000          |

| SENT1DATL   | 0514  |        | DATA4<3:0> DATA5<3:0> DATA6<3:0> CRC<3:0> 0000                                  |         |        |        |           |             |            |            |           |          |       |        |         |         |          |               |

| SENT1DATH   | 0516  |        | STAT<3:0>         DATA1<3:0>         DATA2<3:0>         DATA3<3:0>         0000 |         |        |        |           |             |            |            |           |          | 0000  |        |         |         |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-13: SENT2 RECEIVER REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                                                          | Bit 13                                                               | Bit 12 | Bit 11 | Bit 10    | Bit 9      | Bit 8      | Bit 7     | Bit 6       | Bit 5     | Bit 4 | Bit 3  | Bit 2   | Bit 1   | Bit 0    | All<br>Resets |

|-------------|-------|--------|---------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|--------|-----------|------------|------------|-----------|-------------|-----------|-------|--------|---------|---------|----------|---------------|

| SENT2CON1   | 0520  | SNTEN  | —                                                                               | SNTSIDL                                                              |        | RCVEN  | TXM       | TXPOL      | CRCEN      | PPP       | SPCEN       | -         | PS    | —      | NIBCNT2 | NIBCNT1 | NIBCNT0  | 0000          |

| SENT2CON2   | 0524  |        |                                                                                 | TICKTIME<15:0> (Transmit modes) or SYNCMAX<15:0> (Receive mode) FFFF |        |        |           |            |            |           |             |           |       |        |         |         |          |               |

| SENT2CON3   | 0528  |        |                                                                                 |                                                                      |        | FRAM   | 1ETIME<15 | :0> (Trans | mit modes  | ) or SYNC | MIN<15:0>   | (Receive) | mode) |        |         |         |          | FFFF          |

| SENT2STAT   | 052C  | -      | _                                                                               | _                                                                    |        | —      |           | —          | _          | PAUSE     | NIB2        | NIB1      | NIB0  | CRCERR | FRMERR  | RXIDLE  | SYNCTXEN | 0000          |

| SENT2SYNC   | 0530  |        |                                                                                 |                                                                      |        |        | Synchi    | ronization | Time Peric | d Registe | r (Transmit | mode)     |       |        |         |         |          | 0000          |

| SENT2DATL   | 0534  |        | DATA4<3:0> DATA5<3:0> DATA6<3:0> CRC<3:0> 0000                                  |                                                                      |        |        |           |            |            |           |             |           |       |        |         |         |          |               |

| SENT2DATH   | 0536  |        | STAT<3:0>         DATA1<3:0>         DATA2<3:0>         DATA3<3:0>         0000 |                                                                      |        |        |           |            |            |           |             |           |       |        |         |         |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70005144E-page 49

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in the data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configure the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses an EDS or a PSV page.

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing. However, this does not include Register Offset Addressing.

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using the Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-43 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when an overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

# TABLE 4-43: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS AND PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

| 0/11        |                     |                | Before       |                        |                | After        |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page Description       |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last Page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>Page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page |

| O,<br>Read  | <b>or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>Page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last Page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  | r 1                 | DSRPAG = 0x001 | 1            | PSV Page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>Page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ WII ]             | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>Page  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

**Note 1:** The Register Indirect Addressing now addresses a location in the Base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

**3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

4: Pseudolinear Addressing is not supported for large offsets.

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

| U-0          | U-0                        | U-0             | U-0                        | U-0              | U-0              | U-0             | U-0   |

|--------------|----------------------------|-----------------|----------------------------|------------------|------------------|-----------------|-------|

| —            | —                          | —               | —                          |                  | —                | —               | —     |

| bit 15       |                            |                 |                            |                  |                  |                 | bit 8 |

|              |                            |                 |                            |                  |                  |                 |       |

| U-0          | U-0                        | U-0             | R/W-0                      | U-0              | U-0              | U-0             | U-0   |

| —            | —                          | —               | DMA0MD <sup>(1)</sup>      | —                | —                | —               | —     |

|              |                            |                 | DMA1MD <sup>(1)</sup>      | -                |                  |                 |       |

|              |                            |                 | DMA2MD <sup>(1)</sup>      | -                |                  |                 |       |

|              |                            |                 | DMA3MD <sup>(1)</sup>      |                  |                  |                 |       |

| bit 7        |                            |                 |                            |                  |                  |                 | bit 0 |

|              |                            |                 |                            |                  |                  |                 |       |

| Legend:      |                            |                 |                            |                  |                  |                 |       |

| R = Readal   |                            | W = Writable    |                            | •                | nented bit, read |                 |       |

| -n = Value a | at POR                     | '1' = Bit is se | et                         | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |

|              |                            |                 |                            |                  |                  |                 |       |

| bit 15-5     | Unimplement                |                 |                            |                  |                  |                 |       |

| bit 4        | DMA0MD: DN                 |                 |                            |                  |                  |                 |       |

|              | 1 = DMA0 mo<br>0 = DMA0 mo |                 |                            |                  |                  |                 |       |

|              | DMA1MD: DN                 |                 |                            |                  |                  |                 |       |

|              | 1 = DMA1 mo                |                 |                            |                  |                  |                 |       |

|              | 0 = DMA1 mo                |                 |                            |                  |                  |                 |       |

|              | DMA2MD: DN                 | A2 Module I     | Disable bit <sup>(1)</sup> |                  |                  |                 |       |

|              | 1 = DMA2 mo                |                 |                            |                  |                  |                 |       |

|              | 0 = DMA2 mo                | dule is enable  | ed                         |                  |                  |                 |       |

|              | DMA3MD: DN                 | MA3 Module E    | Disable bit <sup>(1)</sup> |                  |                  |                 |       |

|              | 1 = DMA3 mo<br>0 = DMA3 mo |                 |                            |                  |                  |                 |       |

| bit 3-0      | Unimplement                | ted: Read as    | <b>'</b> 0 <b>'</b>        |                  |                  |                 |       |

|              |                            |                 |                            |                  |                  |                 |       |

## REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

**Note 1:** This single bit enables and disables all four DMA channels.

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |  |  |

|------------------------------|---------------|----------|--------------------|--|--|

| External Interrupt 1         | INT1          | RPINR0   | INT1R<7:0>         |  |  |

| External Interrupt 2         | INT2          | RPINR1   | INT2R<7:0>         |  |  |

| Timer2 External Clock        | T2CK          | RPINR3   | T2CKR<7:0>         |  |  |

| Input Capture 1              | IC1           | RPINR7   | IC1R<7:0>          |  |  |

| Input Capture 2              | IC2           | RPINR7   | IC2R<7:0>          |  |  |

| Input Capture 3              | IC3           | RPINR8   | IC3R<7:0>          |  |  |

| Input Capture 4              | IC4           | RPINR8   | IC4R<7:0>          |  |  |

| Output Compare Fault A       | OCFA          | RPINR11  | OCFAR<7:0>         |  |  |

| PWM Fault 1                  | FLT1          | RPINR12  | FLT1R<7:0>         |  |  |

| PWM Fault 2                  | FLT2          | RPINR12  | FLT2R<7:0>         |  |  |

| UART1 Receive                | U1RX          | RPINR18  | U1RXR<7:0>         |  |  |

| UART2 Receive                | U2RX          | RPINR19  | U2RXR<7:0>         |  |  |

| SPI2 Data Input              | SDI2          | RPINR22  | SDI2R<7:0>         |  |  |

| SPI2 Clock Input             | SCK2          | RPINR22  | SCK2R<7:0>         |  |  |

| SPI2 Slave Select            | SS2           | RPINR23  | SS2R<7:0>          |  |  |

| CAN1 Receive                 | C1RX          | RPINR26  | C1RXR<7:0>         |  |  |

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |  |  |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<7:0>       |  |  |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<7:0>       |  |  |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<7:0>       |  |  |

| SENT1 Input                  | SENT1R        | RPINR44  | SENT1R<7:0>        |  |  |

| SENT2 Input                  | SENT2R        | RPINR45  | SENT2R<7:0>        |  |  |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

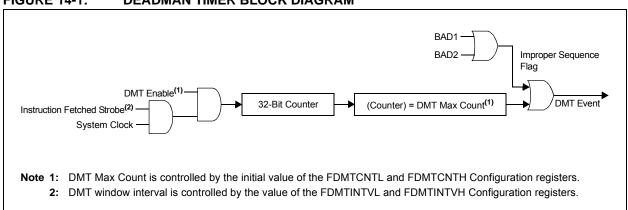

# 14.0 DEADMAN TIMER (DMT)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Deadman Timer (DMT)" (DS70005155) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT, which works on the system clock, is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs, until a count match occurs. Instructions are not fetched when the processor is in Sleep mode.

DMT can be enabled in the Configuration fuse or by software in the DMTCON register by setting the ON bit. The DMT consists of a 32-bit counter with a time-out count match value, as specified by the two 16-bit Configuration Fuse registers: FDMTCNTL and FDMTCNTH.

A DMT is typically used in mission-critical, and safetycritical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 14-1 shows a block diagram of the Deadman Timer module.

### FIGURE 14-1: DEADMAN TIMER BLOCK DIAGRAM

| U-0          | U-0           | U-0                                 | U-0              | U-0                                            | U-0               | U-0             | U-0            |

|--------------|---------------|-------------------------------------|------------------|------------------------------------------------|-------------------|-----------------|----------------|

|              | —             | _                                   | _                | _                                              |                   | _               |                |

| bit 15       |               |                                     |                  |                                                |                   |                 | bit 8          |

|              |               |                                     |                  |                                                |                   |                 |                |

| U-0          | R/W-0         | R/W-0                               | R/W-0            | R/W-0                                          | R/W-0             | R/W-0           | R/W-0          |

|              | PCIE          | SCIE                                | BOEN             | SDAHT                                          | SBCDE             | AHEN            | DHEN           |

| bit 7        |               |                                     |                  |                                                |                   |                 | bit 0          |

| Legend:      |               |                                     |                  |                                                |                   |                 |                |

| R = Readab   | le bit        | W = Writable I                      | oit              | U = Unimplem                                   | ented bit, read   | as '0'          |                |

| -n = Value a | t POR         | '1' = Bit is set                    |                  | '0' = Bit is clea                              |                   | x = Bit is unkn | own            |

|              |               |                                     |                  |                                                |                   |                 |                |

| bit 15-7     | Unimplement   | ted: Read as '(                     | )'               |                                                |                   |                 |                |

| bit 6        | PCIE: Stop Co | ondition Interru                    | pt Enable bit (I | <sup>2</sup> C Slave mode                      | only).            |                 |                |

|              |               | nterrupt on detection interrupts    |                  | condition                                      |                   |                 |                |

| bit 5        |               | •                                   |                  | <sup>2</sup> C Slave mode                      | only)             |                 |                |

| bit 5        |               |                                     | •                | or Restart condi                               | • /               |                 |                |

|              |               | ction interrupts                    |                  |                                                |                   |                 |                |

| bit 4        |               | · Overwrite Ena                     | •                | • •                                            |                   |                 |                |

|              |               |                                     |                  | nd an ACK is g                                 |                   | received addre  | ess/data byte, |

|              |               |                                     |                  | <pre>if the RBF bit =<br/>ed when I2CO\</pre>  |                   |                 |                |

| bit 3        |               | x Hold Time Se                      |                  |                                                |                   |                 |                |

|              |               |                                     |                  | after the falling                              |                   |                 |                |

|              |               |                                     |                  | after the falling                              | -                 |                 |                |

| bit 2        |               |                                     |                  | Enable bit (I <sup>2</sup> C<br>mpled low whei |                   | • /             | and state the  |

|              |               | • •                                 |                  | Detection mode                                 |                   |                 | •              |

|              | sequences.    | ·                                   |                  |                                                | ,                 | 0               |                |

|              |               | collision interr                    |                  |                                                |                   |                 |                |

| bit 1        |               | ss Hold Enable                      | •                |                                                |                   |                 |                |

|              |               |                                     | •                | x for a matchir                                | ng received ad    | dress byte; the | e SCLREL bit   |

|              | ·             | ,                                   |                  | he SCLx will be                                | held low          |                 |                |

| hit 0        |               | holding is disab<br>⊣old Enable bit |                  | do only)                                       |                   |                 |                |

| bit 0        |               |                                     |                  | or a received da                               | ata byte: slave l | hardware clears | s the SCLRFI   |

|              | bit (I2CxC    | CON1<12>) and                       |                  |                                                |                   |                 |                |

|              | 0 = Data hold | ling is disabled                    |                  |                                                |                   |                 |                |

## REGISTER 19-2: I2CxCON2: I2Cx CONTROL REGISTER 2

| R-0, HSC               | R-0, HSC      | R-0, HSC                           | U-0            | U-0                             | R/C-0, HSC                    | R-0, HSC          | R-0, HSC         |

|------------------------|---------------|------------------------------------|----------------|---------------------------------|-------------------------------|-------------------|------------------|

| ACKSTAT                | TRSTAT        | ACKTIM                             | —              | _                               | BCL                           | GCSTAT            | ADD10            |

| bit 15                 |               |                                    |                |                                 |                               |                   | bit 8            |

|                        |               |                                    |                |                                 |                               |                   |                  |

| R/C-0, HS              | R/C-0, HS     | R-0, HSC                           | R/C-0, HSC     | R/C-0, HSC                      | R-0, HSC                      | R-0, HSC          | R-0, HSC         |

| IWCOL                  | I2COV         | D_A                                | Р              | S                               | R_W                           | RBF               | TBF              |

| bit 7                  |               |                                    |                |                                 |                               |                   | bit 0            |

| 1                      |               | O Ola anali                        | I.a. Ia :4     | LICO Llaratur                   |                               | velete le it      |                  |

| Legend:<br>R = Readabl | a h:t         | C = Clearab                        |                |                                 | are Settable/Clear            |                   |                  |

|                        |               | W = Writabl                        |                | 0 = Unimpien                    | ented bit, read a             | HS = Hardware     | Cottoble bit     |

| -n = Value at          | PUR           | '1' = Bit is s                     | 51             |                                 | areu                          |                   | Settable bit     |

| bit 15                 | ACKSTAT: A    | Acknowledge                        | Status bit (up | dated in all Ma                 | ster and Slave m              | odes)             |                  |

|                        |               | edge was not                       |                |                                 |                               | ,                 |                  |

|                        | 0 = Acknowl   | edge was rec                       | eived from sla | ave                             |                               |                   |                  |

| bit 14                 |               |                                    |                | -                               | naster; applicable            | e to master trans | mit operation)   |

|                        |               | ransmit is in p<br>ransmit is not  |                | ts + ACK)                       |                               |                   |                  |

| bit 13                 | ACKTIM: Ad    | cknowledge T                       | ime Status bit | t (valid in I <sup>2</sup> C Sl | ave mode only)                |                   |                  |

|                        |               |                                    |                |                                 |                               | g edge of SCLx o  | lock             |

|                        |               | -                                  | -              | eared on 9 <sup>11</sup> risi   | ng edge of SCL>               | ( clock           |                  |

| bit 12-11              | -             | nted: Read a                       |                |                                 | 1 1 20                        |                   |                  |

| bit 10                 |               |                                    |                |                                 |                               | nodule is disable | d, 12CEN = 0)    |

|                        |               | ision has not l                    |                |                                 | or slave transm               | it operation      |                  |

| bit 9                  |               |                                    |                | ed after Stop de                | etection)                     |                   |                  |

|                        |               | call address v                     |                | ·                               | ,                             |                   |                  |

| bit 8                  |               |                                    |                | red after Stop o                | detection)                    |                   |                  |

| bit o                  |               | dress was m                        |                |                                 |                               |                   |                  |

|                        |               | dress was no                       |                |                                 |                               |                   |                  |

| bit 7                  | IWCOL: Wri    | te Collision D                     | etect bit      |                                 |                               |                   |                  |

|                        |               |                                    | the I2CxTRN    | I register failed               | because the I <sup>2</sup> C  | module is busy;   | must be cleared  |

|                        | In softw      | are<br>n has not occi              | irred          |                                 |                               |                   |                  |

| bit 6                  |               | Receive Ove                        |                | ł                               |                               |                   |                  |

| bit o                  |               |                                    | -              |                                 | s still holding the           | previous byte; 12 | 2COV is a "don't |

|                        | care" in      | Transmit mod                       | de, must be c  | leared in softwa                | -                             |                   |                  |

|                        |               | w has not occ                      |                |                                 |                               |                   |                  |

| bit 5                  |               |                                    |                | g as I <sup>2</sup> C slave)    |                               |                   |                  |

|                        |               | s that the last<br>s that the last |                |                                 | was an address                | i                 |                  |

| bit 4                  | P: I2Cx Stop  |                                    |                |                                 | -                             |                   |                  |

|                        | 1 = Indicates | s that a Stop b                    |                | letected last                   | d when the I <sup>2</sup> C r | nodule is disable | ed, I2CEN = 0.   |

# REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER

| R/W-0           | R/W-0                                                                                                                                                                       | R/W-0                                                                                    | U-0                                                                  | R/W-0, HC                           | R/W-0                                                                     | R-0                 | R-1             |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------|---------------------|-----------------|--|--|

| UTXISEL1        | UTXINV                                                                                                                                                                      | UTXISEL0                                                                                 |                                                                      | UTXBRK                              | UTXEN <sup>(1)</sup>                                                      | UTXBF               | TRMT            |  |  |

| bit 15          | it 15                                                                                                                                                                       |                                                                                          |                                                                      |                                     |                                                                           |                     |                 |  |  |

|                 |                                                                                                                                                                             |                                                                                          |                                                                      |                                     |                                                                           |                     |                 |  |  |

| R/W-0           | R/W-0                                                                                                                                                                       | R/W-0                                                                                    | R-1                                                                  | R-0                                 | R-0                                                                       | R/C-0               | R-0             |  |  |

| URXISEL1        | URXISEL0                                                                                                                                                                    | ADDEN                                                                                    | RIDLE                                                                | PERR                                | FERR                                                                      | OERR                | URXDA           |  |  |

| bit 7           |                                                                                                                                                                             |                                                                                          |                                                                      |                                     |                                                                           |                     | bit 0           |  |  |

| <del></del>     |                                                                                                                                                                             | 0 01 11                                                                                  |                                                                      |                                     |                                                                           |                     |                 |  |  |

| Legend:         | 1.11                                                                                                                                                                        | C = Clearable                                                                            |                                                                      |                                     | are Clearable bit                                                         |                     |                 |  |  |

| R = Readable    |                                                                                                                                                                             | W = Writable                                                                             | DIT                                                                  | •                                   | nented bit, read                                                          |                     |                 |  |  |

| -n = Value at F | POR                                                                                                                                                                         | '1' = Bit is set '0' = Bit is cleared x = Bit is unknow                                  |                                                                      |                                     |                                                                           |                     |                 |  |  |

| bit 15,13       | <ul> <li>11 = Reserve</li> <li>10 = Interrupt</li> <li>the trans</li> <li>01 = Interrupt</li> <li>operatio</li> <li>00 = Interrupt</li> </ul>                               | ed; do not use<br>t when a chara<br>smit buffer beco<br>t when the las<br>ns are complet | cter is transf<br>omes empty<br>it character<br>ed<br>cter is transf | is shifted out<br>Ferred to the Tra | election bits<br>ansmit Shift Reg<br>of the Transmit<br>ansmit Shift Reg  | t Shift Registe     | r; all transmit |  |  |

| bit 14          | $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle}}$ $0 = \text{UxTX Idle}$ $\frac{\text{If IREN = 1:}}{1 = \text{IrDA}^{\textcircled{B}} \text{ en}}$ $0 = \text{IrDA ence}$ | e state is '1'<br>coded UxTX Id<br>oded UxTX Idle                                        | le state is '1'<br>e state is '0'                                    |                                     |                                                                           |                     |                 |  |  |

| bit 12          | Unimplemen                                                                                                                                                                  | ted: Read as '                                                                           | )'                                                                   |                                     |                                                                           |                     |                 |  |  |

| bit 11          | 1 = Sends Sy<br>bit; cleare<br>0 = Sync Bre                                                                                                                                 | ed by hardware<br>ak transmissio                                                         | ext transmis<br>upon compl<br>n is disabled                          |                                     | followed by twe                                                           | elve '0' bits, foll | lowed by Stop   |  |  |

| bit 10          | UTXEN: UAR                                                                                                                                                                  | Tx Transmit Er                                                                           | nable bit <sup>(1)</sup>                                             |                                     |                                                                           |                     |                 |  |  |

|                 | 0 = Transmit                                                                                                                                                                |                                                                                          |                                                                      | ntrolled by UAR<br>ransmission is   | Tx<br>aborted and the                                                     | e buffer is rese    | t; UxTX pin is  |  |  |

| bit 9           | UTXBF: UAR                                                                                                                                                                  | Tx Transmit Bu                                                                           | iffer Full Stat                                                      | us bit (read-onl                    | y)                                                                        |                     |                 |  |  |

|                 | 1 = Transmit<br>0 = Transmit                                                                                                                                                |                                                                                          | ll, at least on                                                      | e more charact                      | er can be writte                                                          | n                   |                 |  |  |

| bit 8           | 1 = Transmit                                                                                                                                                                | Shift Register is                                                                        | s empty and t                                                        |                                     | ly)<br>s empty (the last<br>is in progress o                              |                     | as completed)   |  |  |

| bit 7-6         | 11 = Interrupt<br>10 = Interrupt<br>0x = Interrupt                                                                                                                          | t is set on UxRs<br>t is set on UxRs                                                     | SR transfer, i<br>SR transfer, r<br>ny character                     | naking the rece<br>is received and  | on bits<br>eive buffer full (i.<br>ive buffer 3/4 fu<br>d transferred fro | ll (i.e., has 3 da  | ita characters) |  |  |

### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

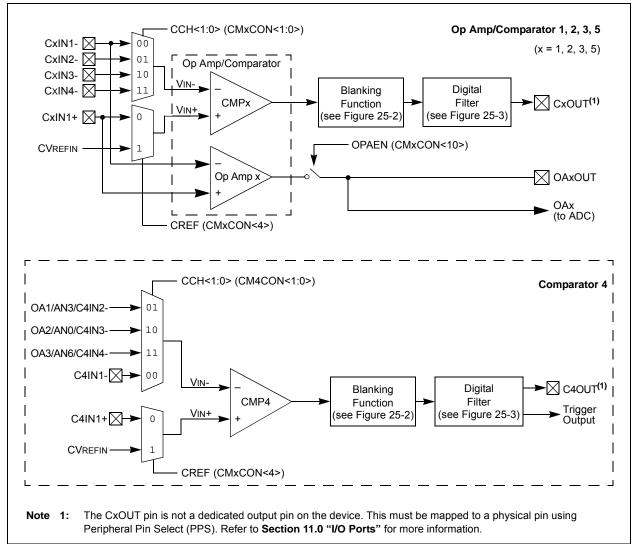

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "**Op Amp/Comparator**" (DS70000357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices contain up to five comparators that can be configured in various ways. CMP1, CMP2, CMP3 and CMP5 also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

The following options allow users to:

- Select the Edge for Trigger and Interrupt Generation

- Configure the Comparator Voltage Reference

- Configure Output Blanking and Masking

- Configure as a Comparator or Op Amp (CMP1, CMP2, CMP3 and CMP5 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM

| File Name | Address          | Device<br>Memory<br>Size<br>(Kbytes) | 23-16 | Bit 15                  | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9   | Bit 8     | Bit 7                   | Bit 6        | Bit 5   | Bit 4    | Bit 3  | Bit 2    | Bit 1   | Bit 0   |  |

|-----------|------------------|--------------------------------------|-------|-------------------------|--------|--------|-------------|--------|--------|---------|-----------|-------------------------|--------------|---------|----------|--------|----------|---------|---------|--|

| FSEC      | 005780           | 32                                   |       | AIVTDIS                 |        |        | _           | CSS2   |        |         |           | GSS1 G                  | GSS0         | GWRP    |          | BSEN   | BSS1     | BSSO    | BWRP    |  |

|           | 00AB80           | 64                                   |       |                         | _      |        |             |        | CSS1   | CSS0 (  | CWRP GSS1 |                         |              |         |          |        |          |         |         |  |

|           | 015780           | 128                                  | -     |                         |        | _      |             |        |        |         |           |                         | 6330         | GWRF    | —        |        |          |         |         |  |

|           | 02AB80           | 256                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| FBSLIM    | 005790           | 32                                   |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 00AB90           | 64                                   |       | _                       | _      | _      | BSLIM<12:0> |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 015790           | 128                                  |       |                         |        |        |             |        |        |         |           |                         | DOLIN        | 1412.05 |          |        |          |         |         |  |

|           | 02AB90           | 256                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| Reserved  | 005794           | 32                                   |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 00AB94           | 64                                   | -     | Reserved <sup>(1)</sup> | _      | _      |             |        | _      | _       |           | _                       | _            | _       | _        | _      | _        |         |         |  |

|           | 015794           | 128                                  |       | Reserveu                |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 02AB94           | 256                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| FOSCSEL   | 005798           | 32                                   | -     | _                       | _      | _      | _           | _      | _      | _       | — IESO    |                         | _            |         |          | — F    |          | ľ       |         |  |

|           | 00AB98           | 64                                   |       |                         |        |        |             |        |        |         |           | IESO                    |              | _       |          |        | FNOSC2   | FNOSC1  | FNOSC0  |  |

|           | 015798           | 128                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 02AB98           | 256                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| FOSC      | 00579C           | 32                                   |       |                         |        | _      | _           | -   -  |        | — P     | PLLKEN    | FCKSM1                  | FCKSM0 IOL1W |         | DL1WAY — | _      | OSCIOFNC | POSCMD1 | POSCMD0 |  |

|           | 00AB9C           | 64                                   |       | _                       | _      |        |             |        | -      |         |           |                         |              | IOL1WAY |          |        |          |         |         |  |

|           | 01579C           | 128                                  | -     |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| DAGE      | 02AB9C           | 256                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| FWDT      | 0057A0           | 32                                   | -     |                         |        |        |             | _      |        | WDTWIN1 | WDTWIN0   | WINDIS                  | FWDTEN1      | FWDTEN0 | WDTPRE   | WDTPS3 | WDTPS2   | WDTPS1  | WDTPS0  |  |

|           | 00ABA0<br>0157A0 | 64<br>128                            | —     | _                       | —      | -      | _           |        | -      |         |           |                         |              |         |          |        |          |         |         |  |

|           | 0157A0           | 256                                  | 1     |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| FPOR      | 02ABA0<br>0057A4 | 32                                   |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         | BOREN   |  |

| FPUR      | 0057A4           | 52<br>64                             | -     |                         | -      | -      |             |        |        |         |           |                         |              |         | -        |        |          |         |         |  |

|           | 00ABA4<br>0157A4 | 128                                  | —     | —                       |        |        | —           | —      | —      | —       | _         | —                       |              | -       |          | —      | —        | —       |         |  |

|           | 0157A4<br>02ABA4 | 256                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

| FICD      | 02ABA4           | 32                                   |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 0057A8           | 64                                   | 1     |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         |         |  |

|           | 00ABA8           | 128                                  |       | -                       | —      | —      | —           | -      | —      | —       | -         | Reserved <sup>(2)</sup> | —            | -       | —        | —      | -        | ICS1    | ICS0    |  |

|           | 0157A8           |                                      | 1     |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          |         | 1       |  |

|           | UZADAŎ           | 200                                  |       |                         |        |        |             |        |        |         |           |                         |              |         |          |        |          | 1       | 1       |  |

#### TABLE 27-1: CONFIGURATION WORD REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1:This bit is reserved and must be programmed as '0'.2:This bit is reserved and must be programmed as '1'.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax       | Description                                      | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------|--------------------------------------------------|---------------|----------------|--------------------------|

| 8                  | BSW                  | BSW.C   | Ws,Wb                 | Write C bit to Ws <wb></wb>                      | 1             | 1              | None                     |

|                    |                      | BSW.Z   | Ws,Wb                 | Write Z bit to Ws <wb></wb>                      | 1             | 1              | None                     |

| 9                  | BTG                  | BTG     | f,#bit4               | Bit Toggle f                                     | 1             | 1              | None                     |

|                    |                      | BTG     | Ws,#bit4              | Bit Toggle Ws                                    | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4               | Bit Test f, Skip if Clear                        | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC    | Ws,#bit4              | Bit Test Ws, Skip if Clear                       | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4               | Bit Test f, Skip if Set                          | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS    | Ws,#bit4              | Bit Test Ws, Skip if Set                         | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST    | f,#bit4               | Bit Test f                                       | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4              | Bit Test Ws to C                                 | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4              | Bit Test Ws to Z                                 | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                       | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                       | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4               | Bit Test then Set f                              | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4              | Bit Test Ws to C, then Set                       | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4              | Bit Test Ws to Z, then Set                       | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23                 | Call subroutine                                  | 2             | 4              | SFA                      |

|                    |                      | CALL    | Wn                    | Call indirect subroutine                         | 1             | 4              | SFA                      |

|                    |                      | CALL.L  | Wn                    | Call indirect subroutine (long address)          | 1             | 4              | SFA                      |

| 15                 | CLR                  | CLR     | f                     | f = 0x0000                                       | 1             | 1              | None                     |

|                    |                      | CLR     | WREG                  | WREG = 0x0000                                    | 1             | 1              | None                     |

|                    |                      | CLR     | Ws                    | Ws = 0x0000                                      | 1             | 1              | None                     |

|                    |                      | CLR     | Acc,Wx,Wxd,Wy,Wyd,AWB | Clear Accumulator                                | 1             | 1              | OA,OB,SA,<br>SB          |

| 16                 | CLRWDT               | CLRWDT  |                       | Clear Watchdog Timer                             | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM     | f                     | $f = \overline{f}$                               | 1             | 1              | N,Z                      |

|                    |                      | COM     | f,WREG                | WREG = f                                         | 1             | 1              | N,Z                      |

|                    |                      | COM     | Ws,Wd                 | $Wd = \overline{Ws}$                             | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f                     | Compare f with WREG                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit8              | Compare Wb with lit8                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                 | Compare Wb with Ws (Wb – Ws)                     | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0     | f                     | Compare f with 0x0000                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws                    | Compare Ws with 0x0000                           | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                     | Compare f with WREG, with Borrow                 | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit8              | Compare Wb with lit8, with Borrow                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                 | Compare Wb with Ws, with Borrow<br>(Wb – Ws – C) | 1             | 1              | C,DC,N,OV,Z              |