Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm002-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Timers/Output Compare/Input Capture**

- Nine General Purpose Timers:

- Five 16-bit and up to two 32-bit timers/counters; Timer3 can provide ADC trigger

- Four Output Compare modules Configurable as Timers/Counters

- Four Input Capture modules

# **Communication Interfaces**

- Two Enhanced Addressable Universal Asynchronous Receiver/Transmitter (UART) modules (6.25 Mbps):

- With support for LIN/J2602 bus and IrDA®

- High and low speed (SCI)

- Two SPI modules (15 Mbps):

- 25 Mbps data rate without using PPS

- One I<sup>2</sup>C module (up to 1 Mbaud) with SMBus Support

- Two SENT J2716 (Single-Edge Nibble Transmission-Transmit/Receive) module for Automotive Applications

- One CAN module:

- 32 buffers, 16 filters and three masks

# **Direct Memory Access (DMA)**

- 4-Channel DMA with User-Selectable Priority Arbitration

- UART, Serial Peripheral Interface (SPI), ADC, Input Capture, Output Compare and Controller Area Network (CAN)

#### Input/Output

- GPIO Registers to Support Selectable Slew Rate I/Os

- Peripheral Pin Select (PPS) to allow Function Remap

- Sink/Source: 8 mA or 12 mA, Pin-Specific for Standard VOH/VOL

- · Selectable Open-Drain, Pull-ups and Pull-Downs

- Change Notice Interrupts on All I/O Pins

### **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1: -40°C to +125°C) Compliant

- AEC-Q100 REVG (Grade 0: -40°C to +150°C) Compliant

- Class B Safety Library, IEC 60730

### **Class B Fault Handling Support**

- Backup FRC

- · Windowed WDT uses LPRC

- Windowed Deadman Timer (DMT) uses System Clock (System Windowed Watchdog Timer)

- H/W Clock Monitor Circuit

- Oscillator Frequency Monitoring through CTMU (OSCI, SYSCLK, FRC, BFRC, LPRC)

- Dedicated PWM Fault Pin

- Lockable Clock Configuration

### **Debugger Development Support**

- In-Circuit and In-Application Programming

- · Three Complex and Five Simple Breakpoints

- Trace and Run-Time Watch

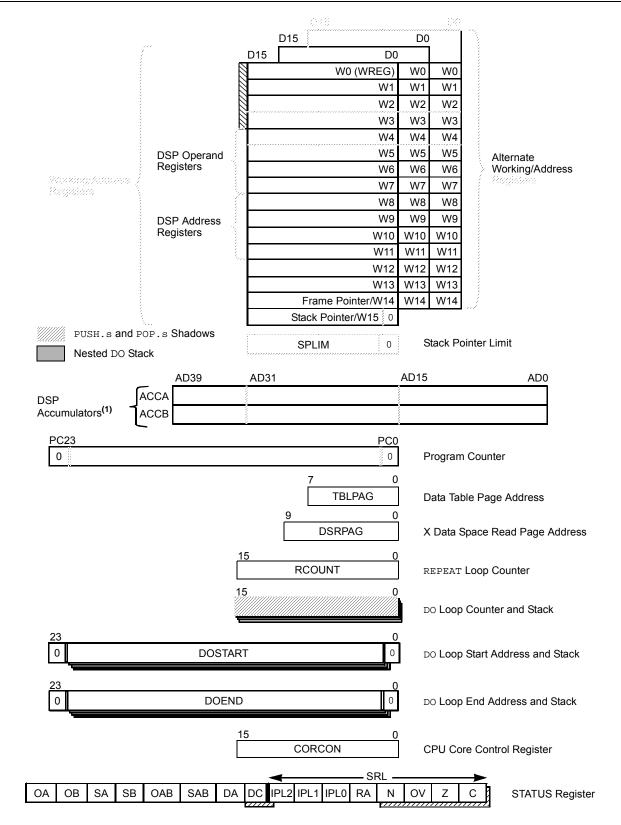

#### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EVXXXGM00X/ 10X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33EVXXXGM00X/10X family devices contain control registers for Modulo Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 1                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 2                        |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine STATUS Register                        |

| SPLIM                                             | Stack Pointer Limit Value Register                        |

| TBLPAG                                            | Table Memory Page Address Register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |

| RCOUNT                                            | REPEAT Loop Counter Register                              |

| DCOUNT                                            | DO Loop Count Register                                    |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: Memory-mapped W0 through W14 represents the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

# dsPIC33EVXXXGM00X/10X FAMILY

#### FIGURE 3-2: PROGRAMMER'S MODEL

**Note 1:** Memory areas are not shown to scale.

# TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7        | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|---------------|--------|--------|--------|--------|--------|--------|--------|-----------|--------------|---------|--------|--------|--------|--------|--------|--------|---------------|

|             | 0400-<br>041E |        |        |        |        |        |        |        | See defin | ition when W | /IN = x |        |        |        |        |        |        |               |

| C1BUFPNT1   | 0420          | F3BP3  | F3BP2  | F3BP1  | F3BP0  | F2BP3  | F2BP2  | F2BP1  | F2BP0     | F1BP3        | F1BP2   | F1BP1  | F1BP0  | F0BP3  | F0BP2  | F0BP1  | F0BP0  | 0000          |

| C1BUFPNT2   | 0422          | F7BP3  | F7BP2  | F7BP1  | F7BP0  | F6BP3  | F6BP2  | F6BP1  | F6BP0     | F5BP3        | F5BP2   | F5BP1  | F5BP0  | F4BP3  | F4BP2  | F4BP1  | F4BP0  | 0000          |

| C1BUFPNT3   | 0424          | F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0    | F9BP3        | F9BP2   | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  | 0000          |

| C1BUFPNT4   | 0426          | F15BP3 | F15BP2 | F15BP1 | F15BP0 | F14BP3 | F14BP2 | F14BP1 | F14BP0    | F13BP3       | F13BP2  | F13BP1 | F13BP0 | F12BP3 | F12BP2 | F12BP1 | F12BP0 | 0000          |

| C1RXM0SID   | 0430          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | —      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM0EID   | 0432          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXM1SID   | 0434          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM1EID   | 0436          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        | •      |        | xxxx          |

| C1RXM2SID   | 0438          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM2EID   | 043A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF0SID   | 0440          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF0EID   | 0442          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF1SID   | 0444          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF1EID   | 0446          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF2SID   | 0448          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | -      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF2EID   | 044A          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        |        |        | xxxx          |

| C1RXF3SID   | 044C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF3EID   | 044E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF4SID   | 0450          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF4EID   | 0452          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF5SID   | 0454          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF5EID   | 0456          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF6SID   | 0458          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF6EID   | 045A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF7SID   | 045C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF7EID   | 045E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF8SID   | 0460          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF8EID   | 0462          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF9SID   | 0464          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF9EID   | 0466          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF10SID  | 0468          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF10EID  | 046A          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        |        |        | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: NVM REGISTER MAP

|             |       |        |        |          |              |             |               |       | -     |           |       | -     |        |            |        |        | -      |               |

|-------------|-------|--------|--------|----------|--------------|-------------|---------------|-------|-------|-----------|-------|-------|--------|------------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12       | Bit 11      | Bit 10        | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| NVMCON      | 0728  | WR     | WREN   | WRERR    | NVMSIDL      | _           | _             | RPDF  | URERR | _         | —     | _     | _      | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        |        |          |              |             |               |       |       | NVMADR<   | 15:0> |       |        |            |        |        |        | 0000          |

| NVMADRU     | 072C  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMAD  | RU<23:16>  |        |        |        | 0000          |

| NVMKEY      | 072E  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMK   | EY<7:0>    |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |        |          |              |             |               |       | NVMSF | RCADR<15: | 1>    |       |        |            |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMSRC | ADR<23:16> |        |        |        | 0000          |

| Lonondy     |       |        |        | Desetual | an are chour | a in heaven | d a stress al |       |       |           |       |       |        |            |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | _      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0000          |

| PLLFBD      | 0746  | -      | —      |        | —      | _      | _       | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0000          |

| OSCTUN      | 0748  | -      | —      |        | —      | _      | _       | —       |         | _        | _        |        |           | TUN     | <5:0>   |         |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

### TABLE 4-21: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   | -      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     | _     | _     | —     | _     | _     | _     | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-39: PORTD REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD       | 0E3C  | —      | —      | _      |        |        | —      |       | TRISD8 | _     | TRISE | 0<6:5> |       |       | _     |       |       | 0160          |

| PORTD       | 0E3E  | _      | _      | _      |        |        | —      |       | RD8    | _     | RD<   | :6:5>  |       |       | _     | _     |       | xxxx          |

| LATD        | 0E40  | _      | _      | _      |        |        | —      |       | LATD8  | _     | LATD  | <6:5>  |       |       | _     | _     |       | xxxx          |

| ODCD        | 0E42  |        | _      | _      |        |        | —      |       | ODCD8  | —     | ODCE  | )<6:5> |       |       | _     |       |       | 0000          |

| CNEND       | 0E44  |        | _      | _      |        |        | —      |       | CNIED8 | —     | CNIED | 0<6:5> |       |       | _     |       |       | 0000          |

| CNPUD       | 0E46  |        | _      | _      |        |        | —      |       | CNPUD8 | —     | CNPU  | D<6:5> |       |       | _     |       |       | 0000          |

| CNPDD       | 0E48  | —      | _      | _      |        |        | -      |       | CNPDD8 |       | CNPDI | D<6:5> |       |       |       |       |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-40: PORTE REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE       | 0E50  |        | TRISE        | <15:12> |        | —      | —      |       | —     | —     | —     | _     | -     | -     | -     | —     |       | F000          |

| PORTE       | 0E52  |        | RE<1         | 5:12>   |        | _      | _      | _     | _     | —     | _     |       | _     | _     | _     | _     | _     | xxxx          |

| LATE        | 0E54  |        | LATE<15:12>  |         |        | _      | _      | _     | _     | —     | _     |       | _     | _     | _     | _     | _     | xxxx          |

| ODCE        | 0E56  |        | ODCE.        | <15:12> |        | _      | _      | _     | _     | —     | _     |       | _     | _     | _     | _     | _     | 0000          |

| CNENE       | 0E58  |        | CNIEE        | <15:12> |        | —      | —      |       | —     | —     | _     | _     |       |       |       | _     | _     | 0000          |

| CNPUE       | 0E5A  |        | CNPUE<15:12> |         | _      | _      | _      | _     | _     | _     |       | _     | _     | _     | _     | _     | 0000  |               |

| CNPDE       | 0E5C  |        | CNPDE        | <15:12> |        | —      | —      |       | —     | —     | _     | _     | _     | _     |       | _     | _     | 0000          |

| ANSELE      | 0E5E  |        | ANSE<        | <15:12> |        | _      | —      |       | _     | —     | _     | _     | -     | -     |       | _     | _     | F000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

The dsPIC33EVXXXGM00X/10X family devices can manage power consumption in the following four methods:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

#### 10.1 Clock Frequency and Clock Switching

The dsPIC33EVXXXGM00X/10X family devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). For more information on the process of changing a system clock during operation, as well as limitations to the process, see **Section 9.0 "Oscillator Configuration"**.

#### 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EVXXXGM00X/10X family devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the Assembler Include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

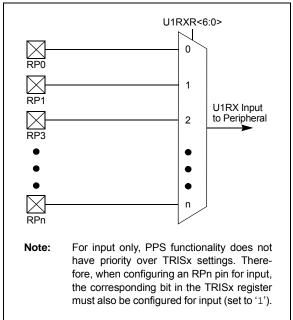

For example, Figure 11-2 shows the remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.5.4.1 Virtual Connections

dsPIC33EVXXXGM00X/10X family devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module").

These devices provide six virtual output pins (RPV0-RPV5) that correspond to the outputs of six peripheral pin output remapper blocks (RP176-RP181). The six virtual remapper outputs (RP176-RP181) are not connected to actual pins. The six virtual pins may be read by any of the input remappers as inputs, RP176-RP181. These virtual pins can be used to connect the internal peripherals, whose signals are of significant use to the other peripherals, but these output signals are not present on the device pin.

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<7:0> bits of the RPINR12 register to the value of 'b0000001', the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

| REGISTER 11-11: | <b>RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23</b> |

|-----------------|---------------------------------------------------------|

|-----------------|---------------------------------------------------------|

| U-0          | U-0        | U-0                                  | U-0   | U-0              | U-0             | U-0             | U-0   |

|--------------|------------|--------------------------------------|-------|------------------|-----------------|-----------------|-------|

| _            | —          | —                                    | _     | —                | —               | —               | _     |

| bit 15       |            |                                      |       |                  |                 |                 | bit 8 |

|              |            |                                      |       | =                |                 |                 |       |

| R/W-0        | R/W-0      | R/W-0                                | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|              |            |                                      | SS2I  | R<7:0>           |                 |                 |       |

| bit 7        |            |                                      |       |                  |                 |                 | bit C |

|              |            |                                      |       |                  |                 |                 |       |

| Legend:      |            |                                      |       |                  |                 |                 |       |

| R = Readab   | ole bit    | W = Writable                         | bit   | U = Unimpler     | mented bit, rea | <b>d as</b> '0' |       |

| -n = Value a | at POR     | '1' = Bit is se                      | t     | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|              |            |                                      |       |                  |                 |                 |       |

| bit 15-8     | Unimpleme  | nted: Read as                        | ʻ0'   |                  |                 |                 |       |

| bit 7-0      |            | : Assign SPI2 S<br>1-2 for input pin |       |                  | esponding RP    | n Pin bits      |       |

|              | 10110101 = | Input tied to R                      | PI181 |                  |                 |                 |       |

|              | •          |                                      |       |                  |                 |                 |       |

|              | •          |                                      |       |                  |                 |                 |       |

|              | -          | Input tied to C                      | MP1   |                  |                 |                 |       |

|              | 0000001 -  |                                      |       |                  |                 |                 |       |

00000000 = Input tied to Vss

#### REGISTER 11-12: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                |       | —                | —                | —               | —     |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | C1RX  | (R<7:0>          |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimpler     | nented bit, read | <b>d as</b> '0' |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-0  | <b>C1RXR&lt;7:0&gt;:</b> Assign CAN1 RX Input (C1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 10110101 = Input tied to RPI181                                                                                                         |

|          | •                                                                                                                                       |

|          | •                                                                                                                                       |

|          | •                                                                                                                                       |

|          | 00000001 = Input tied to CMP1<br>00000000 = Input tied to Vss                                                                           |

#### R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 **FLTMD FLTOUT FLTTRIEN** OCINV \_\_\_\_ \_\_\_\_ OC32 \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0, HS R/W-0 R/W-0 R/W-1 R/W-1 R/W-0 R/W-0 OCTRIG OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 TRIGSTAT SYNCSEL1 SYNCSEL0 bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLTMD: Fault Mode Select bit 1 = Fault mode is maintained until the Fault source is removed; the OCFLTA bit is cleared in software and a new PWM period starts 0 = Fault mode is maintained until the Fault source is removed and a new PWM period starts bit 14 FLTOUT: Fault Out bit 1 = PWM output is driven high on a Fault 0 = PWM output is driven low on a Fault bit 13 FLTTRIEN: Fault Output State Select bit 1 = OCx pin is tri-stated on a Fault condition 0 = OCx pin I/O state is defined by the FLTOUT bit on a Fault condition bit 12 **OCINV:** Output Compare x Invert bit 1 = OCx output is inverted 0 = OCx output is not inverted bit 11-9 Unimplemented: Read as '0' bit 8 OC32: Cascade Two OCx Modules Enable bit (32-bit operation) 1 = Cascade module operation is enabled 0 = Cascade module operation is disabled bit 7 OCTRIG: Output Compare x Trigger/Sync Select bit 1 = Triggers OCx from the source designated by the SYNCSELx bits 0 = Synchronizes OCx with the source designated by the SYNCSELx bits bit 6 TRIGSTAT: Timer Trigger Status bit 1 = Timer source has been triggered and is running 0 = Timer source has not been triggered and is being held clear bit 5 OCTRIS: Output Compare x Output Pin Direction Select bit 1 = Output Compare x is tri-stated 0 = Output Compare x module drives the OCx pin

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

**Note 1:** Do not use the OCx module as its own synchronization or trigger source.

2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

#### 17.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EVXXXGM00X/10X family devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FDEVOPT<0>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 17-1.

#### EXAMPLE 17-1: PWM1 WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

| ; FLT32 pin must be pulled low externally in order to clear and disable the fault<br>; Writing to FCLCON1 register requires unlock sequence |

|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                             |

| mov #0xabcd, w10 ; Load first unlock key to w10 register                                                                                    |

| mov #0x4321, wl1 ; Load second unlock key to wll register                                                                                   |

| mov #0x0000, w0 ; Load desired value of FCLCON1 register in w0                                                                              |

| mov w10, PWMKEY ; Write first unlock key to PWMKEY register                                                                                 |

| mov w11, PWMKEY ; Write second unlock key to PWMKEY register                                                                                |

| mov w0, FCLCON1 ; Write desired value to FCLCON1 register                                                                                   |

|                                                                                                                                             |

| ; Set PWM ownership and polarity using the IOCON1 register                                                                                  |

| ; Writing to IOCON1 register requires unlock sequence                                                                                       |

|                                                                                                                                             |

| mov #0xabcd, w10 ; Load first unlock key to w10 register                                                                                    |

| mov #0x4321, wl1 ; Load second unlock key to wll register                                                                                   |

| mov #0xF000, w0 ; Load desired value of IOCON1 register in w0                                                                               |

| mov w10, PWMKEY ; Write first unlock key to PWMKEY register                                                                                 |

| mov w11, PWMKEY ; Write second unlock key to PWMKEY register                                                                                |

| mov w0, IOCON1 ; Write desired value to IOCON1 register                                                                                     |

|                                                                                                                                             |

# dsPIC33EVXXXGM00X/10X FAMILY

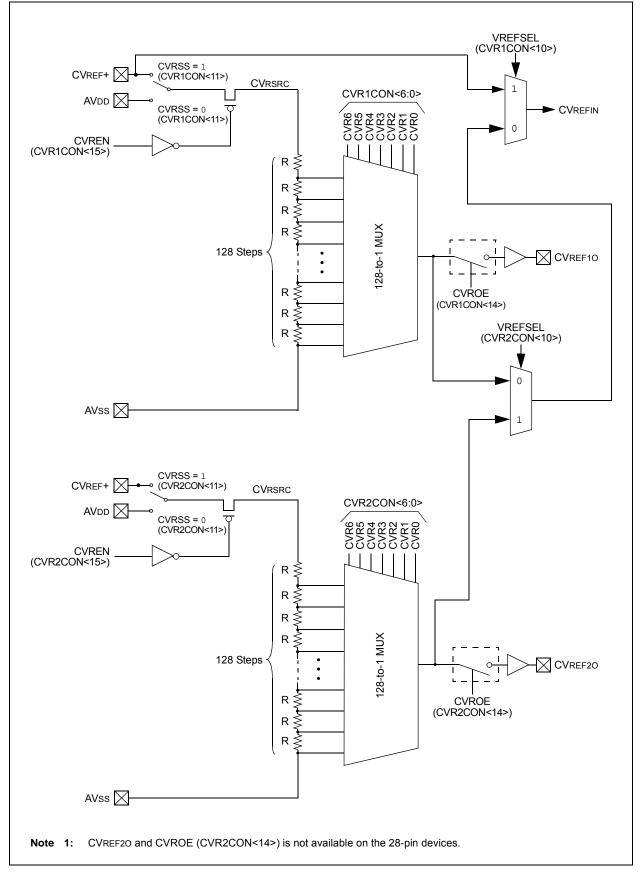

#### FIGURE 26-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

|  | TABLE 28-2: | <b>INSTRUCTION SET OVERVIEW</b> |

|--|-------------|---------------------------------|

|--|-------------|---------------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |                | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|----------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD             | Acc            | Add Accumulators                         | 1             | 1              | OA,OB,SA,<br>SB          |

|                    |                      | ADD             | f              | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD             | f,WREG         | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD             | #lit10,Wn      | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD             | Wb,Ws,Wd       | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD             | Wb,#lit5,Wd    | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD             | Wso,#Slit4,Acc | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,<br>SB          |

| 2                  | ADDC                 | ADDC            | f              | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC            | f,WREG         | WREG = $f + WREG + (C)$                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC            | #lit10,Wn      | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC            | Wb,Ws,Wd       | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC            | Wb,#lit5,Wd    | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND             | f              | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND             | f,WREG         | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND             | #lit10,Wn      | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND             | Wb,Ws,Wd       | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND             | Wb,#lit5,Wd    | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                  | ASR             | f              | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR             | f,WREG         | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR             | Ws,Wd          | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR             | Wb,Wns,Wnd     | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                      | ASR             | Wb,#lit5,Wnd   | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                 | BCLR            | f,#bit4        | Bit Clear f                              | 1             | 1              | None                     |

|                    |                      | BCLR            | Ws,#bit4       | Bit Clear Ws                             | 1             | 1              | None                     |

| 6                  | BRA                  | BRA             | C,Expr         | Branch if Carry                          | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | GE, Expr       | Branch if greater than or equal          | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | GEU, Expr      | Branch if unsigned greater than or equal | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | GT, Expr       | Branch if greater than                   | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | GTU, Expr      | Branch if unsigned greater than          | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | LE, Expr       | Branch if less than or equal             | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | LEU, Expr      | Branch if unsigned less than or equal    | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | LT, Expr       | Branch if less than                      | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | LTU, Expr      | Branch if unsigned less than             | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | N,Expr         | Branch if Negative                       | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | NC, Expr       | Branch if Not Carry                      | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | NN, Expr       | Branch if Not Negative                   | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | NOV, Expr      | Branch if Not Overflow                   | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | NZ,Expr        | Branch if Not Zero                       | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | OA, Expr       | Branch if Accumulator A overflow         | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | OB, Expr       | Branch if Accumulator B overflow         | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | OV,Expr        | Branch if Overflow                       | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | SA, Expr       | Branch if Accumulator A saturated        | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | SB, Expr       | Branch if Accumulator B saturated        | 1             | 1 (4)          | None                     |

|                    |                      | BRA             | Expr           | Branch Unconditionally                   | 1             | 4              | None                     |

|                    |                      | BRA             | Z,Expr         | Branch if Zero                           | 1             | 4 1 (4)        | None                     |

|                    |                      | BRA             | Wn             | Computed Branch                          | 1             | 4              | None                     |

| 7                  | BSET                 | BRA             | f,#bit4        | Bit Set f                                | 1             | 4              | None                     |

| •                  | דבטם                 | THORE           | L, #DICI       | Bit Set Ws                               |               |                | NONE                     |

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

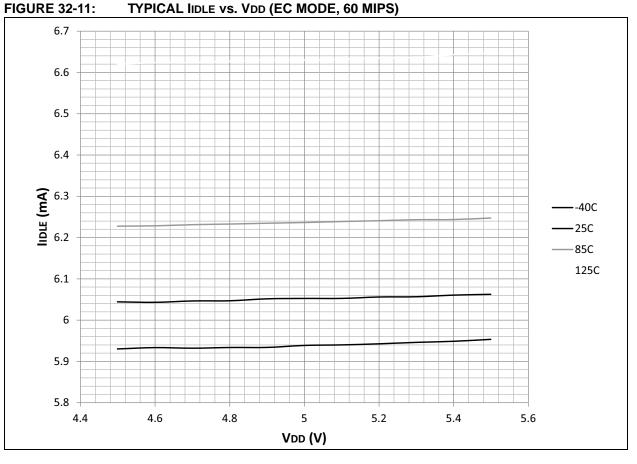

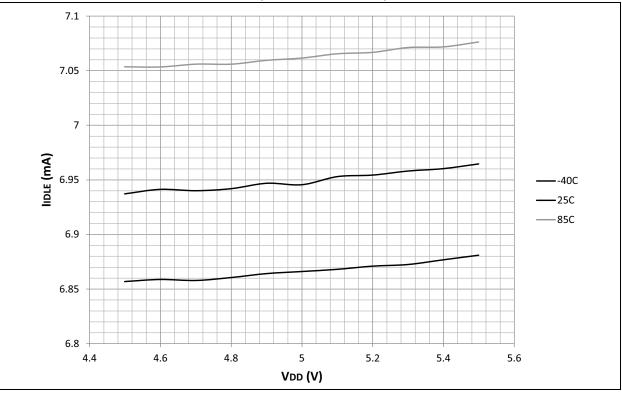

FIGURE 32-12: TYPICAL lidle vs. Vdd (EC MODE, 70 MIPS)

# dsPIC33EVXXXGM00X/10X FAMILY

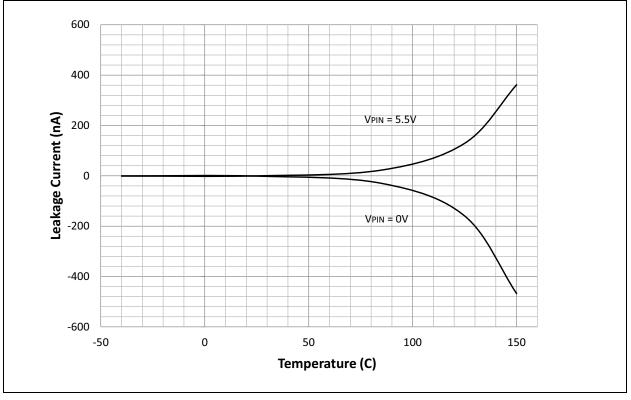

# 32.7 Leakage Current

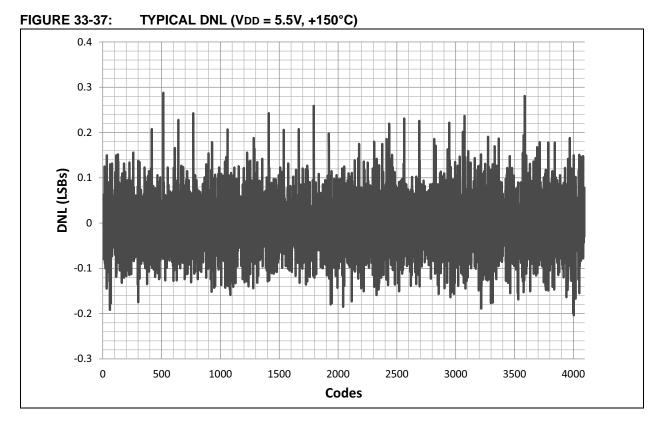

# 33.17 ADC DNL

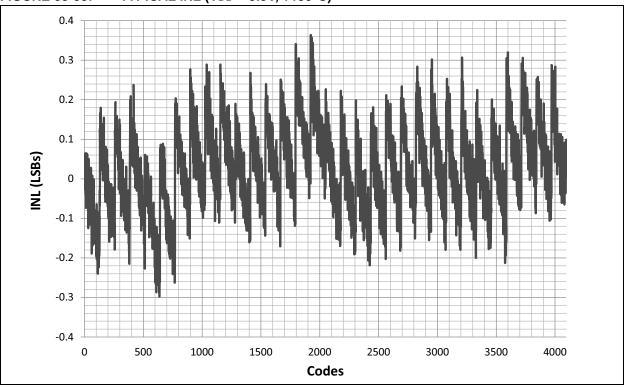

# 33.18 ADC INL

FIGURE 33-38: TYPICAL INL (VDD = 5.5V, +150°C)

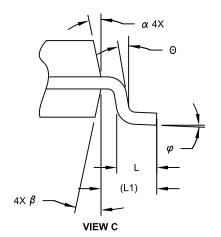

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | MILLIMETERS |           |      |  |

|--------------------------|--------|-------------|-----------|------|--|

| Dimension                | Limits | MIN         | NOM       | MAX  |  |

| Number of Pins           | N      |             | 28        |      |  |

| Pitch                    | е      | 1.27 BSC    |           |      |  |

| Overall Height           | A      | -           | -         | 2.65 |  |

| Molded Package Thickness | A2     | 2.05        | -         | -    |  |

| Standoff §               | A1     | 0.10        | -         | 0.30 |  |

| Overall Width            | E      |             | 10.30 BSC |      |  |

| Molded Package Width     | E1     | 7.50 BSC    |           |      |  |

| Overall Length           | D      | 17.90 BSC   |           |      |  |

| Chamfer (Optional)       | h      | 0.25        | -         | 0.75 |  |

| Foot Length              | L      | 0.40        | -         | 1.27 |  |

| Footprint                | L1     | 1.40 REF    |           |      |  |

| Lead Angle               | Θ      | 0°          | -         | -    |  |

| Foot Angle               | φ      | 0°          | -         | 8°   |  |

| Lead Thickness           | С      | 0.18        | -         | 0.33 |  |

| Lead Width               | b      | 0.31        | -         | 0.51 |  |

| Mold Draft Angle Top     | α      | 5°          | -         | 15°  |  |

| Mold Draft Angle Bottom  | β      | 5°          | -         | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2

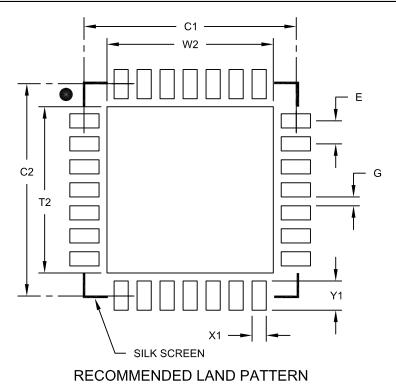

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

|                            | MILLIMETERS      |          |      |      |

|----------------------------|------------------|----------|------|------|

| Dimension                  | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch              | E                | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2               |          |      | 4.70 |

| Optional Center Pad Length | T2               |          |      | 4.70 |

| Contact Pad Spacing        | C1               |          | 6.00 |      |

| Contact Pad Spacing        | C2               |          | 6.00 |      |

| Contact Pad Width (X28)    | X1               |          |      | 0.40 |

| Contact Pad Length (X28)   | Y1               |          |      | 0.85 |

| Distance Between Pads      | G                | 0.25     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0975-5