Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\sim$  -

| Detalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm002-e-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name                        | Pin<br>Type | Buffer<br>Type | PPS        | Description                                                                                                                                                                        |

|---------------------------------|-------------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN19<br>AN24-AN32           | I           | Analog         | No         | Analog input channels.                                                                                                                                                             |

| AN48, AN49                      |             |                |            |                                                                                                                                                                                    |

| AN51-AN56                       |             |                |            |                                                                                                                                                                                    |

| CLKI                            | I           | ST/<br>CMOS    | No         | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO                            | 0           | _              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                            | I           | ST/<br>CMOS    | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| OSC2                            | I/O         | _              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| REFCLKO                         | 0           |                | Yes        | Reference clock output.                                                                                                                                                            |

| IC1-IC4                         | 1           | ST             | Yes        | Capture Inputs 1 to 4.                                                                                                                                                             |

| OCFA                            | 1           | ST             | Yes        | Compare Fault A input (for compare channels).                                                                                                                                      |

| OC1-OC4                         | 0           |                | Yes        | Compare Outputs 1 to 4.                                                                                                                                                            |

| INT0                            | I           | ST             | No         | External Interrupt 0.                                                                                                                                                              |

| INT1                            | I           | ST             | Yes        | External Interrupt 1.                                                                                                                                                              |

| INT2                            | I           | ST             | Yes        | External Interrupt 2.                                                                                                                                                              |

| RA0-RA4, RA7-RA12               | I/O         | ST             | Yes        | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                        | I/O         | ST             | Yes        | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                  | I/O         | ST             | Yes        | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5-RD6, RD8                    | I/O         | ST             | Yes        | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                       | I/O         | ST             | Yes        | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0-RF1                         | I/O         | ST             | No         | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                         | I/O         | ST             | Yes        | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                            | I           | ST             | No         | Timer1 external clock input.                                                                                                                                                       |

| T2CK                            | I           | ST             | Yes        | Timer2 external clock input.                                                                                                                                                       |

| T3CK                            | I           | ST             | No         | Timer3 external clock input.                                                                                                                                                       |

| T4CK<br>T5CK                    |             | ST<br>ST       | No         | Timer4 external clock input.                                                                                                                                                       |

| CTPLS                           |             | ST             | No         | Timer5 external clock input.                                                                                                                                                       |

| CTED1                           | 0           | ST             | No<br>No   | CTMU pulse output.<br>CTMU External Edge Input 1.                                                                                                                                  |

| CTED2                           | i           | ST             | No         | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                           |             | ST             | Yes        | UART1 Clear-to-Send.                                                                                                                                                               |

| U1RTS                           | Ö           | _              | Yes        | UART1 Ready-to-Send.                                                                                                                                                               |

| U1RX                            | I           | ST             | Yes        | UART1 receive.                                                                                                                                                                     |

| U1TX                            | 0           |                | Yes        | UART1 transmit.                                                                                                                                                                    |

| U2CTS                           | I           | ST             | Yes        | UART2 Clear-to-Send.                                                                                                                                                               |

| U2RTS                           | 0           |                | Yes        | UART2 Ready-to-Send.                                                                                                                                                               |

| U2RX<br>U2TX                    | 0           | ST             | Yes<br>Yes | UART2 receive.<br>UART2 transmit.                                                                                                                                                  |

| SCK1                            | 1/0         | ST             | No         | Synchronous serial clock input/output for SPI1.                                                                                                                                    |

| SDI1                            | 1           | ST             | No         | SPI1 data in.                                                                                                                                                                      |

| SDO1                            | Ó           | _              | No         | SPI1 data out.                                                                                                                                                                     |

| SS1                             | I/O         | ST             | No         | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                     |

| Legend: CMOS = CM<br>ST = Schmi |             |                |            |                                                                                                                                                                                    |

| PPS = Perip                     |             |                |            | TTL = TTL input buffer                                                                                                                                                             |

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EVXXXGM00X/10X family of 16-bit microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Note: The AVDD and AVSS pins must be connected, regardless of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu F$  (100 nF), 10V-20V is recommended. This capacitor should be a Low Equivalent Series Resistance (low-ESR), and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the Printed Circuit Board (PCB): The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing the PCB track inductance.

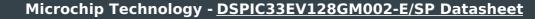

#### FIGURE 4-11: PAGED DATA MEMORY SPACE

DS70005144E-page 70

#### REGISTER 5-5: NVMSRCADRH: NVM DATA MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |  |  |

|------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| —                | _     | _     | _     | —     | _     | —     | —     |  |  |

| bit 15           |       |       |       |       |       |       | bit 8 |  |  |

|                  |       |       |       |       |       |       |       |  |  |

| R/W-x            | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |  |

| NVMSRCADR<23:16> |       |       |       |       |       |       |       |  |  |

| bit 7            |       |       |       |       |       |       | bit 0 |  |  |

|                  |       |       |       |       |       |       |       |  |  |

| Legend:          |       |       |       |       |       |       |       |  |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMSRCADRH<23:16>: Data Memory Upper Address bits

#### REGISTER 5-6: NVMSRCADRL: NVM DATA MEMORY LOWER ADDRESS REGISTER

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x                                   | R/W-x | R/W-x | R/W-x |

|-----------------------------------|-------|------------------|------------------------------------|-----------------------------------------|-------|-------|-------|

|                                   |       |                  | NVMSRC                             | CADR<15:8>                              |       |       |       |

| bit 15                            |       |                  |                                    |                                         |       |       | bit 8 |

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x                                   | R/W-x | R/W-x | r-0   |

|                                   |       | NV               | MSRCADR<                           | 7:1>                                    |       |       | —     |

| bit 7                             |       |                  |                                    |                                         |       |       | bit C |

| Legend:                           |       | r = Reserved     | bit                                |                                         |       |       |       |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                                         |       |       |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-1 NVMSRCADRL<15:1>: Data Memory Lower Address bits

bit 0 Reserved: Maintain as '0'

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EVXXXGM00X/10X CPU. The Interrupt Vector Table (IVT) provides 246 interrupt sources (unused sources are reserved for future use) that can be programmed with different priority levels.

The interrupt controller has the following features:

- · Interrupt Vector Table with up to 246 Vectors

- Alternate Interrupt Vector Table (AIVT)

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- · Fixed Interrupt Entry and Return Latencies

- Software can Generate any Peripheral Interrupt

- Alternate Interrupt Vector Table (AIVT) is available if Boot Security is Enabled and AIVTEN = 1

### 7.1 Interrupt Vector Table

The dsPIC33EVXXXGM00X/10X family IVT, shown in Figure 7-2, resides in program memory, starting at location, 00004h. The IVT contains seven nonmaskable trap vectors and up to 187 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Alternate Interrupt Vector Table

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-1, is available if the Boot Segment (BS) is defined, the AIVTEN bit is set in the INTCON2 register and if the AIVTDIS Configuration bit is set to '1'. The AIVT begins at the start of the last page of the Boot Segment.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel or channels are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA Channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU Interrupt after Half or Full Block Transfer Complete

- Byte or Word Transfers

- · Fixed Priority Channel Arbitration

- Manual (software) or Automatic (peripheral DMA requests) Transfer Initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer complete)

- DMA Request for Each Channel can be Selected from any Supported Interrupt Source

- Debug Support Features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |  |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--|

| External Interrupt 0 (INT0)      | 0000000                              | —                                                       | —                                                      |  |

| Input Capture 1 (IC1)            | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |  |

| Input Capture 2 (IC2)            | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |  |

| Input Capture 3 (IC3)            | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |  |

| Input Capture 4 (IC4)            | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |  |

| Output Compare 1 (OC1)           | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |  |

| Output Compare 2 (OC2)           | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |  |

| Output Compare 3 (OC3)           | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |  |

| Output Compare 4 (OC4)           | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |  |

| Timer2 (TMR2)                    | 00000111                             | _                                                       | _                                                      |  |

| Timer3 (TMR3)                    | 00001000                             | —                                                       | —                                                      |  |

| Timer4 (TMR4)                    | 00011011                             | —                                                       | _                                                      |  |

| Timer5 (TMR5)                    | 00011100                             | —                                                       | —                                                      |  |

| SPI1 Transfer Done               | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |  |

| SPI2 Transfer Done               | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |  |

| UART1 Receiver (UART1RX)         | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |  |

| UART1 Transmitter (UART1TX)      | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |  |

| UART2 Receiver (UART2RX)         | 00011110                             | 0x0236 (U2RXREG)                                        | —                                                      |  |

| UART2 Transmitter (UART2TX)      | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |  |

| RX Data Ready (CAN1)             | 00100010                             | 0x0440 (C1RXD)                                          | —                                                      |  |

| TX Data Request (CAN1)           | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |  |

| ADC1 Convert Done (ADC1)         | 00001101                             | 0x0300 (ADC1BUF0)                                       | _                                                      |  |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| R/W-0           | R/W-0                                                            | R/W-0                                                                                            | R/W-0                                        | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|-----------------|-----------------|-------|

| IC4R7           | IC4R6                                                            | IC4R5                                                                                            | IC4R4                                        | IC4R3            | IC4R2           | IC4R1           | IC4R0 |

| bit 15          |                                                                  |                                                                                                  |                                              | •                | ·               |                 | bit 8 |

|                 |                                                                  |                                                                                                  |                                              |                  |                 |                 |       |

| R/W-0           | R/W-0                                                            | R/W-0                                                                                            | R/W-0                                        | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| IC3R7           | IC3R6                                                            | IC3R5                                                                                            | IC3R4                                        | IC3R3            | IC3R2           | IC3R1           | IC3R0 |

| oit 7           |                                                                  |                                                                                                  |                                              |                  |                 |                 | bit C |

| Legend:         |                                                                  |                                                                                                  |                                              |                  |                 |                 |       |

| R = Readable    | bit                                                              | W = Writable                                                                                     | bit                                          | U = Unimpler     | mented bit, rea | <b>d as</b> '0' |       |

| -n = Value at F | POR                                                              | '1' = Bit is set                                                                                 |                                              | '0' = Bit is cle | eared           | x = Bit is unkı | nown  |

| bit 7-0         | •<br>•<br>00000001 =<br>00000000 =<br>IC3R<7:0>:<br>(see Table 1 | Input tied to Ri<br>Input tied to Ci<br>Input tied to Vi<br>Assign Input Ca<br>1-2 for input pin | MP1<br>SS<br>apture 3 (IC3)<br>selection nur |                  | onding RPn Pi   | n bits          |       |

|                 | •<br>•<br>00000001 =                                             | Input tied to R                                                                                  | MP1                                          |                  |                 |                 |       |

### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

NOTES:

### 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors, for both transmit and receive, appearing as corrupted data.

- 3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. For more information, refer to the SPI specifications in Section 30.0 "Electrical Characteristics".

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

## REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1 (CONTINUED)

| bit 7   | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled.</li> </ul>                                                                                                                                                                                                                              |

| bit 6   | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                                                                                                                                                                                                      |

|         | In I <sup>2</sup> C Slave mode only, used in conjunction with the SCLREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                                                                                                                                                                                            |

| bit 5   | ACKDT: Acknowledge Data bit                                                                                                                                                                                                                                                                                                                                                                               |

|         | In I <sup>2</sup> C Master mode, during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.<br>In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.<br>1 = NACK is sent<br>0 = ACK is sent |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                                                                                                                                                                                                |

| bit 3   | <b>RCEN:</b> Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C, automatically cleared by hardware at the end of 8-bit receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                                                                                                                                                                 |

| bit 2   | PEN: Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins</li> <li>0 = Stop condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                                |

| bit 1   | RSEN: Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiates Restart condition on SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                          |

| bit 0   | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                              |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                                                                                                                                                                                          |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

# dsPIC33EVXXXGM00X/10X FAMILY

| R/W-x        | R/W-x                                            | R/W-x                   | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x              |  |  |  |  |

|--------------|--------------------------------------------------|-------------------------|---------------|------------------|------------------|-----------------|--------------------|--|--|--|--|

| EID5         | EID4                                             | EID3                    | EID2          | EID1             | EID0             | RTR             | RB1                |  |  |  |  |

| bit 15       |                                                  |                         |               |                  |                  |                 | bit 8              |  |  |  |  |

|              |                                                  |                         | D////         |                  | D///             | D///            |                    |  |  |  |  |

| U-x          | U-x                                              | U-x                     | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x              |  |  |  |  |

|              |                                                  | —                       | RB0           | DLC3             | DLC2             | DLC1            | DLC0               |  |  |  |  |

| bit 7        |                                                  |                         |               |                  |                  |                 | bit (              |  |  |  |  |

| Legend:      |                                                  |                         |               |                  |                  |                 |                    |  |  |  |  |

| R = Readab   | le bit                                           | W = Writable            | bit           | U = Unimpler     | mented bit, read | <b>d as</b> '0' |                    |  |  |  |  |

| -n = Value a | t POR                                            | '1' = Bit is set        | t             | '0' = Bit is cle |                  |                 | a = Bit is unknown |  |  |  |  |

|              |                                                  |                         |               |                  |                  |                 |                    |  |  |  |  |

| bit 15-10    | EID<5:0>: E>                                     | xtended Identifi        | er bits       |                  |                  |                 |                    |  |  |  |  |

| bit 9        | RTR: Remote Transmission Request bit             |                         |               |                  |                  |                 |                    |  |  |  |  |

|              | When IDE = 1:                                    |                         |               |                  |                  |                 |                    |  |  |  |  |

|              | 1 = Message will request remote transmission     |                         |               |                  |                  |                 |                    |  |  |  |  |

|              | 0 = Normal message                               |                         |               |                  |                  |                 |                    |  |  |  |  |

|              | $\frac{\text{When IDE} = 0}{\text{The DTD} + 1}$ |                         |               |                  |                  |                 |                    |  |  |  |  |

|              |                                                  | The RTR bit is ignored. |               |                  |                  |                 |                    |  |  |  |  |

| bit 8        |                                                  | RB1: Reserved Bit 1     |               |                  |                  |                 |                    |  |  |  |  |

|              |                                                  | et this bit to '0' p    | -             | ocol.            |                  |                 |                    |  |  |  |  |

| bit 7-5      | Unimplemer                                       | nted: Read as '         | 0'            |                  |                  |                 |                    |  |  |  |  |

| bit 4        | RB0: Reserv                                      | ed Bit 0                |               |                  |                  |                 |                    |  |  |  |  |

|              | User must se                                     | et this bit to '0' p    | per CAN proto | ocol.            |                  |                 |                    |  |  |  |  |

|              |                                                  |                         |               |                  |                  |                 |                    |  |  |  |  |

#### BUFFER 22-3: CANx MESSAGE BUFFER WORD 2

| bit 3-0 DLC<3:0>: Data Length Code bits |

|-----------------------------------------|

|-----------------------------------------|

#### BUFFER 22-4: CANx MESSAGE BUFFER WORD 3

| R/W-x                             | R/W-x                                                               | R/W-x | R/W-x  | R/W-x                              | R/W-x | R/W-x | R/W-x |

|-----------------------------------|---------------------------------------------------------------------|-------|--------|------------------------------------|-------|-------|-------|

|                                   |                                                                     |       | Byte ? | 1<15:8>                            |       |       |       |

| bit 15                            |                                                                     |       |        |                                    |       |       | bit 8 |

|                                   |                                                                     |       |        |                                    |       |       |       |

| R/W-x                             | R/W-x                                                               | R/W-x | R/W-x  | R/W-x                              | R/W-x | R/W-x | R/W-x |

|                                   |                                                                     |       | Byte   | 0<7:0>                             |       |       |       |

| bit 7                             |                                                                     |       |        |                                    |       |       | bit 0 |

|                                   |                                                                     |       |        |                                    |       |       |       |

| Legend:                           |                                                                     |       |        |                                    |       |       |       |

| R = Readable bit W = Writable bit |                                                                     |       | oit    | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at P                   | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is u |       |        | x = Bit is unkr                    | nown  |       |       |

bit 15-8 Byte 1<15:8>: CANx Message Byte 1 bits

bit 7-0 Byte 0<7:0>: CANx Message Byte 0 bits

# dsPIC33EVXXXGM00X/10X FAMILY

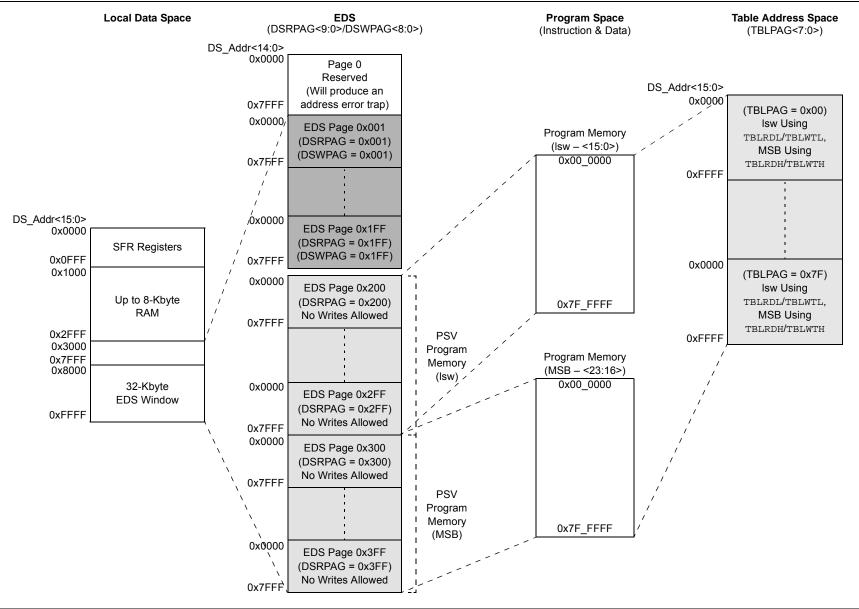

#### FIGURE 26-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

#### TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CHARACTERISTICS |                |                                                              |                     | (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |   |               |      |                                                                             |       |            |

|--------------------|----------------|--------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|------|-----------------------------------------------------------------------------|-------|------------|

| Param<br>No.       | Symbol         | Characteristic <sup>(1)</sup>                                |                     | Characteristic <sup>(1)</sup>                                                                                                                                    |   | Min.          | Тур. | Max.                                                                        | Units | Conditions |

| TB10               | T⊤xH           | TxCK High<br>Time                                            | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                             |   | _             | ns   | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |       |            |

| TB11               | ΤτχL           | TxCK Low<br>Time                                             | Synchronous<br>mode | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                             |   | _             | ns   | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |       |            |

| TB15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous<br>mode | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                           | _ | _             | ns   | N = Prescaler Value<br>(1, 8, 64, 256)                                      |       |            |

| TB20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                     | 0.75 Tcy + 40                                                                                                                                                    |   | 1.75 Tcy + 40 | ns   |                                                                             |       |            |

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                |                                                              |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |               |       |                                        |

|--------------------|----------------|--------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|----------------------------------------|

| Param<br>No.       | Symbol         | Charao                                                       | cteristic <sup>(1)</sup>       | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max.          | Units | Conditions                             |

| TC10               | ТтхН           | TxCK High<br>Time                                            | Synchronous                    | Tcy + 20                                                                                                                                                                                                                                                                                |      | —             | ns    | Must also meet<br>Parameter TC15       |

| TC11               | ΤτxL           | TxCK Low<br>Time                                             | Synchronous                    | Tcy + 20                                                                                                                                                                                                                                                                                | _    | —             | ns    | Must also meet<br>Parameter TC15       |

| TC15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous,<br>with Prescaler | 2 Tcy + 40                                                                                                                                                                                                                                                                              | _    | —             | ns    | N = Prescaler Value<br>(1, 8, 64, 256) |

| TC20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                | 0.75 Tcy + 40                                                                                                                                                                                                                                                                           | _    | 1.75 Tcy + 40 | ns    |                                        |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

NOTES:

### 31.2 AC Characteristics and Timing Parameters

The information contained in this section defines the dsPIC33EVXXXGM00X/10X family AC characteristics and timing parameters for high-temperature devices. However, all AC timing specifications in this section are the same as those in Section 30.2 "AC Characteristics and Timing Parameters", with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter OS53 in Section 30.2 "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

#### TABLE 31-12: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) |

|--------------------|-----------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$         |

|                    | Operating voltage VDD range as described in Table 31-1.               |

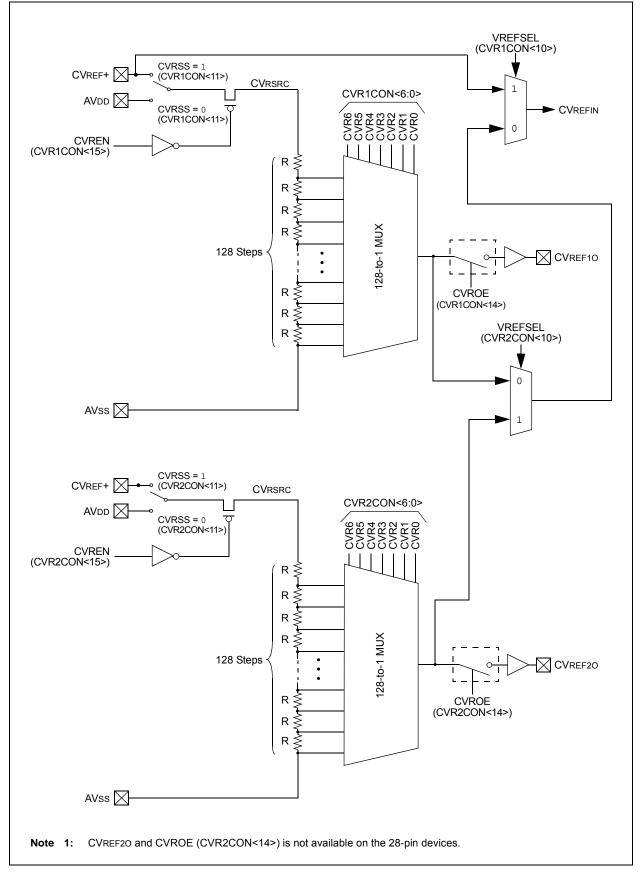

#### FIGURE 31-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## dsPIC33EVXXXGM00X/10X FAMILY

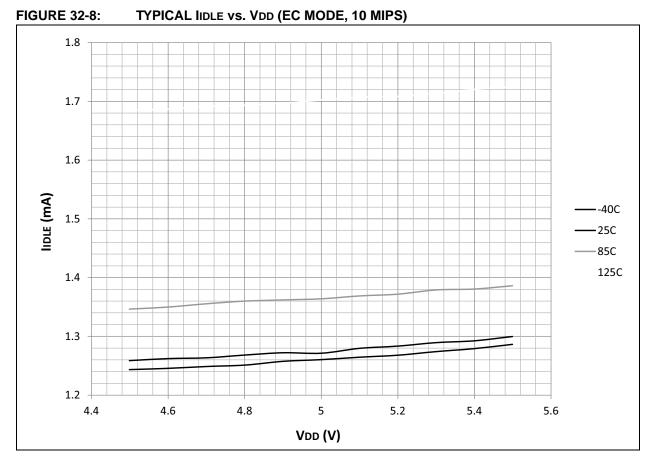

#### 32.2 IIDLE

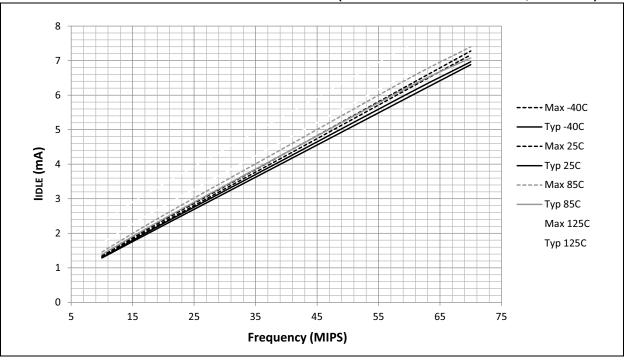

FIGURE 32-7: TYPICAL/MAXIMUM lidle vs. Fosc (EC MODE 10 MHz TO 70 MHz, 5.5V MAX)

DS70005144E-page 416

# dsPIC33EVXXXGM00X/10X FAMILY

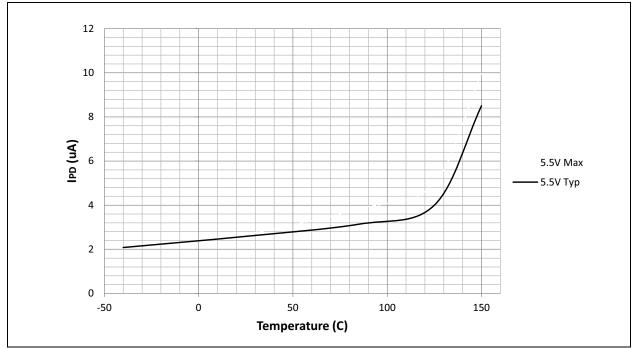

### FIGURE 32-19: TYPICAL/MAXIMUM △IwDT vs. TEMPERATURE

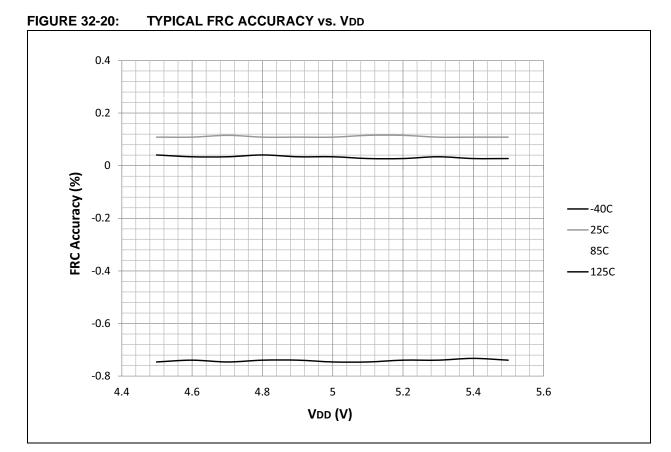

#### 32.5 FRC

DS70005144E-page 422

NOTES:

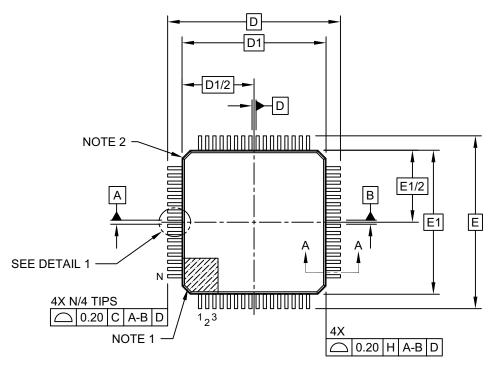

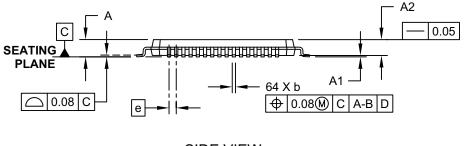

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2