Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm003-i-m5 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EVXXXGM00X/ 10X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33EVXXXGM00X/10X family devices contain control registers for Modulo Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |  |  |  |  |

|---------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |  |  |  |  |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 1                        |  |  |  |  |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 2                        |  |  |  |  |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |  |  |  |  |

| PC                                                | 23-Bit Program Counter                                    |  |  |  |  |

| SR                                                | ALU and DSP Engine STATUS Register                        |  |  |  |  |

| SPLIM                                             | Stack Pointer Limit Value Register                        |  |  |  |  |

| TBLPAG                                            | Table Memory Page Address Register                        |  |  |  |  |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |  |  |  |  |

| RCOUNT                                            | REPEAT Loop Counter Register                              |  |  |  |  |

| DCOUNT                                            | DO Loop Count Register                                    |  |  |  |  |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |  |  |  |  |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |  |  |  |  |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |  |  |  |  |

Note 1: Memory-mapped W0 through W14 represents the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

## REGISTER 3-3: CTXTSTAT: CPU W REGISTER CONTEXT STATUS REGISTER

| U-0          | U-0                                                     | U-0                                                     | U-0                                | U-0                            | R-0                                | R-0             | R-0    |

|--------------|---------------------------------------------------------|---------------------------------------------------------|------------------------------------|--------------------------------|------------------------------------|-----------------|--------|

| _            |                                                         |                                                         | —                                  | _                              | CCTXI2                             | CCTXI1          | CCTXI0 |

| oit 15       |                                                         |                                                         |                                    |                                |                                    |                 | bit 8  |

|              |                                                         |                                                         |                                    |                                |                                    |                 |        |

| U-0          | U-0                                                     | U-0                                                     | U-0                                | U-0                            | R-0                                | R/W-0           | R/W-0  |

| _            | <u> </u>                                                |                                                         | _                                  | —                              | MCTXI2                             | MCTXI1          | MCTXI0 |

| bit 7        |                                                         |                                                         |                                    |                                |                                    |                 | bit C  |

|              |                                                         |                                                         |                                    |                                |                                    |                 |        |

| Legend:      |                                                         |                                                         |                                    |                                |                                    |                 |        |

| R = Readab   |                                                         | W = Writable                                            | bit                                | •                              | mented bit, read                   |                 |        |

| -n = Value a | t POR                                                   | '1' = Bit is set                                        |                                    | '0' = Bit is cle               | eared                              | x = Bit is unkr | nown   |

| bit 7-3      | 001 = Alterna<br>000 = Default                          | ed<br>te Working Re<br>te Working Re<br>register set is | gister Set 1 is<br>currently in us | currently in us                |                                    |                 |        |

|              | -                                                       | ted: Read as '                                          |                                    |                                |                                    |                 |        |

| bit 2-0      | 111 = Reserv<br>•<br>•<br>011 = Reserv<br>010 = Alterna | ed<br>te Working Re<br>te Working Re                    | gister Set 2 w                     | as most recen<br>as most recen | tly manually se<br>tly manually se |                 |        |

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### TABLE 4-45: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| For the MOV instructions, the addressing      |

|-----------------------------------------------|

| mode specified in the instruction can differ  |

| for the source and destination EA. How-       |

| ever, the 4-bit Wb (Register Offset) field is |

| shared by both source and destination         |

| (but typically only used by one).             |

|                                               |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set, {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X Data Space) and W11 (in Y Data Space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (Branch) instructions use 16-bit signed literals to specify the Branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| R/W-0         | R/W-0                                                       | R/W-0                                | R/W-0    | R/W-0            | U-0            | R/W-0               | U-0          |

|---------------|-------------------------------------------------------------|--------------------------------------|----------|------------------|----------------|---------------------|--------------|

| T5MD          | T4MD                                                        | T3MD                                 | T2MD     | T1MD             | —              | PWMMD               | —            |

| bit 15        |                                                             |                                      |          |                  |                |                     | bit 8        |

| R/W-0         | R/W-0                                                       | R/W-0                                | R/W-0    | R/W-0            | U-0            | R/W-0               | R/W-0        |

| I2C1MD        |                                                             |                                      |          |                  | 0-0            | C1MD <sup>(1)</sup> |              |

| bit 7         | U2MD                                                        | U1MD                                 | SPI2MD   | SPI1MD           | —              | CTMD                | AD1MD<br>bit |

|               |                                                             |                                      |          |                  |                |                     |              |

| Legend:       |                                                             |                                      |          |                  |                |                     |              |

| R = Readable  |                                                             | W = Writable                         |          | •                | mented bit, re | ad as '0'           |              |

| -n = Value at | POR                                                         | '1' = Bit is set                     |          | '0' = Bit is cle | ared           | x = Bit is unkn     | own          |

| bit 15        | T5MD: Timer                                                 | 5 Module Disal                       | ole bit  |                  |                |                     |              |

|               |                                                             | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 14        | T4MD: Timer                                                 | 4 Module Disal                       | ole bit  |                  |                |                     |              |

|               | 1 = Timer4 m                                                | odule is disable                     | ed       |                  |                |                     |              |

| bit 13        |                                                             | 3 Module Disal                       |          |                  |                |                     |              |

|               |                                                             | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 12        | T2MD: Timer                                                 | 2 Module Disal                       | ole bit  |                  |                |                     |              |

|               | -                                                           | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 11        | T1MD: Timer                                                 | 1 Module Disal                       | ole bit  |                  |                |                     |              |

|               | -                                                           | odule is disable<br>odule is enable  |          |                  |                |                     |              |

| bit 10        | Unimplemen                                                  | ted: Read as '                       | 0'       |                  |                |                     |              |

| bit 9         | PWMMD: PW                                                   | /M Module Dis                        | able bit |                  |                |                     |              |

|               |                                                             | dule is disabled<br>dule is enabled  |          |                  |                |                     |              |

| bit 8         | Unimplemen                                                  | ted: Read as '                       | 0'       |                  |                |                     |              |

| bit 7         | 12C1MD: 12C                                                 | 1 Module Disal                       | ole bit  |                  |                |                     |              |

|               |                                                             | lule is disabled<br>lule is enabled  |          |                  |                |                     |              |

| bit 6         | U2MD: UART                                                  | 2 Module Disa                        | ble bit  |                  |                |                     |              |

|               | 1 = UART2 module is disabled<br>0 = UART2 module is enabled |                                      |          |                  |                |                     |              |

| bit 5         | U1MD: UART                                                  | 1 Module Disa                        | ble bit  |                  |                |                     |              |

|               |                                                             | nodule is disabl<br>nodule is enable |          |                  |                |                     |              |

| bit 4         | SPI2MD: SPI                                                 | 2 Module Disa                        | ole bit  |                  |                |                     |              |

|               |                                                             | lule is disabled<br>lule is enabled  |          |                  |                |                     |              |

| bit 3         | SPI1MD: SPI                                                 | 1 Module Disa                        | ole bit  |                  |                |                     |              |

|               |                                                             | dule is disabled<br>dule is enabled  |          |                  |                |                     |              |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** This bit is available on dsPIC33EVXXXGM10X devices only.

| R/W-0         | R/W-0  | R/W-0                              | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------|------------------------------------|--------|------------------|------------------|-----------------|--------|

| FLT2R7        | FLT2R6 | FLT2R5                             | FLT2R4 | FLT2R3           | FLT2R2           | FLT2R1          | FLT2R0 |

| bit 15        | ·      |                                    |        |                  |                  |                 | bit 8  |

| R/W-0         | R/W-0  | R/W-0                              | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| FLT1R7        | FLT1R6 | FLT1R5                             | FLT1R4 | FLT1R3           | FLT1R2           | FLT1R1          | FLT1R0 |

| oit 7         | I      |                                    |        |                  |                  |                 | bit 0  |

|               |        |                                    |        |                  |                  |                 |        |

| _egend:       |        |                                    |        |                  |                  |                 |        |

| R = Readable  | e bit  | W = Writable                       | bit    | U = Unimpler     | nented bit, read | <b>d as</b> '0' |        |

| -n = Value at | POR    | '1' = Bit is set                   | t      | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-8      |        | Ų                                  |        |                  | onding RPn Pi    | n bits          |        |

|               | •      | -2 for input pin                   |        | nbers)           |                  |                 |        |

|               | •      | Input tied to R                    | PI181  |                  |                  |                 |        |

|               | •      |                                    |        |                  |                  |                 |        |

|               | •      |                                    |        |                  |                  |                 |        |

|               |        | Input tied to C<br>Input tied to V |        |                  |                  |                 |        |

| bit 7-0       |        | Assign PWM<br>-2 for input pin     |        |                  | onding RPn Pi    | n bits          |        |

|               | •      | Input tied to R                    |        | ,                |                  |                 |        |

|               | •      |                                    |        |                  |                  |                 |        |

|               | •      |                                    |        |                  |                  |                 |        |

|               | •      | Input tied to C                    |        |                  |                  |                 |        |

|               |        | Input tied to C                    |        |                  |                  |                 |        |

#### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12

00000000 = Input tied to Vss

## REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0                                                             | U-0 | R/W-0  | R/W-0            | R/W-0  | R/W-0           | R/W-0  | R/W-0  |

|-----------------------------------------------------------------|-----|--------|------------------|--------|-----------------|--------|--------|

| —                                                               | _   | RP39R5 | RP39R4           | RP39R3 | RP39R2          | RP39R1 | RP39R0 |

| bit 15                                                          |     | -      |                  |        |                 |        | bit 8  |

|                                                                 |     |        |                  |        |                 |        |        |

| U-0                                                             | U-0 | R/W-0  | R/W-0            | R/W-0  | R/W-0           | R/W-0  | R/W-0  |

| —                                                               | —   | RP38R5 | RP38R4           | RP38R3 | RP38R2          | RP38R1 | RP38R0 |

| bit 7                                                           |     |        |                  |        |                 |        | bit 0  |

|                                                                 |     |        |                  |        |                 |        |        |

| Legend:                                                         |     |        |                  |        |                 |        |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read a |     |        | <b>as</b> '0'    |        |                 |        |        |

| -n = Value at POR '1' = Bit is set                              |     |        | '0' = Bit is cle | ared   | x = Bit is unkr | nown   |        |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP39R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP38R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP38 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP41R5 | RP41R4 | RP41R3 | RP41R2 | RP41R1 | RP41R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | —   | RP120R5 <sup>(1)</sup> | RP120R4 <sup>(1)</sup> | RP120R3 <sup>(1)</sup> | RP120R2 <sup>(1)</sup> | RP120R1 <sup>(1)</sup> | RP120R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 11-3 for peripheral function numbers) |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0  | RP120R<5:0>: Peripheral Output Function is Assigned to RP120 Output Pin bits <sup>(1)</sup>                                                |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-29: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP177R<5:0>:** Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 11-3 for peripheral function numbers)

Note 1: RP120R<5:0> is present in dsPIC33EVXXXGM006/106 devices only.

| R/W-1           | R/W-1                                                                     | R/W-0                                                                             | R/W-0                    | R/W-0                | R/W-0                        | R/W-0           | R/W-0  |

|-----------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|----------------------|------------------------------|-----------------|--------|

| PENH            | PENL                                                                      | POLH                                                                              | POLL                     | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>         | OVRENH          | OVRENL |

| bit 15          |                                                                           |                                                                                   |                          |                      |                              |                 | bit 8  |

|                 |                                                                           |                                                                                   |                          |                      |                              |                 |        |

| R/W-0           | R/W-0                                                                     | R/W-0                                                                             | R/W-0                    | R/W-0                | R/W-0                        | R/W-0           | R/W-0  |

| OVRDAT1         | OVRDAT0                                                                   | FLTDAT1                                                                           | FLTDAT0                  | CLDAT1               | CLDAT0                       | SWAP            | OSYNC  |

| bit 7           |                                                                           |                                                                                   |                          |                      |                              |                 | bit 0  |

|                 |                                                                           |                                                                                   |                          |                      |                              |                 |        |

| Legend:         |                                                                           |                                                                                   |                          |                      |                              |                 |        |

| R = Readable    | bit                                                                       | W = Writable                                                                      | bit                      | U = Unimplei         | mented bit, read             | <b>as</b> '0'   |        |

| -n = Value at F | POR                                                                       | '1' = Bit is set                                                                  |                          | '0' = Bit is cle     | eared                        | x = Bit is unkr | nown   |

|                 |                                                                           |                                                                                   |                          |                      |                              |                 |        |

| bit 15          | PENH: PWM                                                                 | xH Output Pin                                                                     | Ownership bit            |                      |                              |                 |        |

|                 |                                                                           | odule controls                                                                    |                          |                      |                              |                 |        |

|                 |                                                                           | dule controls th                                                                  | •                        | ו                    |                              |                 |        |

| bit 14          |                                                                           | L Output Pin                                                                      | •                        |                      |                              |                 |        |

|                 |                                                                           | odule controls<br>dule controls th                                                |                          |                      |                              |                 |        |

| bit 13          |                                                                           |                                                                                   | •                        | I                    |                              |                 |        |

| DIL 13          | <b>POLH:</b> PWMxH Output Pin Polarity bit<br>1 = PWMxH pin is active-low |                                                                                   |                          |                      |                              |                 |        |

|                 |                                                                           | pin is active-hig                                                                 |                          |                      |                              |                 |        |

| bit 12          |                                                                           | <l f<="" output="" pin="" td=""><td></td><td></td><td></td><td></td><td></td></l> |                          |                      |                              |                 |        |

|                 |                                                                           | in is active-low                                                                  |                          |                      |                              |                 |        |

|                 | 0 = PWMxL p                                                               | in is active-hig                                                                  | h                        |                      |                              |                 |        |

| bit 11-10       | PMOD<1:0>:                                                                | PWMx I/O Pin                                                                      | Mode bits <sup>(1)</sup> |                      |                              |                 |        |

|                 | 11 = Reserve                                                              |                                                                                   |                          |                      |                              |                 |        |

|                 |                                                                           | /O pin pair is ir<br>/O pin pair is ir                                            |                          |                      |                              |                 |        |

|                 |                                                                           | O pin pair is in<br>O pin pair is ir                                              |                          | •                    |                              |                 |        |

| bit 9           |                                                                           | verride Enable                                                                    | •                        |                      |                              |                 |        |

|                 | 1 = OVRDAT                                                                | 1 controls the o                                                                  | output on the I          | PWMxH pin            |                              |                 |        |

|                 |                                                                           | enerator contro                                                                   |                          |                      |                              |                 |        |

| bit 8           | OVRENL: Ov                                                                | erride Enable                                                                     | for PWMxL Pi             | n bit                |                              |                 |        |

|                 |                                                                           | 0 controls the o                                                                  | •                        |                      |                              |                 |        |

|                 | •                                                                         | nerator contro                                                                    |                          | •                    |                              |                 |        |

| bit 7-6         |                                                                           |                                                                                   |                          |                      | ide is Enabled b             | its             |        |

|                 |                                                                           | •                                                                                 |                          |                      | d by OVRDAT1.<br>by OVRDAT0. |                 |        |

| bit 5-4         |                                                                           |                                                                                   |                          | •                    | TMOD is Enable               | d hits          |        |

|                 |                                                                           | ve, PWMxH is                                                                      |                          |                      |                              |                 |        |

|                 |                                                                           | ve, PWMxL is                                                                      |                          |                      |                              |                 |        |

| bit 3-2         |                                                                           |                                                                                   |                          | •                    | /IOD is Enabled              | bits            |        |

|                 | If current limit                                                          | is active, PWI                                                                    | MxH is driven            | to the state sp      | ecified by CLDA              | T1.             |        |

|                 | If current limit                                                          | is active, PWI                                                                    | MxL is driven t          | o the state spe      | ecified by CLDA              | ГО.             |        |

| Note 1: The     | ese bits should                                                           | not be change                                                                     | d after the PW           | /Mx module is        | enabled (PTEN                | = 1).           |        |

|                 |                                                                           |                                                                                   |                          |                      |                              |                 |        |

# REGISTER 17-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

**Note 1:** These bits should not be changed after the PWMx module is enabled (PTEN = 1). **2:** If the PWMI OCK Configuration bit (EDEVOPT<0>) is a '1' the IOCONy register can only be

2: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

## REGISTER 17-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

| U-0                               | U-0   | U-0              | U-0                                | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|-----------------------------------|-------|------------------|------------------------------------|-----------------------------------------|-------|--------|-------|

| —                                 | —     | —                | —                                  |                                         | LEE   | <11:8> |       |

| bit 15                            |       |                  |                                    |                                         |       |        | bit 8 |

|                                   |       |                  |                                    |                                         |       |        |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|                                   |       |                  | LEE                                | 3<7:0>                                  |       |        |       |

| bit 7                             |       |                  |                                    |                                         |       |        | bit 0 |

|                                   |       |                  |                                    |                                         |       |        |       |

| Legend:                           |       |                  |                                    |                                         |       |        |       |

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                                         |       |        |       |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknown |       |        | nown  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

## 20.3 Receive Mode

The module can be configured for receive operation by setting the RCVEN (SENTxCON1<11>) bit. The time between each falling edge is compared to SYNCMIN<15:0> (SENTxCON3<15:0>) and SYNCMAX<15:0> (SENTxCON2<15:0>), and if the measured time lies between the minimum and maximum limits, the module begins to receive data. The validated Sync time is captured in the SENTxSYNC register and the tick time is calculated. Subsequent falling edges are verified to be within the valid data width and the data is stored in the SENTxDATH/L register. An interrupt event is generated at the completion of the message and the user software should read the SENTx Data register before the reception of the next nibble. The equation for SYNCMIN<15:0> and SYNCMAX<15:0> is shown in Equation 20-3.

#### EQUATION 20-3: SYNCMIN<15:0> AND SYNCMAX<15:0> CALCULATIONS

$TTICK = TCLK \bullet (TICKTIME < 15:0 > + 1)$

FRAMETIME<15:0> = TTICK/TFRAME

SyncCount = 8 x FRCV x TTICK

SYNCMIN<15:0> = 0.8 x SyncCount

SYNCMAX<15:0> = 1.2 x SyncCount

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 \ge 848 + 12N$

#### Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6  $F_{RCV}$  = FCY x prescaler  $T_{CLK}$  = FCY/Prescaler

For TTICK = 3.0  $\mu$ s and FCLK = 4 MHz, SYNCMIN<15:0> = 76.

| Note: | To ensure a Sync period can be identified, |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|

|       | the value written to SYNCMIN<15:0>         |  |  |  |  |

|       | must be less than the value written to     |  |  |  |  |

|       | SYNCMAX<15:0>.                             |  |  |  |  |

#### 20.3.1 RECEIVE MODE CONFIGURATION

#### 20.3.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 1 for Receive mode.

- 2. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 3. Write CRCEN (SENTxCON1<8>) for hardware or software CRC validation.

- 4. Write PPP (SENTxCON1<7>) = 1 if pause pulse is present.

- 5. Write SENTxCON2 with the value of SYNCMAXx (Nominal Sync Period + 20%).

- Write SENTxCON3 with the value of SYNCMINx (Nominal Sync Period – 20%).

- 7. Enable interrupts and set interrupt priority.

- 8. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

The data should be read from the SENTxDATH/L register after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt trigger.

## 27.2 User OTP Memory

Locations, 800F80h-800FFEh, are a One-Time-Programmable (OTP) memory area. The user OTP words can be used for storing product information, such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

## 27.3 On-Chip Voltage Regulator

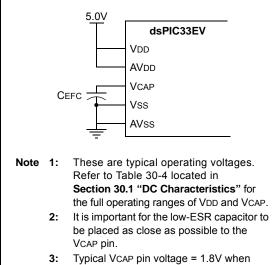

All of the dsPIC33EVXXXGM00X/10X family devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 5.0V. To simplify system design, all devices in the dsPIC33EVXXXGM00X/10X family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5, located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### Typical VCAP pin voltage = 1.8V when VDD ≥ VDDMIN.

## 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the Power-up Timer (PWRT) Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device should VDD fall below the BOR threshold voltage.

| DC CHARACTERISTICS |        |                                      | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |                     |       | ed)   |                                                                |  |

|--------------------|--------|--------------------------------------|---------------------------------------------------------------------------|---------------------|-------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                       | Min.                                                                      | Typ. <sup>(1)</sup> | Max.  | Units | Conditions                                                     |  |

|                    |        | Program Flash Memory                 |                                                                           |                     |       |       |                                                                |  |

| D130               | Eр     | Cell Endurance                       | 10,000                                                                    | —                   | _     | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                         | 4.5                                                                       | —                   | 5.5   | V     |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write             | 4.5                                                                       | —                   | 5.5   | V     |                                                                |  |

| D134               | TRETD  | Characteristic Retention             | 20                                                                        | —                   | —     | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current During<br>Programming | -                                                                         | 10                  | —     | mA    |                                                                |  |

| D136a              | Trw    | Row Write Cycle Time                 | 0.657                                                                     | —                   | 0.691 | ms    | Trw = 4965 FRC cycles,<br>Ta = +85°C (see <b>Note 2)</b>       |  |

| D136b              | Trw    | Row Write Cycle Time                 | 0.651                                                                     | _                   | 0.698 | ms    | Trw = 4965 FRC cycles,<br>Ta = +125°C (see <b>Note 2)</b>      |  |

| D137a              | TPE    | Page Erase Time                      | 19.44                                                                     | _                   | 20.44 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (see <b>Note 2)</b>     |  |

| D137b              | TPE    | Page Erase Time                      | 19.24                                                                     | _                   | 20.65 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (see <b>Note 2)</b>    |  |

| D138a              | Tww    | Word Write Cycle Time                | 45.78                                                                     | _                   | 48.15 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (see <b>Note 2)</b>        |  |

| D138b              | Tww    | Word Write Cycle Time                | 45.33                                                                     | _                   | 48.64 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (see <b>Note 2)</b>       |  |

#### TABLE 30-13: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Other conditions: FRC = 7.3728 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 30-20) and the value of the FRC Oscillator Tuning register.

#### TABLE 30-14: ELECTRICAL CHARACTERISTICS: INTERNAL BAND GAP REFERENCE VOLTAGE

| DC CHARACTERISTICS |        |                                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |            |  |  |

|--------------------|--------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|--|

| Param<br>No.       | Symbol | Characteristic                         | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions |  |  |

| DVR10              | Vbg    | Internal Band Gap Reference<br>Voltage | 1.14                                                                                                                                                                                                                                                                                  | 1.2  | 1.26 | V     |            |  |  |

# dsPIC33EVXXXGM00X/10X FAMILY

© 2013-2016 Microchip Technology Inc.

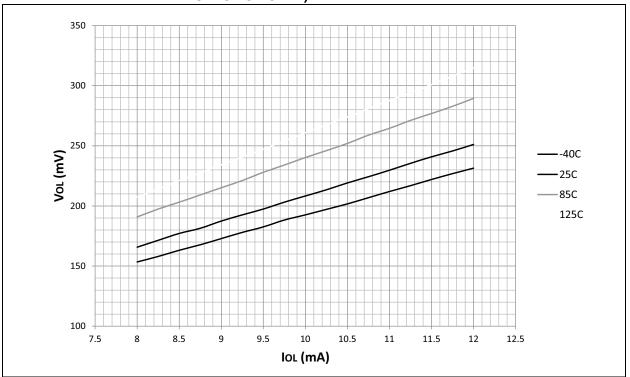

FIGURE 32-33: TYPICAL Vol 4x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

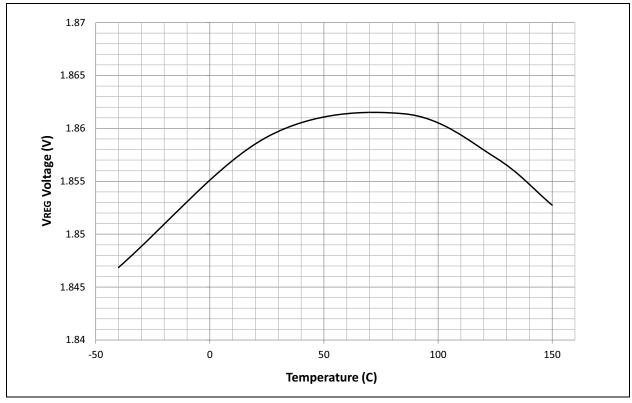

#### 32.11 VREG

FIGURE 32-34: TYPICAL REGULATOR VOLTAGE vs. TEMPERATURE

© 2013-2016 Microchip Technology Inc.

# dsPIC33EVXXXGM00X/10X FAMILY

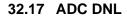

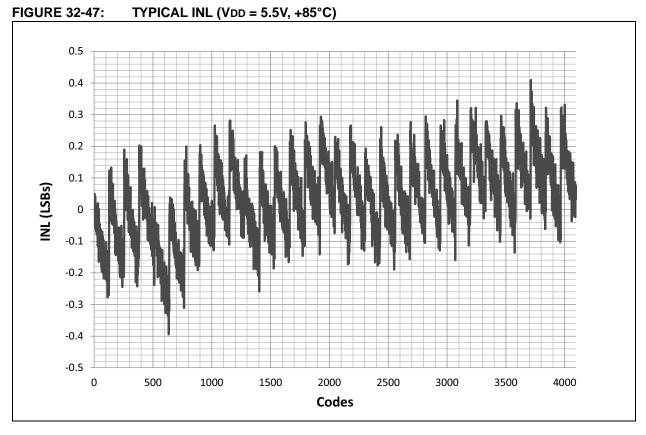

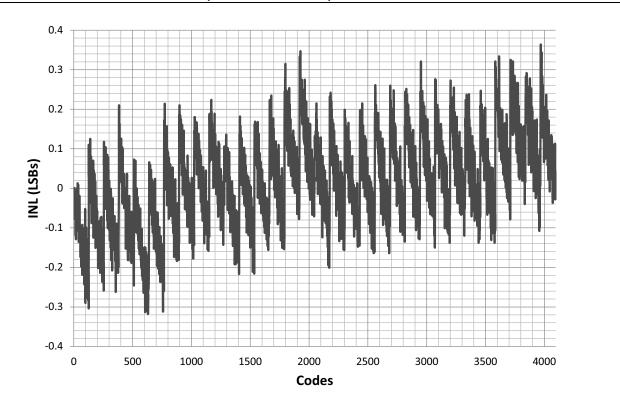

FIGURE 32-48: TYPICAL INL (VDD = 5.5V, +125°C)

NOTES:

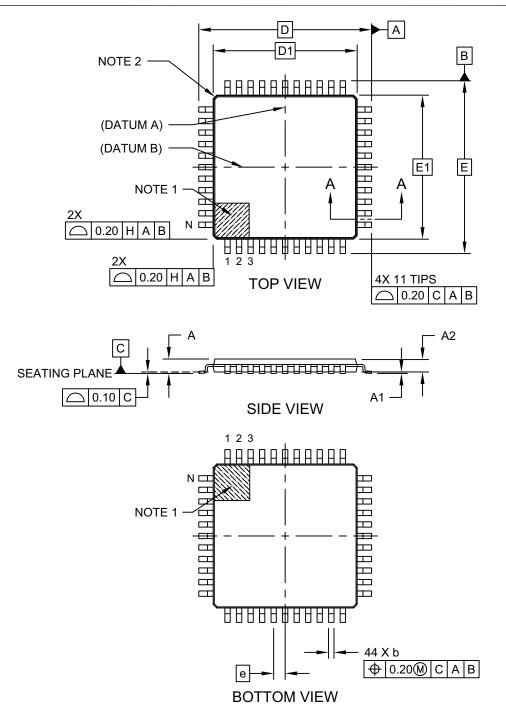

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

# APPENDIX A: REVISION HISTORY

## **Revision A (December 2013)**

This is the initial version of this document.

## Revision B (June 2014)

This revision incorporates the following updates:

- Sections:

- Added Section 31.0 "High-Temperature Electrical Characteristics"

- Updated the "Power Management" section, the "Input/Output" section, Section 3.3

"Data Space Addressing", Section 4.2

"Data Address Space", Section 4.3.2

"Extended X Data Space", Section 4.6.1

"Bit-Reversed Addressing Implementation", Section 7.4.1 "INTCON1 through INTCON4", Section 11.7 "I/O Helpful Tips"

- Updated note in Section 17.0 "High-Speed PWM Module", Section 18.0 "Serial Peripheral Interface (SPI)", Section 27.8 "Code Protection and CodeGuard™ Security"

- Updated title of Section 20.0 "Single-Edge Nibble Transmission (SENT)"

- Updated Section 34.0 "Packaging Information". Deleted e3, Pb-free and Industrial (I) temperature range indication throughout the section, and updated the packaging diagrams

- Updated the "Product Identification System" section

- Registers:

- Updated Register 3-2, Register 7-2, Register 7-6, Register 9-2, Register 11-3, Register 14-1, Register 14-3, Register 14-11, Register 15-1, Register 22-4

- Figures:

- Added Figure 4-6, Figure 4-8, Figure 4-14, Figure 4-15, Figure 14-1, Figure 16-1, Figure 17-2, Figure 23-1, Figure 24-1

- Tables:

- Updated Table 1, Table 27-1, Table 27-2, Table 30-6, Table 30-7, Table 30-8, Table 30-9, Table 30-10, Table 30-11, Table 30-12, Table 30-38, Table 30-50, Table 30-53 and added Table 31-11,

- Changes to text and formatting were incorporated throughout the document

## **Revision C (November 2014)**

This revision incorporates the following updates:

- · Sections:

- Added note in Section 5.2 "RTSP Operation"

- Updated "Section 5.4 "Error Correcting Code (ECC)"

- Deleted 44-Terminal Very Thin Leadless Array Package (TL) - 6x6x0.9 mm Body With Exposed Pad (VTLA).

- Registers

- Updated Register 7-6

- Figures:

- Updated Figure 4-1, Figure 4-3, Figure 4-4

- · Tables:

- Updated Table 27-2, Table 31-13, Table 31-14, Table 31-15

- Added Table 31-16, Table 31-17

## **Revision D (April 2015)**

This revision incorporates the following updates:

- Sections:

- Updated the Clock Management, Timers/ Output Compare/Input Capture, Communication Interfaces and Input/Output sections at the beginning of the data sheet (Page 1 and Page 2).

- Updated all pin diagrams at the beginning of the data sheet (Page 4 through Page 9).

- Added Section 11.6 "High-Voltage Detect (HVD)"

- Updated Section 13.0 "Timer2/3 and Timer4/5"

- Corrects all Buffer heading numbers in Section 22.4 "CAN Message Buffers"

- Registers

- Updated Register 3-2, Register 25-2, Register 26-2

- Figures

- Updated Figure 26-1, Figure 30-5, Figure 30-32

- Tables

- Updated Table 1, Table 4-25, Table 30-10, Table 30-22, Table 30-53 and Table 31-8

- Changes to text and formatting were incorporated throughout the document