Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm004-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EVXXXGM00X/10X PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. The following pages show the devices' pinout diagrams.

# TABLE 1: dsPIC33EVXXXGM00X/10X FAMILY DEVICES

|                   | ry Bytes             | es         |      | lels         | s (T1)             | ers           | ure           | pare           |       |       |     |                  |      | ADC         | ts         | arators            |              |              | lect (PPS)                  | I/O (GPIO)                 | rupts               |             | ø            |   |

|-------------------|----------------------|------------|------|--------------|--------------------|---------------|---------------|----------------|-------|-------|-----|------------------|------|-------------|------------|--------------------|--------------|--------------|-----------------------------|----------------------------|---------------------|-------------|--------------|---|

| Device            | Program Memory Bytes | SRAM Bytes | CAN  | DMA Channels | 16-Bit Timers (T1) | 32-Bit Timers | Input Capture | Output Compare | ВWM   | UART  | SPI | I <sup>2</sup> C | SENT | 10/12-Bit A | ADC Inputs | Op Amp/Comparators | CTMU         | Security     | Peripheral Pin Select (PPS) | General Purpose I/O (GPIO) | External Interrupts | Pins        | Packages     |   |

| dsPIC33EV32GM002  | 001/                 | 414        | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV32GM102  | 32K                  | 4K         | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV64GM002  |                      |            | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV64GM102  | 64K                  | 8K         | 1    | 4            | 5                  | 2             | 4             | 4              | 3x2   | 2     | 2   | 1                | 2    | 1           | 11         | 3/4                | 1            | Intermediate | Y                           | 21                         | 3                   | 28          | SPDIP, SOIC, |   |

| dsPIC33EV128GM002 | 1001/                | 01/        | 0    | 4            | 5                  | 2             | 4             | 4              | . 372 |       | 2   | 1                | 2    | 1           |            | 5/4                |              |              | 21                          | 5                          | 20                  | SSOP, QFN-S |              |   |

| dsPIC33EV128GM102 | 128K                 | 8K         | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV256GM002 | 256K                 | 161        | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV256GM102 | 2001                 | 16K        | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV32GM004  | 32K                  | 4K         | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV32GM104  | JZK                  | 41         | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV64GM004  | 64K                  | 8K         | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV64GM104  | 041                  | or         | 1    | 4            | 5                  | 2             | 4             | 4              | 3x2   | 2     | 2   | 2 1 2            | 1 2  | 2 1 24      | 4/5 1      | 1                  | Intermediate | Y 35         | 35                          | 3                          | 44                  |             |              |   |

| dsPIC33EV128GM004 | 128K                 | 8K         | 0    | 4 5          | 5 2                | 2             | -             |                |       |       |     |                  |      |             |            | internetiate       |              | T 35         | 5                           |                            | TQFP, QFN           |             |              |   |

| dsPIC33EV128GM104 | 1201                 | UN         | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV256GM004 | 256K                 | 16K        | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV256GM104 |                      |            | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV32GM006  | 32K                  | 4K         | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV32GM106  |                      |            | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV64GM006  | 64K                  | 8K         | 8K 0 |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV64GM106  | 2                    | 5.1        | 1    | 4            | 5                  | 2             | 4             | 4              | 3x2   | 2     | 2   | 1                | 2    | 1           | 36         | 4/5                | 1            | Intermediate | Y                           | 53                         | 3                   | 64          | TQFP, QFN    |   |

| dsPIC33EV128GM006 | 128K                 | 8K         | 0    |              | 4                  | Ŭ             | -             |                |       | 0.1.2 | -   | -                |      | -           | 1 3        |                    |              |              | Intermediate                | .<br>                      |                     |             | <u> </u>     | , |

| dsPIC33EV128GM106 |                      | 513        | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV256GM006 | 256K                 | 16K        | 0    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

| dsPIC33EV256GM106 | 2001                 | IUIX       | 1    |              |                    |               |               |                |       |       |     |                  |      |             |            |                    |              |              |                             |                            |                     |             |              |   |

# dsPIC33EVXXXGM00X/10X FAMILY

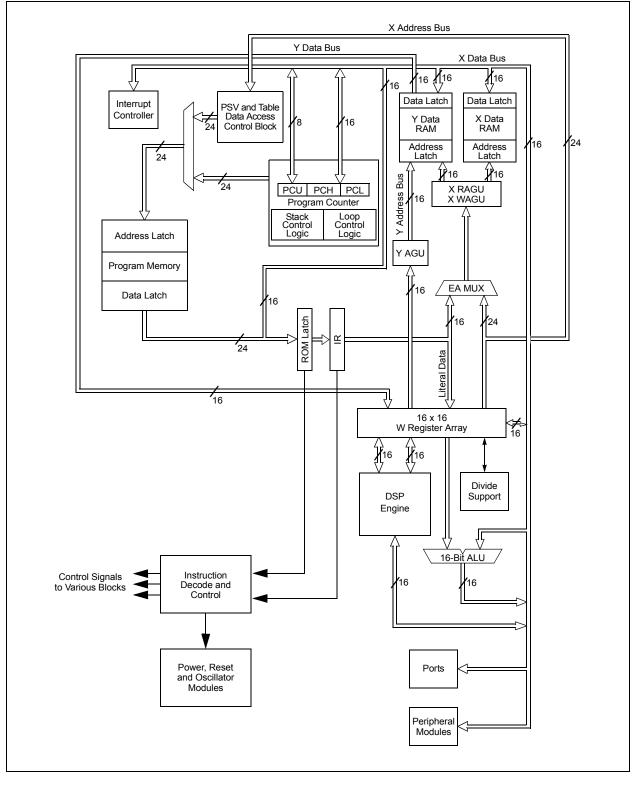

## FIGURE 3-1: dsPIC33EVXXXGM00X/10X FAMILY CPU BLOCK DIAGRAM

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in the data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configure the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses an EDS or a PSV page.

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing. However, this does not include Register Offset Addressing.

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using the Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-43 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when an overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

# TABLE 4-43: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS AND PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

| 0/11        |                     |                | Before       |                        | After          |              |                        |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|--|

| 0/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page Description       |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last Page         | DSRPAG = 0x1FF | 0            | See Note 1             |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>Page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>Page  | DSRPAG = 0x3FF | 0            | See Note 1             |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last Page         | DSWPAG = 0x1FF | 0            | See Note 1             |  |

| U,<br>Read  | r 1                 | DSRPAG = 0x001 | 1            | PSV Page               | DSRPAG = 0x001 | 0            | See Note 1             |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>Page | DSRPAG = 0x200 | 0            | See Note 1             |  |

| U,<br>Read  | [ WII ]             | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>Page  |  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

**Note 1:** The Register Indirect Addressing now addresses a location in the Base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

**3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

4: Pseudolinear Addressing is not supported for large offsets.

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/ 10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

The Flash memory can be programmed in the following three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows for a dsPIC33EVXXXGM00X/10X family device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (PGECx/PGEDx) lines, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed

devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

Enhanced ICSP uses an on-board bootloader, known as the Program Executive (PE), to manage the programming process. Using an SPI data frame format, the Program Executive can erase, program and verify program memory. For more information on Enhanced ICSP, refer to the specific device programming specification.

RTSP is accomplished using the TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data as a double program memory word, a row of 64 instructions (192 bytes) and erase program memory in blocks of 512 instruction words (1536 bytes) at a time.

# 5.1 Table Instructions and Flash Programming

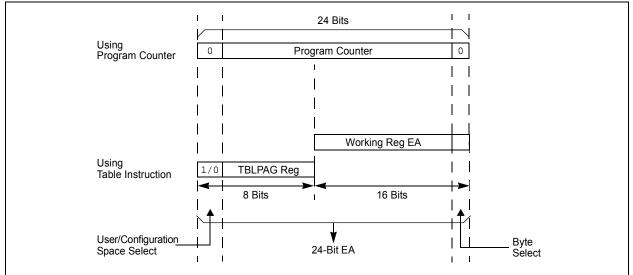

The Flash memory read and the double-word programming operations make use of the TBLRD and TBLWT instructions, respectively. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of the program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of the program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

© 2013-2016 Microchip Technology Inc.

| U-0                               | U-0        | U-0              | U-0             | U-0                                | U-0             | U-0                | R/W-0   |  |  |  |

|-----------------------------------|------------|------------------|-----------------|------------------------------------|-----------------|--------------------|---------|--|--|--|

|                                   | —          | —                | _               | —                                  | —               | —                  | PLLDIV8 |  |  |  |

| bit 15                            |            |                  |                 |                                    |                 |                    | bit 8   |  |  |  |

|                                   |            |                  |                 |                                    |                 |                    |         |  |  |  |

| R/W-0                             | R/W-0      | R/W-1            | R/W-1           | R/W-0                              | R/W-0           | R/W-0              | R/W-0   |  |  |  |

|                                   |            |                  | PLLD            | IV<7:0>                            |                 |                    |         |  |  |  |

| bit 7                             |            |                  |                 |                                    |                 |                    | bit 0   |  |  |  |

|                                   |            |                  |                 |                                    |                 |                    |         |  |  |  |

| Legend:                           |            |                  |                 |                                    |                 |                    |         |  |  |  |

| R = Readable bit W = Writable bit |            |                  | bit             | U = Unimplemented bit, read as '0' |                 |                    |         |  |  |  |

| -n = Value at POR '1' =           |            | '1' = Bit is set | :               | '0' = Bit is cle                   | ared            | x = Bit is unknown |         |  |  |  |

|                                   |            |                  |                 |                                    |                 |                    |         |  |  |  |

| bit 15-9                          | Unimplemer | nted: Read as '  | 0'              |                                    |                 |                    |         |  |  |  |

| bit 8-0                           | PLLDIV<8:0 | >: PLL Feedba    | ck Divisor bits | s (also denoted                    | as 'M', PLL mul | tiplier)           |         |  |  |  |

|                                   | 111111111  | = 513            |                 |                                    |                 |                    |         |  |  |  |

|                                   | •          |                  |                 |                                    |                 |                    |         |  |  |  |

|                                   | •          |                  |                 |                                    |                 |                    |         |  |  |  |

|                                   | 000110000  | = 50 (default)   |                 |                                    |                 |                    |         |  |  |  |

|                                   | •          |                  |                 |                                    |                 |                    |         |  |  |  |

|                                   | •          |                  |                 |                                    |                 |                    |         |  |  |  |

|                                   | •          |                  |                 |                                    |                 |                    |         |  |  |  |

|                                   | 000000010  |                  |                 |                                    |                 |                    |         |  |  |  |

|                                   | 000000000  | -                |                 |                                    |                 |                    |         |  |  |  |

|                                   |            |                  |                 |                                    |                 |                    |         |  |  |  |

# REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

# 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain outputs. This is controlled by the Open-Drain Control x register (ODCx) associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See Table 30-10 in **Section 30.0 "Electrical Characteristics**" for the maximum VIH specification of each pin.

## 11.2 Configuring Analog and Digital Port Pins

The ANSELx registers control the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as timers, UARTs, etc., the corresponding ANSELx bits must be cleared.

The ANSELx register has a default value of 0xFFFF. Therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions table (see Table 1-1 in **Section 1.0 "Device Overview"**).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP, as shown in Example 11-1.

# 11.3 Input Change Notification (ICN)

The Input Change Notification function (ICN) of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States, even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the ICN functionality of each I/O port. The CNENx registers contain the ICN interrupt enable control bits for each of the input pins. Setting any of these bits enables an ICN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pulldown connected to it. The pull-ups and pull-downs act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

**Note:** The pull-ups and pull-downs on ICN pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| —       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | T2CK  | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **T2CKR<7:0>:** Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

• 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

| R/W-0           | R/W-0                                                            | R/W-0                                                                                            | R/W-0                                        | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|-----------------|-----------------|-------|

| IC4R7           | IC4R6                                                            | IC4R5                                                                                            | IC4R4                                        | IC4R3            | IC4R2           | IC4R1           | IC4R0 |

| bit 15          |                                                                  |                                                                                                  |                                              | •                | ·               |                 | bit 8 |

|                 |                                                                  |                                                                                                  |                                              |                  |                 |                 |       |

| R/W-0           | R/W-0                                                            | R/W-0                                                                                            | R/W-0                                        | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| IC3R7           | IC3R6                                                            | IC3R5                                                                                            | IC3R4                                        | IC3R3            | IC3R2           | IC3R1           | IC3R0 |

| oit 7           |                                                                  |                                                                                                  |                                              |                  |                 |                 | bit C |

| Legend:         |                                                                  |                                                                                                  |                                              |                  |                 |                 |       |

| R = Readable    | bit                                                              | W = Writable                                                                                     | bit                                          | U = Unimpler     | mented bit, rea | <b>d as</b> '0' |       |

| -n = Value at F | POR                                                              | '1' = Bit is set                                                                                 |                                              | '0' = Bit is cle | x = Bit is unkı | is unknown      |       |

| bit 7-0         | •<br>•<br>00000001 =<br>00000000 =<br>IC3R<7:0>:<br>(see Table 1 | Input tied to Ri<br>Input tied to Ci<br>Input tied to Vi<br>Assign Input Ca<br>1-2 for input pin | MP1<br>SS<br>apture 3 (IC3)<br>selection nur |                  | onding RPn Pi   | n bits          |       |

|                 | •<br>•<br>00000001 =                                             | Input tied to R                                                                                  | MP1                                          |                  |                 |                 |       |

# REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| _       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | U1RXI | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>l as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

bit 7-0 U1RXR<7:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 • • • • • • • • •

```

00000000 = Input tied to Vss

```

### REGISTER 11-9: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0                                | U-0    | U-0   | U-0              | U-0             | U-0             | U-0   | U-0   |

|------------------------------------|--------|-------|------------------|-----------------|-----------------|-------|-------|

| _                                  | _      | —     |                  | _               | _               | _     | _     |

| bit 15                             | -<br>- |       |                  |                 |                 |       | bit 8 |

| R/W-0                              | R/W-0  | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 | R/W-0 |

|                                    |        |       | U2R>             | (R<7:0>         |                 |       |       |

| bit 7                              |        |       |                  |                 |                 |       | bit 0 |

| Legend:                            |        |       |                  |                 |                 |       |       |

| R = Readable bit W = Writable bi   |        | bit   | U = Unimpler     | nented bit, rea | id as '0'       |       |       |

| -n = Value at POR '1' = Bit is set |        |       | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |       |

| • • • • • • • • • • • • • • • • • • • •                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>U2RXR&lt;7:0&gt;:</b> Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

| 10110101 = Input tied to RPI181                                                                                                         |

| •                                                                                                                                       |

| •                                                                                                                                       |

| •                                                                                                                                       |

| 00000001 = Input tied to CMP1<br>00000000 = Input tied to Vss                                                                           |

|                                                                                                                                         |

# REGISTER 11-15: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| DTCMP3R7 | DTCMP3R6 | DTCMP3R5 | DTCMP3R4 | DTCMP3R3 | DTCMP3R2 | DTCMP3R1 | DTCMP3R0 |

| bit 15   |          |          | •        |          |          |          | bit 8    |

| R/W-0    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| DTCMP2R7 | DTCMP2R6 | DTCMP2R5 | DTCMP2R4 | DTCMP2R3 | DTCMP2R2 | DTCMP2R1 | DTCMP2R0 |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | <b>DTCMP3R&lt;7:0&gt;:</b> Assign PWM Dead-Time Compensation Input 3 to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 10110101 = Input tied to RPI181                                                                                                                         |

|          | •                                                                                                                                                       |

|          | •                                                                                                                                                       |

|          | •                                                                                                                                                       |

|          | 00000001 = Input tied to CMP1                                                                                                                           |

|          | 0000000 = Input tied to Vss                                                                                                                             |

| bit 7-0  | <b>DTCMP2R&lt;7:0&gt;:</b> Assign PWM Dead-Time Compensation Input 2 to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

|          | 10110101 = Input tied to RPI181                                                                                                                         |

|          | •                                                                                                                                                       |

|          | •                                                                                                                                                       |

|          | •                                                                                                                                                       |

|          | 00000001 = Input tied to CMP1                                                                                                                           |

|          | 00000000 = Input tied to Vss                                                                                                                            |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| _     | —   | RP120R5 <sup>(1)</sup> | RP120R4 <sup>(1)</sup> | RP120R3 <sup>(1)</sup> | RP120R2 <sup>(1)</sup> | RP120R1 <sup>(1)</sup> | RP120R0 <sup>(1)</sup> |

| bit 7 |     |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | <b>RP176R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP176 Output Pin bits (see Table 11-3 for peripheral function numbers) |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0  | RP120R<5:0>: Peripheral Output Function is Assigned to RP120 Output Pin bits <sup>(1)</sup>                                                |

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-29: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0    | U-0                               | R/W-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0 | R/W-0 |

|--------|-----------------------------------|-------|---------|---------|---------|-------|-------|

| —      | — RP178R5 RP178R4 RP178R3 RP178R2 |       | RP178R2 | RP178R1 | RP178R0 |       |       |

| bit 15 |                                   |       |         |         |         |       | bit 8 |

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP177R5 | RP177R4 | RP177R3 | RP177R2 | RP177R1 | RP177R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP178R<5:0>:** Peripheral Output Function is Assigned to RP178 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP177R<5:0>:** Peripheral Output Function is Assigned to RP177 Output Pin bits (see Table 11-3 for peripheral function numbers)

Note 1: RP120R<5:0> is present in dsPIC33EVXXXGM006/106 devices only.

| U-0                                | U-0        | U-0            | U-0      | U-0                                | U-0   | U-0                | U-0   |  |  |

|------------------------------------|------------|----------------|----------|------------------------------------|-------|--------------------|-------|--|--|

| _                                  | —          | —              | _        | —                                  | —     | —                  | —     |  |  |

| bit 15                             |            |                |          |                                    |       |                    | bit 8 |  |  |

|                                    |            |                |          |                                    |       |                    |       |  |  |

| R/W-0                              | R/W-0      | R/W-0          | R/W-0    | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|                                    |            |                | STEP     | 2<7:0>                             |       |                    |       |  |  |

| bit 7                              |            |                |          |                                    |       |                    | bit 0 |  |  |

|                                    |            |                |          |                                    |       |                    |       |  |  |

| Legend:                            |            |                |          |                                    |       |                    |       |  |  |

| R = Readable                       | e bit      | W = Writable   | bit      | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at POR '1' = Bit is set |            |                |          | '0' = Bit is cle                   | eared | x = Bit is unknown |       |  |  |

|                                    |            |                |          |                                    |       |                    |       |  |  |

| bit 15-8                           | Unimplemer | ted: Read as ' | 0'       |                                    |       |                    |       |  |  |

| bit 7-0                            | STEP2<7:0> | : DMT Clear Ti | mer bits |                                    |       |                    |       |  |  |

#### REGISTER 14-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if preceded by the correct

loading of the STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading the DMTCNTL/H register and observing the counter being reset. All Other

Write Patterns = Sets the BAD2 bit; the value of STEP1<7:0> will remain unchanged and the new value being written to STEP2<7:0> will be captured. These bits are cleared when a DMT Reset event occurs.

### REGISTER 22-20: CxRXMnSID: CANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER REGISTER (n = 0-2)

|                                                                      |                                          | •                                                                                      | •                               |                                         |                                                            |              |                |  |  |

|----------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|------------------------------------------------------------|--------------|----------------|--|--|

| R/W-x                                                                | R/W-x                                    | R/W-x                                                                                  | R/W-x                           | R/W-x                                   | R/W-x                                                      | R/W-x        | R/W-x          |  |  |

| SID10                                                                | SID9                                     | SID8                                                                                   | SID7                            | SID6                                    | SID5                                                       | SID4         | SID3           |  |  |

| bit 15                                                               |                                          |                                                                                        |                                 |                                         | •                                                          |              | bit 8          |  |  |

| R/W-x                                                                | R/W-x                                    | R/W-x                                                                                  | U-0                             | R/W-x                                   | U-0                                                        | R/W-x        | R/W-x          |  |  |

| SID2                                                                 | SID1                                     | SID0                                                                                   | _                               | MIDE                                    | _                                                          | EID17        | EID16          |  |  |

| bit 7                                                                |                                          |                                                                                        |                                 |                                         |                                                            |              | bit C          |  |  |

|                                                                      |                                          |                                                                                        |                                 |                                         |                                                            |              |                |  |  |

| Legend:                                                              |                                          |                                                                                        |                                 |                                         |                                                            |              |                |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                          |                                                                                        |                                 |                                         |                                                            |              |                |  |  |

| -n = Value at                                                        | POR                                      | '1' = Bit is set                                                                       | t                               | '0' = Bit is cleared x = Bit is unknown |                                                            |              |                |  |  |

| bit 15-5<br>bit 4                                                    | 1 = Includes<br>0 = Bit, SIDx,           | Standard Identi<br>bit, SIDx, in filto<br>, is a don't care<br>h <b>ted:</b> Read as ' | er comparisor<br>in filter comp |                                         |                                                            |              |                |  |  |

| bit 3                                                                | 1 = Matches<br>the filter<br>0 = Matches | either standard                                                                        | types (standa                   | address messa                           | address) that c<br>ge if filters match<br>/lessage SID/EII | n, i.e., if: | e EXIDE bit ir |  |  |

| bit 2                                                                | Unimplemer                               | nted: Read as                                                                          | 0'                              |                                         |                                                            |              |                |  |  |

| bit 1-0                                                              | 1 = Includes                             | Extended Ider<br>bit, EIDx, in filt<br>a, is a don't car                               | ter compariso                   |                                         |                                                            |              |                |  |  |

|                                                                      |                                          |                                                                                        |                                 |                                         |                                                            |              |                |  |  |

# REGISTER 22-21: CxRXMnEID: CANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | EID   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | EID   | <7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable b  | oit   | W = Writable     | bit   | U = Unimpler     | nented bit, rea | <b>d as</b> '0' |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0

- EID<15:0>: Extended Identifier bits

- 1 = Includes bit, EIDx, in filter comparison

- 0 = Bit, EIDx, is a don't care in filter comparison

| R/W-0          | U-0                                                                                  | R/W-0                                                                              | R/W-0                                       | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |

|----------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|------------------|----------------------------------------|----------------|-------|

| HLMS           | 0-0                                                                                  | OCEN                                                                               | OCNEN                                       | OBEN             | OBNEN                                  | OAEN           | OANEN |

|                |                                                                                      | OCEN                                                                               | OCINEIN                                     | OBEN             | OBNEN                                  | UAEN           |       |

| bit 15         |                                                                                      |                                                                                    |                                             |                  |                                        |                | bit 8 |

| R/W-0          | R/W-0                                                                                | R/W-0                                                                              | R/W-0                                       | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |

| NAGS           | PAGS                                                                                 | ACEN                                                                               | ACNEN                                       | ABEN             | ABNEN                                  | AAEN           | AANEN |

| bit 7          |                                                                                      |                                                                                    |                                             |                  |                                        |                | bit   |

|                |                                                                                      |                                                                                    |                                             |                  |                                        |                |       |

| Legend:        |                                                                                      |                                                                                    |                                             |                  |                                        |                |       |

| R = Readab     | le bit                                                                               | W = Writable                                                                       | bit                                         | U = Unimpler     | mented bit, read                       | <b>as</b> '0'  |       |

| -n = Value a   | t POR                                                                                | '1' = Bit is se                                                                    |                                             | '0' = Bit is cle | ared                                   | x = Bit is unk | nown  |

| bit 15         | 1 = The mask                                                                         | ing (blanking)                                                                     |                                             | event any asse   | rted ('0') compai<br>rted ('1') compai |                |       |

| bit 14         | Unimplemen                                                                           | ted: Read as                                                                       | '0'                                         |                  |                                        |                |       |

| bit 13         | OCEN: OR G                                                                           | ate C Input E                                                                      | nable bit                                   |                  |                                        |                |       |

|                |                                                                                      | nnected to OF<br>t connected to                                                    | <b>U</b>                                    |                  |                                        |                |       |

| bit 12         |                                                                                      |                                                                                    | nverted Enable                              | e bit            |                                        |                |       |

|                |                                                                                      | •                                                                                  | ed to OR gate                               |                  |                                        |                |       |

|                | 0 = Inverted I                                                                       | MCI is not con                                                                     | nected to OR g                              | ate              |                                        |                |       |

| bit 11         |                                                                                      | ate B Input Er                                                                     |                                             |                  |                                        |                |       |

|                |                                                                                      | nnected to OF<br>t connected to                                                    |                                             |                  |                                        |                |       |

| bit 10         |                                                                                      |                                                                                    | nverted Enable                              | e bit            |                                        |                |       |

|                |                                                                                      | •                                                                                  | ed to OR gate                               |                  |                                        |                |       |

|                |                                                                                      |                                                                                    | nected to OR g                              | ate              |                                        |                |       |

| bit 9          |                                                                                      | ate A Input Er                                                                     |                                             |                  |                                        |                |       |

|                |                                                                                      | nnected to OF                                                                      | •                                           |                  |                                        |                |       |

| h:+ 0          |                                                                                      | t connected to                                                                     | -                                           | , hit            |                                        |                |       |

| bit 8          |                                                                                      | •                                                                                  | nverted Enable<br>ed to OR gate             |                  |                                        |                |       |

|                |                                                                                      |                                                                                    | nected to OR g                              | ate              |                                        |                |       |

| bit 7          | NAGS: AND                                                                            | Gate Output li                                                                     | nverted Enable                              | bit              |                                        |                |       |

|                |                                                                                      |                                                                                    | cted to OR gate                             |                  |                                        |                |       |

|                |                                                                                      |                                                                                    |                                             | 0                |                                        |                |       |

| bit 6          | PAGS: AND                                                                            | Gate Output E                                                                      | nable bit                                   |                  |                                        |                |       |

| bit 6          |                                                                                      | Gate Output E<br>onnected to C                                                     |                                             |                  |                                        |                |       |

|                | 1 = ANDI is c<br>0 = ANDI is n                                                       | onnected to C<br>ot connected                                                      | R gate<br>o OR gate                         |                  |                                        |                |       |

| bit 6<br>bit 5 | 1 = ANDI is c<br>0 = ANDI is n<br><b>ACEN:</b> AND                                   | onnected to C<br>ot connected<br>Gate C Input F                                    | R gate<br>o OR gate<br>Enable bit           |                  |                                        |                |       |

|                | 1 = ANDI is c<br>0 = ANDI is n<br><b>ACEN:</b> AND<br>1 = MCI is co                  | onnected to C<br>ot connected                                                      | R gate<br>o OR gate<br>Enable bit<br>D gate |                  |                                        |                |       |

|                | 1 = ANDI is c<br>0 = ANDI is n<br><b>ACEN:</b> AND<br>1 = MCI is co<br>0 = MCI is no | onnected to C<br>ot connected<br>Gate C Input E<br>nnected to AN<br>t connected to | R gate<br>o OR gate<br>Enable bit<br>D gate | le bit           |                                        |                |       |

| DC CHARACT       | ERISTICS            |      | (unless oth | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |           |  |  |  |

|------------------|---------------------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|--|--|--|

| Parameter<br>No. | Typ. <sup>(2)</sup> | Max. | Units       | Units Conditions                                                                                                                                                                                                                                                                      |      |           |  |  |  |

| Idle Current (li | dle) <sup>(1)</sup> |      |             | ·                                                                                                                                                                                                                                                                                     |      |           |  |  |  |

| DC40d            | 1.25                | 2    | mA          | -40°C                                                                                                                                                                                                                                                                                 |      | 10 MIPS   |  |  |  |

| DC40a            | 1.25                | 2    | mA          | +25°C                                                                                                                                                                                                                                                                                 | 5.01 |           |  |  |  |

| DC40b            | 1.5                 | 2.6  | mA          | +85°C                                                                                                                                                                                                                                                                                 | 5.0V |           |  |  |  |

| DC40c            | 1.5                 | 2.6  | mA          | +125°C                                                                                                                                                                                                                                                                                |      |           |  |  |  |

| DC42d            | 2.3                 | 3    | mA          | -40°C                                                                                                                                                                                                                                                                                 |      |           |  |  |  |

| DC42a            | 2.3                 | 3    | mA          | +25°C                                                                                                                                                                                                                                                                                 | 5.0V | 20 MIPS   |  |  |  |

| DC42b            | 2.6                 | 3.45 | mA          | +85°C                                                                                                                                                                                                                                                                                 | 5.00 | 20 1011-5 |  |  |  |

| DC42c            | 2.6                 | 3.85 | mA          | +125°C                                                                                                                                                                                                                                                                                | -    |           |  |  |  |

| DC44d            | 6.9                 | 8    | mA          | -40°C                                                                                                                                                                                                                                                                                 |      | 70 MIPS   |  |  |  |

| DC44a            | 6.9                 | 8    | mA          | +25°C                                                                                                                                                                                                                                                                                 | 5.0V |           |  |  |  |

| DC44b            | 7.25                | 8.6  | mA          | +85°C                                                                                                                                                                                                                                                                                 |      |           |  |  |  |

#### TABLE 30-7: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Base Idle current (IIDLE) is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- The NVMSIDL bit (NVMCON<12>) = 1 (i.e., Flash regulator is set to standby while the device is in Idle mode)

- The VREGSF bit (RCON<11>) = 0 (i.e., Flash regulator is set to standby while the device is in Sleep mode)

- 2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

# dsPIC33EVXXXGM00X/10X FAMILY

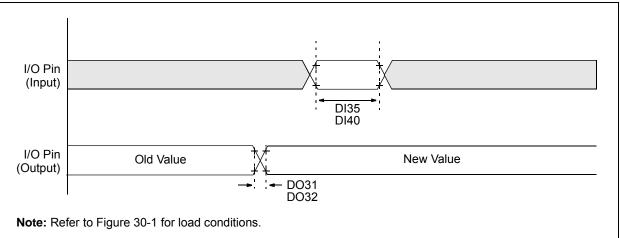

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |            |  |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                                                                                                                                                                                                                                              | Тур. <sup>(1)</sup> | Max. | Units | Conditions |  |

| DO31               | TioR   | Port Output Rise Time             | _                                                                                                                                                                                                                                                                                 | 5                   | 10   | ns    |            |  |