Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm004-h-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Timers/Output Compare/Input Capture**

- Nine General Purpose Timers:

- Five 16-bit and up to two 32-bit timers/counters; Timer3 can provide ADC trigger

- Four Output Compare modules Configurable as Timers/Counters

- Four Input Capture modules

## **Communication Interfaces**

- Two Enhanced Addressable Universal Asynchronous Receiver/Transmitter (UART) modules (6.25 Mbps):

- With support for LIN/J2602 bus and IrDA®

- High and low speed (SCI)

- Two SPI modules (15 Mbps):

- 25 Mbps data rate without using PPS

- One I<sup>2</sup>C module (up to 1 Mbaud) with SMBus Support

- Two SENT J2716 (Single-Edge Nibble Transmission-Transmit/Receive) module for Automotive Applications

- One CAN module:

- 32 buffers, 16 filters and three masks

## **Direct Memory Access (DMA)**

- 4-Channel DMA with User-Selectable Priority Arbitration

- UART, Serial Peripheral Interface (SPI), ADC, Input Capture, Output Compare and Controller Area Network (CAN)

## Input/Output

- GPIO Registers to Support Selectable Slew Rate I/Os

- Peripheral Pin Select (PPS) to allow Function Remap

- Sink/Source: 8 mA or 12 mA, Pin-Specific for Standard VOH/VOL

- · Selectable Open-Drain, Pull-ups and Pull-Downs

- Change Notice Interrupts on All I/O Pins

## **Qualification and Class B Support**

- AEC-Q100 REVG (Grade 1: -40°C to +125°C) Compliant

- AEC-Q100 REVG (Grade 0: -40°C to +150°C) Compliant

- Class B Safety Library, IEC 60730

## **Class B Fault Handling Support**

- Backup FRC

- · Windowed WDT uses LPRC

- Windowed Deadman Timer (DMT) uses System Clock (System Windowed Watchdog Timer)

- H/W Clock Monitor Circuit

- Oscillator Frequency Monitoring through CTMU (OSCI, SYSCLK, FRC, BFRC, LPRC)

- Dedicated PWM Fault Pin

- Lockable Clock Configuration

## **Debugger Development Support**

- In-Circuit and In-Application Programming

- Three Complex and Five Simple Breakpoints

- Trace and Run-Time Watch

## TABLE 4-17: PERIPHERAL INPUT REMAP REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---------------|

| RPINR0      | 06A0  |          |          |          | INT1F    | R<7:0>   |          |          |          |          |          | —        | -        | _        | _        |          | —        | 0000          |

| RPINR1      | 06A2  | _        | _        | _        | _        | _        | _        | _        | _        |          |          |          | INT2R    | <7:0>    |          |          |          | 0000          |

| RPINR3      | 06A6  | _        | _        | _        | _        | _        | _        | _        | _        |          |          |          | T2CKF    | R<7:0>   |          |          |          | 0000          |

| RPINR7      | 06AE  | IC2R7    | IC2R6    | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | IC1R7    | IC1R6    | IC1R5    | IC1R4    | IC1R3    | IC1R2    | IC1R1    | IC1R0    | 0000          |

| RPINR8      | 06B0  | IC4R7    | IC4R6    | IC4R5    | IC4R4    | IC4R3    | IC4R2    | IC4R1    | IC4R0    | IC3R7    | IC3R6    | IC3R5    | IC3R4    | IC3R3    | IC3R2    | IC3R1    | IC3R0    | 0000          |

| RPINR11     | 06B6  | _        | _        | _        | _        | _        | _        | _        | _        |          |          |          | OCFA     | R<7:0>   |          |          |          | 0000          |

| RPINR12     | 06B8  | FLT2R7   | FLT2R6   | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7   | FLT1R6   | FLT1R5   | FLT1R4   | FLT1R3   | FLT1R2   | FLT1R1   | FLT1R0   | 0000          |

| RPINR18     | 06C4  | _        | _        | _        | _        | _        | _        | _        | _        |          |          |          | U1RXF    | R<7:0>   |          |          |          | 0000          |

| RPINR19     | 06C6  | _        | _        | _        | —        | _        | _        | _        | _        |          |          |          | U2RXF    | R<7:0>   |          |          |          | 0000          |

| RPINR22     | 06CC  | SCK2R7   | SCK2R6   | SCK2R5   | SCK2R4   | SCK2R3   | SCK2R2   | SCK2R1   | SCK2R0   | SDI2R7   | SDI2R6   | SDI2R5   | SDI2R4   | SDI2R3   | SDI2R2   | SDI2R1   | SDI2R0   | 0000          |

| RPINR23     | 06CE  | _        | _        | _        | _        | _        | _        | _        | _        |          |          |          | SS2R     | <7:0>    |          |          |          | 0000          |

| RPINR26     | 06D4  | _        | _        | _        | _        | _        | _        | _        | _        |          |          |          | C1RXR    | <7:0>(1) |          |          |          | 0000          |

| RPINR37     | 06EA  |          |          |          | SYNCI    | IR<7:0>  |          |          |          | _        | —        | —        | _        | _        | _        | _        | _        | 0000          |

| RPINR38     | 06EC  |          |          |          | DTCMP    | 1R<7:0>  |          |          |          |          | -        | _        | _        | _        | _        |          | _        | 0000          |

| RPINR39     | 06EE  | DTCMP3R7 | DTCMP3R6 | DTCMP3R5 | DTCMP3R4 | DTCMP3R3 | DTCMP3R2 | DTCMP3R1 | DTCMP3R0 | DTCMP2R7 | DTCMP2R6 | DTCMP2R5 | DTCMP2R4 | DTCMP2R3 | DTCMP2R2 | DTCMP2R1 | DTCMP2R0 | 0000          |

| RPINR44     | 06F8  |          |          |          | SENT1    | R<7:0>   |          |          |          |          | -        | —        | —        | —        | _        |          | —        | 0000          |

| RPINR45     | 06FA  | _        | _        | _        | —        | —        | _        | _        | —        |          |          | •        | SENT2    | R<7:0>   |          |          | •        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

#### TABLE 4-18: DMT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15           | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-------------|-------|------------------|-----------------|--------|--------|--------|--------|-------|---------|---------|-------|----------|-------|-------|-------|-------|--------|---------------|

| DMTCON      | 0700  | ON               |                 | _      |        |        | -      | —     |         | _       | _     | —        | _     | —     |       | _     | —      | 0000          |

| DMTPRECLR   | 0704  |                  |                 |        | STEP1  | <7:0>  |        |       |         | _       | _     | _        | _     | _     | _     | _     | —      | 0000          |

| DMTCLR      | 0708  | _                | _               | _      | _      | _      | _      | _     | _       |         |       |          | STEP2 | <7:0> |       |       |        | 0000          |

| DMTSTAT     | 070C  | _                | _               | _      | _      | _      | _      | _     | _       | BAD1    | BAD2  | DMTEVENT |       | _     | _     | _     | WINOPN | 0000          |

| DMTCNTL     | 0710  |                  |                 |        |        |        |        |       | COUNTER | <15:0>  |       |          |       |       |       |       |        | 0000          |

| DMTCNTH     | 0712  |                  |                 |        |        |        |        | (     | COUNTER | <31:16> |       |          |       |       |       |       |        | 0000          |

| DMTHOLDREG  | 0714  |                  |                 |        |        |        |        |       | UPRCNT  | <15:0>  |       |          |       |       |       |       |        | 0000          |

| DMTPSCNTL   | 0718  |                  |                 |        |        |        |        |       | PSCNT<  | 15:0>   |       |          |       |       |       |       |        | 0000          |

| DMTPSCNTH   | 071A  |                  |                 |        |        |        |        |       | PSCNT<  | 31:16>  |       |          |       |       |       |       |        | 0000          |

| DMTPSINTVL  | 071C  |                  | PSINTV<15:0> 00 |        |        |        |        |       |         |         |       | 0000     |       |       |       |       |        |               |

| DMTPSINTVH  | 071E  | PSINTV<31:16> 00 |                 |        |        |        |        |       |         |         | 0000  |          |       |       |       |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-39: PORTD REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD       | 0E3C  | —      | —      | _      |        |        | —      |       | TRISD8 | _     | TRISE | 0<6:5> |       |       | _     |       |       | 0160          |

| PORTD       | 0E3E  | _      | _      | _      |        |        | —      |       | RD8    | _     | RD<   | :6:5>  |       |       | _     | _     |       | xxxx          |

| LATD        | 0E40  | _      | _      | _      |        |        | —      |       | LATD8  | _     | LATD  | <6:5>  |       |       | _     | _     |       | xxxx          |

| ODCD        | 0E42  |        | _      | _      |        |        | —      |       | ODCD8  | —     | ODCE  | )<6:5> |       |       | _     |       |       | 0000          |

| CNEND       | 0E44  |        | _      | _      |        |        | —      |       | CNIED8 | —     | CNIED | 0<6:5> |       |       | _     |       |       | 0000          |

| CNPUD       | 0E46  |        | _      | _      |        |        | —      |       | CNPUD8 | —     | CNPU  | D<6:5> |       |       | _     |       |       | 0000          |

| CNPDD       | 0E48  | —      | _      | _      |        |        | -      |       | CNPDD8 | _     | CNPDI | D<6:5> |       |       |       |       |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-40: PORTE REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE       | 0E50  |        | TRISE  | <15:12> |        | —      | —      |       | —     | —     | —     | _     | -     | -     | -     | —     |       | F000          |

| PORTE       | 0E52  |        | RE<1   | 5:12>   |        | _      | _      | _     | _     | _     | _     |       | _     | _     | _     | _     | _     | xxxx          |

| LATE        | 0E54  |        | LATE<  | :15:12> |        | _      | _      | _     | _     | _     | _     |       | _     | _     | _     | _     | _     | xxxx          |

| ODCE        | 0E56  |        | ODCE.  | <15:12> |        | _      | _      | _     | _     | _     | _     |       | _     | _     | _     | _     | _     | 0000          |

| CNENE       | 0E58  |        | CNIEE  | <15:12> |        | —      | —      |       | —     | —     | _     | _     |       |       |       | _     | _     | 0000          |

| CNPUE       | 0E5A  |        | CNPUE  | <15:12> |        | _      | _      | _     | _     | _     | _     |       | _     | _     | _     | _     | _     | 0000          |

| CNPDE       | 0E5C  |        | CNPDE  | <15:12> |        | —      | —      |       | —     | —     | _     | _     | _     | _     |       | _     | _     | 0000          |

| ANSELE      | 0E5E  |        | ANSE<  | <15:12> |        | _      | —      |       | _     | —     | _     | _     | -     | -     |       | _     | _     | F000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

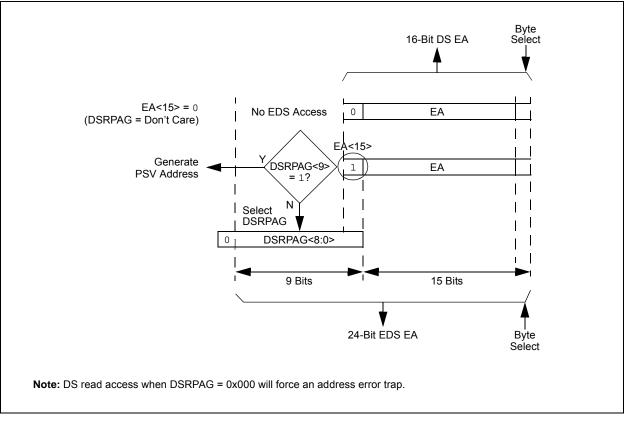

### 4.3.1 PAGED MEMORY SCHEME

The dsPIC33EVXXXGM00X/10X family architecture extends the available DS through a paging scheme, which allows the available DS to be accessed using MOV instructions in a linear fashion for pre- and post-modified Effective Addresses (EAs). The upper half of the Base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Data Space Read Page register (DSRPAG) or the 9-bit Data Space Write Page register (DSWPAG), to form an EDS address, or Program Space Visibility (PSV) address.

The Data Space Page registers are located in the SFR space. Construction of the EDS address is shown in Figure 4-9 and Figure 4-10. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS write address.

#### FIGURE 4-9: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### TABLE 4-45: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| For the MOV instructions, the addressing      |

|-----------------------------------------------|

| mode specified in the instruction can differ  |

| for the source and destination EA. How-       |

| ever, the 4-bit Wb (Register Offset) field is |

| shared by both source and destination         |

| (but typically only used by one).             |

|                                               |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set, {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X Data Space) and W11 (in Y Data Space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (Branch) instructions use 16-bit signed literals to specify the Branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| U-0                                                                        | U-0                                                            | U-0                                                                                                                                                                | U-0          | U-0                 | U-0    | U-0    | U-0    |  |  |  |  |  |

|----------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|--------|--------|--------|--|--|--|--|--|

| —                                                                          |                                                                | _                                                                                                                                                                  | —            | —                   | _      |        | —      |  |  |  |  |  |

| bit 15                                                                     |                                                                |                                                                                                                                                                    |              |                     |        |        | bit 8  |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

| U-0                                                                        | U-0                                                            | U-0                                                                                                                                                                | U-0          | R-0                 | R-0    | R-0    | R-0    |  |  |  |  |  |

| _                                                                          |                                                                |                                                                                                                                                                    | —            | RQCOL3              | RQCOL2 | RQCOL1 | RQCOL0 |  |  |  |  |  |

| bit 7                                                                      |                                                                |                                                                                                                                                                    |              |                     |        |        | bit 0  |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

| Legend:                                                                    |                                                                |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

| R = Readab                                                                 | Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                                |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

| bit 15-4                                                                   | Unimplemer                                                     | nted: Read as '                                                                                                                                                    | 0'           |                     |        |        |        |  |  |  |  |  |

| bit 3                                                                      | RQCOL3: Cl                                                     | nannel 3 Transfe                                                                                                                                                   | er Request C | Collision Flag bit  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              | est collision is d  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                | •                                                                                                                                                                  | •            | est collision is n  |        |        |        |  |  |  |  |  |

| bit 2                                                                      |                                                                |                                                                                                                                                                    | •            | Collision Flag bit  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              | est collision is de |        |        |        |  |  |  |  |  |

| L:1.4                                                                      |                                                                | •                                                                                                                                                                  |              | est collision is no |        |        |        |  |  |  |  |  |

| bit 1                                                                      |                                                                |                                                                                                                                                                    | •            | Collision Flag bit  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                | <ul> <li>1 = User force and interrupt-based request collision is detected</li> <li>0 = User force and interrupt-based request collision is not detected</li> </ul> |              |                     |        |        |        |  |  |  |  |  |

| bit 0                                                                      |                                                                | •                                                                                                                                                                  | •            | collision Flag bit  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    | •            | est collision is d  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              | est collision is n  |        |        |        |  |  |  |  |  |

|                                                                            |                                                                |                                                                                                                                                                    |              |                     |        |        |        |  |  |  |  |  |

### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

## 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

## 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP43R5 | RP43R4 | RP43R3 | RP43R2 | RP43R1 | RP43R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP42R5 | RP42R4 | RP42R3 | RP42R2 | RP42R1 | RP42R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

## REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP49R5 | RP49R4 | RP49R3 | RP49R2 | RP49R1 | RP49R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | —   | RP48R5 | RP48R4 | RP48R3 | RP48R2 | RP48R1 | RP48R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                      |

|-------------------|------------------|-----------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , <b>read as</b> '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown   |

bit 15-14 Unimplemented: Read as '0'

bit 13-8**RP49R<5:0>:** Peripheral Output Function is Assigned to RP49 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP48R<5:0>:** Peripheral Output Function is Assigned to RP48 Output Pin bits

(see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

## 12.1 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0                                                                                                                                         | R/W-0                          | U-0            | U-0              | U-0                       | U-0                | U-0         |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|------------------|---------------------------|--------------------|-------------|--|--|

| TON <sup>(1)</sup> | —                                                                                                                                           | TSIDL                          | —              | —                | _                         | —                  | —           |  |  |

| bit 15             |                                                                                                                                             |                                |                |                  |                           |                    | bit 8       |  |  |

|                    |                                                                                                                                             |                                |                |                  |                           |                    |             |  |  |

| U-0                | R/W-0                                                                                                                                       | R/W-0                          | R/W-0          | U-0              | R/W-0                     | R/W-0              | U-0         |  |  |

|                    | TGATE                                                                                                                                       | TCKPS1                         | TCKPS0         | —                | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |  |  |

| bit 7              |                                                                                                                                             |                                |                |                  |                           |                    | bit 0       |  |  |

|                    |                                                                                                                                             |                                |                |                  |                           |                    |             |  |  |

| Legend:            |                                                                                                                                             |                                |                |                  |                           |                    |             |  |  |

| R = Readable       |                                                                                                                                             | W = Writable                   |                | -                | mented bit, read          |                    |             |  |  |

| -n = Value at F    | POR                                                                                                                                         | '1' = Bit is set               |                | '0' = Bit is cle | ared                      | x = Bit is unkr    | nown        |  |  |

|                    |                                                                                                                                             | o                              |                |                  |                           |                    |             |  |  |

| bit 15             | TON: Timer1                                                                                                                                 |                                |                |                  |                           |                    |             |  |  |

|                    | 1 = Starts 16-<br>0 = Stops 16-                                                                                                             |                                |                |                  |                           |                    |             |  |  |

| bit 14             | •                                                                                                                                           | ted: Read as '                 | י)             |                  |                           |                    |             |  |  |

| bit 13             | -                                                                                                                                           | 1 Stop in Idle N               |                |                  |                           |                    |             |  |  |

| 2.1.10             |                                                                                                                                             |                                |                | he device ente   | ers Idle mode             |                    |             |  |  |

|                    | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul> |                                |                |                  |                           |                    |             |  |  |

| bit 12-7           | Unimplemen                                                                                                                                  | ted: Read as '                 | כי             |                  |                           |                    |             |  |  |

| bit 6              | TGATE: Time                                                                                                                                 | r1 Gated Time                  | Accumulation   | Enable bit       |                           |                    |             |  |  |

|                    | When TCS =<br>This bit is igno                                                                                                              |                                |                |                  |                           |                    |             |  |  |

|                    | When TCS =                                                                                                                                  |                                |                |                  |                           |                    |             |  |  |

|                    |                                                                                                                                             | e accumulation                 |                |                  |                           |                    |             |  |  |

| bit 5-4            |                                                                                                                                             | e accumulation                 |                | a Salaat hita    |                           |                    |             |  |  |

| DIL 3-4            | 11 = 1:256                                                                                                                                  | : Timer1 Input                 |                |                  |                           |                    |             |  |  |

|                    | 10 = 1:64                                                                                                                                   |                                |                |                  |                           |                    |             |  |  |

|                    | 01 = 1:8                                                                                                                                    |                                |                |                  |                           |                    |             |  |  |

|                    | 00 = 1:1                                                                                                                                    |                                |                |                  |                           |                    |             |  |  |

| bit 3              | -                                                                                                                                           | ted: Read as '                 |                |                  | (1)                       |                    |             |  |  |

| bit 2              |                                                                                                                                             | er1 External Clo               | ock Input Synd | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |  |  |

|                    | <u>When TCS =</u><br>1 = External c                                                                                                         |                                | nchronized     |                  |                           |                    |             |  |  |

|                    | 1 = External clock input is synchronized<br>0 = External clock input is not synchronized                                                    |                                |                |                  |                           |                    |             |  |  |

|                    | When TCS =                                                                                                                                  | =                              | ,              |                  |                           |                    |             |  |  |

|                    | This bit is igno                                                                                                                            |                                |                |                  |                           |                    |             |  |  |

| bit 1              |                                                                                                                                             | Clock Source S                 |                |                  |                           |                    |             |  |  |

|                    | 1 = External c<br>0 = Internal cl                                                                                                           | clock is from pii<br>lock (FP) | n, T1CK (on th | ne rising edge)  |                           |                    |             |  |  |

| bit 0              | Unimplemen                                                                                                                                  | ted: Read as '                 | כי             |                  |                           |                    |             |  |  |

|                    | en Timer1 is en<br>mpts by user se                                                                                                          |                                |                |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |  |  |

| U-0           | U-0                                                                                                                                                                                                                   | U-0                            | U-0             | U-0              | U-0            | U-0              | U-0    |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|------------------|----------------|------------------|--------|

| _             | —                                                                                                                                                                                                                     | _                              | —               | —                | —              |                  | —      |

| bit 15        |                                                                                                                                                                                                                       |                                |                 |                  |                |                  | bit 8  |

|               |                                                                                                                                                                                                                       |                                |                 |                  |                |                  |        |

| R-0, HC       | R-0, HC                                                                                                                                                                                                               | R-0, HC                        | U-0             | U-0              | U-0            | U-0              | R-0    |

| BAD1          | BAD2                                                                                                                                                                                                                  | DMTEVENT                       |                 | —                | _              |                  | WINOPN |

| bit 7         |                                                                                                                                                                                                                       |                                |                 |                  |                |                  | bit 0  |

|               |                                                                                                                                                                                                                       |                                |                 |                  |                |                  |        |

| Legend:       |                                                                                                                                                                                                                       | HC = Hardwar                   | e Clearable bit |                  |                |                  |        |

| R = Readable  | e bit                                                                                                                                                                                                                 | W = Writable b                 | it              | U = Unimple      | mented bit, re | <b>ad as</b> '0' |        |

| -n = Value at | POR                                                                                                                                                                                                                   | '1' = Bit is set               |                 | '0' = Bit is cle | eared          | x = Bit is unk   | nown   |

| bit 15-8      | Unimplemer                                                                                                                                                                                                            | nted: Read as '0               | 3               |                  |                |                  |        |

| bit 7         | BAD1: Dead                                                                                                                                                                                                            | man Timer Bad                  | STEP1<7:0> V    | alue Detect bit  |                |                  |        |

|               |                                                                                                                                                                                                                       | STEP1<7:0> va<br>STEP1<7:0> va |                 |                  |                |                  |        |

| bit 6         | BAD2: Dead                                                                                                                                                                                                            | man Timer Bad                  | STEP2<7:0> V    | alue Detect bit  |                |                  |        |

|               |                                                                                                                                                                                                                       | STEP2<7:0> va<br>STEP2<7:0> va |                 |                  |                |                  |        |

| bit 5         | DMTEVENT:                                                                                                                                                                                                             | Deadman Time                   | r Event bit     |                  |                |                  |        |

|               | <ul> <li>1 = Deadman Timer event was detected (counter expired, or bad STEP1&lt;7:0&gt; or STEP2&lt;7:0&gt; valu was entered prior to counter increment)</li> <li>0 = Deadman Timer event was not detected</li> </ul> |                                |                 |                  |                |                  |        |

| bit 4-1       |                                                                                                                                                                                                                       | nted: Read as '0               |                 | I                |                |                  |        |

| bit 0         | -                                                                                                                                                                                                                     | adman Timer C                  |                 | ŀ                |                |                  |        |

| Sit 0         | 1 = Deadmar                                                                                                                                                                                                           | n Timer clear wir              | ndow is open    | -                |                |                  |        |

|               |                                                                                                                                                                                                                       | n Timer clear wir              | nor obe         | 11               |                |                  |        |

### REGISTER 14-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

## 15.1 Input Capture Control Registers

## REGISTER 15-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER     | 15-1: ICxCO                                                                           | N1: INPUT C                                                                                                                                              | CAPTURE x CO                            | ONTROL REG           | ISTER 1          |                 |              |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|------------------|-----------------|--------------|--|--|--|--|--|

| U-0          | U-0                                                                                   | R/W-0                                                                                                                                                    | R/W-0                                   | R/W-0                | R/W-0            | U-0             | U-0          |  |  |  |  |  |

| _            |                                                                                       | ICSIDL                                                                                                                                                   | ICTSEL2                                 | ICTSEL1              | ICTSEL0          | —               | _            |  |  |  |  |  |

| bit 15       |                                                                                       | •                                                                                                                                                        |                                         |                      |                  |                 | bit          |  |  |  |  |  |

| U-0          | R/W-0                                                                                 | R/W-0                                                                                                                                                    | R-0, HC, HS                             | R-0, HC, HS          | R/W-0            | R/W-0           | R/W-0        |  |  |  |  |  |

| _            | ICI1                                                                                  | ICI0                                                                                                                                                     | ICOV                                    | ICBNE                | ICM2             | ICM1            | ICM0         |  |  |  |  |  |

| bit 7        |                                                                                       |                                                                                                                                                          |                                         |                      |                  |                 | bit          |  |  |  |  |  |

| Legend:      |                                                                                       | HC = Hardwa                                                                                                                                              | re Clearable bit                        | HS = Hardwar         | re Settable bit  |                 |              |  |  |  |  |  |

| R = Readab   | le bit                                                                                | W = Writable                                                                                                                                             | bit                                     | U = Unimplem         | nented bit, read | <b>l as</b> '0' |              |  |  |  |  |  |

| -n = Value a | t POR                                                                                 | '1' = Bit is set                                                                                                                                         |                                         | '0' = Bit is clea    | ared             | x = Bit is un   | known        |  |  |  |  |  |

| bit 15-14    | Unimplemen                                                                            | ted: Read as '                                                                                                                                           | 0'                                      |                      |                  |                 |              |  |  |  |  |  |

| bit 13       | -                                                                                     |                                                                                                                                                          | p in Idle Mode C                        | control bit          |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | -                                                                                                                                                        | t in CPU Idle mod                       |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | -                                                                                                                                                        | tinue to operate                        |                      | de               |                 |              |  |  |  |  |  |

| bit 12-10    |                                                                                       |                                                                                                                                                          | e x Timer Select                        |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | is the clock sour                       | ce of the ICx        |                  |                 |              |  |  |  |  |  |

|              | 110 = Reserv                                                                          |                                                                                                                                                          |                                         |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | 101 = Reserved<br>100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)                                                   |                                         |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | 011 = T5CLK is the clock source of the ICx                                                                                                               |                                         |                      |                  |                 |              |  |  |  |  |  |

|              | 010 = T4CLK is the clock source of the ICx                                            |                                                                                                                                                          |                                         |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | ource of the ICx                        |                      |                  |                 |              |  |  |  |  |  |

| bit 9-7      |                                                                                       | ted: Read as '                                                                                                                                           |                                         |                      |                  |                 |              |  |  |  |  |  |

| bit 6-5      | ICI<1:0>: Nur                                                                         | mber of Captur                                                                                                                                           | es per Interrupt S                      | Select bits (this fi | eld is not used  | if ICM<2:0> =   | 001 or 111   |  |  |  |  |  |

|              | 11 = Interrupt                                                                        | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)<br>11 = Interrupt on every fourth capture event |                                         |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | 10 = Interrupt on every third capture event                                                                                                              |                                         |                      |                  |                 |              |  |  |  |  |  |

|              | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event |                                                                                                                                                          |                                         |                      |                  |                 |              |  |  |  |  |  |

|              | -                                                                                     |                                                                                                                                                          |                                         |                      |                  |                 |              |  |  |  |  |  |

| bit 4        | -                                                                                     | -                                                                                                                                                        | flow Status Flag                        |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | overflow has occu                       |                      |                  |                 |              |  |  |  |  |  |

| bit 3        |                                                                                       | -                                                                                                                                                        | fer Not Empty St                        |                      | nlv)             |                 |              |  |  |  |  |  |

|              | -                                                                                     | -                                                                                                                                                        | s not empty, at le                      | -                    | • •              | an be read      |              |  |  |  |  |  |

|              |                                                                                       | pture x buffer i                                                                                                                                         |                                         |                      |                  |                 |              |  |  |  |  |  |

| bit 2-0      | ICM<2:0>: In                                                                          | put Capture x                                                                                                                                            | Mode Select bits                        |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | tions as an inter                       |                      | CPU Sleep an     | d Idle modes    | (rising edg  |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | control bits are r                      | ot applicable)       |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | ed (module is d                                                                                                                                          | ,                                       |                      | nturo modo)      |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | / 16th rising edge<br>/ 4th rising edge |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | / rising edge (Sir                      |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       |                                                                                                                                                          | / falling edge (Si                      |                      |                  |                 |              |  |  |  |  |  |

|              |                                                                                       | re mode, every                                                                                                                                           | edge, rising and                        |                      |                  | CI<1:0>) is not | t used in th |  |  |  |  |  |

|              | ,                                                                                     |                                                                                                                                                          | ule is turned off                       |                      |                  |                 |              |  |  |  |  |  |

000 = Input Capture x module is turned off

### REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>S: I2Cx Start bit</li> <li>Updated when Start, Reset or Stop is detected; cleared when the I<sup>2</sup>C module is disabled, I2CEN = 0.</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Indicates that a Start bit was not detected last</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                             |

|       | <ul> <li>1 = Read: Indicates that the data transfer is output from the slave</li> <li>0 = Write: Indicates that the data transfer is input to the slave</li> </ul>                                                                                                                                            |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                                                           |

|       | 1 = Receive is complete, the I2CxRCV bit is full                                                                                                                                                                                                                                                              |

|       | 0 = Receive is not complete, the I2CxRCV bit is empty                                                                                                                                                                                                                                                         |