Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm102-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

# 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

# 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

# 3.3 Data Space Addressing

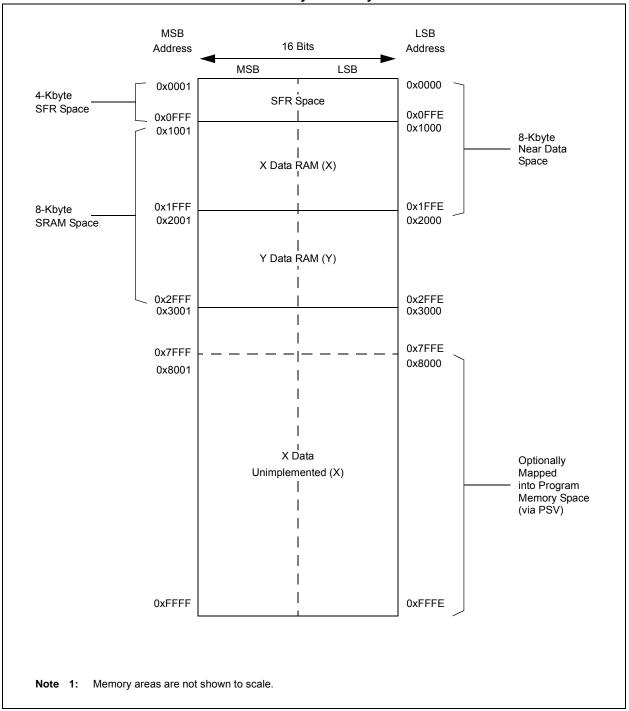

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

# 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

# FIGURE 4-7: DATA MEMORY MAP FOR 64-Kbyte/128-Kbyte DEVICES<sup>(1)</sup>

| IABLE       | 4-16: | PER    | PHERA  | L PIN S | ELECI   | OUIPU   | I REGIS |         | AP FOR  | dsPIC | 33EV) | XXXGMU  | 06/106 L | DEVICES | 5       |         |         |               |

|-------------|-------|--------|--------|---------|---------|---------|---------|---------|---------|-------|-------|---------|----------|---------|---------|---------|---------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5   | Bit 4    | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

| RPOR0       | 0670  | _      | _      | RP35R5  | RP35R4  | RP35R3  | RP35R2  | RP35R1  | RP35R0  | —     | —     | RP20R5  | RP20R4   | RP20R3  | RP20R2  | RP20R1  | RP20R0  | 0000          |

| RPOR1       | 0672  | _      | _      | RP37R5  | RP37R4  | RP37R3  | RP37R2  | RP37R1  | RP37R0  | _     | _     | RP36R5  | RP36R4   | RP36R3  | RP36R2  | RP36R1  | RP36R0  | 0000          |

| RPOR2       | 0674  | _      | _      | RP39R5  | RP39R4  | RP39R3  | RP39R2  | RP39R1  | RP39R0  | _     | _     | RP38R5  | RP38R4   | RP38R3  | RP38R2  | RP38R1  | RP38R0  | 0000          |

| RPOR3       | 0676  | _      | _      | RP41R5  | RP41R4  | RP41R3  | RP41R2  | RP41R1  | RP41R0  | _     | _     | RP40R5  | RP40R4   | RP40R3  | RP40R2  | RP40R1  | RP40R0  | 0000          |

| RPOR4       | 0678  | —      | _      | RP43R5  | RP43R4  | RP43R3  | RP43R2  | RP43R1  | RP43R0  | _     |       | RP42R5  | RP42R4   | RP42R3  | RP42R2  | RP42R1  | RP42R0  | 0000          |

| RPOR5       | 067A  | —      | _      | RP49R5  | RP49R4  | RP49R3  | RP49R2  | RP49R1  | RP49R0  | _     |       | RP48R5  | RP48R4   | RP48R3  | RP48R2  | RP48R1  | RP48R0  | 0000          |

| RPOR6       | 067C  | —      | _      | RP55R5  | RP55R4  | RP55R3  | RP55R2  | RP55R1  | RP55R0  | _     |       | RP54R5  | RP54R4   | RP54R3  | RP54R2  | RP54R1  | RP54R0  | 0000          |

| RPOR7       | 067E  | —      | _      | RP57R5  | RP57R4  | RP57R3  | RP57R2  | RP57R1  | RP57R0  | _     |       | RP56R5  | RP56R4   | RP56R3  | RP56R2  | RP56R1  | RP56R0  | 0000          |

| RPOR8       | 0680  | —      | _      | RP70R5  | RP70R4  | RP70R3  | RP70R2  | RP70R1  | RP70R0  | _     |       | RP69R5  | RP69R4   | RP69R3  | RP69R2  | RP69R1  | RP69R0  | 0000          |

| RPOR9       | 0682  | —      | _      | RP118R5 | RP118R4 | RP118R3 | RP118R2 | RP118R1 | RP118R0 | _     |       | RP97R5  | RP97R4   | RP97R3  | RP97R2  | RP97R1  | RP97R0  | 0000          |

| RPOR10      | 0684  | —      | _      | RP176R5 | RP176R4 | RP176R3 | RP176R2 | RP176R1 | RP176R0 | _     |       | RP120R5 | RP120R4  | RP120R3 | RP120R2 | RP120R1 | RP120R0 | 0000          |

| RPOR11      | 0686  | _      | _      | RP178R5 | RP178R4 | RP178R3 | RP178R2 | RP178R1 | RP178R0 | _     |       | RP177R5 | RP177R4  | RP177R3 | RP177R2 | RP177R1 | RP177R0 | 0000          |

| RPOR12      | 0688  | —      | _      | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 | —     |       | RP179R5 | RP179R4  | RP179R3 | RP179R2 | RP179R1 | RP179R0 | 0000          |

| RPOR13      | 068A  | —      | _      | _       | —       | _       | —       | _       | _       | —     |       |         |          | RP181   | R<5:0>  |         |         | 0000          |

#### TABLE 4-16: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EVXXXGM006/106 DEVICES

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: DMAC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6    | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|---------|----------|---------|---------|---------|---------|---------|---------|---------------|

| DMA0CON     | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _     | —       | _        | AMODE1  | AMODE0  | —       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ     | 0B02  | FORCE  | _      | _      | _      | _      | _      | -     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA0STAL    | 0B04  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STAH    | 0B06  | _      | _      | _      | _      | _      |        |       |       |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA0STBL    | 0B08  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STBH    | 0B0A  | _      | _      | —      | _      | _      |        | _     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA0PAD     | 0B0C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0CNT     | 0B0E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA1CON     | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA1REQ     | 0B12  | FORCE  | —      | —      | _      |        | -      | —     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA1STAL    | 0B14  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STAH    | 0B16  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA1STBL    | 0B18  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STBH    | 0B1A  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA1PAD     | 0B1C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1CNT     | 0B1E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA2CON     | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA2REQ     | 0B22  | FORCE  | —      | _      | —      | —      | —      | _     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA2STAL    | 0B24  |        |        |        | -      |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STAH    | 0B26  | —      | —      |        | _      |        | —      | —     | —     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA2STBL    | 0B28  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STBH    | 0B2A  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA2PAD     | 0B2C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2CNT     | 0B2E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA3CON     | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA3REQ     | 0B32  | FORCE  | —      | —      | _      |        | -      | —     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA3STAL    | 0B34  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STAH    | 0B36  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA3STBL    | 0B38  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STBH    | 0B3A  | —      | —      | _      |        | _      | _      | —     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA3PAD     | 0B3C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3CNT     | 0B3E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMAPWC      | 0BF0  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       |         |         | PWCC    | )L<3:0> |         | 0000          |

| DMARQC      | 0BF2  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       | _       |         | RQCC    | )L<3:0> |         | 0000          |

| DMAPPS      | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _     | _       | _        | _       | _       |         | PPS     | Г<3:0>  |         | 0000          |

dsPIC33EVXXXGM00X/10X FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in the data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configure the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address, prior to modification, addresses an EDS or a PSV page.

- The EA calculation uses Pre- or Post-Modified Register Indirect Addressing. However, this does not include Register Offset Addressing.

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using the Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-43 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when an overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

# TABLE 4-43: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS AND PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

| 0/11        |                     |                | Before       |                        |                | After        |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page Description       |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last Page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>Page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page |

| O,<br>Read  | <b>or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>Page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last Page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  | r 1                 | DSRPAG = 0x001 | 1            | PSV Page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>Page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ WII ]             | DSRPAG = 0x300 | 1            | PSV: First MSB<br>Page | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>Page  |

Legend: O = Overflow, U = Underflow, R = Read, W = Write

**Note 1:** The Register Indirect Addressing now addresses a location in the Base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

**3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

4: Pseudolinear Addressing is not supported for large offsets.

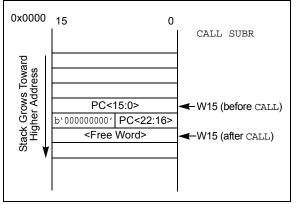

# 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the SSP (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EVXXXGM00X/10X family devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within the Data Space.

The SSP always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-14 illustrates how it predecrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-14. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register (SR). This allows the contents of SRL to be preserved automatically during interrupt processing.

- Note 1: To maintain system SSP (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment.

#### FIGURE 4-14:

#### CALL STACK FRAME

# 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-45 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

# 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

# 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where, Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

# 4.7 Interfacing Program and Data Memory Spaces

The dsPIC33EVXXXGM00X/10X family architecture uses a 24-bit wide Program Space and a 16-bit wide Data Space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both the spaces.

Aside from normal execution, the architecture of the dsPIC33EVXXXGM00X/10X family devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

Table 4-47 shows the construction of the Program Space address.

How the data is accessed from Program Space is shown in Figure 4-17.

| A                      | Access        | Program Space Address |            |          |               |     |  |  |  |  |

|------------------------|---------------|-----------------------|------------|----------|---------------|-----|--|--|--|--|

| Access Type            | Space         | <23>                  | <22:16>    | <15>     | <14:1>        | <0> |  |  |  |  |

| Instruction Access     | User          | 0                     |            | PC<22:1> |               | 0   |  |  |  |  |

| (Code Execution)       |               |                       | 0xx xxxx x | XXX XXXX | x xxxx xxx0   |     |  |  |  |  |

| TBLRD/TBLWT            | User          | TB                    | LPAG<7:0>  |          | Data EA<15:0> |     |  |  |  |  |

| (Byte/Word Read/Write) |               | 0                     | xxx xxxx   | XXXX     |               | xx  |  |  |  |  |

|                        | Configuration | TB                    | LPAG<7:0>  |          | Data EA<15:0> |     |  |  |  |  |

|                        |               | 1                     | xxx xxxx   | XXXX     |               | xx  |  |  |  |  |

### TABLE 4-47: PROGRAM SPACE ADDRESS CONSTRUCTION

# 9.1 CPU Clocking System

The dsPIC33EVXXXGM00X/10X family of devices provides the following six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Low-Power RC (LPRC) Oscillator

For instruction execution speed or device operating frequency, FCY, see Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

#### FCY = FOSC/2

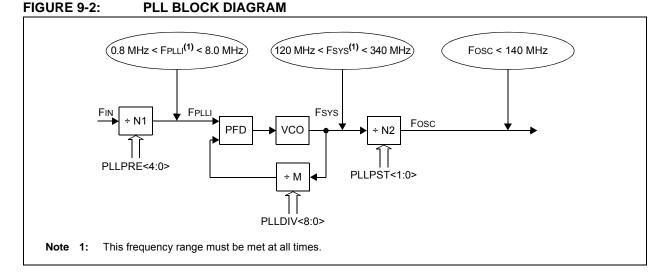

Figure 9-2 provides the block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FOSC).

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FSYS).

# EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2) \times 2(PLLPOST < 1:0 > + 1)}\right)$$

Where: *N*1 = *PLLPRE*<4:0> + 2 *N*2 = 2 x (*PLLPOST*<1:0> + 1) *M* = *PLLDIV*<8:0> + 2

# EQUATION 9-3: Fvco CALCULATION

$$FSYS = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV < 8:0 > + 2)}{(PLLPRE < 4:0 > + 2)}\right)$$

|              | R/W-0                                                             | R/W-0                                                                                   | R/W-0                                        | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|--------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------|-------------------|------------------|-----------------|-------|

| IC2R7        | IC2R6                                                             | IC2R5                                                                                   | IC2R4                                        | IC2R3             | IC2R2            | IC2R1           | IC2R0 |

| oit 15       |                                                                   |                                                                                         |                                              |                   |                  |                 | bit 8 |

| R/W-0        | R/W-0                                                             | R/W-0                                                                                   | R/W-0                                        | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| IC1R7        | IC1R6                                                             | IC1R5                                                                                   | IC1R4                                        | IC1R3             | IC1R2            | IC1R1           | IC1R0 |

| it 7         |                                                                   |                                                                                         |                                              | -                 |                  |                 | bit 0 |

| .egend:      |                                                                   |                                                                                         |                                              |                   |                  |                 |       |

| R = Readable | e bit                                                             | W = Writable                                                                            | bit                                          | U = Unimpler      | nented bit, read | <b>d as</b> '0' |       |

| n = Value at | POR                                                               | '1' = Bit is set                                                                        |                                              | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              | 10110101 -                                                        |                                                                                         |                                              |                   |                  |                 |       |

|              | •<br>•                                                            | <ul> <li>Input tied to RI</li> <li>Input tied to CI</li> </ul>                          |                                              |                   |                  |                 |       |

|              | •<br>•<br>000000001 =<br>00000000 =                               | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> </ul>                          | MP1<br>SS                                    |                   |                  |                 |       |

| bit 7-0      | •<br>•<br>00000001 =<br>00000000 =<br>IC1R<7:0>:                  | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> <li>Assign Input Ca</li> </ul> | MP1<br>SS<br>apture 1 (IC1)                  |                   | onding RPn Pir   | n bits          |       |

| iit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | <ul> <li>Input tied to Cl</li> <li>Input tied to Vs</li> </ul>                          | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits          |       |

| iit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | Input tied to Cl<br>Input tied to Vs<br>Assign Input Ca<br>1-2 for input pin            | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits          |       |

| vit 7-0      | •<br>•<br>000000001 =<br>00000000 =<br>IC1R<7:0>:<br>(see Table 1 | Input tied to Cl<br>Input tied to Vs<br>Assign Input Ca<br>1-2 for input pin            | MP1<br>SS<br>apture 1 (IC1)<br>selection nur |                   | onding RPn Pir   | n bits          |       |

# REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

# REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----|------------------|--------|------------------|------------------|-----------------|--------|

| —               | _   | RP39R5           | RP39R4 | RP39R3           | RP39R2           | RP39R1          | RP39R0 |

| bit 15          |     | -                |        |                  |                  |                 | bit 8  |

|                 |     |                  |        |                  |                  |                 |        |

| U-0             | U-0 | R/W-0            | R/W-0  | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —               | —   | RP38R5           | RP38R4 | RP38R3           | RP38R2           | RP38R1          | RP38R0 |

| bit 7           |     |                  |        |                  |                  |                 | bit 0  |

|                 |     |                  |        |                  |                  |                 |        |

| Legend:         |     |                  |        |                  |                  |                 |        |

| R = Readable    | bit | W = Writable     | bit    | U = Unimpler     | nented bit, read | <b>as</b> '0'   |        |

| -n = Value at P | OR  | '1' = Bit is set |        | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP39R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP39 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP38R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP38 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP41R5 | RP41R4 | RP41R3 | RP41R2 | RP41R1 | RP41R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP40R5 | RP40R4 | RP40R3 | RP40R2 | RP40R1 | RP40R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

|        |     |        |        |        |        |        |        |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

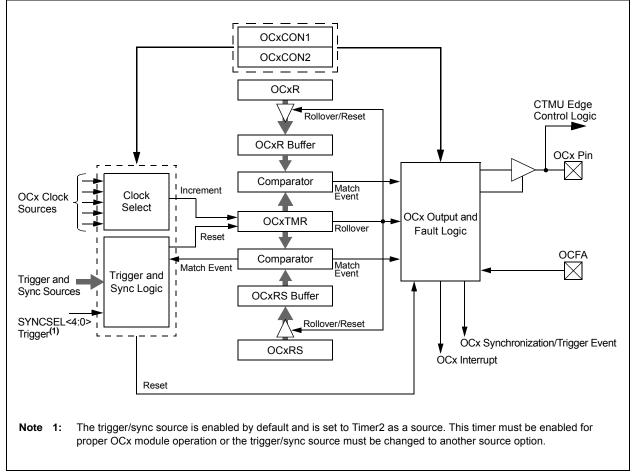

# 16.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70005157) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices support up to 4 output compare modules. The output compare module can select one of eight available clock

sources for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Figure 16-1 shows a block diagram of the output compare module.

Note: For more information on OCxR and OCxRS register restrictions, refer to the "Output Compare" (DS70005157) section in the "dsPIC33/PIC24 Family Reference Manual".

#### **REGISTER 16-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output sets high when OCxTMR = OCxR and sets low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output sets high when OCxTMR = 0 and sets low when OCxTMR =  $OCxR^{(1)}$

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

# 17.2 **PWM Resources**

Many useful resources are provided on the main product page on the Microchip web site (www.microchip.com) for the devices listed in this data sheet. This product page contains the latest updates and additional information.

Note: In case the above link is not accessible, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 17.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# REGISTER 20-2: SENTxSTAT: SENTx STATUS REGISTER (CONTINUED)

bit 0 SYNCTXEN: SENTx Synchronization Period Status/Transmit Enable bit<sup>(1)</sup> Module in Receive Mode (RCVEN = 1):

1 = A valid synchronization period was detected; the module is receiving nibble data

0 = No synchronization period has been detected; the module is not receiving nibble data

Module in Asynchronous Transmit Mode (RCVEN = 0, TXM = 0):

The bit always reads as '1' when the module is enabled, indicating the module transmits SENTx data frames continuously. The bit reads '0' when the module is disabled.

Module in Synchronous Transmit Mode (RCVEN = 0, TXM = 1):

1 = The module is transmitting a SENTx data frame

- 0 = The module is not transmitting a data frame, user software may set SYNCTXEN to start another data frame transmission

- Note 1: In Receive mode (RCVEN = 1), the SYNCTXEN bit is read-only.

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|----------------------|------------------|------------------|------------------|------------------|-----------------|--------|

| F15BP3        | F15BP2               | F15BP1           | F15BP0           | F14BP3           | F14BP2           | F14BP1          | F14BP0 |

| bit 15        |                      |                  |                  |                  | •                |                 | bit 8  |

|               |                      |                  |                  |                  |                  |                 |        |

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| F13BP3        | F13BP2               | F13BP1           | F13BP0           | F12BP3           | F12BP2           | F12BP1          | F12BP0 |

| bit 7         |                      |                  |                  |                  |                  |                 | bit 0  |

|               |                      |                  |                  |                  |                  |                 |        |

| Legend:       |                      |                  |                  |                  |                  |                 |        |

| R = Readable  | e bit                | W = Writable     | bit              | U = Unimpler     | mented bit, read | <b>l as</b> '0' |        |

| -n = Value at | POR                  | '1' = Bit is set |                  | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|               |                      |                  |                  |                  |                  |                 |        |

| bit 15-12     | F15BP<3:0>:          | RX Buffer Ma     | sk for Filter 15 | 5 bits           |                  |                 |        |

|               | 1111 = Filter        | hits received in | n RX FIFO but    | ffer             |                  |                 |        |

|               | 1110 = Filter        | hits received in | n RX Buffer 14   | ļ.               |                  |                 |        |

|               | •                    |                  |                  |                  |                  |                 |        |

|               | •                    |                  |                  |                  |                  |                 |        |

|               | 0001 <b>= Filter</b> | hits received ir | n RX Buffer 1    |                  |                  |                 |        |

|               | 0000 <b>= Filter</b> | hits received in | n RX Buffer 0    |                  |                  |                 |        |

| bit 11-8      | F14BP<3:0>:          | RX Buffer Ma     | sk for Filter 14 | l bits (same va  | lues as bits 15- | 12)             |        |

| bit 7-4       | F13BP<3:0>:          | RX Buffer Ma     | sk for Filter 13 | 3 bits (same va  | lues as bits 15- | 12)             |        |

| bit 3-0       | F12BP<3:0>:          | RX Buffer Ma     | sk for Filter 12 | 2 bits (same va  | lues as bits 15- | 12)             |        |

|               |                      |                  |                  |                  |                  |                 |        |

# REGISTER 22-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

# BUFFER 22-7: CANx MESSAGE BUFFER WORD 6

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                | R/W-x | R/W-x | R/W-x |  |

|-----------------------------------|-------|------------------|-------|--------------------------------------|-------|-------|-------|--|

|                                   |       |                  | Byte  | 7<15:8>                              |       |       |       |  |

| bit 15                            |       |                  |       |                                      |       |       | bit 8 |  |

|                                   |       |                  |       |                                      |       |       |       |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                | R/W-x | R/W-x | R/W-x |  |

|                                   |       |                  | Byte  | 6<7:0>                               |       |       |       |  |

| bit 7                             |       |                  |       |                                      |       |       | bit 0 |  |

|                                   |       |                  |       |                                      |       |       |       |  |

| Legend:                           |       |                  |       |                                      |       |       |       |  |

| R = Readable bit W = Writable bit |       |                  | oit   | U = Unimplemented bit, read as '0'   |       |       |       |  |

| -n = Value at POR '1' = Bit is s  |       | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unkn |       |       | nown  |  |

bit 15-8 Byte 7<15:8>: CANx Message Byte 7 bits

bit 7-0 Byte 6<7:0>: CANx Message Byte 6 bits

# BUFFER 22-8: CANx MESSAGE BUFFER WORD 7

| U-0                                | U-0 | U-0                                   | R/W-x                                   | R/W-x | R/W-x | R/W-x | R/W-x |  |

|------------------------------------|-----|---------------------------------------|-----------------------------------------|-------|-------|-------|-------|--|

| —                                  |     | —                                     | FILHIT<4:0> <sup>(1)</sup>              |       |       |       |       |  |

| bit 15                             |     |                                       |                                         |       |       |       | bit 8 |  |

|                                    |     |                                       |                                         |       |       |       |       |  |

| U-0                                | U-0 | U-0                                   | U-0                                     | U-0   | U-0   | U-0   | U-0   |  |

| —                                  | —   |                                       | —                                       | —     |       |       | —     |  |

| bit 7                              |     |                                       |                                         |       |       |       | bit 0 |  |

| Legend:                            |     |                                       |                                         |       |       |       |       |  |

| R = Readable bit W = Writable b    |     | it U = Unimplemented bit, read as '0' |                                         |       |       |       |       |  |

| -n = Value at POR '1' = Bit is set |     |                                       | '0' = Bit is cleared x = Bit is unknown |       |       |       |       |  |

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits<sup>(1)</sup>

Encodes number of filter that resulted in writing this buffer.

bit 7-0 Unimplemented: Read as '0'

Note 1: Only written by module for receive buffers, unused for transmit buffers.

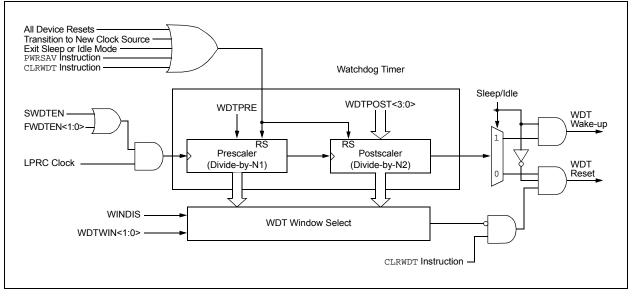

# 27.5 Watchdog Timer (WDT)

For dsPIC33EVXXXGM00X/10X family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Time-out Period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 27-2: WDT BLOCK DIAGRAM

### 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3:2>) needs to be cleared in software after the device wakes up.

### 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN<1:0> Configuration bits in the FWDT Configuration register. When the FWDTEN<1:0> Configuration bits are set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTENx Configuration bits have been programmed to '00'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

# 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<7>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window (WDTWIN<1:0>) select bits.

# TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CH        | AC CHARACTERISTICS |                                         |                           | (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |               |       |                                                                             |  |

|--------------|--------------------|-----------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|--|

| Param<br>No. | Symbol             | Charac                                  | cteristic <sup>(1)</sup>  | Min.                                                                                                                                                             | Тур. | Max.          | Units | Conditions                                                                  |  |

| TB10         | T⊤xH               | TxCK High<br>Time                       | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                             |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |  |

| TB11         | ΤτχL               | TxCK Low<br>Time                        | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N                                                                                                                             | _    | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |  |

| TB15         | ΤτχΡ               | TxCK Input<br>Period                    | Synchronous<br>mode       | Greater of:<br>40 or<br>(2 Tcy + 40)/N                                                                                                                           | _    | _             | ns    | N = Prescaler Value<br>(1, 8, 64, 256)                                      |  |

| TB20         | TCKEXT-<br>MRL     | Delay from I<br>Clock Edge<br>Increment | External TxCK<br>to Timer | 0.75 Tcy + 40                                                                                                                                                    | _    | 1.75 Tcy + 40 | ns    |                                                                             |  |

Note 1: These parameters are characterized but not tested in manufacturing.

# TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                      |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |               |      |               |            |                                        |

|--------------------|--------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------|------------|----------------------------------------|

| Param<br>No.       | Symbol Characteristic <sup>(1)</sup> |                                                              | Min.                                                                                                                                                                                                                                                                                | Тур.          | Max. | Units         | Conditions |                                        |

| TC10               | ТтхН                                 | TxCK High<br>Time                                            | Synchronous                                                                                                                                                                                                                                                                         | Tcy + 20      |      | _             | ns         | Must also meet<br>Parameter TC15       |

| TC11               | ΤτxL                                 | TxCK Low<br>Time                                             | Synchronous                                                                                                                                                                                                                                                                         | Tcy + 20      | _    | —             | ns         | Must also meet<br>Parameter TC15       |

| TC15               | ΤτχΡ                                 | TxCK Input<br>Period                                         | Synchronous,<br>with Prescaler                                                                                                                                                                                                                                                      | 2 Tcy + 40    | _    | —             | ns         | N = Prescaler Value<br>(1, 8, 64, 256) |

| TC20               | TCKEXT-<br>MRL                       | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                                                                                                                                     | 0.75 Tcy + 40 | _    | 1.75 Tcy + 40 | ns         |                                        |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

| AC CHARACTERISTICS |                       |                                | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |         |       |                                                  |  |

|--------------------|-----------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------|--------------------------------------------------|--|

| Param<br>No.       | Symbol Characteristic |                                | Min.                                                                                                                                                                                                                                                                                               | Тур.      | Max.    | Units | Conditions                                       |  |

|                    |                       | ADC A                          | Accuracy                                                                                                                                                                                                                                                                                           | (10-Bit   | Mode)   |       |                                                  |  |

| AD20b              | Nr                    | Resolution                     | 1(                                                                                                                                                                                                                                                                                                 | ) data bi | ts      | bits  |                                                  |  |

| AD21b              | INL                   | Integral Nonlinearity          | -1.5                                                                                                                                                                                                                                                                                               | —         | +1.5    | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5.5V |  |

| AD22b              | DNL                   | Differential Nonlinearity      | ≥ 1                                                                                                                                                                                                                                                                                                | —         | < 1     | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |  |

| AD23b              | Gerr                  | Gain Error                     | 1                                                                                                                                                                                                                                                                                                  | 3         | 6       | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |  |

| AD24b              | EOFF                  | Offset Error                   | 1                                                                                                                                                                                                                                                                                                  | 2         | 4       | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |  |

| AD25b              | —                     | Monotonicity <sup>(2)</sup>    | _                                                                                                                                                                                                                                                                                                  |           | _       |       | Guaranteed                                       |  |

|                    |                       | Dynamic                        | Performa                                                                                                                                                                                                                                                                                           | nce (10-  | Bit Mod | e)    |                                                  |  |

| AD30b              | THD                   | Total Harmonic Distortion      | _                                                                                                                                                                                                                                                                                                  |           | -64     | dB    |                                                  |  |

| AD31b              | SINAD                 | Signal to Noise and Distortion | 57                                                                                                                                                                                                                                                                                                 | 58.5      | _       | dB    |                                                  |  |

| AD32b              | SFDR                  | Spurious Free Dynamic<br>Range | 72                                                                                                                                                                                                                                                                                                 | _         | —       | dB    |                                                  |  |

| AD33b              | Fnyq                  | Input Signal Bandwidth         | _                                                                                                                                                                                                                                                                                                  | —         | 550     | kHz   |                                                  |  |

| AD34b              | ENOB                  | Effective Number of Bits       | 9.16                                                                                                                                                                                                                                                                                               | 9.4       |         | bits  |                                                  |  |

# TABLE 30-56: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

2: The conversion result never decreases with an increase in the input voltage.

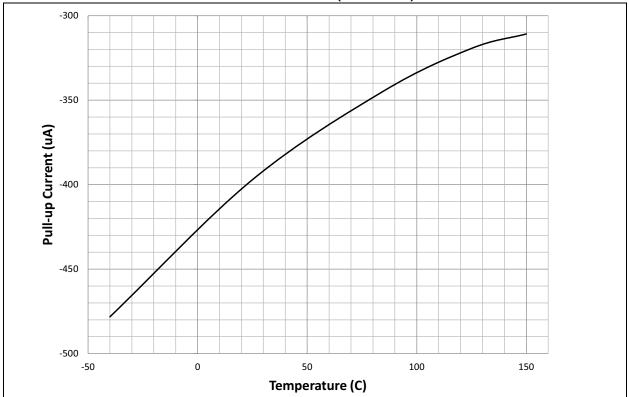

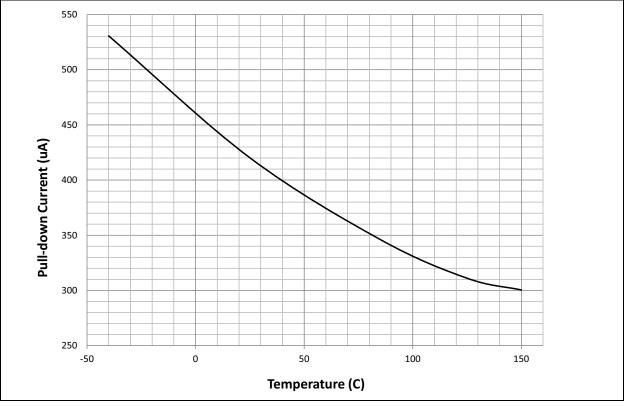

# 33.8 Pull-up/Pull-Down Current