Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

|                           |                                                                                  |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| peed                      | 60 MIPs                                                                          |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| eripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| lumber of I/O             | 21                                                                               |

| rogram Memory Size        | 128KB (43K x 24)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AAM Size                  | 8K x 8                                                                           |

| oltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Oata Converters           | A/D 11x10/12b                                                                    |

| Scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C (TA)                                                               |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package   | 28-SOIC                                                                          |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm102-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2 Data Address Space

The dsPIC33EVXXXGM00X/10X family CPU has a separate, 16-bit wide data memory space. The Data Space (DS) is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-6 and Figure 4-8.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the DS. This arrangement gives a Base Data Space address range of 64 Kbytes or 32K words.

The Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS), which has a total address range of 16 Mbytes.

dsPIC33EVXXXGM00X/10X family devices implement up to 20 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 16 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all zero word or byte is returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte-addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all DS EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

# 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC® MCU devices and improve Data Space memory usage efficiency, the dsPIC33EVXXXGM00X/10X family instruction set supports both word and byte operations. As a consequence of byte accessibility, all the Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, therefore, care must be taken when mixing byte and word operations or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB: the MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EVXXXGM00X/10X family core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

Note:

The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole DS is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a Working register as an Address Pointer.

TABLE 4-41: PORTF REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | AII<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISF       | 0E64  | _      | -      | -      |        | 1      | _      | _     | _     | 1     | _     | _     | _     | _     |       | TRISF | <1:0> | 0003          |

| PORTF       | 0E66  | 1      | -      | _      | -      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | RF<1  | :0>   | xxxx          |

| LATF        | 0E68  | 1      | -      | _      | -      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | LATF< | :1:0> | xxxx          |

| ODCF        | 0E6A  |        | ı      | 1      |        | ı      | _      | _     | _     | ı     | _     | -     | -     | _     |       | ODCF: | <1:0> | 0000          |

| CNENF       | 0E6C  | 1      | -      | _      | -      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | CNIEF | <1:0> | 0000          |

| CNPUF       | 0E6E  | 1      | -      | _      | -      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | CNPUF | <1:0> | 0000          |

| CNPDF       | 0E70  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | CNPDF | <1:0> | 0000          |

$\textbf{Legend:} \quad \mathbf{x} = \text{unknown value on Reset;} \\ \textbf{--} = \text{unimplemented, read as '0'}. \\ \textbf{Reset values are shown in hexadecimal.}$

### TABLE 4-42: PORTG REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG       | 0E78  | _      | _      | _      | _      | _      | _      |       | TRISC | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 03C0          |

| PORTG       | 0E7A  |        | _      | _      | _      | _      | _      |       | RG<   | 9:6>   |       | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG        | 0E7C  |        | _      | _      | _      | _      | _      |       | LATG  | <9:6>  |       | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG        | 0E7E  |        | _      | _      | _      | _      | _      |       | ODC   | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG       | 0E80  |        | _      | _      | _      | _      | _      |       | CNIE  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG       | 0E82  |        | _      | _      | _      | _      | _      |       | CNPU  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG       | 0E84  |        | _      | _      | _      | _      | _      |       | CNPD  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| ANSELG      | 0E86  |        | _      | _      | _      | _      | _      |       | ANSG  | S<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.3.1 PAGED MEMORY SCHEME

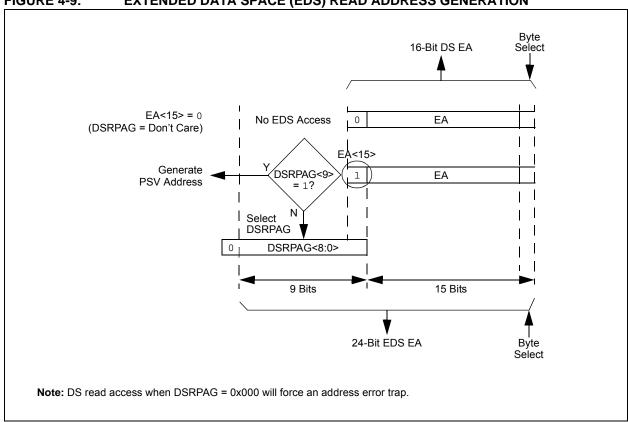

The dsPIC33EVXXXGM00X/10X family architecture extends the available DS through a paging scheme, which allows the available DS to be accessed using MOV instructions in a linear fashion for pre- and postmodified Effective Addresses (EAs). The upper half of the Base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Data Space Read Page register (DSRPAG) or the 9-bit Data Space Write Page register (DSWPAG), to form an EDS address, or Program Space Visibility (PSV) address.

The Data Space Page registers are located in the SFR space. Construction of the EDS address is shown in Figure 4-9 and Figure 4-10. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when the base address bit, EA<15> = 1, the DSWPAG<8:0> bits are concatenated onto EA<14:0> to form the 24bit EDS write address.

FIGURE 4-9: **EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION**

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode, with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC® DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

Note:

If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### REGISTER 11-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| IC2R7  | IC2R6 | IC2R5 | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IC1R7 | IC1R6 | IC1R5 | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 IC2R<7:0>: Assign Input Capture 2 (IC2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers)

10110101 = Input tied to RPI181

•

•

•

00000001 = Input tied to CMP1 00000000 = Input tied to Vss

bit 7-0 IC1R<7:0>: Assign Input Capture 1 (IC1) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

10110101 = Input tied to RPI181

•

•

00000001 = Input tied to CMP1 00000000 = Input tied to Vss

### REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | RP70R5 | RP70R4 | RP70R3 | RP70R2 | RP70R1 | RP70R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP69R5 | RP69R4 | RP69R3 | RP69R2 | RP69R1 | RP69R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP70R<5:0>: Peripheral Output Function is Assigned to RP70 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP69R<5:0>: Peripheral Output Function is Assigned to RP69 Output Pin bits

(see Table 11-3 for peripheral function numbers)

**Note 1:** This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9<sup>(1)</sup>

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | RP118R5 | RP118R4 | RP118R3 | RP118R2 | RP118R1 | RP118R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | RP97R5 | RP97R4 | RP97R3 | RP97R2 | RP97R1 | RP97R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 RP118R<5:0>: Peripheral Output Function is Assigned to RP118 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP97R<5:0>: Peripheral Output Function is Assigned to RP97 Output Pin bits

(see Table 11-3 for peripheral function numbers)

**Note 1:** This register is present in dsPIC33EVXXXGM004/106 devices only.

# REGISTER 17-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

```

FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator x bits

bit 7-3

11111 = Fault 32 (default)

11110 = Reserved

01100 = Op Amp/Comparator 5

01011 = Comparator 4

01010 = Op Amp/Comparator 3

01001 = Op Amp/Comparator 2

01000 = Op Amp/Comparator 1

00111 = Fault 8

00110 = Fault 7

00101 = Fault 6

00100 = Fault 5

00011 = Fault 4

00010 = Fault 3

00001 = Fault 2

00000 = Fault 1

FLTPOL: Fault Polarity for PWM Generator x bit<sup>(2)</sup>

bit 2

1 = The selected Fault source is active-low

0 = The selected Fault source is active-high

bit 1-0

FLTMOD<1:0>: Fault Mode for PWM Generator x bits

11 = Fault input is disabled

10 = Reserved

01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDAT<1:0> values (cycle)

00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDAT<1:0> values (latched condition)

```

- Note 1: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the FCLCONx register can only be written after the unlock sequence has been executed.

- 2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|--------|--------|-----|-----|-----|-----|-------|

| FRMEN  | SPIFSD | FRMPOL | _   | _   | _   | _   | _     |

| bit 15 |        |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|-----|--------|--------|

| _     | _   | _   | _   | _   | _   | FRMDLY | SPIBEN |

| bit 7 |     |     |     |     |     |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 FRMEN: Framed SPIx Support bit

1 = Framed SPIx support is enabled  $(\overline{SSx})$  pin is used as the Frame Sync pulse input/output)

0 = Framed SPIx support is disabled

bit 14 SPIFSD: SPIx Frame Sync Pulse Direction Control bit

1 = Frame Sync pulse input (slave)0 = Frame Sync pulse output (master)

bit 13 FRMPOL: Frame Sync Pulse Polarity bit

1 = Frame Sync pulse is active-high 0 = Frame Sync pulse is active-low

bit 12-2 **Unimplemented:** Read as '0'

bit 1 FRMDLY: Frame Sync Pulse Edge Select bit

1 = Frame Sync pulse coincides with the first bit clock 0 = Frame Sync pulse precedes the first bit clock

bit 0 SPIBEN: SPIx Enhanced Buffer Enable bit

1 = Enhanced buffer is enabled

0 = Enhanced buffer is disabled (Standard mode)

#### REGISTER 19-3: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC | R-0, HSC | R-0, HSC | U-0 | U-0 | R/C-0, HSC | R-0, HSC | R-0, HSC |

|----------|----------|----------|-----|-----|------------|----------|----------|

| ACKSTAT  | TRSTAT   | ACKTIM   | _   | _   | BCL        | GCSTAT   | ADD10    |

| bit 15   |          |          |     |     |            |          | bit 8    |

| R/C-0, HS | R/C-0, HS | R-0, HSC | R/C-0, HSC | R/C-0, HSC | R-0, HSC | R-0, HSC | R-0, HSC |

|-----------|-----------|----------|------------|------------|----------|----------|----------|

| IWCOL     | I2COV     | D_A      | Р          | S          | R_W      | RBF      | TBF      |

| bit 7     |           |          |            |            |          |          | bit 0    |

| Legend:           | C = Clearable bit | HSC = Hardware Settable/Clearable bit |                            |  |  |

|-------------------|-------------------|---------------------------------------|----------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'    |                            |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared                  | HS = Hardware Settable bit |  |  |

bit 15 ACKSTAT: Acknowledge Status bit (updated in all Master and Slave modes)

1 = Acknowledge was not received from slave

0 = Acknowledge was received from slave

bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master; applicable to master transmit operation)

1 = Master transmit is in progress (8 bits +  $\overline{ACK}$ )

0 = Master transmit is not in progress

bit 13 **ACKTIM:** Acknowledge Time Status bit (valid in I<sup>2</sup>C Slave mode only)

1 = Indicates I<sup>2</sup>C bus is in an Acknowledge sequence, set on 8<sup>th</sup> falling edge of SCLx clock

0 = Not an Acknowledge sequence, cleared on 9<sup>th</sup> rising edge of SCLx clock

bit 12-11 Unimplemented: Read as '0'

bit 10 BCL: Bus Collision Detect bit (Master/Slave mode; cleared when I<sup>2</sup>C module is disabled, I2CEN = 0)

1 = A bus collision has been detected during a master or slave transmit operation

0 = Bus collision has not been detected

bit 9 GCSTAT: General Call Status bit (cleared after Stop detection)

1 = General call address was received

0 = General call address was not received

bit 8 **ADD10:** 10-Bit Address Status bit (cleared after Stop detection)

1 = 10-bit address was matched

0 = 10-bit address was not matched

bit 7 IWCOL: Write Collision Detect bit

1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy; must be cleared in software

0 = Collision has not occurred

bit 6 I2COV: I2Cx Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte; I2COV is a "don't care" in Transmit mode, must be cleared in software

0 = Overflow has not occurred

bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

1 = Indicates that the last byte received was data

0 = Indicates that the last byte received or transmitted was an address

bit 4 P: I2Cx Stop bit

Updated when Start, Reset or Stop is detected; cleared when the I<sup>2</sup>C module is disabled, I2CEN = 0.

1 = Indicates that a Stop bit has been detected last

0 = Indicates that a Stop bit was not detected last

### REGISTER 22-2: CxCTRL2: CANx CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R-0        | R-0 | R-0 | R-0 | R-0   |  |

|-------|-----|-----|------------|-----|-----|-----|-------|--|

| _     | _   | _   | DNCNT<4:0> |     |     |     |       |  |

| bit 7 |     |     |            |     |     |     | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 **DNCNT<4:0>:** DeviceNet™ Filter Bit Number bits

10010-11111 = Invalid selection

10001 = Compare up to Data Byte 3, bit 6 with EID<17>

•

.

00001 = Compare up to Data Byte 1, bit 7 with EID<0>

00000 = Do not compare data bytes

### REGISTER 24-8: ADxCSSL: ADCx INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| CSS<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15    |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| CSS<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7    |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 CSS<15:0>: ADCx Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

**2:** CSSx = ANx, where 'x' = 0-5.

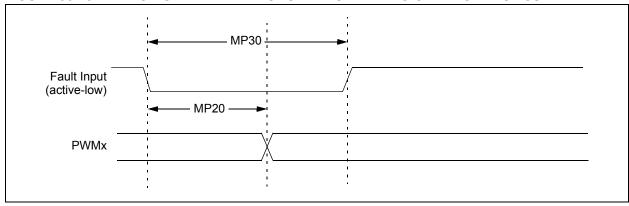

FIGURE 30-10: HIGH-SPEED PWMx MODULE FAULT TIMING CHARACTERISTICS

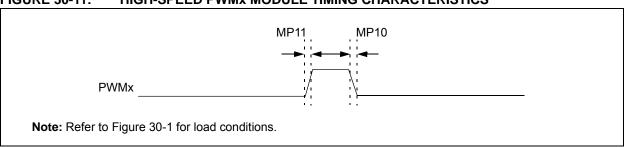

FIGURE 30-11: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS

TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                  | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$ for Extended |                                 |    |    |                    |  |

|--------------------|--------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----|----|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                 | Min. Typ. Max. Units Conditions |    |    |                    |  |

| MP10               | TFPWM  | PWMx Output Fall Time            | _                                                                                                                                                                                                                                                    | _                               | _  | ns | See Parameter DO32 |  |

| MP11               | TRPWM  | PWMx Output Rise Time            | _                                                                                                                                                                                                                                                    | _                               | _  | ns | See Parameter DO31 |  |

| MP20               | TFD    | Fault Input ↓ to PWMx I/O Change | _                                                                                                                                                                                                                                                    | _                               | 15 | ns |                    |  |

| MP30               | TFH    | Fault Input Pulse Width          | 15                                                                                                                                                                                                                                                   | _                               | _  | ns |                    |  |

Note 1: These parameters are characterized but not tested in manufacturing.

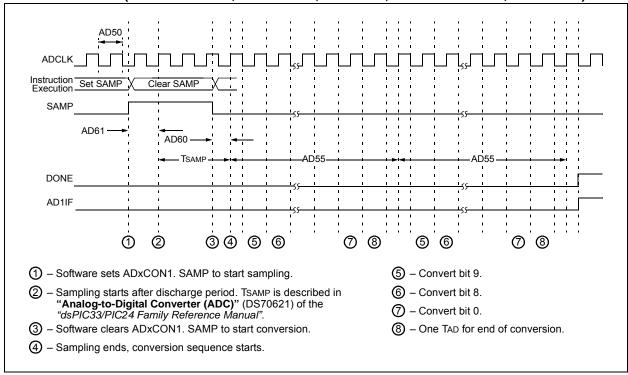

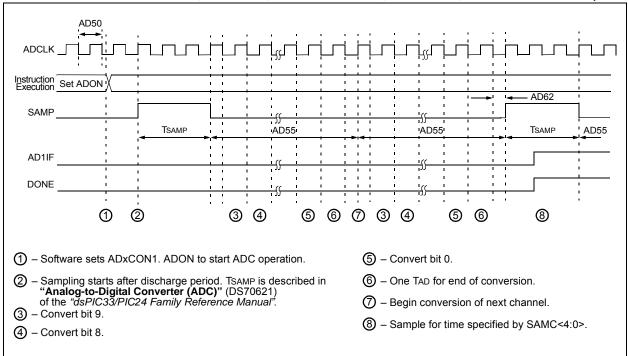

FIGURE 30-35: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

FIGURE 30-36: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

### TABLE 31-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACT    | ERISTICS      |      | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature |                                         |  |  |  |

|---------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| Parameter No. | Typical       | Max  | Units                                                                                                                                                                         | Conditions                              |  |  |  |

| Power-Down    | Current (IPD) |      |                                                                                                                                                                               |                                         |  |  |  |

| HDC60e        | 1300          | 2500 | μΑ                                                                                                                                                                            | +150°C 5V Base Power-Down Current       |  |  |  |

| HDC61c        | 10            | 50   | μΑ                                                                                                                                                                            | +150°C 5V Watchdog Timer Current: ΔIWDT |  |  |  |

### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG     | CTERISTICS |     | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature |                   |    |         |  |

|---------------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|---------|--|

| Parameter No. | Typical    | Max | Units                                                                                                                                                                         | Conditions        |    |         |  |

| HDC40e        | 2.6        | 5.0 | mA                                                                                                                                                                            | +150°C            | 5V | 10 MIPS |  |

| HDC42e        | 3.6        | 7.0 | mA                                                                                                                                                                            | +150°C 5V 20 MIPS |    |         |  |

### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAC     | CTERISTICS |      |       | •          |    | V (unless otherwise stated) C for High Temperature |  |

|---------------|------------|------|-------|------------|----|----------------------------------------------------|--|

| Parameter No. | Typical    | Max  | Units | Conditions |    |                                                    |  |

| HDC20e        | 5.9        | 8.0  | mA    | +150°C     | 5V | 10 MIPS                                            |  |

| HDC22e        | 10.3       | 15.0 | mA    | +150°C     | 5V | 20 MIPS                                            |  |

| HDC23e        | 19.0       | 25.0 | mA    | +150°C     | 5V | 40 MIPS                                            |  |

### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARAC     | CTERISTICS |      | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +150^{\circ}\text{C}$ for High Temperature |       |            |     |           |  |

|---------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-----|-----------|--|

| Parameter No. | Typical    | Max  | Doze Ratio                                                                                                                                                                    | Units | Conditions |     |           |  |

| HDC73a        | 18.5       | 22.0 | 1:2                                                                                                                                                                           | mA    | +150°C     | 5)/ | 40 MIPS   |  |

| HDC73g        | 8.35       | 12.0 | 1:128                                                                                                                                                                         | mA    | +150 C     | 5V  | 40 IVIIPS |  |

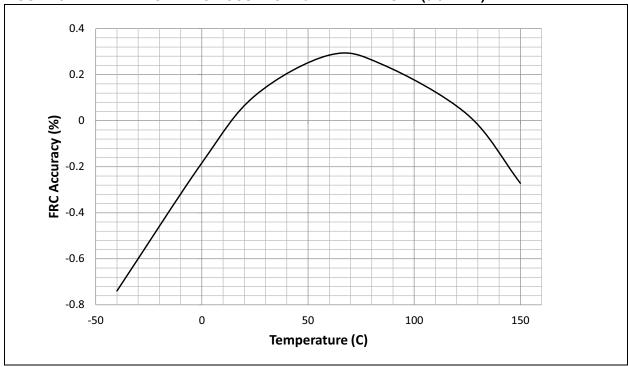

FIGURE 32-21: TYPICAL FRC ACCURACY vs. TEMPERATURE (5.5V VDD)

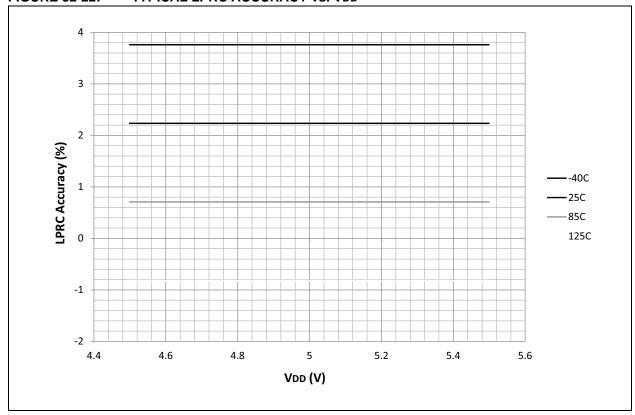

32.6 LPRC

FIGURE 32-22: TYPICAL LPRC ACCURACY vs. VDD

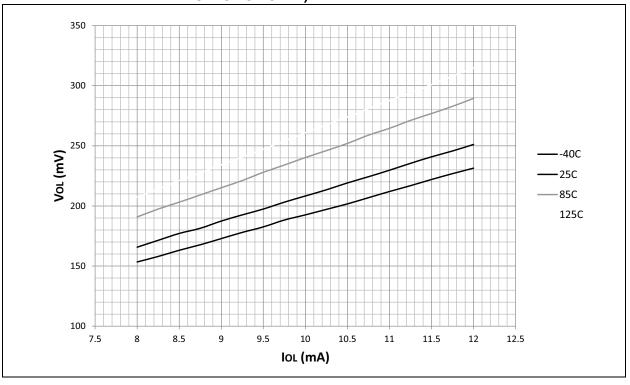

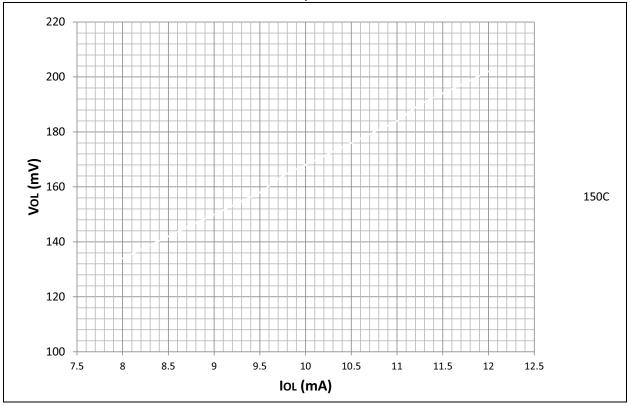

FIGURE 32-33: TYPICAL Vol 4x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, **TEMPERATURES AS NOTED)**

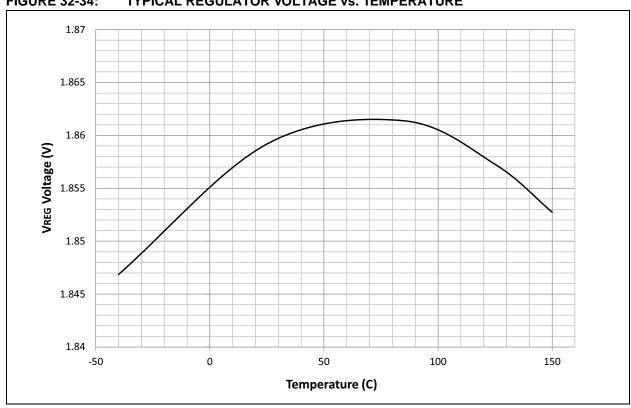

### 32.11 **V**REG

FIGURE 32-34: TYPICAL REGULATOR VOLTAGE vs. TEMPERATURE

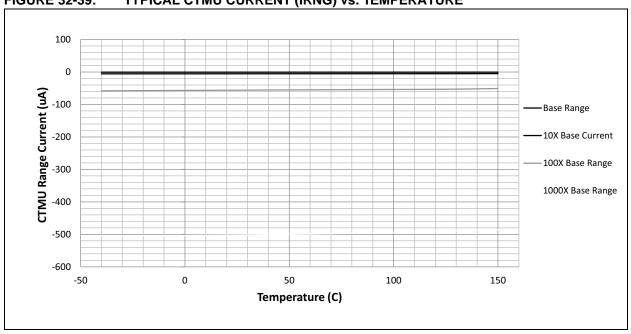

### 32.15 CTMU Current vs. Temperature

FIGURE 32-39: TYPICAL CTMU CURRENT (IRNG) vs. TEMPERATURE

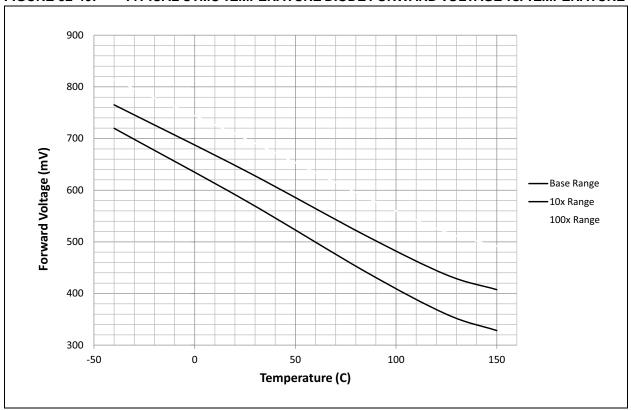

### 32.16 CTMU Temperature Forward Diode

FIGURE 32-40: TYPICAL CTMU TEMPERATURE DIODE FORWARD VOLTAGE vs. TEMPERATURE

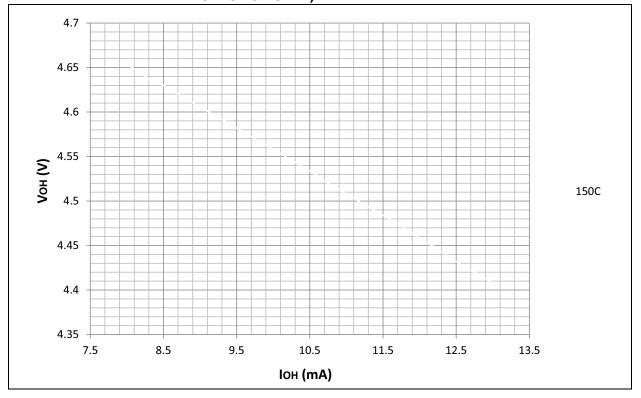

FIGURE 33-27: TYPICAL VOH 4x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

FIGURE 33-28: TYPICAL Vol. 8x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

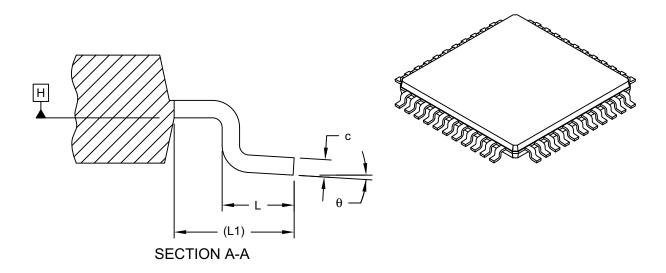

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units  | MILLIMETERS |           |      |  |

|--------------------------|--------|-------------|-----------|------|--|

| Dimension                | Limits | MIN         | NOM       | MAX  |  |

| Number of Leads          |        | 44          |           |      |  |

| Lead Pitch               | е      |             | 0.80 BSC  |      |  |

| Overall Height           | Α      | -           | -         | 1.20 |  |

| Standoff                 | A1     | 0.05        | -         | 0.15 |  |

| Molded Package Thickness | A2     | 0.95        | 1.00      | 1.05 |  |

| Overall Width            | Е      | 12.00 BSC   |           |      |  |

| Molded Package Width     | E1     |             | 10.00 BSC |      |  |

| Overall Length           | D      |             | 12.00 BSC |      |  |

| Molded Package Length    | D1     |             | 10.00 BSC |      |  |

| Lead Width               | b      | 0.30        | 0.37      | 0.45 |  |

| Lead Thickness           | С      | 0.09        | -         | 0.20 |  |

| Lead Length              | L      | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1     | 1.00 REF    |           |      |  |

| Foot Angle               | θ      | 0°          | 3.5°      | 7°   |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Exact shape of each corner is optional.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2

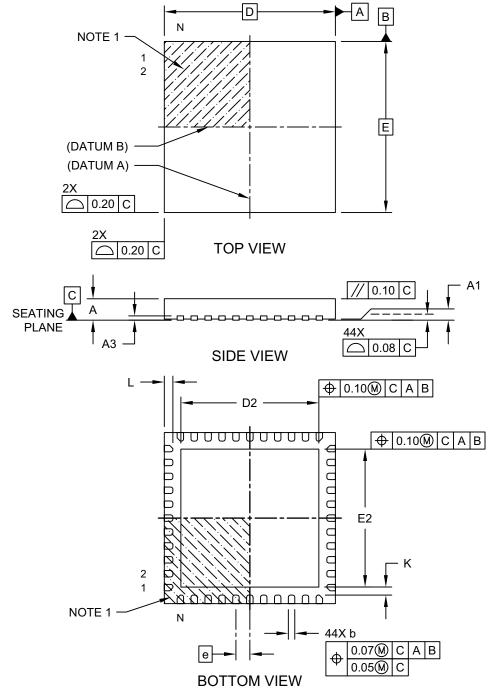

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-103D Sheet 1 of 2