#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Decalis                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm102-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-19: NVM REGISTER MAP

|             |       |        |        |          |              |             |               |       | -     |           |       | -     |        |            |        |        | -      |               |

|-------------|-------|--------|--------|----------|--------------|-------------|---------------|-------|-------|-----------|-------|-------|--------|------------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12       | Bit 11      | Bit 10        | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| NVMCON      | 0728  | WR     | WREN   | WRERR    | NVMSIDL      | _           | _             | RPDF  | URERR | _         | —     | _     | _      | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        |        |          |              |             |               |       |       | NVMADR<   | 15:0> |       |        |            |        |        |        | 0000          |

| NVMADRU     | 072C  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMAD  | RU<23:16>  |        |        |        | 0000          |

| NVMKEY      | 072E  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMK   | EY<7:0>    |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |        |          |              |             |               |       | NVMSF | RCADR<15: | 1>    |       |        |            |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMSRC | ADR<23:16> |        |        |        | 0000          |

| Lonondy     |       |        |        | Desetual | an are chour | a in heaven | d a stress al |       |       |           |       |       |        |            |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | _      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0000          |

| PLLFBD      | 0746  | -      | —      |        | —      | _      | _       | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0000          |

| OSCTUN      | 0748  | -      | —      |        | —      | _      | _       | —       |         | _        | _        |        |           | TUN     | <5:0>   |         |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

#### TABLE 4-21: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   | -      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     | _     | _     | _     | _     | _     | _     | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-33: PORTA REGISTER MAP FOR dsPIC33EVXXXGMX02 DEVICES

|             |       |        |        |        |        |        |        |       |       |       |       |       |       |       |            |           |       | · · · · · · · · · · · · · · · · · · · |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|------------|-----------|-------|---------------------------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1     | Bit 0 | All<br>Resets                         |

| TRISA       | 0E00  | _      | —      | _      | —      | —      | —      | —     | _     | _     | _     | _     |       | -     | TRISA<4:0> | >         |       | DF9F                                  |

| PORTA       | 0E02  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       |       | RA<4:0>    |           |       | 0000                                  |

| LATA        | 0E04  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       |       | LATA<4:0>  |           |       | 0000                                  |

| ODCA        | 0E06  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | (     | ODCA<4:0>  | >         |       | 0000                                  |

| CNENA       | 0E08  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | (     | CNIEA<4:0  | >         |       | 0000                                  |

| CNPUA       | 0E0A  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | C     | NPUA<4:0   | >         |       | 0000                                  |

| CNPDA       | 0E0C  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     |       | C     | NPDA<4:0   | >         |       | 0000                                  |

| ANSELA      | 0E0E  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ANSA4 | _     | 1          | ANSA<2:0> |       | 1813                                  |

| SR1A        | 0E10  | _      | —      | _      | _      | _      | _      | _     | _     | —     | _     | _     | SR1A4 | _     | —          | —         | —     | 0000                                  |

| SR0A        | 0E12  | _      | _      | _      | —      | —      | -      | —     |       | _     | _     |       | SR0A4 | _     | _          | -         | _     | 0000                                  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: PORTB REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|------------------------|--------|--------|--------|--------|-------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISB       | 0E14  |        |                        |        |        |        |        |       | TRISB<15  | :0>   |       |       |       |       |       |       |       | FFFF          |

| PORTB       | 0E16  |        |                        |        |        |        |        |       | RB<15:0   | >     |       |       |       |       |       |       |       | xxxx          |

| LATB        | 0E18  |        |                        |        |        |        |        |       | LATB<15:  | 0>    |       |       |       |       |       |       |       | xxxx          |

| ODCB        | 0E1A  |        | ODCB<15:0> 0.0         |        |        |        |        |       |           | 0000  |       |       |       |       |       |       |       |               |

| CNENB       | 0E1C  |        |                        |        |        |        |        |       | CNIEB<15  | :0>   |       |       |       |       |       |       |       | 0000          |

| CNPUB       | 0E1E  |        |                        |        |        |        |        |       | CNPUB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| CNPDB       | 0E20  |        |                        |        |        |        |        |       | CNPDB<15  | 5:0>  |       |       |       |       |       |       |       | 0000          |

| ANSELB      | 0E22  |        | ANSB<9:7> ANSB<3:0> 03 |        |        |        |        |       |           | 038F  |       |       |       |       |       |       |       |               |

| SR1B        | 0E24  |        | _                      | _      | _      |        |        |       | SR1B<9:7> |       | _     |       | SR1B4 | —     | _     | —     |       | 0000          |

| SR0B        | 0E26  | _      | —                      | _      | _      | _      | _      | :     | SR0B<9:7> |       | _     | _     | SR0B4 | _     | -     | _     | _     | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0             | U-0 | U-0              | U-0            | U-0              | U-0             | U-0                   | U-0         |

|-----------------|-----|------------------|----------------|------------------|-----------------|-----------------------|-------------|

| —               | —   | —                | —              | —                | —               | _                     | —           |

| bit 15          |     |                  |                |                  |                 |                       | bit 8       |

|                 |     |                  |                |                  |                 |                       |             |

| U-0             | U-0 | U-0              | U-0            | U-0              | U-0             | R-0, HS, SC           | R-0, HS, SC |

| —               | —   | —                |                | —                |                 | ECCDBE <sup>(1)</sup> | SGHT        |

| bit 7           |     |                  |                |                  |                 |                       | bit 0       |

|                 |     |                  |                |                  |                 |                       |             |

| Legend:         |     | HS = Hardwar     | e Settable bit | SC = Softwa      | re Clearable bi | t                     |             |

| R = Readable b  | bit | W = Writable b   | bit            | U = Unimplei     | mented bit, rea | d as '0'              |             |

| -n = Value at P | OR  | '1' = Bit is set |                | '0' = Bit is cle | eared           | x = Bit is unkr       | nown        |

#### **REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4**

| bit 15-2 | Unimplemented: Read as '0'                                                                                                |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| bit 1    | ECCDBE: ECC Double-Bit Error Trap bit <sup>(1)</sup>                                                                      |

|          | <ul><li>1 = ECC double-bit error trap has occurred</li><li>0 = ECC double-bit error trap has not occurred</li></ul>       |

| bit 0    | SGHT: Software-Generated Hard Trap Status bit                                                                             |

|          | <ul><li>1 = Software-generated hard trap has occurred</li><li>0 = Software-generated hard trap has not occurred</li></ul> |

Note 1: ECC double-bit error causes a generic hard trap.

| U-0             | U-0                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                | U-0                                   | R-0              | R-0             | R-0    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|-----------------|--------|

| _               | _                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          | —                                                                                                                  |                                       | ILR3             | ILR2            | ILR1   |

| bit 15          |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                    | · · · · · · · · · · · · · · · · · · · |                  |                 | bit    |

| R-0             | R-0                                                                                                                                                           | R-0                                                                                                                                                                                                                                                                                                      | R-0                                                                                                                | R-0                                   | R-0              | R-0             | R-0    |

| VECNUM7         | VECNUM6                                                                                                                                                       | VECNUM5                                                                                                                                                                                                                                                                                                  | VECNUM4                                                                                                            | VECNUM3                               | VECNUM2          | VECNUM1         | VECNUM |

| bit 7           |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                    |                                       |                  |                 | bit    |

| Legend:         |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                    |                                       |                  |                 |        |

| R = Readable    | bit                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                             | bit                                                                                                                | U = Unimplen                          | nented bit, read | l as '0'        |        |

| -n = Value at F | POR                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                         |                                                                                                                    | '0' = Bit is clea                     | ared             | x = Bit is unkr | nown   |

|                 | •<br>•<br>0001 = CPU                                                                                                                                          | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit                                                                                                                                                                                                                                              | y Level is 1                                                                                                       |                                       |                  |                 |        |

| bit 7-0         | 111111111 = 2<br>00001001 = 9<br>00001000 = 2<br>00000111 = 1<br>00000101 = 2<br>00000101 = 2<br>00000010 = 2<br>00000010 = 2<br>00000010 = 2<br>00000010 = 2 | <ol> <li>Vector Nun</li> <li>Reserved</li> <li>Input Captur</li> <li>External Inter</li> <li>External Inter</li> <li>Reserved; d</li> <li>Generic soft</li> <li>DMAC error</li> <li>Math error tr</li> <li>Stack error t</li> <li>Generic hard</li> <li>Address error</li> <li>Oscillator fai</li> </ol> | ; do not use<br>er 1 (IC1)<br>errupt 0 (INT0)<br>o not use<br>error trap<br>trap<br>ap<br>rap<br>d trap<br>or trap | ig Interrupt bits                     |                  |                 |        |

#### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

#### 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

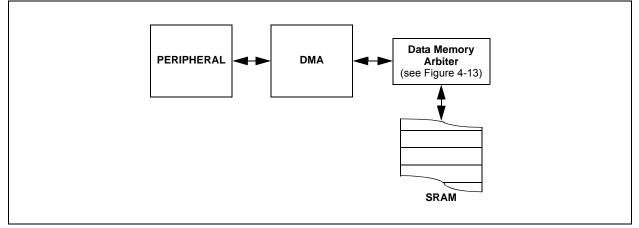

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

| R/W-0           | R/W-0                                    | R/W-0                                                                                           | R/W-0                         | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------|-----------------|-------|

|                 |                                          |                                                                                                 | SYNC                          | I1R<7:0>         |                 |                 |       |

| bit 15          |                                          |                                                                                                 |                               |                  |                 |                 | bit 8 |

| U-0             | U-0                                      | U-0                                                                                             | U-0                           | U-0              | U-0             | U-0             | U-0   |

| _               | _                                        | _                                                                                               | _                             | _                |                 | _               | —     |

| bit 7           |                                          |                                                                                                 |                               |                  |                 |                 | bit C |

|                 |                                          |                                                                                                 |                               |                  |                 |                 |       |

| Legend:         |                                          |                                                                                                 |                               |                  |                 |                 |       |

| R = Readable    | bit                                      | W = Writable                                                                                    | bit                           | U = Unimplei     | mented bit, rea | <b>d as</b> '0' |       |

| -n = Value at F | POR                                      | '1' = Bit is set                                                                                |                               | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 15-8        | (see Table 1<br>10110101 =<br>00000001 = | :0>: Assign PW<br>1-2 for input pin<br>Input tied to RF<br>Input tied to CM<br>Input tied to Vs | selection nur<br>PI181<br>MP1 |                  | o the Correspor | nding RPn Pin b | bits  |

#### REGISTER 11-13: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-14: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| R/W-0                        | R/W-0                                                | R/W-0                                                                        | R/W-0                                         | R/W-0                            | R/W-0            | R/W-0                       | R/W-0 |

|------------------------------|------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------|------------------|-----------------------------|-------|

|                              |                                                      |                                                                              | DTCM                                          | P1R<7:0>                         |                  |                             |       |

| bit 15                       |                                                      |                                                                              |                                               |                                  |                  |                             | bit 8 |

|                              |                                                      |                                                                              |                                               |                                  |                  |                             |       |

| U-0                          | U-0                                                  | U-0                                                                          | U-0                                           | U-0                              | U-0              | U-0                         | U-0   |

|                              |                                                      | _                                                                            | _                                             |                                  |                  |                             | —     |

| bit 7                        |                                                      |                                                                              |                                               |                                  |                  |                             | bit 0 |

|                              |                                                      |                                                                              |                                               |                                  |                  |                             |       |

| Legend:                      |                                                      |                                                                              |                                               |                                  |                  |                             |       |

|                              |                                                      |                                                                              |                                               |                                  |                  |                             |       |

| R = Readabl                  | e bit                                                | W = Writable                                                                 | bit                                           | U = Unimpler                     | mented bit, read | <b>l as</b> '0'             |       |

| R = Readabl<br>-n = Value at |                                                      | W = Writable<br>'1' = Bit is set                                             |                                               | U = Unimpler<br>'0' = Bit is cle |                  | l as '0'<br>x = Bit is unkr | nown  |

|                              | DTCMP1R<<br>(see Table 1<br>10110101 =               | '1' = Bit is set<br>7:0>: Assign PV<br>1-2 for input pin<br>Input tied to RF | VM Dead-Tirr<br>selection nur<br>PI181        | '0' = Bit is cle                 | ared             | x = Bit is unkr             | -     |

| -n = Value at                | DTCMP1R<<br>(see Table 1<br>10110101 =<br>00000001 = | '1' = Bit is set<br>7:0>: Assign PV<br>1-2 for input pin                     | WM Dead-Tirr<br>selection nur<br>PI181<br>MP1 | '0' = Bit is cle                 | ared             | x = Bit is unkr             | -     |

bit 7-0 Unimplemented: Read as '0'

#### 15.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70000352) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

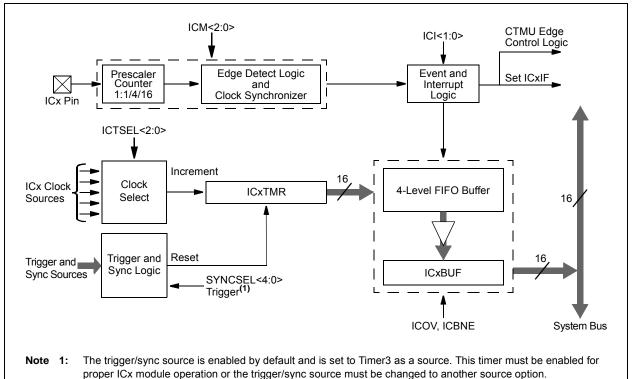

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EVXXXGM00X/10X family devices support 4 input capture channels.

Key features of the input capture module include:

- Hardware-Configurable for 32-Bit Operation in All Modes by Cascading Two Adjacent modules

- Synchronous and Trigger Modes of Output Compare Operation, with up to 31 User-Selectable Trigger/Sync Sources Available

- A 4-Level FIFO Buffer for Capturing and Holding Timer Values for Several Events

- Configurable Interrupt Generation

- Up to Six Clock Sources Available for Each Module, Driving a Separate Internal 16-Bit Counter

Figure 15-1 shows a block diagram of the Input capture module.

#### FIGURE 15-1: INPUT CAPTURE x MODULE BLOCK DIAGRAM

#### REGISTER 15-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits <sup>(4)</sup>                                                                            |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 11111 = Reserved                                                                                                                                                           |

|         | 11110 = Reserved                                                                                                                                                           |

|         | 1110 = Reserved                                                                                                                                                            |

|         | 11100 = CTMU trigger is the source for the capture timer synchronization                                                                                                   |

|         | 11011 = ADC1 interrupt is the source for the capture timer synchronization <sup>(5)</sup>                                                                                  |

|         | 11010 = Analog Comparator 3 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11001 = Analog Comparator 2 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 11000 = Analog Comparator 1 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10111 = Analog Comparator 5 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10110 = Analog Comparator 4 is the source for the capture timer synchronization <sup>(5)</sup>                                                                             |

|         | 10101 = Reserved                                                                                                                                                           |

|         | 10100 = Reserved                                                                                                                                                           |

|         | 10011 = Input Capture 4 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10010 = Input Capture 3 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10001 = Input Capture 2 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 10000 = Input Capture 1 interrupt is the source for the capture timer synchronization                                                                                      |

|         | 01111 = GP Timer5 is the source for the capture timer synchronization                                                                                                      |

|         | 01110 = GP Timer4 is the source for the capture timer synchronization                                                                                                      |

|         | 01101 = GP Timer3 is the source for the capture timer synchronization                                                                                                      |

|         | 01100 = GP Timer2 is the source for the capture timer synchronization                                                                                                      |

|         | 01011 = GP Timer1 is the source for the capture timer synchronization                                                                                                      |

|         | 01010 = Reserved                                                                                                                                                           |

|         | 01001 = Reserved                                                                                                                                                           |

|         | 01000 = Input Capture 4 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00111 = Input Capture 3 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00110 = Input Capture 2 is the source for the capture timer synchronization <sup>(6)</sup>                                                                                 |

|         | 00101 = Input Capture 1 is the source for the capture timer synchronization <sup>(6)</sup><br>00100 = Output Compare 4 is the source for the capture timer synchronization |

|         | 00011 = Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00011 – Output Compare 3 is the source for the capture timer synchronization                                                                                               |

|         | 00001 = Output Compare 1 is the source for the capture timer synchronization                                                                                               |

|         | 00000 = Reserved                                                                                                                                                           |

|         |                                                                                                                                                                            |

| Note 1: | The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.                                                                                              |

- **Note 1:** The IC32 bit in both the odd and even ICx must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by the SYNCSEL<4:0> bits); it can be read, set and cleared in software.

- 4: Do not use the ICx module as its own sync or trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: When the source ICx timer rolls over, then in the next clock cycle, trigger or synchronization occurs.

#### **REGISTER 16-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output sets high when OCxTMR = OCxR and sets low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output sets high when OCxTMR = 0 and sets low when OCxTMR =  $OCxR^{(1)}$

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits 11111 = OCxRS compare event is used for synchronization 11110 = INT2 is the source for compare timer synchronization 11101 = INT1 is the source for compare timer synchronization 11100 = CTMU Trigger is the source for compare timer synchronization 11011 = ADC1 interrupt is the source for compare timer synchronization 11010 = Analog Comparator 3 is the source for compare timer synchronization 11001 = Analog Comparator 2 is the source for compare timer synchronization 11000 = Analog Comparator 1 is the source for compare timer synchronization 10111 = Analog Comparator 5 is the source for compare timer synchronization 10110 = Analog Comparator 4 is the source for compare timer synchronization 10101 = Capture timer is unsynchronized 10100 = Capture timer is unsynchronized 10011 = Input Capture 4 interrupt is the source for compare timer synchronization 10010 = Input Capture 3 interrupt is the source for compare timer synchronization 10001 = Input Capture 2 interrupt is the source for compare timer synchronization 10000 = Input Capture 1 interrupt is the source for compare timer synchronization 01111 = GP Timer5 is the source for compare timer synchronization 01110 = GP Timer4 is the source for compare timer synchronization 01101 = GP Timer3 is the source for compare timer synchronization 01100 = GP Timer2 is the source for compare timer synchronization 01011 = GP Timer1 is the source for compare timer synchronization 01010 = Compare timer is unsynchronized 01001 = Compare timer is unsynchronized 01000 = Capture timer is unsynchronized 00101 = Compare timer is unsynchronized 00100 = Output Compare 4 is the source for compare timer synchronization<sup>(1,2)</sup> 00011 = Output Compare 3 is the source for compare timer synchronization<sup>(1,2)</sup> 00010 = Output Compare 2 is the source for compare timer synchronization<sup>(1,2)</sup> 00001 = Output Compare 1 is the source for compare timer synchronization<sup>(1,2)</sup>

- 00000 = Compare timer is unsynchronized

- **Note 1:** Do not use the OCx module as its own synchronization or trigger source.

- 2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

#### REGISTER 17-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

| R/W-1                                                                | R/W-1 | R/W-1            | R/W-1 | R/W-1                | R/W-1 | R/W-1           | R/W-1 |

|----------------------------------------------------------------------|-------|------------------|-------|----------------------|-------|-----------------|-------|

|                                                                      |       |                  | PTPE  | R<15:8>              |       |                 |       |

| bit 15                                                               |       |                  |       |                      |       |                 | bit 8 |

|                                                                      |       |                  |       |                      |       |                 |       |

| R/W-1                                                                | R/W-1 | R/W-1            | R/W-1 | R/W-1                | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |                  | PTPE  | R<7:0>               |       |                 |       |

| bit 7                                                                |       |                  |       |                      |       |                 | bit 0 |

|                                                                      |       |                  |       |                      |       |                 |       |

| Legend:                                                              |       |                  |       |                      |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                      |       |                 |       |

| -n = Value at POR                                                    |       | '1' = Bit is set |       | '0' = Bit is cleared |       | x = Bit is unkr | nown  |

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

#### REGISTER 17-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0                                                                | R/W-0 | R/W-0                             | R/W-0                         | R/W-0                                                                                                 | R/W-0                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------------------------------------------------|-------|-----------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                      |       | SEVTC                             | MP<15:8>                      |                                                                                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                      |       |                                   |                               |                                                                                                       |                                                                                                       | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                      |       |                                   |                               |                                                                                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| R/W-0                                                                | R/W-0 | R/W-0                             | R/W-0                         | R/W-0                                                                                                 | R/W-0                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                      |       | SEVTO                             | CMP<7:0>                      |                                                                                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                      |       |                                   |                               |                                                                                                       |                                                                                                       | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                      |       |                                   |                               |                                                                                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                      |       |                                   |                               |                                                                                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                                   |                               |                                                                                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| -n = Value at POR                                                    |       | '1' = Bit is set                  |                               | '0' = Bit is cleared                                                                                  |                                                                                                       | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                      | R/W-0 | R/W-0 R/W-0<br>it W = Writable bi | SEVTC<br>R/W-0 R/W-0<br>SEVTC | SEVTCMP<15:8>           R/W-0         R/W-0         R/W-0           SEVTCMP<7:0>         SEVTCMP<7:0> | SEVTCMP<15:8>           R/W-0         R/W-0         R/W-0           SEVTCMP<7:0>         SEVTCMP<7:0> | SEVTCMP<15:8>           R/W-0         R/W-0         R/W-0         R/W-0           SEVTCMP<7:0>         Image: Several content of the second content of th |  |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

# dsPIC33EVXXXGM00X/10X FAMILY

#### REGISTER 17-12: TRGCONX: PWMx TRIGGER CONTROL REGISTER

| R/W-0        | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0 |  |

|--------------|---------|---------|---------|-----|-----|-----|-----|--|

| TRGDIV3      | TRGDIV2 | TRGDIV1 | TRGDIV0 | —   | —   | —   | —   |  |

| bit 15 bit 8 |         |         |         |     |     |     |     |  |

| U-0   | U-0                                                   | R/W-0 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0 |

|-------|-------------------------------------------------------|-------|-------------------------|-------------------------|-------------------------|-------------------------|-------|

| —     | — TRGSTRT5 <sup>(1)</sup> TRGSTRT4 <sup>(1)</sup> TRG |       | TRGSTRT3 <sup>(1)</sup> | TRGSTRT2 <sup>(1)</sup> | TRGSTRT1 <sup>(1)</sup> | TRGSTRT0 <sup>(1)</sup> |       |

| bit 7 |                                                       |       |                         |                         |                         |                         | bit 0 |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

#### bit 15-12 TRGDIV<3:0>: Trigger Output Divider bits

- 1111 = Triggers output for every 16th trigger event

- 1110 = Triggers output for every 15th trigger event

- 1101 = Triggers output for every 14th trigger event

- 1100 = Triggers output for every 13th trigger event

- 1011 = Triggers output for every 12th trigger event

- 1010 = Triggers output for every 11th trigger event

- 1001 = Triggers output for every 10th trigger event

- 1000 = Triggers output for every 9th trigger event

- 0111 = Triggers output for every 8th trigger event

- 0110 = Triggers output for every 7th trigger event

- 0101 = Triggers output for every 6th trigger event

- 0100 = Triggers output for every 5th trigger event 0011 = Triggers output for every 4th trigger event

- 0010 = Triggers output for every 3rd trigger event

- 0001 = Triggers output for every 2nd trigger event

- 0000 = Triggers output for every trigger event

- bit 11-6 **Unimplemented:** Read as '0'

#### bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits<sup>(1)</sup>

111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled

- •

- •