Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm102-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

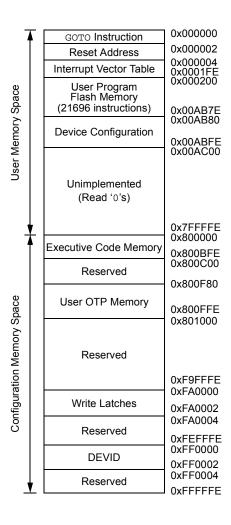

**Note 1:** Memory areas are not shown to scale.

### 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the SSP (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EVXXXGM00X/10X family devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within the Data Space.

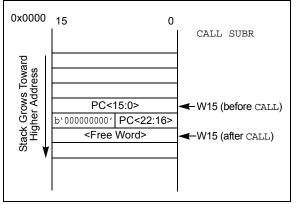

The SSP always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-14 illustrates how it predecrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-14. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register (SR). This allows the contents of SRL to be preserved automatically during interrupt processing.

- Note 1: To maintain system SSP (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment.

#### FIGURE 4-14:

#### CALL STACK FRAME

### 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-45 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where, Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

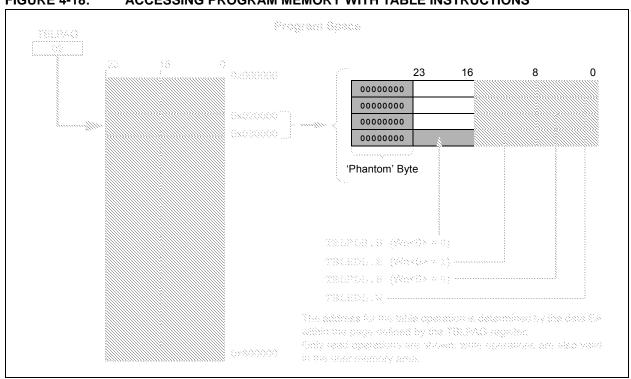

#### 4.7.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through the Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. The TBLRDL and TBLWTL instructions access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>).

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

Similarly, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space. Accessing the program memory with table instructions is shown in Figure 4-18.

### FIGURE 4-18: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0             | U-0                                                              | U-0              | U-0   | U-0                                     | U-0 | U-0 | U-0   |

|-----------------|------------------------------------------------------------------|------------------|-------|-----------------------------------------|-----|-----|-------|

| —               | —                                                                | —                | _     | —                                       | —   | —   | —     |

| bit 15          | •                                                                |                  |       |                                         |     |     | bit 8 |

|                 |                                                                  |                  |       |                                         |     |     |       |

| W-0             | W-0                                                              | W-0              | W-0   | W-0                                     | W-0 | W-0 | W-0   |

|                 |                                                                  |                  | NVMKE | Y<7:0>                                  |     |     |       |

| bit 7           |                                                                  |                  |       |                                         |     |     | bit 0 |

|                 |                                                                  |                  |       |                                         |     |     |       |

| Legend:         |                                                                  |                  |       |                                         |     |     |       |

| R = Readable    | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                                         |     |     |       |

| -n = Value at F | POR                                                              | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |     |     |       |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: NVM Key Register bits (write-only)

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel or channels are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA Channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU Interrupt after Half or Full Block Transfer Complete

- Byte or Word Transfers

- · Fixed Priority Channel Arbitration

- Manual (software) or Automatic (peripheral DMA requests) Transfer Initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer complete)

- DMA Request for Each Channel can be Selected from any Supported Interrupt Source

- Debug Support Features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA<br>Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |  |

|----------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--|

| External Interrupt 0 (INT0)      | 0000000                              | —                                                       | —                                                      |  |

| Input Capture 1 (IC1)            | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |  |

| Input Capture 2 (IC2)            | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |  |

| Input Capture 3 (IC3)            | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |  |

| Input Capture 4 (IC4)            | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |  |

| Output Compare 1 (OC1)           | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |  |

| Output Compare 2 (OC2)           | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |  |

| Output Compare 3 (OC3)           | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |  |

| Output Compare 4 (OC4)           | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |  |

| Timer2 (TMR2)                    | 00000111                             | _                                                       | _                                                      |  |

| Timer3 (TMR3)                    | 00001000                             | —                                                       | —                                                      |  |

| Timer4 (TMR4)                    | 00011011                             | —                                                       | _                                                      |  |

| Timer5 (TMR5)                    | 00011100                             | —                                                       | —                                                      |  |

| SPI1 Transfer Done               | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |  |

| SPI2 Transfer Done               | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |  |

| UART1 Receiver (UART1RX)         | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |  |

| UART1 Transmitter (UART1TX)      | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |  |

| UART2 Receiver (UART2RX)         | 00011110                             | 0x0236 (U2RXREG)                                        | —                                                      |  |

| UART2 Transmitter (UART2TX)      | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |  |

| RX Data Ready (CAN1)             | 00100010                             | 0x0440 (C1RXD)                                          | —                                                      |  |

| TX Data Request (CAN1)           | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |  |

| ADC1 Convert Done (ADC1)         | 00001101                             | 0x0300 (ADC1BUF0)                                       | _                                                      |  |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

# **REGISTER 9-2:** CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

- **Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register resets only on a Power-on Reset (POR).

- **3:** DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

### 11.5.5.1 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-to-one, and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

| Function     | RPnR<5:0> | Output Name                                   |

|--------------|-----------|-----------------------------------------------|

| Default Port | 000000    | RPn tied to Default Pin                       |

| U1TX         | 000001    | RPn tied to UART1 Transmit                    |

| U2TX         | 000011    | RPn tied to UART2 Transmit                    |

| SDO2         | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2         | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2          | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX         | 001110    | RPn tied to CAN1 Transmit                     |

| OC1          | 010000    | RPn tied to Output Compare 1 Output           |

| OC2          | 010001    | RPn tied to Output Compare 2 Output           |

| OC3          | 010010    | RPn tied to Output Compare 3 Output           |

| OC4          | 010011    | RPn tied to Output Compare 4 Output           |

| C10UT        | 011000    | RPn tied to Comparator Output 1               |

| C2OUT        | 011001    | RPn tied to Comparator Output 2               |

| C3OUT        | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1       | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| REFCLKO      | 110001    | RPn tied to Reference Clock Output            |

| C4OUT        | 110010    | RPn tied to Comparator Output 4               |

| C5OUT        | 110011    | RPn tied to Comparator Output 5               |

| SENT1        | 111001    | RPn tied to SENT Out 1                        |

| SENT2        | 111010    | RPn tied to SENT Out 2                        |

|--|

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| _       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       | ·      |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | U1RXI | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>l as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

bit 7-0 U1RXR<7:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 • • • • • • • • •

```

00000000 = Input tied to Vss

```

### REGISTER 11-9: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0               | U-0    | U-0              | U-0   | U-0                        | U-0   | U-0                | U-0   |

|-------------------|--------|------------------|-------|----------------------------|-------|--------------------|-------|

| _                 | _      | —                |       | _                          | _     | _                  | _     |

| bit 15            | -<br>- |                  |       |                            |       |                    | bit 8 |

| R/W-0             | R/W-0  | R/W-0            | R/W-0 | R/W-0                      | R/W-0 | R/W-0              | R/W-0 |

|                   |        |                  | U2R>  | (R<7:0>                    |       |                    |       |

| bit 7             |        |                  |       |                            |       |                    | bit 0 |

| Legend:           |        |                  |       |                            |       |                    |       |

| R = Readable bit  |        | W = Writable bit |       | U = Unimplemented bit, rea |       | id as '0'          |       |

| -n = Value at POR |        | '1' = Bit is set |       | '0' = Bit is cleared       |       | x = Bit is unknown |       |

| • • • • • • • • • • • • • • • • • • • •                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>U2RXR&lt;7:0&gt;:</b> Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

| 10110101 = Input tied to RPI181                                                                                                         |

| •                                                                                                                                       |

| •                                                                                                                                       |

| •                                                                                                                                       |

| 00000001 = Input tied to CMP1<br>00000000 = Input tied to Vss                                                                           |

|                                                                                                                                         |

# 17.0 HIGH-SPEED PWM MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices support a dedicated Pulse-Width Modulation (PWM) module with up to 6 outputs.

The high-speed PWMx module consists of the following major features:

- Three PWM Generators

- Two PWM Outputs per PWM Generator

- Individual Period and Duty Cycle for each PWM Pair

- Duty Cycle, Dead Time, Phase Shift and Frequency Resolution of 8.32 ns

- Independent Fault and Current-Limit Inputs for Six PWM Outputs

- Redundant Output

- Center-Aligned PWM mode

- Output Override Control

- Chop mode (also known as Gated mode)

- Special Event Trigger

- Prescaler for Input Clock

- PWMxL and PWMxH Output Pin Swapping

- Independent PWM Frequency, Duty Cycle and Phase-Shift Changes for each PWM Generator

- Dead-Time Compensation

- Enhanced Leading-Edge Blanking (LEB) Functionality

- Frequency Resolution Enhancement

- PWM Capture Functionality

**Note:** In Edge-Aligned PWM mode, the duty cycle, dead time, phase shift and frequency resolution are 8.32 ns at 60 MIPS.

The high-speed PWMx module contains up to three PWM generators. Each PWM generator provides two PWM outputs: PWMxH and PWMxL. The master time base generator provides a synchronous signal as a common time base to synchronize the various PWM outputs. The individual PWM outputs are available on the output pins of the device. The input Fault signals and current-limit signals, when enabled, can monitor and protect the system by placing the PWM outputs into a known "safe" state.

Each PWMx can generate a trigger to the ADC module to sample the analog signal at a specific instance during the PWM period. In addition, the high-speed PWMx module also generates a Special Event Trigger to the ADC module based on the master time base.

The high-speed PWMx module can synchronize itself with an external signal or can act as a synchronizing source to any external device. The SYNCI1 input pin, that utilizes PPS, can synchronize the high-speed PWMx module with an external signal. The SYNCO1 pin is an output pin that provides a synchronous signal to an external device.

Figure 17-1 illustrates an architectural overview of the high-speed PWMx module and its interconnection with the CPU and other peripherals.

### 17.1 PWM Faults

The PWMx module incorporates multiple external Fault inputs as follows:

- FLT1 and FLT2, available on 28-pin, 44-pin and 64-pin packages, which are remappable using the PPS feature

- FLT3, available on 44-pin and 64-pin packages, which is available as a fixed pin

- FLT4-FLT8, available on 64-pin packages, which are available as fixed pins

- · FLT32 is available on a fixed pin on all devices

These Faults provide a safe and reliable way to safely shut down the PWM outputs when the Fault input is asserted.

#### 17.1.1 PWM FAULTS AT RESET

During any Reset event, the PWMx module maintains ownership of the Class B Fault, FLT32. At Reset, this Fault is enabled in Latched mode to ensure the fail-safe power-up of the application. The application software must clear the PWM Fault before enabling the highspeed motor control PWMx module. To clear the Fault condition, the FLT32 pin must first be pulled low externally or the internal pull-down resistor in the CNPDx register can be enabled.

**Note:** The Fault mode may be changed using the FLTMOD<1:0> bits (FCLCONx<1:0>), regardless of the state of FLT32.

### 17.2 **PWM Resources**

Many useful resources are provided on the main product page on the Microchip web site (www.microchip.com) for the devices listed in this data sheet. This product page contains the latest updates and additional information.

Note: In case the above link is not accessible, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 17.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 20.3 Receive Mode

The module can be configured for receive operation by setting the RCVEN (SENTxCON1<11>) bit. The time between each falling edge is compared to SYNCMIN<15:0> (SENTxCON3<15:0>) and SYNCMAX<15:0> (SENTxCON2<15:0>), and if the measured time lies between the minimum and maximum limits, the module begins to receive data. The validated Sync time is captured in the SENTxSYNC register and the tick time is calculated. Subsequent falling edges are verified to be within the valid data width and the data is stored in the SENTxDATH/L register. An interrupt event is generated at the completion of the message and the user software should read the SENTx Data register before the reception of the next nibble. The equation for SYNCMIN<15:0> and SYNCMAX<15:0> is shown in Equation 20-3.

#### EQUATION 20-3: SYNCMIN<15:0> AND SYNCMAX<15:0> CALCULATIONS

$TTICK = TCLK \bullet (TICKTIME < 15:0 > + 1)$

FRAMETIME<15:0> = TTICK/TFRAME

SyncCount = 8 x FRCV x TTICK

SYNCMIN<15:0> = 0.8 x SyncCount

SYNCMAX<15:0> = 1.2 x SyncCount

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 \ge 848 + 12N$

#### Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6  $F_{RCV}$  = FCY x prescaler  $T_{CLK}$  = FCY/Prescaler

For TTICK = 3.0  $\mu$ s and FCLK = 4 MHz, SYNCMIN<15:0> = 76.

| Note: | To ensure a Sync period can be identified, |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | the value written to SYNCMIN<15:0>         |  |  |  |  |  |  |  |  |

|       | must be less than the value written to     |  |  |  |  |  |  |  |  |

|       | SYNCMAX<15:0>.                             |  |  |  |  |  |  |  |  |

### 20.3.1 RECEIVE MODE CONFIGURATION

#### 20.3.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 1 for Receive mode.

- 2. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 3. Write CRCEN (SENTxCON1<8>) for hardware or software CRC validation.

- 4. Write PPP (SENTxCON1<7>) = 1 if pause pulse is present.

- 5. Write SENTxCON2 with the value of SYNCMAXx (Nominal Sync Period + 20%).

- Write SENTxCON3 with the value of SYNCMINx (Nominal Sync Period – 20%).

- 7. Enable interrupts and set interrupt priority.

- 8. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

The data should be read from the SENTxDATH/L register after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt trigger.

| U-0                     | U-0           | R-0                                     | R-0              | R-0              | R-0                                    | R-0             | R-0   |

|-------------------------|---------------|-----------------------------------------|------------------|------------------|----------------------------------------|-----------------|-------|

| _                       | _             | TXBO                                    | TXBP             | RXBP             | TXWAR                                  | RXWAR           | EWARN |

| bit 15                  |               |                                         |                  |                  | 1                                      |                 | bit 8 |

|                         |               |                                         |                  |                  |                                        |                 |       |

| R/C-0                   | R/C-0         | R/C-0                                   | U-0              | R/C-0            | R/C-0                                  | R/C-0           | R/C-0 |

| IVRIF                   | WAKIF         | ERRIF                                   | _                | FIFOIF           | RBOVIF                                 | RBIF            | TBIF  |

| bit 7                   |               |                                         |                  |                  |                                        |                 | bit ( |

|                         |               | 0 10/-:t-bla                            | h:t ht a         |                  |                                        |                 |       |

| Legend:<br>R = Readable | hit           | W = Writable                            | -                |                  | n to clear the bit<br>mented bit, read |                 |       |

| -n = Value at l         |               | '1' = Bit is set                        |                  | '0' = Bit is cle | -                                      | x = Bit is unkr |       |

|                         | FOR           |                                         |                  |                  | careu                                  | X - DILIS UIKI  |       |

| bit 15-14               | Unimplemer    | nted: Read as '                         | 0'               |                  |                                        |                 |       |

| bit 13                  | -             | smitter in Error                        |                  | bit              |                                        |                 |       |

|                         | 1 = Transmit  | ter is in Bus Of<br>ter is not in Bus   | fstate           |                  |                                        |                 |       |

| bit 12                  | TXBP: Trans   | mitter in Error                         | State Bus Pas    | sive bit         |                                        |                 |       |

|                         |               | ter is in Bus Pa<br>ter is not in Bus   |                  | e                |                                        |                 |       |

| bit 11                  |               | iver in Error Sta                       |                  |                  |                                        |                 |       |

|                         |               | is in Bus Pass<br>is not in Bus P       |                  |                  |                                        |                 |       |

| bit 10                  | TXWAR: Tra    | nsmitter in Erro                        | or State Warni   | ng bit           |                                        |                 |       |

|                         |               | ter is in Error W<br>ter is not in Erro |                  | ate              |                                        |                 |       |

| bit 9                   | RXWAR: Re     | ceiver in Error                         | State Warning    | bit              |                                        |                 |       |

|                         |               | is in Error War                         | •                |                  |                                        |                 |       |

| <b>L</b> H 0            |               | is not in Error                         | •                |                  | . 1. 14                                |                 |       |

| bit 8                   |               | insmitter or Red<br>ter or receiver i   |                  | •                | DIT                                    |                 |       |

|                         |               | ter or receiver i                       |                  |                  |                                        |                 |       |

| bit 7                   |               | d Message Inte                          |                  |                  |                                        |                 |       |

|                         |               | request has oc<br>request has no        |                  |                  |                                        |                 |       |

| bit 6                   | WAKIF: Bus    | Wake-up Activ                           | ity Interrupt FI | lag bit          |                                        |                 |       |

|                         |               | request has oc<br>request has no        |                  |                  |                                        |                 |       |

| bit 5                   | ERRIF: Error  | r Interrupt Flag                        | bit (multiple s  | ources in CxIN   | TF<13:8> regist                        | ter)            |       |

|                         |               | request has oc<br>request has no        |                  |                  |                                        |                 |       |

| bit 4                   | Unimplemer    | nted: Read as '                         | 0'               |                  |                                        |                 |       |

| bit 3                   | FIFOIF: FIFO  | O Almost Full In                        | terrupt Flag b   | it               |                                        |                 |       |

|                         |               | request has oc<br>request has no        |                  |                  |                                        |                 |       |

| bit 2                   | RBOVIF: RX    | Buffer Overflo                          | w Interrupt Fla  | ag bit           |                                        |                 |       |

|                         | 1 = Interrupt | request has as                          | ourrod           |                  |                                        |                 |       |

## REGISTER 22-6: CXINTF: CANX INTERRUPT FLAG REGISTER

### REGISTER 22-22: CxRXFUL1: CANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0           | R/C-0 | R/C-0            | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|-----------------|-------|------------------|------------------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | RXFU             | L<15:8>           |                 |                 |       |

| bit 15          |       |                  |                  |                   |                 |                 | bit 8 |

|                 |       |                  |                  |                   |                 |                 |       |

| R/C-0           | R/C-0 | R/C-0            | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|                 |       |                  | RXFL             | JL<7:0>           |                 |                 |       |

| bit 7           |       |                  |                  |                   |                 |                 | bit 0 |

|                 |       |                  |                  |                   |                 |                 |       |

| Legend:         |       | C = Writable b   | oit, but only '( | )' can be written | to clear the b  | it              |       |

| R = Readable    | bit   | W = Writable     | bit              | U = Unimplem      | nented bit, rea | <b>d as</b> '0' |       |

| -n = Value at F | POR   | '1' = Bit is set |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 RXFUL<15:0>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### REGISTER 22-23: CxRXFUL2: CANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0                                                                      | R/C-0 | R/C-0          | R/C-0           | R/C-0             | R/C-0          | R/C-0 | R/C-0 |

|----------------------------------------------------------------------------|-------|----------------|-----------------|-------------------|----------------|-------|-------|

|                                                                            |       |                | RXFU            | _<31:24>          |                |       |       |

| bit 15                                                                     |       |                |                 |                   |                |       | bit 8 |

|                                                                            |       |                |                 |                   |                |       |       |

| R/C-0                                                                      | R/C-0 | R/C-0          | R/C-0           | R/C-0             | R/C-0          | R/C-0 | R/C-0 |

|                                                                            |       |                | RXFU            | _<23:16>          |                |       |       |

| bit 7                                                                      |       |                |                 |                   |                |       | bit 0 |

|                                                                            |       |                |                 |                   |                |       |       |

| Legend:                                                                    |       | C = Writable b | it, but only '( | )' can be written | to clear the b | bit   |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |                |                 |                   |                |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |                 |                   |                |       | nown  |

bit 15-0 RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### REGISTER 25-4: CMxMSKSRC: COMPARATOR x MASK SOURCE SELECT CONTROL REGISTER (CONTINUED)

bit 3-0 SELSRCA<3:0>: Mask A Input Select bits

1111 = FLT4 1110 = FLT2

1101 = Reserved

1100 = Reserved

1011 = Reserved

- 1010 = Reserved

- 1001 = Reserved

- 1000 = Reserved

0111 = Reserved

0110 = Reserved

0101 = PWM3H

0100 = PWM3L

- 0011 = PWM2H

- 0010 = PWM2L

- 0001 = PWM1H 0000 = PWM1L

### TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CH        | ARACTERIS      | STICS                                   |                           | (unless otherv                         | perating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |               |       | or Industrial                                                               |

|--------------|----------------|-----------------------------------------|---------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No. | Symbol         | Charac                                  | cteristic <sup>(1)</sup>  | Min.                                   | Тур.                                                                                                                            | Max.          | Units | Conditions                                                                  |

| TB10         | T⊤xH           | TxCK High<br>Time                       | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N   |                                                                                                                                 | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB11         | ΤτχL           | TxCK Low<br>Time                        | Synchronous<br>mode       | Greater of:<br>20 or<br>(Tcy + 20)/N   |                                                                                                                                 | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB15         | ΤτχΡ           | TxCK Input<br>Period                    | Synchronous<br>mode       | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _                                                                                                                               | _             | ns    | N = Prescaler Value<br>(1, 8, 64, 256)                                      |

| TB20         | TCKEXT-<br>MRL | Delay from I<br>Clock Edge<br>Increment | External TxCK<br>to Timer | 0.75 Tcy + 40                          |                                                                                                                                 | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: These parameters are characterized but not tested in manufacturing.

### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA                                                                           | ARACTERIS | TICS                                       |               | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |               |       |            |                                        |

|----------------------------------------------------------------------------------|-----------|--------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|------------|----------------------------------------|

| Param<br>No. Symbol Characteristic <sup>(1)</sup>                                |           |                                            | Min.          | Тур.                                                                                                                                                                                                                                                                                | Max.          | Units | Conditions |                                        |

| TC10                                                                             | ТтхН      | TxCK High Synchronous<br>Time              |               | Tcy + 20                                                                                                                                                                                                                                                                            | —             | _     | ns         | Must also meet<br>Parameter TC15       |

| TC11                                                                             | ΤτxL      | TxCK Low<br>Time                           | Synchronous   | Tcy + 20                                                                                                                                                                                                                                                                            | _             | —     | ns         | Must also meet<br>Parameter TC15       |

| TC15                                                                             | ΤτχΡ      | TxCK InputSynchronous,Periodwith Prescaler |               | 2 Tcy + 40                                                                                                                                                                                                                                                                          | _             | —     | ns         | N = Prescaler Value<br>(1, 8, 64, 256) |

| TC20 TCKEXT-<br>MRL Delay from External TxCK<br>Clock Edge to Timer<br>Increment |           |                                            | 0.75 Tcy + 40 | —                                                                                                                                                                                                                                                                                   | 1.75 Tcy + 40 | ns    |            |                                        |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

| TABLE 31-4: | DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) |

|-------------|----------------------------------------------|

|-------------|----------------------------------------------|

| DC CHARACT       | ERISTICS      |      |       |                                         |  | <b>5V to 5.5V (unless otherwise stated)</b> $\leq$ +150°C for High Temperature |  |  |

|------------------|---------------|------|-------|-----------------------------------------|--|--------------------------------------------------------------------------------|--|--|

| Parameter<br>No. | Typical       | Мах  | Units | Units Conditions                        |  |                                                                                |  |  |

| Power-Down (     | Current (IPD) |      |       |                                         |  |                                                                                |  |  |

| HDC60e           | 1300          | 2500 | μA    | +150°C 5V Base Power-Down Current       |  |                                                                                |  |  |

| HDC61c           | 10            | 50   | μA    | +150°C 5V Watchdog Timer Current: ∆IwDT |  |                                                                                |  |  |

### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG        | CTERISTICS |     |       | •                 |  | (unless otherwise stated)<br>for High Temperature |  |  |

|------------------|------------|-----|-------|-------------------|--|---------------------------------------------------|--|--|

| Parameter<br>No. | Typical    | Max | Units | Conditions        |  |                                                   |  |  |

| HDC40e           | 2.6        | 5.0 | mA    | +150°C 5V 10 MIPS |  |                                                   |  |  |

| HDC42e           | 3.6        | 7.0 | mA    | +150°C 5V 20 MIPS |  |                                                   |  |  |

### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAG        | CTERISTICS |      |       | •                 |    | V (unless otherwise stated)<br>C for High Temperature |  |

|------------------|------------|------|-------|-------------------|----|-------------------------------------------------------|--|

| Parameter<br>No. | Typical    | Max  | Units | Conditions        |    |                                                       |  |

| HDC20e           | 5.9        | 8.0  | mA    | +150°C            | 5V | 10 MIPS                                               |  |

| HDC22e           | 10.3       | 15.0 | mA    | +150°C 5V 20 MIPS |    |                                                       |  |

| HDC23e           | 19.0       | 25.0 | mA    | +150°C 5V 40 MIPS |    |                                                       |  |

### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARAG        |               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |    |                    |            |  |  |  |

|------------------|---------------|------------------------------------------------------|-------|----|--------------------|------------|--|--|--|

| Parameter<br>No. | Typical Max D |                                                      |       |    |                    | Conditions |  |  |  |

| HDC73a           | 18.5          | 22.0                                                 | 1:2   | mA | 1450°C 51/ 40 MIDO |            |  |  |  |

| HDC73g           | 8.35          | 12.0                                                 | 1:128 | mA | +150°C 5V 40 MIPS  |            |  |  |  |

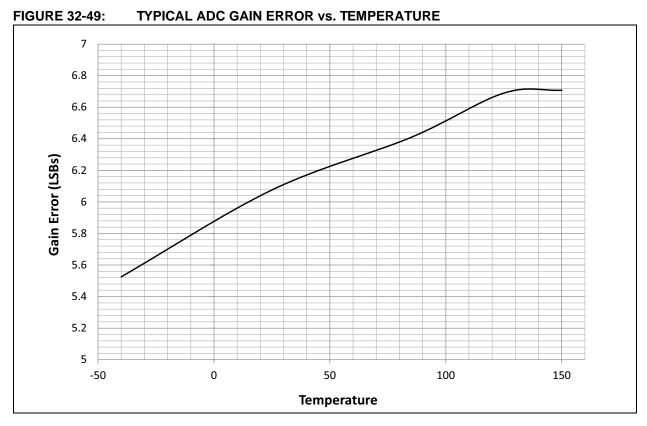

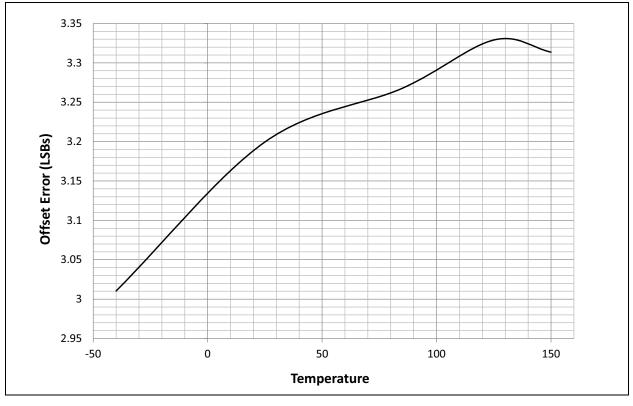

### 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

# 34.0 PACKAGING INFORMATION

## 34.1 Package Marking Information

### 28-Lead SPDIP (.300")

### 28-Lead SOIC (.300")

### 28-Lead SSOP

### 28-Lead QFN-S (6x6x0.9 mm)

Example

| Legenc | I: XXX<br>Y<br>YY<br>WW<br>NNN | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                      | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                            |

### Example

## Example

### Example

# APPENDIX A: REVISION HISTORY

## **Revision A (December 2013)**

This is the initial version of this document.

## Revision B (June 2014)

This revision incorporates the following updates:

- · Sections:

- Added Section 31.0 "High-Temperature Electrical Characteristics"

- Updated the "Power Management" section, the "Input/Output" section, Section 3.3

"Data Space Addressing", Section 4.2

"Data Address Space", Section 4.3.2

"Extended X Data Space", Section 4.6.1

"Bit-Reversed Addressing Implementation", Section 7.4.1 "INTCON1 through INTCON4", Section 11.7 "I/O Helpful Tips"

- Updated note in Section 17.0 "High-Speed PWM Module", Section 18.0 "Serial Peripheral Interface (SPI)", Section 27.8 "Code Protection and CodeGuard™ Security"

- Updated title of Section 20.0 "Single-Edge Nibble Transmission (SENT)"

- Updated Section 34.0 "Packaging Information". Deleted e3, Pb-free and Industrial (I) temperature range indication throughout the section, and updated the packaging diagrams

- Updated the "Product Identification System" section

- Registers:

- Updated Register 3-2, Register 7-2, Register 7-6, Register 9-2, Register 11-3, Register 14-1, Register 14-3, Register 14-11, Register 15-1, Register 22-4

- Figures:

- Added Figure 4-6, Figure 4-8, Figure 4-14, Figure 4-15, Figure 14-1, Figure 16-1, Figure 17-2, Figure 23-1, Figure 24-1

- Tables:

- Updated Table 1, Table 27-1, Table 27-2, Table 30-6, Table 30-7, Table 30-8, Table 30-9, Table 30-10, Table 30-11, Table 30-12, Table 30-38, Table 30-50, Table 30-53 and added Table 31-11,

- Changes to text and formatting were incorporated throughout the document

### **Revision C (November 2014)**

This revision incorporates the following updates:

- · Sections:

- Added note in Section 5.2 "RTSP Operation"

- Updated "Section 5.4 "Error Correcting Code (ECC)"

- Deleted 44-Terminal Very Thin Leadless Array Package (TL) - 6x6x0.9 mm Body With Exposed Pad (VTLA).

- Registers

- Updated Register 7-6

- Figures:

- Updated Figure 4-1, Figure 4-3, Figure 4-4

- · Tables:

- Updated Table 27-2, Table 31-13, Table 31-14, Table 31-15

- Added Table 31-16, Table 31-17

## **Revision D (April 2015)**

This revision incorporates the following updates:

- Sections:

- Updated the Clock Management, Timers/ Output Compare/Input Capture, Communication Interfaces and Input/Output sections at the beginning of the data sheet (Page 1 and Page 2).

- Updated all pin diagrams at the beginning of the data sheet (Page 4 through Page 9).

- Added Section 11.6 "High-Voltage Detect (HVD)"

- Updated Section 13.0 "Timer2/3 and Timer4/5"

- Corrects all Buffer heading numbers in Section 22.4 "CAN Message Buffers"

- Registers

- Updated Register 3-2, Register 25-2, Register 26-2

- Figures

- Updated Figure 26-1, Figure 30-5, Figure 30-32

- Tables

- Updated Table 1, Table 4-25, Table 30-10, Table 30-22, Table 30-53 and Table 31-8

- Changes to text and formatting were incorporated throughout the document

| SPI2 Slave Mode (Full-Duplex, CKE = 1,<br>CKP = 0, SMP = 0) |  |

|-------------------------------------------------------------|--|

| SPI2 Slave Mode (Full-Duplex, CKE = 1,                      |  |

| CKP = 1, SMP = 0)                                           |  |

| Timer1-Timer5 External Clock                                |  |

| UARTx I/O                                                   |  |

| U                                                           |  |

| UART                                                        |  |

| Control Registers                                      |     |  |  |  |

|--------------------------------------------------------|-----|--|--|--|

| Helpful Tips                                           |     |  |  |  |

| Universal Asynchronous Receiver                        |     |  |  |  |

| Transmitter (UART)                                     | 247 |  |  |  |

| Universal Asynchronous Receiver Transmitter. See UART. |     |  |  |  |

| User OTP Memory                                        | 324 |  |  |  |

| ۱/ |  |

|----|--|

| v  |  |

| Voltage Regulator (On-Chip) |          |  |  |

|-----------------------------|----------|--|--|

| W                           |          |  |  |

| Watchdog Timer (WDT)        | 317, 325 |  |  |

| Programming Considerations  | 325      |  |  |

| WWW Address                 | 493      |  |  |

| WWW, On-Line Support        | 11       |  |  |