#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm103-e-m5 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EVXXXGM00X/ 10X family is shown in Figure 3-2. All registers in the programmer's model are memory-mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register. In addition to the registers contained in the programmer's model, the dsPIC33EVXXXGM00X/10X family devices contain control registers for Modulo Addressing and Bit-Reversed Addressing, and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory-mapped, as shown in Table 4-1.

| TABLE 3-1: | PROGRAMMER'S MODEL REGISTER DESCRIPTIONS |

|------------|------------------------------------------|

|            |                                          |

| Register(s) Name                                  | Description                                               |

|---------------------------------------------------|-----------------------------------------------------------|

| W0 through W15 <sup>(1)</sup>                     | Working Register Array                                    |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 1                        |

| W0 through W14 <sup>(1)</sup>                     | Alternate Working Register Array 2                        |

| ACCA, ACCB                                        | 40-Bit DSP Accumulators                                   |

| PC                                                | 23-Bit Program Counter                                    |

| SR                                                | ALU and DSP Engine STATUS Register                        |

| SPLIM                                             | Stack Pointer Limit Value Register                        |

| TBLPAG                                            | Table Memory Page Address Register                        |

| DSRPAG                                            | Extended Data Space (EDS) Read Page Register              |

| RCOUNT                                            | REPEAT Loop Counter Register                              |

| DCOUNT                                            | DO Loop Count Register                                    |

| DOSTARTH <sup>(2)</sup> , DOSTARTL <sup>(2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH, DOENDL                                    | DO Loop End Address Register (High and Low)               |

| CORCON                                            | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: Memory-mapped W0 through W14 represents the value of the register in the currently active CPU context.

2: The DOSTARTH and DOSTARTL registers are read-only.

### 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33EVXXXGM00X/10X family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. The data for the ALU operation can come from the W register array or from the data memory, depending on the addressing mode of the instruction. Similarly, the output data from the ALU can be written to the W register array or a data memory location.

For information on the SR bits affected by each instruction, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes the single-cycle per bit of the divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.8 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON) as follows:

- Fractional or Integer DSP Multiply (IF)

- Signed, Unsigned or Mixed-Sign DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- · Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

# TABLE 3-2:DSP INSTRUCTIONSSUMMARY

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

| IABLE       | ABLE 4-3: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP |        |                                      |        |                                                                          |            |             |          |           |            |               |       |          |          |          |          |          |               |

|-------------|----------------------------------------------------------------|--------|--------------------------------------|--------|--------------------------------------------------------------------------|------------|-------------|----------|-----------|------------|---------------|-------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr.                                                          | Bit 15 | Bit 14                               | Bit 13 | Bit 12                                                                   | Bit 11     | Bit 10      | Bit 9    | Bit 8     | Bit 7      | Bit 6         | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IC1CON1     | 0140                                                           | _      | _                                    | ICSIDL | ICTSEL2                                                                  | ICTSEL1    | ICTSEL0     | —        | —         | —          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2     | 0142                                                           | _      | _                                    | _      | IC32 ICTRIG TRIGSTAT - SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SYNCSEL0 000D |            |             |          |           |            |               |       |          |          |          |          |          |               |

| IC1BUF      | 0144                                                           |        |                                      |        |                                                                          |            |             |          | Inp       | ut Capture | 1 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC1TMR      | 0146                                                           |        |                                      |        |                                                                          |            |             |          | Inp       | ut Capture | 1 Timer Regis | ster  |          |          |          |          |          | 0000          |

| IC2CON1     | 0148                                                           | _      | _                                    | ICSIDL | ICTSEL2                                                                  | ICTSEL1    | ICTSEL0     | -        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2     | 014A                                                           | _      | _                                    | _      | _                                                                        | _          | _           | -        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF      | 014C                                                           |        |                                      |        |                                                                          |            |             |          | Inp       | ut Capture | 2 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC2TMR      | 014E                                                           |        |                                      |        |                                                                          |            |             |          | Inp       | ut Capture | 2 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| IC3CON1     | 0150                                                           | _      | _                                    | ICSIDL | ICTSEL2                                                                  | ICTSEL1    | ICTSEL0     | -        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2     | 0152                                                           | _      | _                                    | _      | _                                                                        | _          | _           | _        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF      | 0154                                                           |        |                                      |        |                                                                          |            |             |          | Inp       | ut Capture | 3 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC3TMR      | 0156                                                           |        |                                      |        |                                                                          |            |             |          | Inp       | ut Capture | 3 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| IC4CON1     | 0158                                                           |        |                                      | ICSIDL | ICTSEL2                                                                  | ICTSEL1    | ICTSEL0     | _        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2     | 015A                                                           |        |                                      | —      | —                                                                        | _          | _           | _        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF      | 015C                                                           |        | Input Capture 4 Buffer Register xxxx |        |                                                                          |            |             |          |           |            |               |       |          |          |          |          |          |               |

| IC4TMR      | 015E                                                           |        | Input Capture 4 Timer Register 0000  |        |                                                                          |            |             |          |           |            |               |       |          |          |          |          |          |               |

| Lonondi     |                                                                |        |                                      | aati - | unimanlama                                                               | optod road | Loo '0' Boo | at value | ara ahawa | in hovedor | simal         |       |          |          |          |          |          |               |

#### TABLE 4-3: INDUT CARTINE 1 THROUGH INDUT CARTINE A REGISTER MAD

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: **I2C1 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                        | Bit 8 | Bit 7 | Bit 6 | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|------------------------------|-------|-------|-------|-------------|--------------|--------------|-------|-------|-------|---------------|

| I2C1CON1    | 0200  | I2CEN   | —      | I2CSIDL | SCLREL | STRICT | A10M   | DISSLW                       | SMEN  | GCEN  | STREN | ACKDT       | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1CON2    | 0202  | _       | _      | _       | _      | _      | _      | _                            | _     | _     | PCIE  | SCIE        | BOEN         | SDAHT        | SBCDE | AHEN  | DHEN  | 1000          |

| I2C1STAT    | 0204  | ACKSTAT | TRSTAT | ACKTIM  |        | _      | BCL    | GCSTAT                       | ADD10 | IWCOL | I2COV | D_A         | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 0206  |         |        |         |        | _      |        |                              |       |       |       | I2C1 Addr   | ess Register |              |       |       |       | 0000          |

| I2C1MSK     | 0208  |         |        |         |        | _      |        |                              |       |       | 12    | 2C1 Address | Mask Regis   | ster         |       |       |       | 0000          |

| I2C1BRG     | 020A  |         |        |         |        |        |        | Baud Rate Generator Register |       |       |       |             |              | 0000         |       |       |       |               |

| I2C1TRN     | 020C  |         |        |         |        | _      |        |                              |       |       |       |             | I2C1 Transr  | nit Register |       |       |       | OOFF          |

| I2C1RCV     | 020E  |         |        |         |        | _      |        | I2C1 Receive Register 0      |       |       |       |             |              |              | 0000  |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-11: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 1 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8     | Bit 7        | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|---------------|--------|--------|--------|--------|--------|--------|--------|-----------|--------------|---------|--------|--------|--------|--------|--------|--------|---------------|

|             | 0400-<br>041E |        |        |        |        |        |        |        | See defin | ition when W | /IN = x |        |        |        |        |        |        |               |

| C1BUFPNT1   | 0420          | F3BP3  | F3BP2  | F3BP1  | F3BP0  | F2BP3  | F2BP2  | F2BP1  | F2BP0     | F1BP3        | F1BP2   | F1BP1  | F1BP0  | F0BP3  | F0BP2  | F0BP1  | F0BP0  | 0000          |

| C1BUFPNT2   | 0422          | F7BP3  | F7BP2  | F7BP1  | F7BP0  | F6BP3  | F6BP2  | F6BP1  | F6BP0     | F5BP3        | F5BP2   | F5BP1  | F5BP0  | F4BP3  | F4BP2  | F4BP1  | F4BP0  | 0000          |

| C1BUFPNT3   | 0424          | F11BP3 | F11BP2 | F11BP1 | F11BP0 | F10BP3 | F10BP2 | F10BP1 | F10BP0    | F9BP3        | F9BP2   | F9BP1  | F9BP0  | F8BP3  | F8BP2  | F8BP1  | F8BP0  | 0000          |

| C1BUFPNT4   | 0426          | F15BP3 | F15BP2 | F15BP1 | F15BP0 | F14BP3 | F14BP2 | F14BP1 | F14BP0    | F13BP3       | F13BP2  | F13BP1 | F13BP0 | F12BP3 | F12BP2 | F12BP1 | F12BP0 | 0000          |

| C1RXM0SID   | 0430          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | —      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM0EID   | 0432          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXM1SID   | 0434          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM1EID   | 0436          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        | •      |        | xxxx          |

| C1RXM2SID   | 0438          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | MIDE   | _      | EID17  | EID16  | xxxx          |

| C1RXM2EID   | 043A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF0SID   | 0440          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF0EID   | 0442          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF1SID   | 0444          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF1EID   | 0446          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | •      |        | xxxx          |

| C1RXF2SID   | 0448          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | -      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF2EID   | 044A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF3SID   | 044C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF3EID   | 044E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF4SID   | 0450          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF4EID   | 0452          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF5SID   | 0454          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF5EID   | 0456          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF6SID   | 0458          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF6EID   | 045A          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF7SID   | 045C          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   |        | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF7EID   | 045E          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        | _      |        | xxxx          |

| C1RXF8SID   | 0460          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | _      | EID17  | EID16  | xxxx          |

| C1RXF8EID   | 0462          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF9SID   | 0464          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF9EID   | 0466          |        |        |        |        |        |        |        | E         | EID<15:0>    |         |        |        |        |        |        |        | xxxx          |

| C1RXF10SID  | 0468          | SID10  | SID9   | SID8   | SID7   | SID6   | SID5   | SID4   | SID3      | SID2         | SID1    | SID0   | _      | EXIDE  | —      | EID17  | EID16  | xxxx          |

| C1RXF10EID  | 046A          |        |        |        |        |        |        |        | E         | ID<15:0>     |         |        |        |        |        |        |        | xxxx          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-26: DMAC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6    | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|---------|----------|---------|---------|---------|---------|---------|---------|---------------|

| DMA0CON     | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _     | —       | _        | AMODE1  | AMODE0  | —       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ     | 0B02  | FORCE  | _      | _      | _      | _      | _      | -     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA0STAL    | 0B04  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STAH    | 0B06  | _      | _      | _      | _      | _      |        |       |       |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA0STBL    | 0B08  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STBH    | 0B0A  | _      | _      | —      | _      | _      |        | _     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA0PAD     | 0B0C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0CNT     | 0B0E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA1CON     | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA1REQ     | 0B12  | FORCE  | —      | —      | _      |        | -      | —     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA1STAL    | 0B14  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STAH    | 0B16  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA1STBL    | 0B18  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STBH    | 0B1A  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA1PAD     | 0B1C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1CNT     | 0B1E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA2CON     | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA2REQ     | 0B22  | FORCE  | —      | _      | —      | —      | _      | _     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA2STAL    | 0B24  |        |        |        | -      |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STAH    | 0B26  | —      | —      |        | _      |        | —      | —     | —     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA2STBL    | 0B28  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STBH    | 0B2A  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA2PAD     | 0B2C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2CNT     | 0B2E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA3CON     | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA3REQ     | 0B32  | FORCE  | —      | —      | _      |        | -      | —     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA3STAL    | 0B34  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STAH    | 0B36  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA3STBL    | 0B38  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STBH    | 0B3A  | —      | —      | _      |        |        | _      | —     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA3PAD     | 0B3C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3CNT     | 0B3E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMAPWC      | 0BF0  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       |         |         | PWCC    | )L<3:0> |         | 0000          |

| DMARQC      | 0BF2  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       | _       |         | RQCC    | )L<3:0> |         | 0000          |

| DMAPPS      | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _     | _       | _        | _       | _       |         | PPS     | Г<3:0>  |         | 0000          |

dsPIC33EVXXXGM00X/10X FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

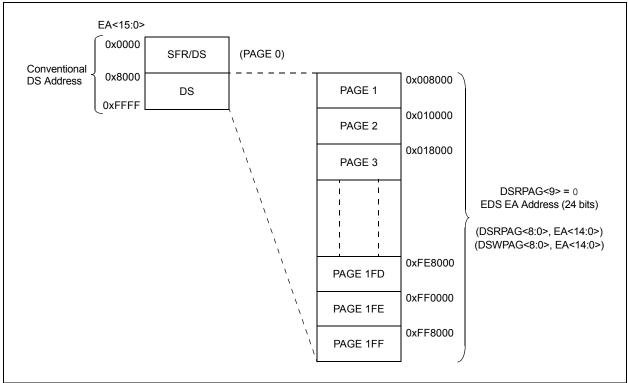

#### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

| R/W-0           | R/W-0                                    | R/W-0                                                                                           | R/W-0                         | R/W-0                              | R/W-0           | R/W-0              | R/W-0 |  |  |  |

|-----------------|------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------|-----------------|--------------------|-------|--|--|--|

|                 |                                          |                                                                                                 | SYNC                          | I1R<7:0>                           |                 |                    |       |  |  |  |

| bit 15          |                                          |                                                                                                 |                               |                                    |                 |                    | bit 8 |  |  |  |

| U-0             | U-0                                      | U-0                                                                                             | U-0                           | U-0                                | U-0             | U-0                | U-0   |  |  |  |

| _               | _                                        | _                                                                                               | _                             | _                                  |                 | _                  | —     |  |  |  |

| bit 7           |                                          |                                                                                                 |                               |                                    |                 |                    | bit C |  |  |  |

|                 |                                          |                                                                                                 |                               |                                    |                 |                    |       |  |  |  |

| Legend:         |                                          |                                                                                                 |                               |                                    |                 |                    |       |  |  |  |

| R = Readable    | bit                                      | W = Writable                                                                                    | bit                           | U = Unimplemented bit, read as '0' |                 |                    |       |  |  |  |

| -n = Value at F | POR                                      | '1' = Bit is set                                                                                |                               | '0' = Bit is cle                   | eared           | x = Bit is unknown |       |  |  |  |

| bit 15-8        | (see Table 1<br>10110101 =<br>00000001 = | :0>: Assign PW<br>1-2 for input pin<br>Input tied to RF<br>Input tied to CM<br>Input tied to Vs | selection nur<br>PI181<br>MP1 |                                    | o the Correspor | nding RPn Pin b    | bits  |  |  |  |

#### REGISTER 11-13: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-14: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| R/W-0                        | R/W-0                                                | R/W-0                                                                        | R/W-0                                         | R/W-0                              | R/W-0            | R/W-0                       | R/W-0 |  |  |  |

|------------------------------|------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------------------|-------|--|--|--|

|                              |                                                      |                                                                              | DTCM                                          | P1R<7:0>                           |                  |                             |       |  |  |  |

| bit 15                       |                                                      |                                                                              |                                               |                                    |                  |                             | bit 8 |  |  |  |

|                              |                                                      |                                                                              |                                               |                                    |                  |                             |       |  |  |  |

| U-0                          | U-0                                                  | U-0                                                                          | U-0                                           | U-0                                | U-0              | U-0                         | U-0   |  |  |  |

|                              |                                                      | _                                                                            | _                                             |                                    |                  |                             | —     |  |  |  |

| bit 7                        |                                                      |                                                                              |                                               |                                    |                  |                             | bit 0 |  |  |  |

|                              |                                                      |                                                                              |                                               |                                    |                  |                             |       |  |  |  |

| Legend:                      |                                                      |                                                                              |                                               |                                    |                  |                             |       |  |  |  |

|                              |                                                      |                                                                              |                                               | U = Unimplemented bit, read as '0' |                  |                             |       |  |  |  |

| R = Readabl                  | e bit                                                | W = Writable                                                                 | bit                                           | U = Unimpler                       | mented bit, read | <b>l as</b> '0'             |       |  |  |  |

| R = Readabl<br>-n = Value at |                                                      | W = Writable<br>'1' = Bit is set                                             |                                               | U = Unimpler<br>'0' = Bit is cle   |                  | l as '0'<br>x = Bit is unkr | nown  |  |  |  |

|                              | DTCMP1R<<br>(see Table 1<br>10110101 =               | '1' = Bit is set<br>7:0>: Assign PV<br>1-2 for input pin<br>Input tied to RF | VM Dead-Tirr<br>selection nur<br>PI181        | '0' = Bit is cle                   | ared             | x = Bit is unkr             | -     |  |  |  |

| -n = Value at                | DTCMP1R<<br>(see Table 1<br>10110101 =<br>00000001 = | '1' = Bit is set<br>7:0>: Assign PV<br>1-2 for input pin                     | WM Dead-Tirr<br>selection nur<br>PI181<br>MP1 | '0' = Bit is cle                   | ared             | x = Bit is unkr             | -     |  |  |  |

bit 7-0 Unimplemented: Read as '0'

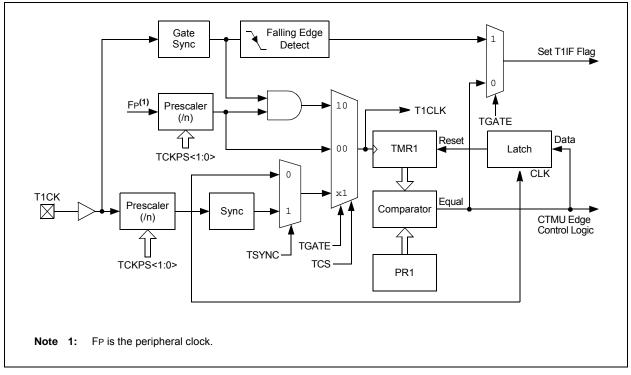

#### 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer that can operate as a free-running, interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be Operated in Asynchronous Counter mode from an External Clock Source

- The Timer1 External Clock Input (T1CK) can Optionally be Synchronized to the Internal Device Clock and the Clock Synchronization is Performed after the Prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FcY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit settings for different operating modes are given in Table 12-1.

| TABLE 12-1: | TIMER MODE SETTI | NGS |

|-------------|------------------|-----|

|-------------|------------------|-----|

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | x     |

| Gated Timer             | 0   | 1     | х     |

| Synchronous<br>Counter  | 1   | x     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

NOTES:

# dsPIC33EVXXXGM00X/10X FAMILY

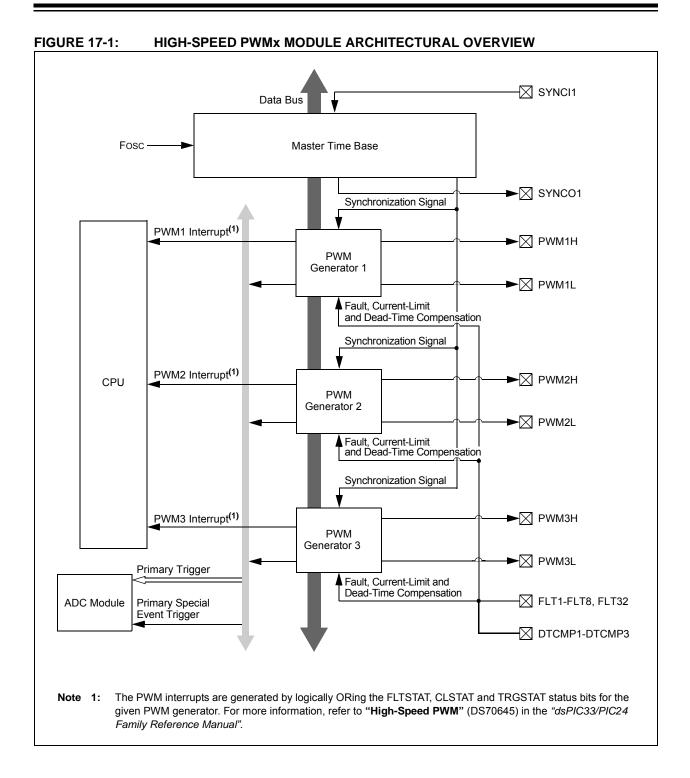

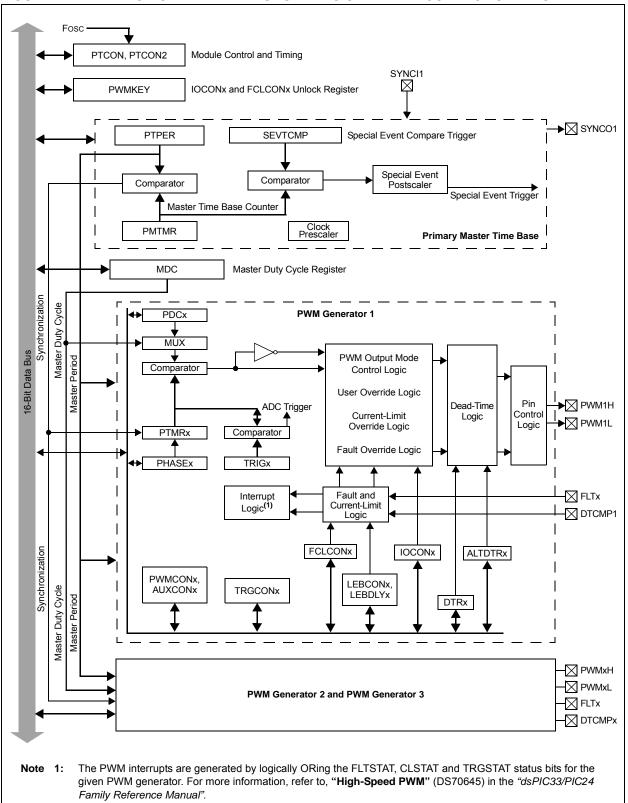

#### FIGURE 17-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EVXXXGM00X/10X device family offers two SPI modules on a single device, SPI1 and SPI2, that are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

**Note:** In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of this module, but results in a lower maximum speed. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of the following four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

**Note:** All of the 4 pins of the SPIx serial interface must be configured as digital in the ANSELx registers.

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

#### REGISTER 21-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                      |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | <ul> <li>1 = Baud rate measurement on the next character is enabled – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or has completed</li> </ul> |  |  |  |  |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                                     |  |  |  |  |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                         |  |  |  |  |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                                  |  |  |  |  |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                               |  |  |  |  |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                       |  |  |  |  |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                                    |  |  |  |  |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                                    |  |  |  |  |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                            |  |  |  |  |

| Note 1: | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the                                                                                                                                                                |  |  |  |  |

- "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- **3:** This feature is only available on 44-pin and 64-pin devices.

- **4:** This feature is only available on 64-pin devices.

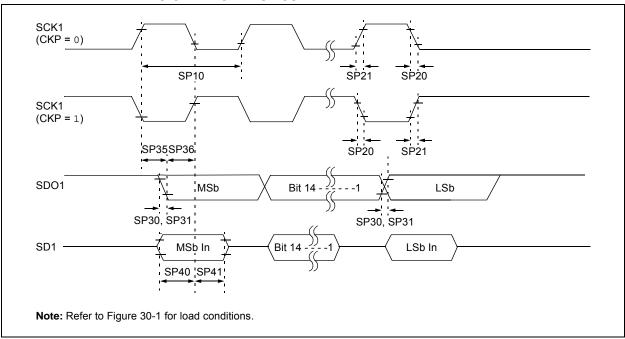

#### FIGURE 30-23: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

#### 32.12 VBOR

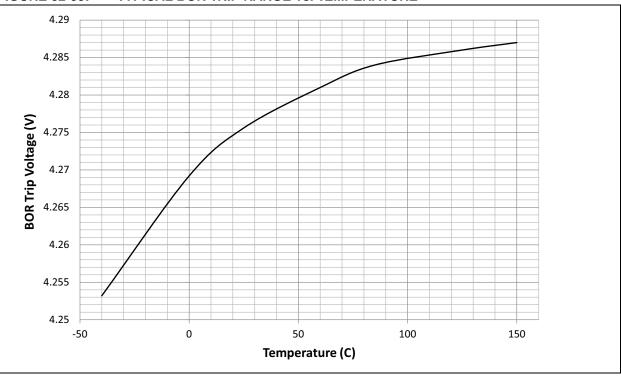

FIGURE 32-35: TYPICAL BOR TRIP RANGE vs. TEMPERATURE

### 32.13 RAM Retention

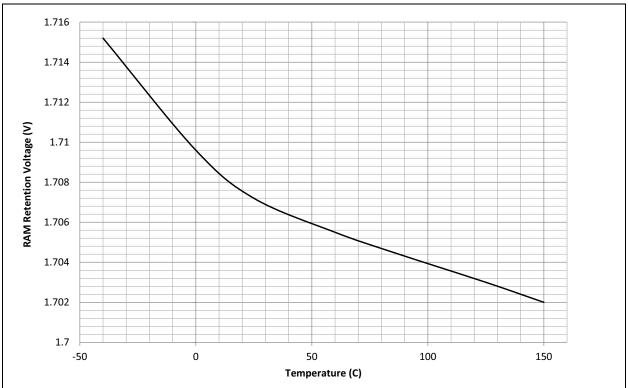

FIGURE 32-36: TYPICAL RAM RETENTION VOLTAGE vs. TEMPERATURE

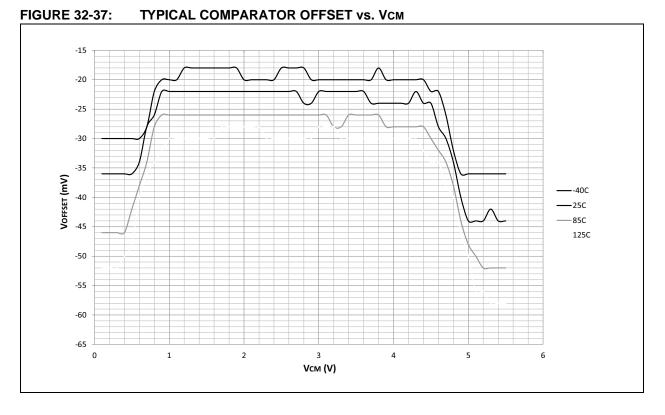

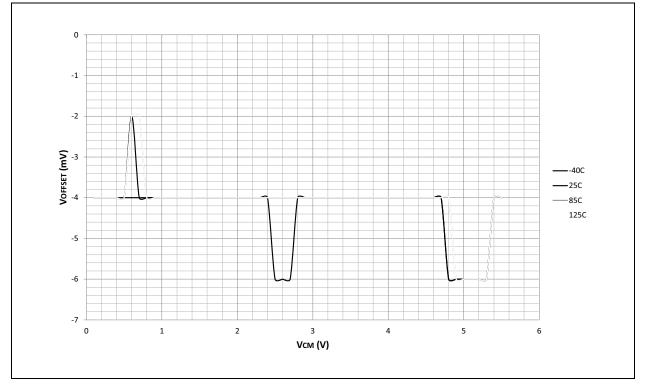

### 32.14 Comparator Op Amp Offset

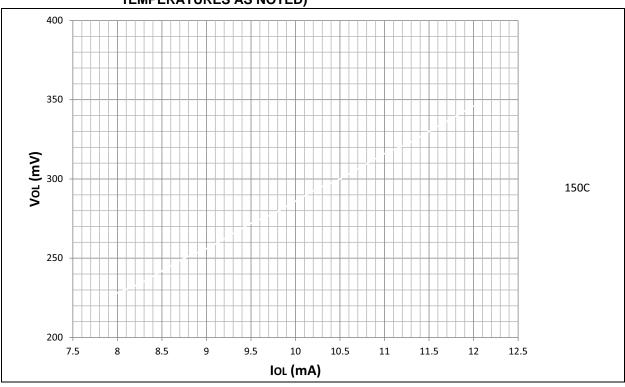

# FIGURE 33-29: TYPICAL Vol 4x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

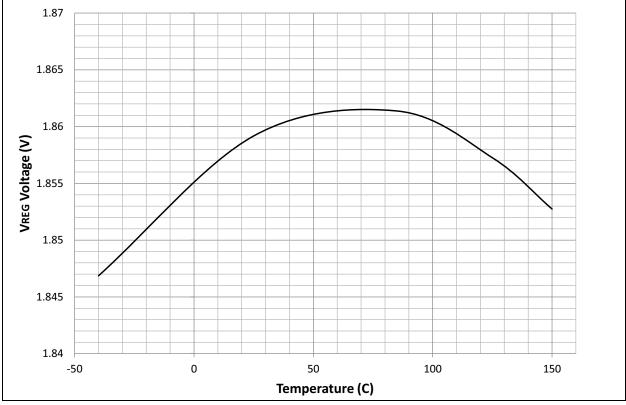

### 33.11 VREG

NOTES:

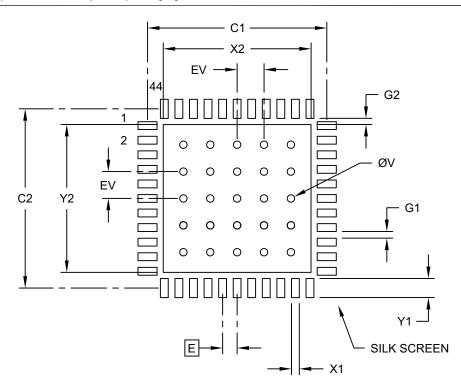

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

| Units                            |    | MILLIMETERS |      |      |

|----------------------------------|----|-------------|------|------|

| Dimension Limits                 |    | MIN         | NOM  | MAX  |

| Contact Pitch                    | E  | 0.65 BSC    |      |      |

| Optional Center Pad Width        | X2 |             |      | 6.60 |

| Optional Center Pad Length       | Y2 |             |      | 6.60 |

| Contact Pad Spacing              | C1 |             | 8.00 |      |

| Contact Pad Spacing              | C2 |             | 8.00 |      |

| Contact Pad Width (X44)          | X1 |             |      | 0.35 |

| Contact Pad Length (X44)         | Y1 |             |      | 0.85 |

| Contact Pad to Contact Pad (X40) | G1 | 0.30        |      |      |

| Contact Pad to Center Pad (X44)  | G2 | 0.28        |      |      |

| Thermal Via Diameter             | V  |             | 0.33 |      |

| Thermal Via Pitch                | EV |             | 1.20 |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2103C