Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm104-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

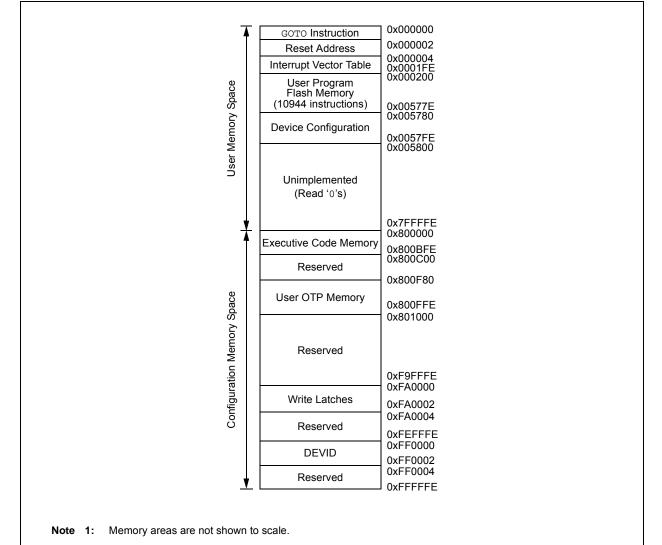

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EVXXXGM00X/10X family architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33EVXXXGM00X/10X family devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC, during program execution or from table operation, or from DS remapping, as described in Section 4.7 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x02ABFF). The exception is the use of the TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space and the TBLWT operations, which are used to set up the write latches located in configuration memory space.

The program memory maps, which are presented by the device family and memory size, are shown in Figure 4-1 through Figure 4-4.

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

### TABLE 4-45: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| For the MOV instructions, the addressing      |

|-----------------------------------------------|

| mode specified in the instruction can differ  |

| for the source and destination EA. How-       |

| ever, the 4-bit Wb (Register Offset) field is |

| shared by both source and destination         |

| (but typically only used by one).             |

|                                               |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set, {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X Data Space) and W11 (in Y Data Space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (Branch) instructions use 16-bit signed literals to specify the Branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| U-0             | U-0                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                | U-0               | R-0              | R-0             | R-0    |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-----------------|--------|

| _               | _                                                                                                                                                             |                                                                                                                                                                                                                                                                                                          | —                                                                                                                  |                   | ILR3             | ILR2            | ILR1   |

| bit 15          |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                    |                   |                  |                 | bit    |

| R-0             | R-0                                                                                                                                                           | R-0                                                                                                                                                                                                                                                                                                      | R-0                                                                                                                | R-0               | R-0              | R-0             | R-0    |

| VECNUM7         | VECNUM6                                                                                                                                                       | VECNUM5                                                                                                                                                                                                                                                                                                  | VECNUM4                                                                                                            | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM |

| bit 7           |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                    |                   |                  |                 | bit    |

| Legend:         |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                          |                                                                                                                    |                   |                  |                 |        |

| R = Readable    | bit                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                                                                             | bit                                                                                                                | U = Unimplen      | nented bit, read | l as '0'        |        |

| -n = Value at F | POR                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                                                         |                                                                                                                    | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|                 | •<br>•<br>0001 = CPU                                                                                                                                          | Interrupt Priorit<br>Interrupt Priorit<br>Interrupt Priorit                                                                                                                                                                                                                                              | y Level is 1                                                                                                       |                   |                  |                 |        |

| bit 7-0         | 111111111 = 2<br>00001001 = 9<br>00001000 = 2<br>00000111 = 1<br>00000101 = 2<br>00000101 = 2<br>00000010 = 2<br>00000010 = 2<br>00000010 = 2<br>00000010 = 2 | <ol> <li>Vector Nun</li> <li>Reserved</li> <li>Input Captur</li> <li>External Inter</li> <li>External Inter</li> <li>Reserved; d</li> <li>Generic soft</li> <li>DMAC error</li> <li>Math error tr</li> <li>Stack error t</li> <li>Generic hard</li> <li>Address error</li> <li>Oscillator fai</li> </ol> | ; do not use<br>er 1 (IC1)<br>errupt 0 (INT0)<br>o not use<br>error trap<br>trap<br>ap<br>rap<br>d trap<br>or trap | ig Interrupt bits |                  |                 |        |

## REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| Input Name <sup>(1)</sup>    | Function Name | Register | Configuration Bits |

|------------------------------|---------------|----------|--------------------|

| External Interrupt 1         | INT1          | RPINR0   | INT1R<7:0>         |

| External Interrupt 2         | INT2          | RPINR1   | INT2R<7:0>         |

| Timer2 External Clock        | T2CK          | RPINR3   | T2CKR<7:0>         |

| Input Capture 1              | IC1           | RPINR7   | IC1R<7:0>          |

| Input Capture 2              | IC2           | RPINR7   | IC2R<7:0>          |

| Input Capture 3              | IC3           | RPINR8   | IC3R<7:0>          |

| Input Capture 4              | IC4           | RPINR8   | IC4R<7:0>          |

| Output Compare Fault A       | OCFA          | RPINR11  | OCFAR<7:0>         |

| PWM Fault 1                  | FLT1          | RPINR12  | FLT1R<7:0>         |

| PWM Fault 2                  | FLT2          | RPINR12  | FLT2R<7:0>         |

| UART1 Receive                | U1RX          | RPINR18  | U1RXR<7:0>         |

| UART2 Receive                | U2RX          | RPINR19  | U2RXR<7:0>         |

| SPI2 Data Input              | SDI2          | RPINR22  | SDI2R<7:0>         |

| SPI2 Clock Input             | SCK2          | RPINR22  | SCK2R<7:0>         |

| SPI2 Slave Select            | SS2           | RPINR23  | SS2R<7:0>          |

| CAN1 Receive                 | C1RX          | RPINR26  | C1RXR<7:0>         |

| PWM Sync Input 1             | SYNCI1        | RPINR37  | SYNCI1R<7:0>       |

| PWM Dead-Time Compensation 1 | DTCMP1        | RPINR38  | DTCMP1R<7:0>       |

| PWM Dead-Time Compensation 2 | DTCMP2        | RPINR39  | DTCMP2R<7:0>       |

| PWM Dead-Time Compensation 3 | DTCMP3        | RPINR39  | DTCMP3R<7:0>       |

| SENT1 Input                  | SENT1R        | RPINR44  | SENT1R<7:0>        |

| SENT2 Input                  | SENT2R        | RPINR45  | SENT2R<7:0>        |

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP35R5 | RP35R4 | RP35R3 | RP35R2 | RP35R1 | RP35R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|        |     | RP20R5 | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

#### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP37R5 | RP37R4 | RP37R3 | RP37R2 | RP37R1 | RP37R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | RP36R5 | RP36R4 | RP36R3 | RP36R2 | RP36R1 | RP36R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 7

bit 13-8 **RP37R<5:0>:** Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP36R<5:0>:** Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 0

## REGISTER 14-5: DMTCNTL: DEADMAN TIMER COUNT REGISTER LOW

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|--|--|

|                                   |       |                  | COUNT | ER<15:8>                           |       |                 |       |  |  |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |

|                                   |       |                  | COUN  | ΓER<7:0>                           |       |                 |       |  |  |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |  |  |

|                                   |       |                  |       |                                    |       |                 |       |  |  |

| Legend:                           |       |                  |       |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit |       |                  | oit   | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |  |  |

bit 15-0 COUNTER<15:0>: Read Current Contents of Lower DMT Counter bits

### REGISTER 14-6: DMTCNTH: DEADMAN TIMER COUNT REGISTER HIGH

| R/W-0                                                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0                              | R/W-0 | R/W-0 |  |  |

|---------------------------------------------------------------------------|-------|-------|-------|--------------|------------------------------------|-------|-------|--|--|

|                                                                           |       |       | COUNT | ER<31:24>    |                                    |       |       |  |  |

| bit 15                                                                    |       |       |       |              |                                    |       | bit 8 |  |  |

|                                                                           |       |       |       |              |                                    |       |       |  |  |

| R/W-0                                                                     | R/W-0 | R/W-0 | R/W-0 | R/W-0        | R/W-0                              | R/W-0 | R/W-0 |  |  |

|                                                                           |       |       | COUNT | ER<23:16>    |                                    |       |       |  |  |

| bit 7                                                                     |       |       |       |              |                                    |       | bit 0 |  |  |

|                                                                           |       |       |       |              |                                    |       |       |  |  |

| Legend:                                                                   |       |       |       |              |                                    |       |       |  |  |

| R = Readable bit W = Writable bit U                                       |       |       |       | U = Unimpler | U = Unimplemented bit, read as '0' |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow |       |       |       |              |                                    | nown  |       |  |  |

bit 15-0 COUNTER<31:16>: Read Current Contents of Higher DMT Counter bits

# REGISTER 14-11: DMTHOLDREG: DMT HOLD REGISTER<sup>(1)</sup>

| R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0             | R/W-0                              | R/W-0              | R/W-0 |  |  |

|------------------|-------|------------------|------------------|-------------------|------------------------------------|--------------------|-------|--|--|

|                  |       |                  | UPRO             | CNT<15:8>         |                                    |                    |       |  |  |

| bit 15           |       |                  |                  |                   |                                    |                    | bit 8 |  |  |

|                  |       |                  |                  |                   |                                    |                    |       |  |  |

| R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0             | R/W-0                              | R/W-0              | R/W-0 |  |  |

|                  |       |                  | UPR              | CNT<7:0>          |                                    |                    |       |  |  |

| bit 7            |       |                  |                  |                   |                                    |                    | bit 0 |  |  |

|                  |       |                  |                  |                   |                                    |                    |       |  |  |

| Legend:          |       |                  |                  |                   |                                    |                    |       |  |  |

| R = Readable bit |       | W = Writable I   | W = Writable bit |                   | U = Unimplemented bit, read as '0' |                    |       |  |  |

| -n = Value at    | POR   | '1' = Bit is set |                  | '0' = Bit is clea | ared                               | x = Bit is unknown |       |  |  |

bit 15-0 UPRCNT<15:0>: Value of the DMTCNTH register when DMTCNTL and DMTCNTH were Last Read bits

**Note 1:** The DMTHOLDREG register is initialized to '0' on Reset, and is only loaded when the DMTCNTL and DMTCNTH registers are read.

| HS-0, HC               | HS-0, HC                                                               | HS-0, HC                                   | R/W-0                 | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

|------------------------|------------------------------------------------------------------------|--------------------------------------------|-----------------------|------------------|----------------------|----------------------|---------------------|

| FLTSTAT <sup>(1)</sup> | CLSTAT <sup>(1)</sup>                                                  | TRGSTAT                                    | FLTIEN                | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15                 |                                                                        | ·                                          |                       |                  |                      |                      | bit 8               |

|                        |                                                                        |                                            |                       |                  |                      |                      |                     |

| R/W-0                  | R/W-0                                                                  | R/W-0                                      | U-0                   | U-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1                   | DTC0                                                                   | DTCP <sup>(3)</sup>                        | —                     | —                | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7                  |                                                                        |                                            |                       |                  |                      |                      | bit (               |

|                        |                                                                        |                                            |                       |                  |                      |                      |                     |

| Legend:                |                                                                        | HC = Hardware                              | Clearable bit         | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Readable           | bit                                                                    | W = Writable bi                            | t                     | U = Unimple      | mented bit, rea      | <b>d as</b> '0'      |                     |

| -n = Value at I        | POR                                                                    | '1' = Bit is set                           |                       | '0' = Bit is cle | eared                | x = Bit is unki      | nown                |

| bit 15                 | FLTSTAT: Fai                                                           | ult Interrupt Statu                        | us bit <sup>(1)</sup> |                  |                      |                      |                     |

|                        |                                                                        | rupt is pending                            |                       |                  |                      |                      |                     |

|                        |                                                                        | rrupt is not pendi<br>ared by setting F    |                       |                  |                      |                      |                     |

| bit 14                 |                                                                        | rent-Limit Interru                         |                       |                  |                      |                      |                     |

|                        |                                                                        | mit interrupt is pe                        | •                     |                  |                      |                      |                     |

|                        | 0 = Current-lin                                                        | mit interrupt is no<br>ared by setting C   | ot pending            |                  |                      |                      |                     |

| bit 13                 | TRGSTAT: Trigger Interrupt Status bit                                  |                                            |                       |                  |                      |                      |                     |

|                        |                                                                        | terrupt is pending                         |                       |                  |                      |                      |                     |

|                        |                                                                        | terrupt is not per<br>ared by setting T    |                       |                  |                      |                      |                     |

| bit 12                 | FLTIEN: Fault                                                          | t Interrupt Enable                         | e bit                 |                  |                      |                      |                     |

|                        |                                                                        | rrupt is enabled                           | and the FLTST         | AT bit is cleare | ed                   |                      |                     |

| bit 11                 | CLIEN: Curre                                                           | nt-Limit Interrup                          | t Enable bit          |                  |                      |                      |                     |

|                        |                                                                        | mit interrupt is er<br>mit interrupt is di |                       | CLSTAT bit is    | cleared              |                      |                     |

| bit 10                 |                                                                        | ger Interrupt Ena                          |                       |                  |                      |                      |                     |

|                        | 1 = Trigger ev                                                         | vent generates a<br>vent interrupts ar     | n interrupt requ      |                  | bit is cleared       |                      |                     |

| bit 9                  |                                                                        | dent Time Base I                           |                       |                  |                      |                      |                     |

| bit 0                  | 1 = PHASEx I                                                           | register provides                          | time base per         |                  |                      |                      |                     |

| bit 8                  |                                                                        | er Duty Cycle Re                           |                       |                  |                      |                      |                     |

|                        | 1 = MDC regi                                                           | ster provides du<br>ister provides du      | ty cycle information  | ation for this P |                      |                      |                     |

| Note 1: So             | ftware must clea                                                       | ar the interrupt st                        | atus here and         | in the correspo  | onding IFSx bit      | in the interrupt     | controller.         |

|                        | These bits should not be changed after the PWMx is enabled (PTEN = 1). |                                            |                       |                  |                      |                      |                     |

|                        | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.         |                                            |                       |                  |                      |                      |                     |

|                        | e Independent T<br>M bit is ignored.                                   | īme Base (ITB =                            | 1) mode mus           | t be enabled to  | use Center-Al        | igned mode. If       | ITB = 0, the        |

|                        | operate in Exter<br>jister must be '0                                  | nal Period Rese<br>'.                      | t mode, the ITI       | B bit must be ': | 1' and the CLM       | OD bit in the F      | CLCONx              |

## REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER

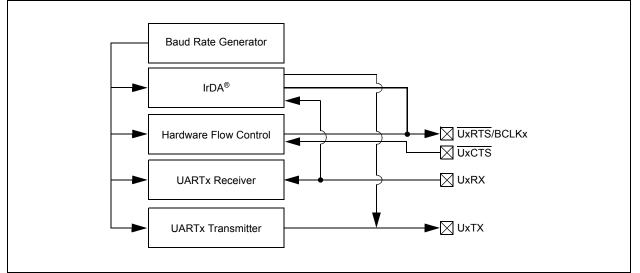

## 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EVXXXGM00X/10X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a

hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

| Note: | Hardware flow control using UxRTS and   |

|-------|-----------------------------------------|

|       | UxCTS is not available on all pin count |

|       | devices. See the "Pin Diagrams" section |

|       | for availability.                       |

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

## FIGURE 21-1: UARTX SIMPLIFIED BLOCK DIAGRAM

# 21.2 UART Control Registers

## REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER                                                                                                        | 21-1: UxMO                                                     | DE: UARTx N                                                       |                                                             | TER                             |                                          |                  |                           |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|------------------|---------------------------|--|

| R/W-0                                                                                                           | U-0                                                            | R/W-0                                                             | R/W-0                                                       | R/W-0                           | U-0                                      | R/W-0            | R/W-0                     |  |

| UARTEN <sup>(1)</sup>                                                                                           |                                                                | USIDL                                                             | IREN <sup>(2)</sup>                                         | RTSMD                           |                                          | UEN1             | UEN0                      |  |

| bit 15                                                                                                          |                                                                |                                                                   |                                                             | ·                               |                                          |                  | bit 8                     |  |

| R/W-0, HC                                                                                                       | R/W-0                                                          | R/W-0, HC                                                         | R/W-0                                                       | R/W-0                           | R/W-0                                    | R/W-0            | R/W-0                     |  |

| WAKE                                                                                                            | LPBACK                                                         | ABAUD                                                             | URXINV                                                      | BRGH                            | PDSEL1                                   | PDSEL0           | STSEL                     |  |

| bit 7                                                                                                           |                                                                | 101100                                                            | Orodity                                                     | ыкоп                            | TDOLLI                                   | TDOLLO           | bit (                     |  |

|                                                                                                                 |                                                                |                                                                   |                                                             |                                 |                                          |                  |                           |  |

| Legend:                                                                                                         |                                                                | HC = Hardwar                                                      | e Clearable bit                                             | t                               |                                          |                  |                           |  |

| R = Readable                                                                                                    | e bit                                                          | W = Writable I                                                    | oit                                                         | U = Unimple                     | mented bit, rea                          | ad as '0'        |                           |  |

| -n = Value at                                                                                                   | POR                                                            | '1' = Bit is set                                                  |                                                             | '0' = Bit is cle                | eared                                    | x = Bit is unk   | nown                      |  |

| bit 15                                                                                                          | 1 = UARTx is                                                   | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U          | ARTx pins are                                               |                                 |                                          |                  |                           |  |

|                                                                                                                 | is minima                                                      |                                                                   |                                                             |                                 |                                          |                  |                           |  |

| bit 14                                                                                                          | •                                                              | ted: Read as '0                                                   |                                                             |                                 |                                          |                  |                           |  |

| bit 13 USIDL: UARTx Stop in Idle Mode bit<br>1 = Discontinues module operation when the device enters Idle mode |                                                                |                                                                   |                                                             |                                 |                                          |                  |                           |  |

|                                                                                                                 |                                                                | iues module op<br>es module opera                                 |                                                             |                                 | s Idle mode                              |                  |                           |  |

| bit 12                                                                                                          | IREN: IrDA <sup>®</sup>                                        | Encoder and De                                                    | ecoder Enable                                               | bit <sup>(2)</sup>              |                                          |                  |                           |  |

| <ul><li>1 = IrDA encoder and decoder are enabled</li><li>0 = IrDA encoder and decoder are disabled</li></ul>    |                                                                |                                                                   |                                                             |                                 |                                          |                  |                           |  |

| bit 11                                                                                                          |                                                                | le Selection for                                                  |                                                             |                                 |                                          |                  |                           |  |

|                                                                                                                 | 1 = UxRTS p                                                    | oin is in Simplex<br>oin is in Flow Co                            | mode                                                        |                                 |                                          |                  |                           |  |

| bit 10                                                                                                          |                                                                | ited: Read as '0                                                  |                                                             |                                 |                                          |                  |                           |  |

| bit 9-8                                                                                                         | -                                                              | IARTx Pin Enab                                                    |                                                             |                                 |                                          |                  |                           |  |

|                                                                                                                 | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                   | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used; | nd used <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |  |

| bit 7                                                                                                           | WAKE: UAR                                                      | Tx Wake-up on                                                     | Start bit Detect                                            | During Sleep                    | Mode Enable I                            | oit              |                           |  |

|                                                                                                                 | in hardwa                                                      | ontinues to sam<br>are on the follow<br>is not enabled            |                                                             |                                 | generated on                             | the falling edge | , bit is cleare           |  |

| bit 6                                                                                                           | -                                                              | RTx Loopback                                                      | Mode Select b                                               | it                              |                                          |                  |                           |  |

|                                                                                                                 |                                                                | k mode is enab                                                    |                                                             |                                 |                                          |                  |                           |  |

|                                                                                                                 |                                                                | k mode is disab                                                   |                                                             |                                 |                                          |                  |                           |  |

| "d:<br>tra                                                                                                      | efer to " <b>Univers</b><br>sPIC33/PIC24 F<br>insmit operation | amily Referenc                                                    | e <i>Manual"</i> for i                                      | nformation on e                 | enabling the U                           |                  |                           |  |

|                                                                                                                 | is feature is only                                             | -                                                                 |                                                             |                                 | )).                                      |                  |                           |  |

| <b>3:</b> Th                                                                                                    | is feature is only available on 44-pin and 64-pin devices.     |                                                                   |                                                             |                                 |                                          |                  |                           |  |

4: This feature is only available on 64-pin devices.

# 26.2 Comparator Voltage Reference Registers

# REGISTER 26-1: CVR1CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0        | R/W-0      | U-0   | U-0   | R/W-0     | R/W-0 U-0 |       | U-0   |  |

|--------------|------------|-------|-------|-----------|-----------|-------|-------|--|

| CVREN        | CVROE      | —     | _     | CVRSS     | VREFSEL   | —     | _     |  |

| pit 15 bit 8 |            |       |       |           |           |       |       |  |

|              |            |       |       |           |           |       |       |  |

| U-0          | R/W-0      | R/W-0 | R/W-0 | R/W-0     | R/W-0     | R/W-0 | R/W-0 |  |

| _            | — CVR6 CVF |       | CVR4  | CVR3 CVR2 |           | CVR1  | CVR0  |  |

| bit 7        |            |       |       |           |           |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | CVREN: Comparator Voltage Reference Enable bit                      |

|-----------|---------------------------------------------------------------------|

|           | 1 = Comparator voltage reference circuit is powered on              |

|           | 0 = Comparator voltage reference circuit is powered down            |

| bit 14    | CVROE: Comparator Voltage Reference Output Enable (CVREF10 Pin) bit |

|           | 1 = Voltage level is output on the CVREF10 pin                      |

|           | 0 = Voltage level is disconnected from the CVREF10 pin              |

| bit 13-12 | Unimplemented: Read as '0'                                          |

| bit 11    | CVRSS: Comparator Voltage Reference Source Selection bit            |

|           | 1 = Comparator reference source, CVRsRC = CVREF+ – AVss             |

|           | 0 = Comparator reference source, CVRSRC = AVDD – AVSS               |

| bit 10    | VREFSEL: Voltage Reference Select bit                               |

|           | 1 = CVREFIN = CVREF+                                                |

|           | 0 = CVREFIN is generated by the resistor network                    |

| bit 9-7   | Unimplemented: Read as '0'                                          |

| bit 6-0   | CVR<6:0>: Comparator Voltage Reference Value Selection bits         |

|           | 1111111 = 127/128 x VREF input voltage                              |

|           | •                                                                   |

|           | •                                                                   |

|           |                                                                     |

|           | 0000000 = <b>0.0 volts</b>                                          |

| File Name      | Address                           | Device<br>Memory<br>Size<br>(Kbytes) | 23-16                   | Bit 15             | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9                   | Bit 8            | Bit 7                                   | Bit 6   | Bit 5   | Bit 4  | Bit 3   | Bit 2     | Bit 1  | Bit 0  |

|----------------|-----------------------------------|--------------------------------------|-------------------------|--------------------|--------|--------|-------------|--------|--------|-------------------------|------------------|-----------------------------------------|---------|---------|--------|---------|-----------|--------|--------|

| FSEC           | 005780                            | 32                                   |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00AB80                            | 64                                   |                         | AIVTDIS            |        |        |             | CSS2   | CSS1   | CSS0                    | CWRP             | GSS1                                    | 0000    | GWRP    |        | BSEN    | BSS1      | BSS0   |        |

|                | 015780                            | 128                                  | -                       | AIVIDIS            | _      | —      | _           | 0332   | 0331   | 0330                    | CWRF             | 6551                                    | GSS0 G  | GWRF    | _      | - DOLN  | 6001      | 8330   | BWRP   |

|                | 02AB80                            | 256                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| FBSLIM         | 005790                            | 32                                   |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00AB90                            | 64                                   |                         | _                  | _      | _      | BSLIM<12:0> |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 015790                            | 128                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 02AB90                            | 256                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| Reserved       | 005794                            | 32                                   |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00AB94 64 — Reserved <sup>(</sup> |                                      | Reserved <sup>(1)</sup> | d <sup>(1)</sup> — | -      | -      |             | _      |        | -                       | _                | —                                       | —       | —       | -      | _       | —         |        |        |

|                |                                   |                                      | 1 toool vou             |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 02AB94                            | 256                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| FOSCSEL        |                                   |                                      |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00AB98                            | 64                                   |                         | _                  | _      |        | _           | _      | _      | _                       | _                | IESO                                    |         | _       | _      | _       | FNOSC2    | FNOSC1 | FNOSC0 |

|                | 015798                            | 128                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 02AB98                            | 256                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| FOSC           | 00579C                            | 32                                   |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00AB9C                            | 64                                   |                         | _                  | _      | _      | _           | _      | _      | _                       | PLLKEN           | FCKSM1 FCKSM0 IOL1WAY - OSCIOFNC POSCMI |         |         |        | POSCMD1 | 1 POSCMD0 |        |        |

|                | 01579C                            | 128                                  | -                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| 514/0 <b>7</b> | 02AB9C                            | 256                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         | -      | -       |           |        |        |

| FWDT           | 0057A0                            | 32                                   | -                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00ABA0                            | 64                                   |                         | _                  | _      | _      | _           | _      | _      | WDTWIN1                 | WDTWIN0          | WINDIS                                  | FWDTEN1 | FWDTEN0 | WDTPRE | WDTPS3  | WDTPS2    | WDTPS1 | WDTPS0 |

|                | 0157A0                            | 128                                  | -                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| FPOR           | 02ABA0<br>0057A4                  | 256<br>32                            |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| FPUR           | 0057A4<br>00ABA4                  | 32<br>64                             | -                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 00ABA4<br>0157A4                  | 64<br>128                            |                         | —                  | —      | —      | —           | —      | —      | _                       | —                | —                                       | —       | —       | —      | —       | —         | —      | BOREN  |

|                | 0157A4<br>02ABA4                  | 256                                  | 1                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| FICD           | 02ABA4                            | 32                                   |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | 0057A8                            | 64                                   | 1                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

| 0157A8 128     |                                   | -                                    | —                       | —                  | _      | —      | —           | —      | —      | Reserved <sup>(2)</sup> | i <sup>(2)</sup> |                                         |         | -       | ICS1   | ICS0    |           |        |        |

|                | 0157A8                            |                                      | 1                       |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           |        |        |

|                | UZADAŎ                            | 200                                  |                         |                    |        |        |             |        |        |                         |                  |                                         |         |         |        |         |           | 1      |        |

#### TABLE 27-1: CONFIGURATION WORD REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1:This bit is reserved and must be programmed as '0'.2:This bit is reserved and must be programmed as '1'.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|-------------|------------------------------|---------------|----------------|--------------------------|

| 78                 | SWAP                 | SWAP.b          | Wn          | Wn = nibble swap Wn          | 1             | 1              | None                     |

|                    |                      | SWAP            | Wn          | Wn = byte swap Wn            | 1             | 1              | None                     |

| 79                 | TBLRDH               | TBLRDH          | Ws,Wd       | Read Prog<23:16> to Wd<7:0>  | 1             | 5              | None                     |

| 80                 | TBLRDL               | TBLRDL          | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 5              | None                     |

| 81                 | TBLWTH               | TBLWTH          | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| 82                 | TBLWTL               | TBLWTL          | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| 83                 | ULNK                 | ULNK            |             | Unlink Frame Pointer         | 1             | 1              | SFA                      |

| 84                 | XOR                  | XOR             | f           | f = f .XOR. WREG             | 1             | 1              | N,Z                      |

|                    |                      | XOR             | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N,Z                      |

|                    |                      | XOR             | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N,Z                      |

|                    |                      | XOR             | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N,Z                      |

| 1                  |                      | XOR             | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N,Z                      |

| 85                 | ZE                   | ZE              | Ws,Wnd      | Wnd = Zero-extend Ws         | 1             | 1              | C,Z,N                    |

## TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

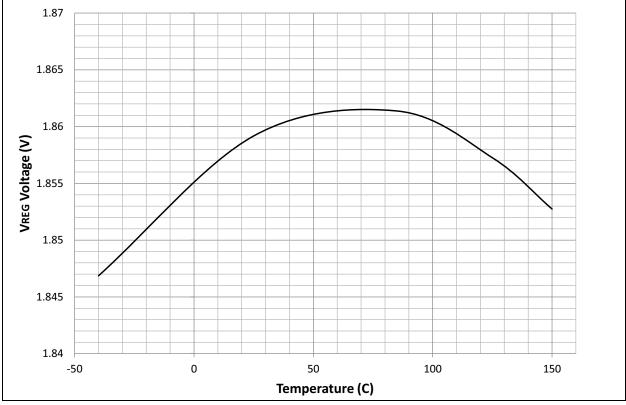

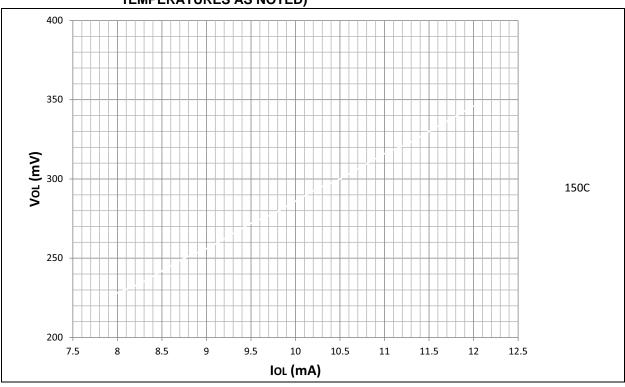

# **30.0 ELECTRICAL CHARACTERISTICS**

This section provides an overview of dsPIC33EVXXXGM00X/10X family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EVXXXGM00X/10X family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                           | 40°C to +125°C |

|----------------------------------------------------------|----------------|

| Storage temperature                                      | 65°C to +160°C |

| Voltage on VDD with respect to Vss                       | 0.3V to +6.0V  |

| Voltage on VCAP with respect to Vss                      | 1.62V to 1.98V |

| Maximum current out of Vss pin                           | 350 mA         |

| Maximum current into Vod pin <sup>(2)</sup>              | 350 mA         |

| Maximum current sunk by any I/O pin                      | 20 mA          |

| Maximum current sourced by I/O pin                       | 18 mA          |

| Maximum current sourced/sunk by all ports <sup>(2)</sup> | 200 mA         |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 30-2).

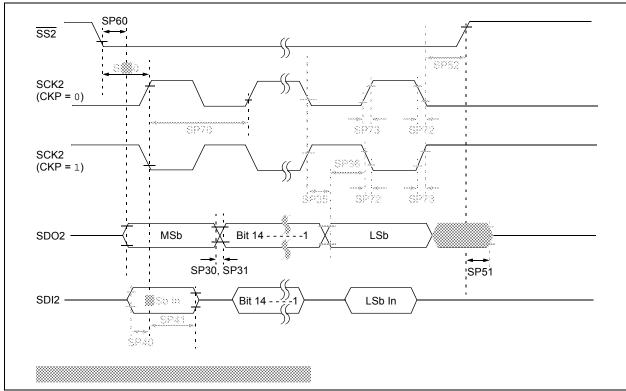

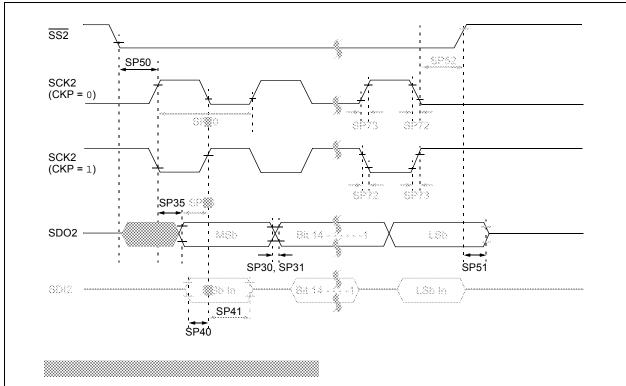

# FIGURE 30-17: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-42:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                      |

|--------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |

| SP70               | FscP                  | Maximum SCK1 Input Frequency                 | —                                                                                                                                                                                                                                                                                     | —                   | 25   | MHz   | See Note 3                           |

| SP72               | TscF                  | SCK1 Input Fall Time                         | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73               | TscR                  | SCK1 Input Rise Time                         | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                   | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                   | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |