Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm106-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

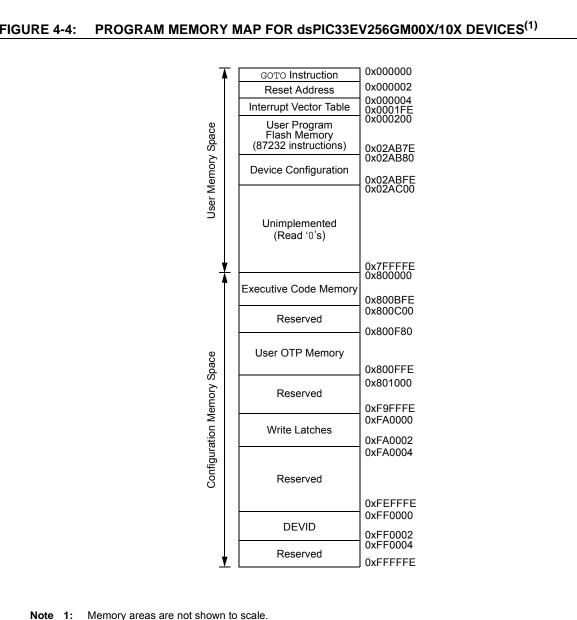

### FIGURE 4-4:

## TABLE 4-24: OUTPUT COMPARE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10       | Bit 9 | Bit 8    | Bit 7      | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------------------------------------|--------|------------|---------|---------|--------------|-------|----------|------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1     | 0900  | _                                     | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     | —        | ENFLTA     | _            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                 | FLTOUT | FLTTRIEN   | OCINV   | _       |              | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC1RS       | 0904  |                                       |        |            |         |         |              | Ou    | tput Con | npare 1 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC1R        | 0906  |                                       |        |            |         |         |              |       | Outpu    | ut Compare | e 1 Register |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                                       |        |            |         |         |              | Out   | put Com  | pare 1 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _                                     | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD                                 | FLTOUT | FLTTRIEN   | OCINV   | _       | _            | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                                       |        |            |         |         |              | Ou    | tput Con | npare 2 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |                                       |        |            |         |         |              |       | Outpu    | ut Compare | e 2 Register |        |          |          |          |          |          | xxxx          |

| OC2TMR      | 0912  |                                       |        |            |         |         |              | Out   | put Com  | pare 2 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC3CON1     | 0914  | _                                     | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                 | FLTOUT | FLTTRIEN   | OCINV   | _       |              | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                                       |        |            |         |         |              | Ou    | tput Con | npare 3 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                                       |        |            |         |         |              |       | Outpu    | ut Compare | e 3 Register |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                                       |        |            |         |         |              | Out   | put Com  | pare 3 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC4CON1     | 091E  | _                                     | —      | OCSIDL     | OCTSEL2 | OCTSEL1 | OCTSEL0      | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                 | FLTOUT | FLTTRIEN   | OCINV   | _       | _            | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                                       |        |            |         |         |              | Ou    | tput Con | npare 4 Se | condary Reg  | gister |          |          |          |          |          | xxxx          |

| OC4R        | 0924  |                                       |        |            |         |         |              |       | Outpu    | ut Compare | e 4 Register |        |          |          |          |          |          | xxxx          |

| OC4TMR      | 0926  | Output Compare 4 Timer Value Register |        |            |         |         |              |       |          |            |              | xxxx   |          |          |          |          |          |               |

| Logondu     |       |                                       | -      | ot: – unim |         | 1 /-1   | <b>-</b> · · |       |          |            |              |        |          |          |          |          |          | <i>.</i>      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

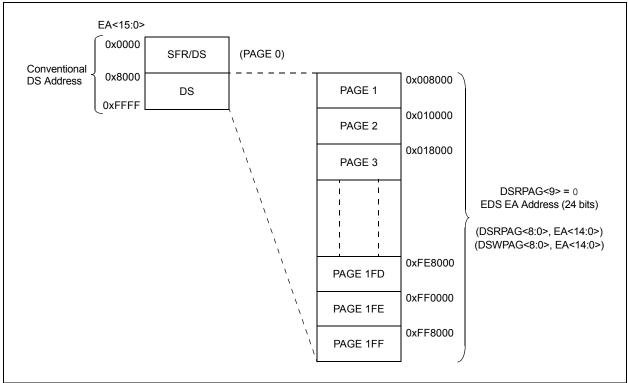

### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

| REGISTER      |                      | CON: DMA C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |                   |                 |                 |        |

|---------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-----------------|-----------------|--------|

| R/W-0         | R/W-0                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0               | R/W-0             | U-0             | U-0             | U-0    |

| CHEN          | SIZE                 | DIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | HALF                | NULLW             | —               | —               | _      |

| bit 15        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | •                 |                 |                 | bit 8  |

|               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| U-0           | U-0                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0               | U-0               | U-0             | R/W-0           | R/W-0  |

| —             | —                    | AMODE1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AMODE0              | —                 | _               | MODE1           | MODE0  |

| bit 7         |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 | bit 0  |

|               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| Legend:       |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| R = Readable  | e bit                | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit                 | U = Unimplen      | nented bit, rea | d as '0'        |        |

| -n = Value at | POR                  | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                     | '0' = Bit is clea | ared            | x = Bit is unkn | own    |

|               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| bit 15        | CHEN: DMA            | Channel Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | le bit              |                   |                 |                 |        |

|               | 1 = Channel          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

|               | 0 = Channel          | is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |                   |                 |                 |        |

| bit 14        | SIZE: DMA D          | ata Transfer S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ize bit             |                   |                 |                 |        |

|               | 1 = Byte<br>0 = Word |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| L:1 1 0       |                      | anafar Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | a hit (a a ura a /d | activation bus    | a a la at)      |                 |        |

| bit 13        |                      | ansfer Directior<br>om RAM addre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                   |                   | -               |                 |        |

|               |                      | om peripheral a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| bit 12        |                      | Block Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                   |                 |                 |        |

|               |                      | nterrupt when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                   |                   | ved             |                 |        |

|               |                      | nterrupt when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                   |                 |                 |        |

| bit 11        | NULLW: Null          | Data Peripher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | al Write Mode       | Select bit        |                 |                 |        |

|               |                      | write to periph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | eral in addition    | n to RAM write    | (DIR bit must   | also be clear)  |        |

|               | 0 = Normal c         | peration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                   |                 |                 |        |

| bit 10-6      | -                    | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                   |                 |                 |        |

| bit 5-4       |                      | >: DMA Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | el Addressing       | Mode Select b     | its             |                 |        |

|               | 11 = Reserve         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.                  |                   |                 |                 |        |

|               |                      | ral Indirect moon<br>Indirect without reading the second s |                     | ent mode          |                 |                 |        |

|               | •                    | Indirect with F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

| bit 3-2       | •                    | ted: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                   |                 |                 |        |

| bit 1-0       | -                    | DMA Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     | de Select bits    |                 |                 |        |

|               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   | transfer from   | /to each DMA bu | (ffer) |

|               |                      | ous Ping-Pong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | modes are en        | abled             |                 |                 |        |

|               |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                   |                 |                 |        |

|               |                      | ot Ping-Pong n<br>ous Ping-Pong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nodes are disa      | bled              |                 |                 |        |

## REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

## 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

The dsPIC33EVXXXGM00X/10X family devices can manage power consumption in the following four methods:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

### 10.1 Clock Frequency and Clock Switching

The dsPIC33EVXXXGM00X/10X family devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). For more information on the process of changing a system clock during operation, as well as limitations to the process, see **Section 9.0 "Oscillator Configuration"**.

### 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EVXXXGM00X/10X family devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the Assembler Include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

## 11.8 Peripheral Pin Select Registers

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        |       |       | INT1R | <7:0> |       |       |       |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —     | —     | —     | —     |

| bit 7  |       |       |       |       |       |       | bit C |

|        |       |       |       |       |       |       |       |

### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| Legend:           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0           | U-0        | U-0                                | U-0   | U-0              | U-0              | U-0                | U-0   |  |

|---------------|------------|------------------------------------|-------|------------------|------------------|--------------------|-------|--|

| _             | —          | —                                  | -     | _                | —                | —                  | —     |  |

| bit 15        |            |                                    |       |                  |                  |                    | bit 8 |  |

|               |            |                                    |       |                  |                  |                    |       |  |

| R/W-0         | R/W-0      | R/W-0                              | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |

|               |            |                                    | INT2F | R<7:0>           |                  |                    |       |  |

| bit 7         |            |                                    |       |                  |                  |                    | bit 0 |  |

|               |            |                                    |       |                  |                  |                    |       |  |

| Legend:       |            |                                    |       |                  |                  |                    |       |  |

| R = Readable  | e bit      | W = Writable                       | bit   | U = Unimpler     | mented bit, read | <b>as</b> '0'      |       |  |

| -n = Value at | POR        | '1' = Bit is set                   |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

|               |            |                                    |       |                  |                  |                    |       |  |

| bit 15-8      | Unimplemen | ted: Read as '                     | )'    |                  |                  |                    |       |  |

| bit 7-0       |            | Assign Externa<br>-2 for input pin |       |                  | orresponding RI  | Pn Pin bits        |       |  |

|               | 10110101 = | Input tied to RF                   | 91181 |                  |                  |                    |       |  |

|               | •          |                                    |       |                  |                  |                    |       |  |

|               | •          |                                    |       |                  |                  |                    |       |  |

|               | •          |                                    | -     |                  |                  |                    |       |  |

|               |            | Input tied to CN                   |       |                  |                  |                    |       |  |

|               | 00000000 = | Input tied to Vs                   | S     |                  |                  |                    |       |  |

| HS-0, HC               | HS-0, HC                              | HS-0, HC                                   | R/W-0                 | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

|------------------------|---------------------------------------|--------------------------------------------|-----------------------|------------------|----------------------|----------------------|---------------------|

| FLTSTAT <sup>(1)</sup> | CLSTAT <sup>(1)</sup>                 | TRGSTAT                                    | FLTIEN                | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15                 |                                       | ·                                          |                       |                  |                      |                      | bit 8               |

|                        |                                       |                                            |                       |                  |                      |                      |                     |

| R/W-0                  | R/W-0                                 | R/W-0                                      | U-0                   | U-0              | R/W-0                | R/W-0                | R/W-0               |

| DTC1                   | DTC0                                  | DTCP <sup>(3)</sup>                        | —                     | —                | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7                  |                                       |                                            |                       |                  |                      |                      | bit (               |

|                        |                                       |                                            |                       |                  |                      |                      |                     |

| Legend:                |                                       | HC = Hardware                              | Clearable bit         | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Readable           | bit                                   | W = Writable bi                            | t                     | U = Unimple      | mented bit, rea      | <b>d as</b> '0'      |                     |

| -n = Value at I        | POR                                   | '1' = Bit is set                           |                       | '0' = Bit is cle | eared                | x = Bit is unki      | nown                |

| bit 15                 | FLTSTAT: Fai                          | ult Interrupt Statu                        | us bit <sup>(1)</sup> |                  |                      |                      |                     |

|                        |                                       | rupt is pending                            |                       |                  |                      |                      |                     |

|                        |                                       | rrupt is not pendi<br>ared by setting F    |                       |                  |                      |                      |                     |

| bit 14                 |                                       | rent-Limit Interru                         |                       |                  |                      |                      |                     |

|                        |                                       | mit interrupt is pe                        | •                     |                  |                      |                      |                     |

|                        | 0 = Current-lin                       | mit interrupt is no<br>ared by setting C   | ot pending            |                  |                      |                      |                     |

| bit 13                 |                                       | igger Interrupt Si                         |                       |                  |                      |                      |                     |

|                        |                                       | terrupt is pending                         |                       |                  |                      |                      |                     |

|                        |                                       | terrupt is not per<br>ared by setting T    |                       |                  |                      |                      |                     |

| bit 12                 | FLTIEN: Fault                         | t Interrupt Enable                         | e bit                 |                  |                      |                      |                     |

|                        |                                       | rrupt is enabled                           | and the FLTST         | AT bit is cleare | ed                   |                      |                     |

| bit 11                 | CLIEN: Curre                          | nt-Limit Interrup                          | t Enable bit          |                  |                      |                      |                     |

|                        |                                       | mit interrupt is er<br>mit interrupt is di |                       | CLSTAT bit is    | cleared              |                      |                     |

| bit 10                 |                                       | ger Interrupt Ena                          |                       |                  |                      |                      |                     |

|                        | 1 = Trigger ev                        | vent generates a<br>vent interrupts ar     | n interrupt requ      |                  | bit is cleared       |                      |                     |

| bit 9                  |                                       | dent Time Base I                           |                       |                  |                      |                      |                     |

| bit 0                  | 1 = PHASEx I                          | register provides                          | time base per         |                  |                      |                      |                     |

| bit 8                  |                                       | er Duty Cycle Re                           |                       |                  |                      |                      |                     |

|                        | 1 = MDC regi                          | ster provides du<br>ister provides du      | ty cycle information  | ation for this P |                      |                      |                     |

| Note 1: So             | ftware must clea                      | ar the interrupt st                        | atus here and         | in the correspo  | onding IFSx bit      | in the interrupt     | controller.         |

|                        |                                       | not be changed a                           |                       | -                | -                    |                      |                     |

|                        |                                       | DTCP to be effe                            |                       |                  |                      |                      |                     |

|                        | e Independent T<br>M bit is ignored.  | īme Base (ITB =                            | 1) mode mus           | t be enabled to  | use Center-Al        | igned mode. If       | ITB = 0, the        |

|                        | operate in Exter<br>jister must be '0 | nal Period Rese<br>'.                      | t mode, the ITI       | B bit must be ': | 1' and the CLM       | OD bit in the F      | CLCONx              |

## REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER

### REGISTER 17-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

|                 |                                                                          | DAMA           |       | D/14/ 0      |                  | D 44/ 0         |       |  |  |  |  |

|-----------------|--------------------------------------------------------------------------|----------------|-------|--------------|------------------|-----------------|-------|--|--|--|--|

| R/W-0           | R/W-0                                                                    | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|                 |                                                                          |                | PDC   | x<15:8>      |                  |                 |       |  |  |  |  |

| bit 15          |                                                                          |                |       |              |                  |                 | bit 8 |  |  |  |  |

|                 |                                                                          |                |       |              |                  |                 | ]     |  |  |  |  |

| R/W-0           | R/W-0                                                                    | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|                 |                                                                          |                | PDC   | \$x<7:0>     |                  |                 |       |  |  |  |  |

| bit 7           |                                                                          |                |       |              |                  |                 | bit 0 |  |  |  |  |

|                 |                                                                          |                |       |              |                  |                 |       |  |  |  |  |

| Legend:         |                                                                          |                |       |              |                  |                 |       |  |  |  |  |

| R = Readable    | bit                                                                      | W = Writable b | oit   | U = Unimplem | nented bit, read | <b>d as</b> '0' |       |  |  |  |  |

| -n = Value at P | n = Value at POR (1' = Bit is set 0' = Bit is cleared x = Bit is unknown |                |       |              |                  |                 |       |  |  |  |  |

bit 15-0 PDCx<15:0>: PWMx Generator Duty Cycle Value bits

### REGISTER 17-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PHAS  | Ex<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PHAS  | Ex<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs.

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output modes (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent Time Base period value for PWMxH and PWMxL.

| U-0                 | U-0                              | U-0                                 | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |

|---------------------|----------------------------------|-------------------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|

|                     |                                  |                                     | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |

| bit 15              |                                  |                                     | Diocon               | DICCDO                                 | MODEIO               | Olin                 | bit                  |

|                     |                                  |                                     |                      |                                        |                      |                      |                      |

| R/W-0               | R/W-0                            | R/W-0                               | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |

| SSEN <sup>(2)</sup> | CKP                              | MSTEN                               | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |                                  |                                     |                      | 1                                      |                      |                      | bit                  |

|                     |                                  |                                     |                      |                                        |                      |                      |                      |

| Legend:             |                                  |                                     |                      |                                        |                      |                      |                      |

| R = Readab          | le bit                           | W = Writable                        | bit                  | U = Unimplen                           | nented bit, read     | <b>l as</b> '0'      |                      |

| -n = Value a        | t POR                            | '1' = Bit is set                    |                      | '0' = Bit is clea                      | ared                 | x = Bit is unkr      | nown                 |

|                     |                                  |                                     | _ 1                  |                                        |                      |                      |                      |

| bit 15-13           | -                                | ted: Read as '                      |                      |                                        |                      |                      |                      |

| bit 12              |                                  | PI clock is disa                    | -                    | er modes only)                         |                      |                      |                      |

|                     |                                  | PI clock is disa<br>PI clock is ena |                      | ao 1/U                                 |                      |                      |                      |

| bit 11              |                                  | able SDOx Pin                       |                      |                                        |                      |                      |                      |

|                     | 1 = SDOx pin                     | is not used by                      | the module; p        | oin functions as                       | ; I/O                |                      |                      |

|                     |                                  | is controlled b                     |                      |                                        |                      |                      |                      |

| bit 10              | MODE16: Wo                       | ord/Byte Comm                       | unication Sele       | ect bit                                |                      |                      |                      |

|                     |                                  | cation is word-                     | , ,                  |                                        |                      |                      |                      |

|                     |                                  | cation is byte-                     | . ,                  |                                        |                      |                      |                      |

| bit 9               |                                  | ata Input Samp                      | ole Phase bit        |                                        |                      |                      |                      |

|                     | Master mode:                     | :<br>a is sampled at                | the end of da        | ta output time                         |                      |                      |                      |

|                     |                                  |                                     |                      | data output time                       | ie                   |                      |                      |

|                     | Slave mode:                      | -                                   |                      | n Slave mode.                          |                      |                      |                      |

| bit 8               | CKE: Clock E                     | dge Select bit                      | 1)                   |                                        |                      |                      |                      |

|                     |                                  |                                     |                      |                                        | clock state to Id    |                      |                      |