Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (43K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 36x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

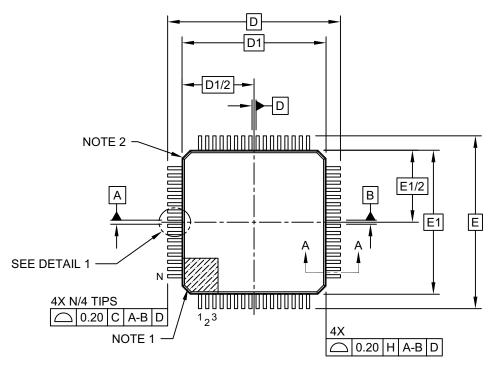

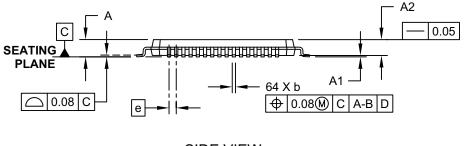

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm106-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Note 1:** Memory areas are not shown to scale.

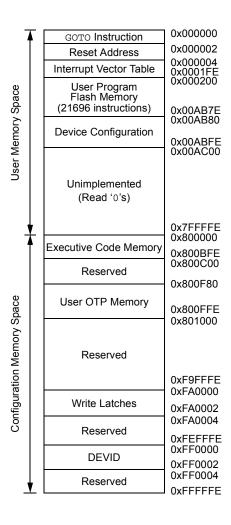

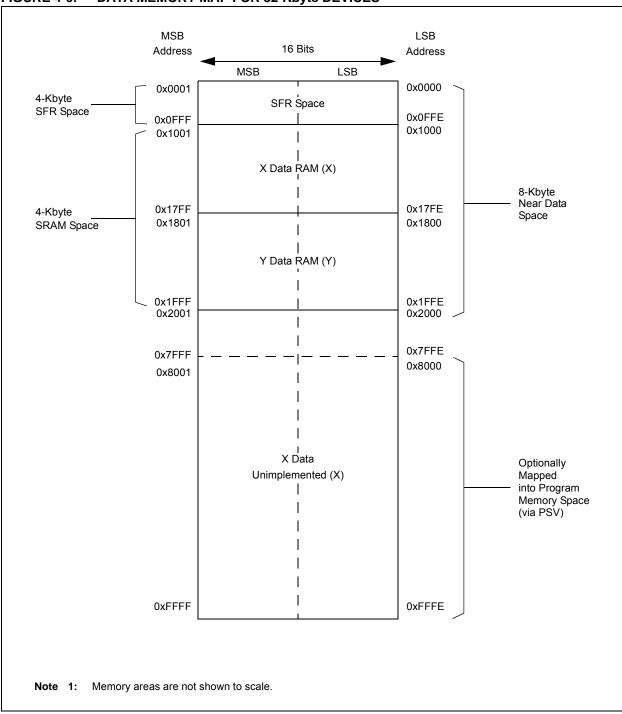

FIGURE 4-6: DATA MEMORY MAP FOR 32-Kbyte DEVICES<sup>(1)</sup>

## TABLE 4-5: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8     | Bit 7         | Bit 6         | Bit 5 | Bit 4       | Bit 3   | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|--------|----------|-----------|---------------|---------------|-------|-------------|---------|--------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | —      | UEN1     | UEN0      | WAKE          | LPBACK        | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF    | TRMT      | URXISEL1      | URXISEL0      | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | _      | _        | _      | _      | _      | _        |           |               |               | UART1 | Transmit Re | egister |        |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _      | _      | _        |           |               |               | UART1 | Receive Re  | egister |        |        |       | 0000          |

| U1BRG       | 0228  |          |        |          |        |        | U      | ART1 Bau | id Rate G | enerator Pres | caler Registe | r     |             |         |        |        |       | 0000          |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN1     | UEN0      | WAKE          | LPBACK        | ABAUD | URXINV      | BRGH    | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF    | TRMT      | URXISEL1      | URXISEL0      | ADDEN | RIDLE       | PERR    | FERR   | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _      | _        |           |               |               | UART2 | Transmit Re | egister |        |        |       | xxxx          |

| U2RXREG     | 0236  | _        | _      | _        | _      | —      | _      | —        |           |               |               | UART2 | Receive Re  | egister |        |        |       | 0000          |

| U2BRG       | 0238  |          |        |          |        |        | U      | ART2 Bau | id Rate G | enerator Pres | caler Registe | r     |             |         |        |        |       | 0000          |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-6: SPI1 AND SPI2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9    | Bit 8        | Bit 7      | Bit 6       | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|---------|--------|--------|---------|----------|--------------|------------|-------------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT    | 0240  | SPIEN  | -      | SPISIDL |        | _      | SPIBEC2 | SPIBEC1  | SPIBEC0      | SRMPT      | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242  | _      |        | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE          | SSEN       | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2    | 0244  | FRMEN  | SPIFSD | FRMPOL  | _      | —      | _       | _        | _            | _          | —           | —      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI1BUF     | 0248  |        |        |         |        |        |         | SPI1 Tra | ansmit and R | eceive Buf | fer Registe | r      |        |        |        |        |        | 0000          |

| SPI2STAT    | 0260  | SPIEN  | _      | SPISIDL | _      | _      | SPIBEC2 | SPIBEC1  | SPIBEC0      | SRMPT      | SPIROV      | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI2CON1    | 0262  | _      |        | _       | DISSCK | DISSDO | MODE16  | SMP      | CKE          | SSEN       | CKP         | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI2CON2    | 0264  | FRMEN  | SPIFSD | FRMPOL  | _      | —      | _       | —        | _            | _          | —           | —      | _      | _      | _      | FRMDLY | SPIBEN | 0000          |

| SPI2BUF     | 0268  |        |        |         |        |        |         | SPI2 Tra | ansmit and R | eceive Buf | fer Registe | r      |        |        |        |        |        | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|             | ••    |        |        |        |          |            |          |          |          |             |       |        |          |          |          |          |          |               |

|-------------|-------|--------|--------|--------|----------|------------|----------|----------|----------|-------------|-------|--------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12   | Bit 11     | Bit 10   | Bit 9    | Bit 8    | Bit 7       | Bit 6 | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| ADC1BUF0    | 0300  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 0     |        |          |          |          |          |          | xxxx          |

| ADC1BUF1    | 0302  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 1     |        |          |          |          |          |          | xxxx          |

| ADC1BUF2    | 0304  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 2     |        |          |          |          |          |          | xxxx          |

| ADC1BUF3    | 0306  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 3     |        |          |          |          |          |          | xxxx          |

| ADC1BUF4    | 0308  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 4     |        |          |          |          |          |          | xxxx          |

| ADC1BUF5    | 030A  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 5     |        |          |          |          |          |          | xxxx          |

| ADC1BUF6    | 030C  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 6     |        |          |          |          |          |          | xxxx          |

| ADC1BUF7    | 030E  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 7     |        |          |          |          |          |          | xxxx          |

| ADC1BUF8    | 0310  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 8     |        |          |          |          |          |          | xxxx          |

| ADC1BUF9    | 0312  |        |        |        |          |            |          |          | ADC1 Da  | ta Buffer   | 9     |        |          |          |          |          |          | xxxx          |

| ADC1BUFA    | 0314  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 0     |        |          |          |          |          |          | xxxx          |

| ADC1BUFB    | 0316  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 1     |        |          |          |          |          |          | xxxx          |

| ADC1BUFC    | 0318  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 2     |        |          |          |          |          |          | xxxx          |

| ADC1BUFD    | 031A  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 3     |        |          |          |          |          |          | xxxx          |

| ADC1BUFE    | 031C  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 4     |        |          |          |          |          |          | xxxx          |

| ADC1BUFF    | 031E  |        |        |        |          |            |          |          | ADC1 Dat | ta Buffer 1 | 5     |        |          |          |          |          |          | xxxx          |

| AD1CON1     | 0320  | ADON   | I      | ADSIDL | ADDMABM  | —          | AD12B    | FORM1    | FORM0    | SSRC2       | SSRC1 | SSRC0  | SSRCG    | SIMSAM   | ASAM     | SAMP     | DONE     | 0000          |

| AD1CON2     | 0322  | VCFG2  | VCFG1  | VCFG0  | —        | —          | CSCNA    | CHPS1    | CHPS0    | BUFS        | SMPI4 | SMPI3  | SMPI2    | SMPI1    | SMPI0    | BUFM     | ALTS     | 0000          |

| AD1CON3     | 0324  | ADRC   | I      |        | SAMC4    | SAMC3      | SAMC2    | SAMC1    | SAMC0    | ADCS7       | ADCS6 | ADCS5  | ADCS4    | ADCS3    | ADCS2    | ADCS1    | ADCS0    | 0000          |

| AD1CHS123   | 0326  | _      | I      |        | CH123SB2 | CH123SB1   | CH123NB1 | CH123NB0 | CH123SB0 | —           |       |        | CH123SA2 | CH123SA1 | CH123NA1 | CH123NA0 | CH123SA0 | 0000          |

| AD1CHS0     | 0328  | CH0NB  |        | CH0SB5 | CH0SB4   | CH0SB3     | CH0SB2   | CH0SB1   | CH0SB0   | CH0NA       | -     | CH0SA5 | CH0SA4   | CH0SA3   | CH0SA2   | CH0SA1   | CH0SA0   | 0000          |

| AD1CSSH     | 032E  |        |        |        |          | CSS<31:24> |          |          |          | _           | _     | _      | —        |          | CSS<     | <19:16>  |          | 0000          |

| AD1CSSL     | 0330  |        |        |        |          |            |          |          | CSS      | <15:0>      |       |        |          |          |          |          |          | 0000          |

| AD1CON4     | 0332  | -      | _      | _      | —        | —          | _        | _        | ADDMAEN  | _           | _     | _      | _        | -        | DMABL2   | DMABL1   | DMABL0   | 0000          |

|             |       |        |        |        |          |            | <b>D</b> |          |          |             |       |        |          |          |          |          |          |               |

### TABLE 4-7: ADC1 REGISTER MAP

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-8: CTMU REGISTER MAP

|   | SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Reset<br>s |

|---|-------------|-------|---------|---------|----------|----------|----------|----------|----------|----------|---------|---------|----------|----------|----------|----------|-------|-------|-------------------|

| Ī | CTMUCON1    | 033A  | CTMUEN  | -       | CTMUSIDL | TGEN     | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | —       |          | _        | _        | _        | _     |       | 0000              |

| Ī | CTMUCON2    | 033C  | EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 | _     | _     | 0000              |

|   | CTMUICON    | 033E  | ITRIM5  | ITRIM4  | ITRIM3   | ITRIM2   | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | -       | _       |          | _        | _        | _        | _     | _     | 0000              |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-26: DMAC REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6    | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|---------|----------|---------|---------|---------|---------|---------|---------|---------------|

| DMA0CON     | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _     | —       | _        | AMODE1  | AMODE0  | —       | —       | MODE1   | MODE0   | 0000          |

| DMA0REQ     | 0B02  | FORCE  | _      | _      | _      | _      | _      | -     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA0STAL    | 0B04  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STAH    | 0B06  | _      | _      | _      | _      | _      |        |       |       |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA0STBL    | 0B08  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0STBH    | 0B0A  | _      | _      | —      | _      | _      |        | _     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA0PAD     | 0B0C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA0CNT     | 0B0E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA1CON     | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA1REQ     | 0B12  | FORCE  | —      | —      | _      |        | -      | —     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA1STAL    | 0B14  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STAH    | 0B16  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA1STBL    | 0B18  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1STBH    | 0B1A  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA1PAD     | 0B1C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA1CNT     | 0B1E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA2CON     | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA2REQ     | 0B22  | FORCE  | —      | _      | —      | —      | —      | _     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | 00FF          |

| DMA2STAL    | 0B24  |        |        |        | -      |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STAH    | 0B26  | —      | —      |        | _      |        | —      | —     | —     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA2STBL    | 0B28  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2STBH    | 0B2A  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA2PAD     | 0B2C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA2CNT     | 0B2E  | —      | —      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMA3CON     | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | -      | —     | _     | _       | —        | AMODE1  | AMODE0  | _       | _       | MODE1   | MODE0   | 0000          |

| DMA3REQ     | 0B32  | FORCE  | —      | —      | _      |        | -      | —     | _     | IRQSEL7 | IRQSEL6  | IRQSEL5 | IRQSEL4 | IRQSEL3 | IRQSEL2 | IRQSEL1 | IRQSEL0 | OOFF          |

| DMA3STAL    | 0B34  |        |        |        |        |        |        |       |       | STA<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STAH    | 0B36  | —      | —      | —      | _      |        | -      | —     | _     |         |          |         | STA<    | 23:16>  |         |         |         | 0000          |

| DMA3STBL    | 0B38  |        |        |        |        |        |        |       |       | STB<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3STBH    | 0B3A  | —      | —      | _      |        |        | _      | —     |       |         |          |         | STB<    | 23:16>  |         |         |         | 0000          |

| DMA3PAD     | 0B3C  |        |        |        |        |        |        |       |       | PAD<    | 15:0>    |         |         |         |         |         |         | 0000          |

| DMA3CNT     | 0B3E  | _      | _      |        |        |        |        |       |       |         | CNT<13:0 | )>      |         |         |         |         |         | 0000          |

| DMAPWC      | 0BF0  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       |         |         | PWCC    | )L<3:0> |         | 0000          |

| DMARQC      | 0BF2  |        | _      | _      | _      |        | _      | _     | _     | _       | _        | _       | _       |         | RQCC    | )L<3:0> |         | 0000          |

| DMAPPS      | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _     | _       | _        | _       | _       |         | PPS     | Г<3:0>  |         | 0000          |

dsPIC33EVXXXGM00X/10X FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory, program a row and to program two instruction words at a time. See Table 1 in the "dsPIC33EVXXXGM00X/10X Product Families" section for the page sizes of each device.memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to era

The Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of program memory, which consists of eight rows (512 instructions) at a time, and to program one row or two adjacent words at a time. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Table 30-13 in **Section 30.0 "Electrical Characteristics"** lists the typical erase and programming times.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. See Figure 4-1 to Figure 4-5 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

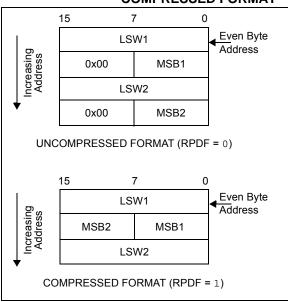

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

For more information on erasing and programming the Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

- Note 1: Before reprogramming either of the two words in a double-word pair, the user must erase the Flash memory page in which it is located.

- 2: Before reprogramming any word in a row, the user must erase the Flash memory page in which it is located.

#### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **"Flash Programming"** (DS70609) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and code examples on programming using RTSP.

#### REGISTER 5-5: NVMSRCADRH: NVM DATA MEMORY UPPER ADDRESS REGISTER

| U-0     | U-0   | U-0   | U-0      | U-0       | U-0   | U-0   | U-0   |

|---------|-------|-------|----------|-----------|-------|-------|-------|

| —       | _     | _     | _        | —         | _     | —     | —     |

| bit 15  |       |       |          |           |       |       | bit 8 |

|         |       |       |          |           |       |       |       |

| R/W-x   | R/W-x | R/W-x | R/W-x    | R/W-x     | R/W-x | R/W-x | R/W-x |

|         |       |       | NVMSRCAD | )R<23:16> |       |       |       |

| bit 7   |       |       |          |           |       |       | bit 0 |

|         |       |       |          |           |       |       |       |

| Legend: |       |       |          |           |       |       |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMSRCADRH<23:16>: Data Memory Upper Address bits

#### REGISTER 5-6: NVMSRCADRL: NVM DATA MEMORY LOWER ADDRESS REGISTER

| R/W-x           | R/W-x | R/W-x            | R/W-x    | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|----------|------------------|-----------------|-----------------|-------|

|                 |       |                  | NVMSRC   | CADR<15:8>       |                 |                 |       |

| bit 15          |       |                  |          |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x    | R/W-x            | R/W-x           | R/W-x           | r-0   |

|                 |       | NV               | MSRCADR< | 7:1>             |                 |                 | —     |

| bit 7           |       |                  |          |                  |                 |                 | bit C |

| Legend:         |       | r = Reserved     | bit      |                  |                 |                 |       |

| R = Readable b  | bit   | W = Writable     | bit      | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-1 NVMSRCADRL<15:1>: Data Memory Lower Address bits

bit 0 Reserved: Maintain as '0'

| R/W-0          | R/W-0                                     | U-0                                  | U-0             | R/W-0                        | U-0              | R/W-0            | R/W-0          |

|----------------|-------------------------------------------|--------------------------------------|-----------------|------------------------------|------------------|------------------|----------------|

| TRAPF          | R IOPUWR                                  |                                      | —               | VREGSF                       |                  | CM               | VREGS          |

| bit 15         |                                           |                                      |                 |                              |                  |                  | bit 8          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| R/W-0          | R/W-0                                     | R/W-0                                | R/W-0           | R/W-0                        | R/W-0            | R/W-1            | R/W-1          |

| EXTR           | SWR                                       | SWDTEN <sup>(2)</sup>                | WDTO            | SLEEP                        | IDLE             | BOR              | POR            |

| bit 7          |                                           |                                      |                 |                              |                  |                  | bit (          |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Legend:        |                                           |                                      |                 |                              |                  |                  |                |

| R = Reada      |                                           | W = Writable                         | oit             | •                            | nented bit, read | d as '0'         |                |

| -n = Value     | at POR                                    | '1' = Bit is set                     |                 | '0' = Bit is cle             | ared             | x = Bit is unk   | nown           |

| 6:4 <i>4 C</i> |                                           | Deast Flag bit                       |                 |                              |                  |                  |                |

| bit 15         |                                           | o Reset Flag bit<br>onflict Reset ha | e occurrod      |                              |                  |                  |                |

|                |                                           | onflict Reset ha                     |                 | ed                           |                  |                  |                |

| bit 14         | •                                         | egal Opcode or                       |                 |                              | ess Reset Flag   | a bit            |                |

|                |                                           | al Opcode detec                      |                 | •                            | -                |                  | ter used as ar |

|                |                                           | Pointer caused                       |                 | · · · · · · · · · · · ·      |                  |                  |                |

|                |                                           | I Opcode Rese                        |                 | zed W Register               | Reset has not    | occurred         |                |

| bit 13-12      | -                                         | nted: Read as '                      |                 |                              |                  |                  |                |

| bit 11         |                                           | ash Voltage Reg                      |                 |                              | o bit            |                  |                |

|                |                                           | Itage regulator i                    |                 | •                            | ing Sleep mode   | 2                |                |

| bit 10         |                                           | nted: Read as '                      | -               |                              | ing cleep mout   |                  |                |

| bit 9          | -                                         | ration Mismatch                      |                 |                              |                  |                  |                |

|                | •                                         | uration Mismatc                      | •               | occurred.                    |                  |                  |                |

|                |                                           | uration Mismato                      |                 |                              |                  |                  |                |

| bit 8          | VREGS: Volt                               | age Regulator S                      | Standby Durii   | ng Sleep bit                 |                  |                  |                |

|                |                                           | regulator is activ                   |                 |                              |                  |                  |                |

|                | •                                         | regulator goes i                     |                 | mode during Sle              | еер              |                  |                |

| bit 7          |                                           | nal Reset (MCL                       | ,               |                              |                  |                  |                |

|                |                                           | Clear (pin) Res<br>Clear (pin) Res   |                 |                              |                  |                  |                |

| bit 6          |                                           | are RESET (Instr                     |                 |                              |                  |                  |                |

|                |                                           | instruction has                      |                 |                              |                  |                  |                |

|                | 0 = A reset                               | instruction has                      | not been exe    | ecuted                       |                  |                  |                |

| bit 5          | SWDTEN: So                                | oftware Enable/                      | Disable of W    | DT bit <b><sup>(2)</sup></b> |                  |                  |                |

|                | 1 = WDT is e                              |                                      |                 |                              |                  |                  |                |

|                | 0 = WDT is d                              |                                      |                 |                              |                  |                  |                |

| bit 4          |                                           | hdog Timer Tim                       | -               | it                           |                  |                  |                |

|                |                                           | e-out has occur<br>e-out has not oc  |                 |                              |                  |                  |                |

|                |                                           |                                      |                 |                              |                  |                  |                |

| Note 1:        | All of the Reset sta<br>cause a device Re |                                      | set or cleare   | a in software. S             | etting one of th | ese bits in soft | ware does not  |

| 2:             | If the FWDTEN<1                           |                                      | n hits are '1 1 | ' (unprogramm                | ed) the WDT is   | always enable    | od rogardlaar  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |   | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignmen        |

|--------------------------------------------------|------------------|----------------|---|--------------------------------------------------|------------------|----------------------|

| 011 0001                                         | I/O              | RP49           |   | 101 1110                                         | I                | RPI94                |

| 110 0000                                         | I                | RPI96          |   | 101 1111                                         | Ι                | RPI95                |

| 110 0001                                         | I/O              | RP97           |   | 111 0011                                         |                  |                      |

| 110 0010                                         | —                | _              |   | 111 0100                                         |                  |                      |

| 110 0011                                         | —                | —              |   | 111 0101                                         |                  |                      |

| 110 0100                                         | _                | _              |   | 111 0110                                         | I/O              | RP118                |

| 110 0101                                         | _                | —              |   | 111 0111                                         | Ι                | RPI119               |

| 110 0110                                         | —                | _              |   | 111 1000                                         | I/O              | RP120                |

| 110 0111                                         | —                | _              |   | 111 1001                                         | I                | RPI121               |

| 110 1000                                         | —                | _              |   | 111 1010                                         | —                | _                    |

| 110 1001                                         | —                | _              |   | 111 1011                                         | _                |                      |

| 110 1010                                         | —                | —              |   | 111 1100                                         | Ι                | RPI124               |

| 110 1011                                         | —                | —              |   | 111 1101                                         | I/O              | RP125                |

| 101 0101                                         | —                | _              |   | 111 1110                                         | I/O              | RP126                |

| 101 0110                                         |                  | _              |   | 111 1111                                         | I/O              | RP127                |

| 101 0111                                         | _                | _              |   | 10110000                                         | I/O              | RP176 <sup>(1)</sup> |

| 110 1100                                         | —                | _              |   | 10110001                                         | I/O              | RP177 <sup>(1)</sup> |

| 110 1101                                         | —                |                | [ | 10110010                                         | I/O              | RP178 <sup>(1)</sup> |

| 110 1110                                         | _                | _              |   | 10110011                                         | I/O              | RP179 <sup>(1)</sup> |

| 110 1111                                         | _                | _              |   | 10110100                                         | I/O              | RP180 <sup>(1)</sup> |

| 111 0010                                         | _                | _              |   | 10110101                                         | I/O              | RP181 <sup>(1)</sup> |

Legend: Shaded rows indicate the PPS Input register values that are unimplemented.

Note 1: These are virtual pins. See Section 11.5.4.1 "Virtual Connections" for more information on selecting this pin assignment.

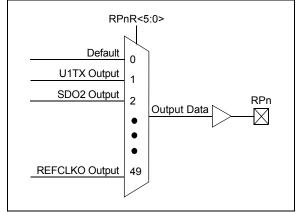

#### 11.5.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 to Register 11-31). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the Output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

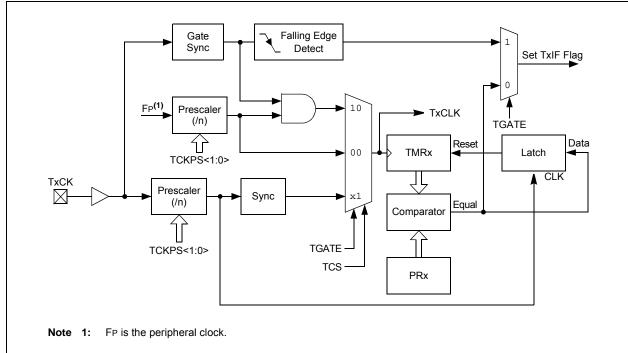

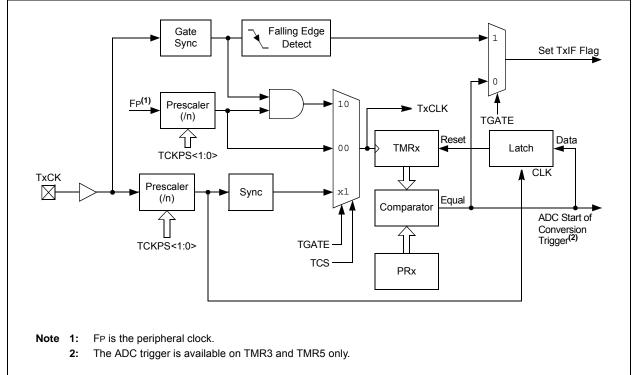

#### FIGURE 13-1: TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

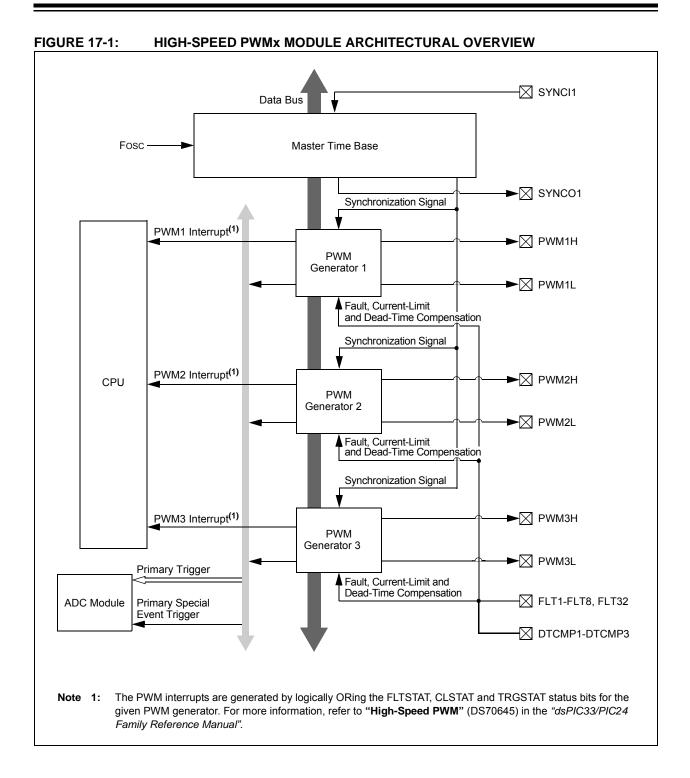

## 17.3 PWMx Control Registers

#### REGISTER 17-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS-0, HC | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|----------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT   | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |          |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | arable bit HS = Hardware Settable bit |                    |  |

|-------------------|-----------------------------|---------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'    |                    |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared                  | x = Bit is unknown |  |

| bit 15 | PTEN: PWMx Module Enable bit                                                                                                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 = PWMx module is enabled                                                                                                                              |

|        | 0 = PWMx module is disabled                                                                                                                             |

| bit 14 | Unimplemented: Read as '0'                                                                                                                              |

| bit 13 | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|        | 1 = PWMx time base halts in CPU Idle mode<br>0 = PWMx time base runs in CPU Idle mode                                                                   |

| bit 12 | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|        | <ul><li>1 = Special event interrupt is pending</li><li>0 = Special event interrupt is not pending</li></ul>                                             |

| bit 11 | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|        | 1 = Special event interrupt is enabled                                                                                                                  |

|        | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10 | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|        | 1 = Active Period register is updated immediately                                                                                                       |

|        | 0 = Active Period register updates occur on PWMx cycle boundaries                                                                                       |

| bit 9  | <b>SYNCPOL:</b> Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                |

|        | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

| 1.11.0 | 0 = SYNCI1/SYNCO1  is active-high                                                                                                                       |

| bit 8  | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|        | 1 = SYNCO1 output is enabled<br>0 = SYNCO1 output is disabled                                                                                           |

| bit 7  | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|        |                                                                                                                                                         |

|        | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|        |                                                                                                                                                         |

| Note 1 | : These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the us                                                   |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

| HS-0, HC                                   |                                                                  | HS-0, HC                                                                                                               | R/W-0                 | R/W-0             | R/W-0                | R/W-0                | R/W-0               |  |  |  |

|--------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|----------------------|----------------------|---------------------|--|--|--|

| FLTSTAT <sup>(1</sup>                      | ) CLSTAT <sup>(1)</sup>                                          | TRGSTAT                                                                                                                | FLTIEN                | CLIEN             | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |  |  |  |

| bit 15                                     |                                                                  | •                                                                                                                      |                       | •                 |                      |                      | bit 8               |  |  |  |

|                                            |                                                                  |                                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

| R/W-0                                      | R/W-0                                                            | R/W-0                                                                                                                  | U-0                   | U-0               | R/W-0                | R/W-0                | R/W-0               |  |  |  |

| DTC1                                       | DTC0                                                             | DTCP <sup>(3)</sup>                                                                                                    |                       | _                 | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |  |  |  |

| bit 7                                      |                                                                  | •                                                                                                                      |                       |                   | ·                    |                      | bit (               |  |  |  |

|                                            |                                                                  |                                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

| Legend:                                    |                                                                  | HC = Hardware                                                                                                          | Clearable bit         | HS = Hardwa       | are Settable bit     |                      |                     |  |  |  |

| R = Readab                                 | le bit                                                           | W = Writable bi                                                                                                        | t                     | U = Unimple       | mented bit, rea      | <b>d as</b> '0'      |                     |  |  |  |

| -n = Value a                               | t POR                                                            | '1' = Bit is set                                                                                                       |                       | '0' = Bit is cle  | eared                | x = Bit is unkr      | nown                |  |  |  |

|                                            |                                                                  |                                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

| bit 15                                     |                                                                  | ult Interrupt Statu                                                                                                    | us bit <sup>(1)</sup> |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | rupt is pending                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | rrupt is not pendi<br>ared by setting F                                                                                |                       |                   |                      |                      |                     |  |  |  |

| bit 14                                     |                                                                  | rent-Limit Interru                                                                                                     |                       |                   |                      |                      |                     |  |  |  |

|                                            | 1 = Current-limit interrupt is pending                           |                                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

| 0 = Current-limit interrupt is not pending |                                                                  |                                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | ared by setting C                                                                                                      |                       |                   |                      |                      |                     |  |  |  |

| bit 13                                     |                                                                  | igger Interrupt St                                                                                                     |                       |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | terrupt is pending                                                                                                     |                       |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | terrupt is not per<br>ared by setting T                                                                                |                       |                   |                      |                      |                     |  |  |  |

| bit 12                                     |                                                                  | t Interrupt Enable                                                                                                     |                       |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | rupt is enabled                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

|                                            | 0 = Fault inter                                                  | rupt is disabled                                                                                                       | and the FLTST         | AT bit is cleare  | ed                   |                      |                     |  |  |  |

| bit 11                                     | CLIEN: Curre                                                     | nt-Limit Interrup                                                                                                      | t Enable bit          |                   |                      |                      |                     |  |  |  |

|                                            |                                                                  | mit interrupt is er                                                                                                    |                       | 0.0747            |                      |                      |                     |  |  |  |

| L:1 4 0                                    |                                                                  | mit interrupt is di                                                                                                    |                       | CLSTAT bit is     | cleared              |                      |                     |  |  |  |

| bit 10                                     | •                                                                | ger Interrupt Ena<br>ent generates a                                                                                   |                       | loot              |                      |                      |                     |  |  |  |

|                                            |                                                                  | ent interrupts ar                                                                                                      |                       |                   | bit is cleared       |                      |                     |  |  |  |

| bit 9                                      | 00                                                               | dent Time Base I                                                                                                       |                       |                   |                      |                      |                     |  |  |  |

|                                            | -                                                                | register provides                                                                                                      |                       | iod for this PW   | /M generator         |                      |                     |  |  |  |

|                                            |                                                                  | egister provides t                                                                                                     |                       |                   |                      |                      |                     |  |  |  |

| bit 8                                      | MDCS: Maste                                                      | er Duty Cycle Re                                                                                                       | gister Select b       | it <sup>(2)</sup> |                      |                      |                     |  |  |  |

|                                            | •                                                                | ster provides dut<br>ister provides du                                                                                 |                       |                   | •                    |                      |                     |  |  |  |

| Note 1: S                                  | oftware must clea                                                | ar the interrupt st                                                                                                    | atus here and         | in the correspo   | onding IFSx bit      | in the interrupt     | controller.         |  |  |  |

|                                            | hese bits should                                                 | •                                                                                                                      |                       | •                 | •                    | Į.                   |                     |  |  |  |

|                                            | DTC<1:0> = $11$ for DTCP to be effective; else, DTCP is ignored. |                                                                                                                        |                       |                   |                      |                      |                     |  |  |  |

|                                            | he Independent T<br>AM bit is ignored                            | ne Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the AM bit is ignored. |                       |                   |                      |                      |                     |  |  |  |

| <b>5:</b> T                                | o operate in Exter<br>egister must be '0                         | rnal Period Rese                                                                                                       | t mode, the IT        | B bit must be '   | 1' and the CLM       | OD bit in the F      | CLCONx              |  |  |  |

## REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER

NOTES:

| DC CHARACTERISTICS |        |                                      | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |                     |       | ed)   |                                                                |  |

|--------------------|--------|--------------------------------------|---------------------------------------------------------------------------|---------------------|-------|-------|----------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                       | Min.                                                                      | Typ. <sup>(1)</sup> | Max.  | Units | Conditions                                                     |  |

|                    |        | Program Flash Memory                 |                                                                           |                     |       |       |                                                                |  |

| D130               | Eр     | Cell Endurance                       | 10,000                                                                    | —                   | _     | E/W   | -40°C to +125°C                                                |  |

| D131               | Vpr    | VDD for Read                         | 4.5                                                                       | —                   | 5.5   | V     |                                                                |  |

| D132b              | VPEW   | VDD for Self-Timed Write             | 4.5                                                                       | —                   | 5.5   | V     |                                                                |  |

| D134               | TRETD  | Characteristic Retention             | 20                                                                        | —                   | —     | Year  | Provided no other specifications are violated, -40°C to +125°C |  |

| D135               | IDDP   | Supply Current During<br>Programming | _                                                                         | 10                  | —     | mA    |                                                                |  |

| D136a              | Trw    | Row Write Cycle Time                 | 0.657                                                                     | —                   | 0.691 | ms    | Trw = 4965 FRC cycles,<br>Ta = +85°C (see <b>Note 2)</b>       |  |

| D136b              | Trw    | Row Write Cycle Time                 | 0.651                                                                     | _                   | 0.698 | ms    | Trw = 4965 FRC cycles,<br>Ta = +125°C (see <b>Note 2)</b>      |  |

| D137a              | TPE    | Page Erase Time                      | 19.44                                                                     | _                   | 20.44 | ms    | TPE = 146893 FRC cycles,<br>TA = +85°C (see <b>Note 2)</b>     |  |

| D137b              | TPE    | Page Erase Time                      | 19.24                                                                     | —                   | 20.65 | ms    | TPE = 146893 FRC cycles,<br>TA = +125°C (see <b>Note 2)</b>    |  |

| D138a              | Tww    | Word Write Cycle Time                | 45.78                                                                     | —                   | 48.15 | μs    | Tww = 346 FRC cycles,<br>TA = +85°C (see <b>Note 2)</b>        |  |

| D138b              | Tww    | Word Write Cycle Time                | 45.33                                                                     | _                   | 48.64 | μs    | Tww = 346 FRC cycles,<br>TA = +125°C (see <b>Note 2)</b>       |  |

#### TABLE 30-13: DC CHARACTERISTICS: PROGRAM MEMORY

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Other conditions: FRC = 7.3728 MHz, TUN<5:0> = b'011111 (for Min), TUN<5:0> = b'100000 (for Max). This parameter depends on the FRC accuracy (see Table 30-20) and the value of the FRC Oscillator Tuning register.

#### TABLE 30-14: ELECTRICAL CHARACTERISTICS: INTERNAL BAND GAP REFERENCE VOLTAGE

| DC CHAR      | DC CHARACTERISTICS |                                        |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |            |  |  |

|--------------|--------------------|----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|

| Param<br>No. | Symbol             | Characteristic                         | Min. | Тур.                                                                                                                                                                                                                                                                                    | Max. | Units | Conditions |  |  |

| DVR10        | Vbg                | Internal Band Gap Reference<br>Voltage | 1.14 | 1.2                                                                                                                                                                                                                                                                                     | 1.26 | V     |            |  |  |

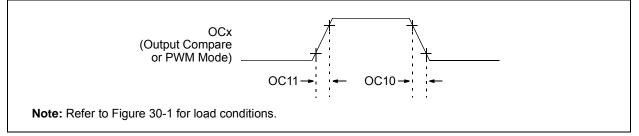

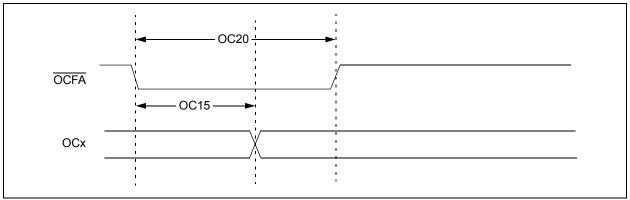

### FIGURE 30-8: OUTPUT COMPARE x (OCx) TIMING CHARACTERISTICS

#### TABLE 30-27: OUTPUT COMPARE x (OCx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |  |

|--------------------|--------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions         |  |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                                                       | _    |      | ns    | See Parameter DO32 |  |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                                                       | _    | —    | ns    | See Parameter DO31 |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

#### FIGURE 30-9: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |          |       |            |  |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                                                                                                                                                                                                                                                    | Тур. | Max.     | Units | Conditions |  |

| OC15               | Tfd    | Fault Input to PWMx I/O<br>Change | —                                                                                                                                                                                                                                                                                       | _    | Tcy + 20 | ns    |            |  |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                                                                                                                                                                                                                                                                |      | —        | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

| DC CHARACTERISTICS |        |                                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                            |  |

|--------------------|--------|-----------------------------------------------------------|------------------------------------------------------|------|------|-------|----------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                            | Min. <sup>(1)</sup>                                  | Тур. | Max. | Units | Conditions                 |  |

| HDO16              | Vol    | Output Low Voltage<br>4x Sink Driver Pins <sup>(2)</sup>  |                                                      |      | 0.4  | V     | Iol = 8.8 mA, VDD = 5.0V   |  |

| HDO10              | Vol    | Output Low Voltage<br>8x Sink Driver Pins <sup>(3)</sup>  | _                                                    |      | 0.4  | V     | IOL = 10.8 mA, VDD = 5.0V  |  |

| HDO26              | Vон    | Output High Voltage<br>4x Sink Driver Pins <sup>(2)</sup> | Vdd - 0.6                                            |      | _    | V     | Іон = -8.3 mA, Vdd = 5.0V  |  |

| HDO20              | Vон    | Output High Voltage<br>8x Sink Driver Pins                | Vdd - 0.6                                            | _    | _    | V     | Іон = -12.3 mA, Vdd = 5.0V |  |

#### TABLE 31-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized but not tested.

2: Includes all I/O pins that are not 8x sink driver pins (see below).

**3:** Includes the pins, such as RA3, RA4 and RB<15:10> for 28-pin devices, RA3, RA4, RA9 and RB<15:10> for 44-pin devices, and RA4, RA7, RA9, RB<15:10> and RC15 for 64-pin devices.

#### TABLE 31-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHA       | DC CHARACTERISTICS |                                            |                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                     |  |

|--------------|--------------------|--------------------------------------------|---------------------|------------------------------------------------------|------|-------|-------------------------------------|--|

| Param<br>No. | Symbol             | Characteristic                             | Min. <sup>(1)</sup> | Тур.                                                 | Max. | Units | Conditions                          |  |

| HBO10        | VBOR               | BOR Event on VDD<br>Transition High-to-Low | 4.15                | 4.285                                                | 4.4  | V     | VDD (see Note 2, Note 3 and Note 4) |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

- **2:** The VBOR specification is relative to the VDD.

- **3:** The device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, op amp/comparator and comparator voltage reference will have degraded performance. Device functionality is tested but is not characterized.

- 4: The start-up VDD must rise above 4.6V.

#### TABLE 31-11: DC CHARACTERISTICS: PROGRAM MEMORY

| DC CHA       | RACTERI | STICS                         | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |      |      |       |                                                                  |