Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 36x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm106t-i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

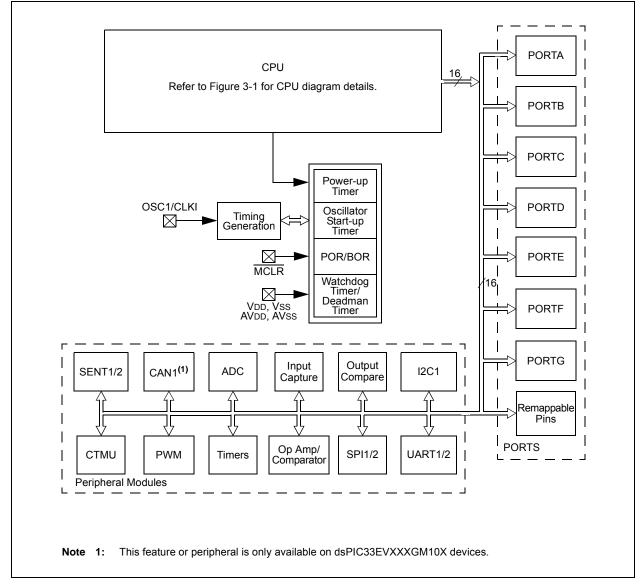

This document contains device-specific information for the dsPIC33EVXXXGM00X/10X family Digital Signal Controller (DSC) devices.

dsPIC33EVXXXGM00X/10X family devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EVXXXGM00X/10X FAMILY BLOCK DIAGRAM

| R/W-0               | U-0                                                                                                                                                                                  | R/W-0                                                   | R/W-0                                                | EGISTER             | R-0           | R-0             | R-0   |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------|---------------------|---------------|-----------------|-------|

| VAR                 | 0-0                                                                                                                                                                                  | US1                                                     | US0                                                  | EDT <sup>(1)</sup>  | DL2           | DL1             | DL0   |

| bit 15              |                                                                                                                                                                                      | 031                                                     | 030                                                  | EDI                 | DL2           |                 | bit   |

| R/W-0               | R/W-0                                                                                                                                                                                | R/W-1                                                   | R/W-0                                                | R/C-0               | R-0           | R/W-0           | R/W-0 |

| SATA                | SATB                                                                                                                                                                                 | SATDW                                                   | ACCSAT                                               | IPL3 <sup>(2)</sup> | SFA           | R/W-0           | IF    |

| bit 7               | SAID                                                                                                                                                                                 | SAIDW                                                   | ACCOAL                                               | IF LOV /            | SFA           | RND             | bit   |

| Legend:             |                                                                                                                                                                                      | C = Clearable                                           | a hit                                                |                     |               |                 |       |

| R = Readable        | hit                                                                                                                                                                                  | W = Writable                                            |                                                      | U = Unimplem        | onted hit rea | d as '0'        |       |

| -n = Value at F     |                                                                                                                                                                                      | '1' = Bit is set                                        |                                                      | '0' = Bit is clea   |               | x = Bit is unkr |       |

|                     | -                                                                                                                                                                                    |                                                         |                                                      |                     |               |                 |       |

| bit 15              | 1 = Variable e                                                                                                                                                                       | exception proc                                          | ocessing Later<br>essing latency                     | is enabled          |               |                 |       |

| L:4 4 4             |                                                                                                                                                                                      | • •                                                     | sing latency is o                                    | enabled             |               |                 |       |

| bit 14<br>bit 13-12 | •                                                                                                                                                                                    | ted: Read as '                                          | o<br>igned/Signed (                                  | Control hito        |               |                 |       |

|                     | <ul> <li>11 = Reserved</li> <li>10 = DSP engine multiplies are mixed-sign</li> <li>01 = DSP engine multiplies are unsigned</li> <li>00 = DSP engine multiplies are signed</li> </ul> |                                                         |                                                      |                     |               |                 |       |

| bit 11              | <b>EDT:</b> Early DO Loop Termination Control bit <sup>(1)</sup><br>1 = Terminates executing the DO loop at the end of the current loop iteration<br>0 = No effect                   |                                                         |                                                      |                     |               |                 |       |

| bit 10-8            | 111 = 7 DO lo                                                                                                                                                                        | oops are active                                         |                                                      | ts                  |               |                 |       |

| bit 7               |                                                                                                                                                                                      | Saturation En                                           |                                                      |                     |               |                 |       |

|                     |                                                                                                                                                                                      | ator A saturatio<br>ator A saturatio                    |                                                      |                     |               |                 |       |

| bit 6               | 1 = Accumula                                                                                                                                                                         | B Saturation En<br>ator B saturatio<br>ator B saturatio | n is enabled                                         |                     |               |                 |       |

| bit 5               | 1 = Data Spa                                                                                                                                                                         | ce write satura                                         | from DSP Engi<br>tion is enabled<br>tion is disabled |                     | Enable bit    |                 |       |

| bit 4               |                                                                                                                                                                                      | cumulator Satu                                          | ration Mode S                                        |                     |               |                 |       |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

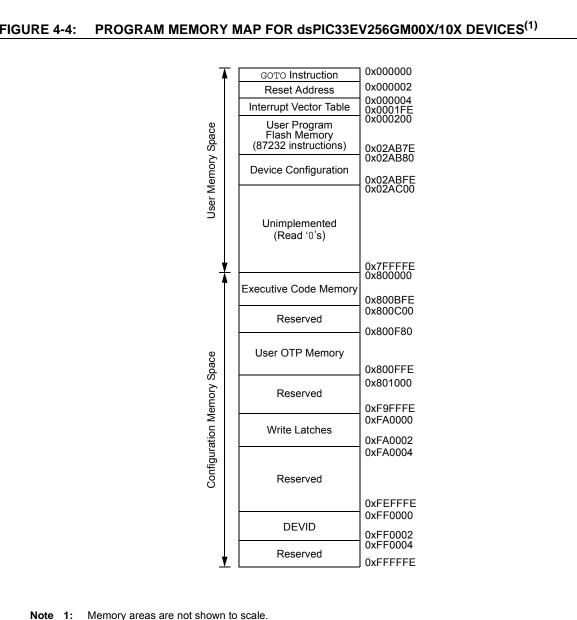

#### FIGURE 4-4:

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### TABLE 4-45: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.4.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

| For the MOV instructions, the addressing      |

|-----------------------------------------------|

| mode specified in the instruction can differ  |

| for the source and destination EA. How-       |

| ever, the 4-bit Wb (Register Offset) field is |

| shared by both source and destination         |

| (but typically only used by one).             |

|                                               |

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set, {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X Data Space) and W11 (in Y Data Space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.4.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (Branch) instructions use 16-bit signed literals to specify the Branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| U-0                                                                  | U-0                                                                                                                             | U-0             | U-0          | U-0                                     | U-0              | U-0    | U-0    |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-----------------------------------------|------------------|--------|--------|--|

| —                                                                    | —                                                                                                                               |                 | —            | —                                       | _                |        |        |  |

| bit 15                                                               |                                                                                                                                 |                 |              |                                         |                  |        | bit 8  |  |

|                                                                      |                                                                                                                                 |                 |              |                                         |                  |        |        |  |

| U-0                                                                  | U-0                                                                                                                             | U-0             | U-0          | R-0                                     | R-0              | R-0    | R-0    |  |

| —                                                                    | <u> </u>                                                                                                                        |                 | —            | RQCOL3                                  | RQCOL2           | RQCOL1 | RQCOL0 |  |

| bit 7                                                                |                                                                                                                                 |                 |              |                                         |                  |        | bit 0  |  |

|                                                                      |                                                                                                                                 |                 |              |                                         |                  |        |        |  |

| Legend:                                                              |                                                                                                                                 |                 |              |                                         |                  |        |        |  |

| R = Readab                                                           | le bit                                                                                                                          | W = Writable    | bit          | U = Unimpler                            | nented bit, read | as '0' |        |  |

| -n = Value a                                                         | -n = Value at POR '1' = Bit is set                                                                                              |                 |              | '0' = Bit is cleared x = Bit is unknown |                  |        |        |  |

|                                                                      |                                                                                                                                 |                 |              |                                         |                  |        |        |  |

| bit 15-4                                                             | Unimplemer                                                                                                                      | nted: Read as ' | 0'           |                                         |                  |        |        |  |

| bit 3                                                                | RQCOL3: Cl                                                                                                                      | nannel 3 Transf | er Request C | Collision Flag bit                      |                  |        |        |  |

|                                                                      |                                                                                                                                 |                 |              | est collision is d                      |                  |        |        |  |

|                                                                      |                                                                                                                                 | •               | •            | est collision is n                      |                  |        |        |  |

| bit 2                                                                |                                                                                                                                 |                 | •            | Collision Flag bit                      |                  |        |        |  |

|                                                                      | 1 = User force and interrupt-based request collision is detected                                                                |                 |              |                                         |                  |        |        |  |

| 0 = User force and interrupt-based request collision is not detected |                                                                                                                                 |                 |              |                                         |                  |        |        |  |

| bit 1                                                                | bit 1 RQCOL1: Channel 1 Transfer Request Collision Flag bit<br>1 = User force and interrupt-based request collision is detected |                 |              |                                         |                  |        |        |  |

|                                                                      | 0 = User force and interrupt-based request collision is not detected                                                            |                 |              |                                         |                  |        |        |  |

| bit 0                                                                | <b>RQCOL0:</b> Channel 0 Transfer Request Collision Flag bit                                                                    |                 |              |                                         |                  |        |        |  |

|                                                                      |                                                                                                                                 |                 | •            | est collision is d                      |                  |        |        |  |

|                                                                      |                                                                                                                                 |                 |              | est collision is n                      |                  |        |        |  |

|                                                                      |                                                                                                                                 |                 |              |                                         |                  |        |        |  |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0                                   | U-0                                                | U-0              | U-0            | U-0                                | U-0   | U-0             | U-0   |  |  |

|---------------------------------------|----------------------------------------------------|------------------|----------------|------------------------------------|-------|-----------------|-------|--|--|

| —                                     | _                                                  | _                | —              | —                                  | _     | _               | _     |  |  |

| bit 15                                |                                                    |                  |                |                                    |       |                 | bit 8 |  |  |

| r                                     |                                                    |                  |                |                                    |       |                 |       |  |  |

| U-0                                   | U-0                                                | U-0              | U-0            | R-1                                | R-1   | R-1             | R-1   |  |  |

|                                       |                                                    | <u> </u>         | —              |                                    | LSTCH | l<3:0>          |       |  |  |

| bit 7                                 |                                                    |                  |                |                                    |       |                 | bit 0 |  |  |

| r                                     |                                                    |                  |                |                                    |       |                 |       |  |  |

| Legend:                               |                                                    |                  |                |                                    |       |                 |       |  |  |

| R = Readable bit W = Writable bit U = |                                                    |                  |                | U = Unimplemented bit, read as '0' |       |                 |       |  |  |

| -n = Value at                         | t POR                                              | '1' = Bit is set |                | '0' = Bit is cle                   | ared  | x = Bit is unki | nown  |  |  |

|                                       |                                                    |                  |                |                                    |       |                 |       |  |  |

| bit 15-4                              | Unimplemen                                         | ted: Read as '   | 0'             |                                    |       |                 |       |  |  |

| bit 3-0                               | LSTCH<3:0>                                         | : Last DMAC C    | hannel Active  | Status bits                        |       |                 |       |  |  |

|                                       |                                                    | MA transfer has  | s occurred sin | ce system Res                      | set   |                 |       |  |  |

|                                       | 1110 = Reserved                                    |                  |                |                                    |       |                 |       |  |  |

|                                       |                                                    |                  |                |                                    |       |                 |       |  |  |

|                                       |                                                    |                  |                |                                    |       |                 |       |  |  |

|                                       | 0100 = Reserved                                    |                  |                |                                    |       |                 |       |  |  |

|                                       | 0011 = Last data transfer was handled by Channel 3 |                  |                |                                    |       |                 |       |  |  |

|                                       | 0010 = Last data transfer was handled by Channel 2 |                  |                |                                    |       |                 |       |  |  |

|                                       |                                                    | data transfer wa |                |                                    |       |                 |       |  |  |

|                                       | 0000 = Last data transfer was handled by Channel 0 |                  |                |                                    |       |                 |       |  |  |

# 10.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of peripherals being clocked constitutes lower consumed power.

The dsPIC33EVXXXGM00X/10X family devices can manage power consumption in the following four methods:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- · Software Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

#### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

# 10.1 Clock Frequency and Clock Switching

The dsPIC33EVXXXGM00X/10X family devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or highprecision oscillators by simply changing the NOSCx bits (OSCCON<10:8>). For more information on the process of changing a system clock during operation, as well as limitations to the process, see **Section 9.0 "Oscillator Configuration"**.

## 10.2 Instruction-Based Power-Saving Modes

The dsPIC33EVXXXGM00X/10X family devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembler syntax of the PWRSAV instruction is shown in Example 10-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the Assembler Include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

# 16.1 Output Compare Control Registers

# REGISTER 16-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                                                                                                      | R/W-0                                                                                            | R/W-0                                                                                                           | R/W-0                                    | R/W-0            | U-0             | U-0   |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|-----------------|-------|

|               | —                                                                                                        | OCSIDL                                                                                           | OCTSEL2                                                                                                         | OCTSEL1                                  | OCTSEL0          | —               | —     |

| bit 15        |                                                                                                          |                                                                                                  |                                                                                                                 |                                          |                  |                 | bit 8 |

|               |                                                                                                          |                                                                                                  |                                                                                                                 |                                          |                  |                 |       |

| R/W-0         | U-0                                                                                                      | U-0                                                                                              | R/W-0, HSC                                                                                                      | R/W-0                                    | R/W-0            | R/W-0           | R/W-0 |

| ENFLTA        | <u> </u>                                                                                                 | _                                                                                                | OCFLTA                                                                                                          | TRIGMODE                                 | OCM2             | OCM1            | OCM0  |

| bit 7         |                                                                                                          |                                                                                                  |                                                                                                                 |                                          |                  |                 | bit ( |

| Legend:       |                                                                                                          | HSC = Hardv                                                                                      | vare Settable/Cl                                                                                                | earable bit                              |                  |                 |       |

| R = Readable  | e bit                                                                                                    | W = Writable                                                                                     | bit                                                                                                             | U = Unimplem                             | nented bit, read | <b>l as</b> '0' |       |

| -n = Value at | POR                                                                                                      | '1' = Bit is set                                                                                 | t                                                                                                               | '0' = Bit is clea                        | ared             | x = Bit is unkn | iown  |

| bit 12-10     | OCTSEL<2:0<br>111 = Periphe<br>110 = Reserv<br>101 = Reserv<br>100 = T1CLK<br>011 = T5CLK<br>010 = T4CLK | >: Output Con<br>eral clock (FP)<br>red<br>is the clock so<br>is the clock so<br>is the clock so | inues to operate<br>npare x Clock S<br>purce of the OC<br>purce of the OC<br>purce of the OC<br>purce of the OC | elect bits<br>x (only the syne<br>x<br>x |                  | s is supported) |       |

|               |                                                                                                          |                                                                                                  | ource of the OC                                                                                                 |                                          |                  |                 |       |

| bit 9-8       | Unimplemen                                                                                               | ted: Read as '                                                                                   | 0'                                                                                                              |                                          |                  |                 |       |

| bit 7         | 1 = Output C                                                                                             | ompare Fault                                                                                     | k Fault A Input E<br>A (OCFA) input<br>A (OCFA) input                                                           | is enabled                               |                  |                 |       |

| bit 6-5       | -                                                                                                        | ted: Read as '                                                                                   |                                                                                                                 |                                          |                  |                 |       |

| bit 4         | 1 = PWM Fai                                                                                              | ult A condition                                                                                  | ndition Status bit<br>on the OCFA pi<br>on the OCFA pi                                                          | in has occurred                          |                  |                 |       |

| bit 3         | 1 = TRIGSTA                                                                                              | T (OCxCON2                                                                                       | Mode Select bit<br><6>) is cleared v<br>nly by software                                                         |                                          | = OCxTMR or i    | n software      |       |

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

# 17.2 **PWM Resources**

Many useful resources are provided on the main product page on the Microchip web site (www.microchip.com) for the devices listed in this data sheet. This product page contains the latest updates and additional information.

Note: In case the above link is not accessible, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

#### 17.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

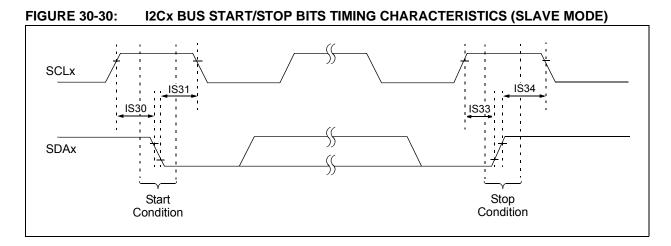

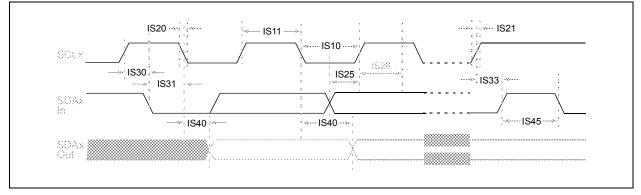

# REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1 (CONTINUED)

| bit 7   | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled.</li> </ul>                                                                                                                                                                                                                              |

| bit 6   | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                                                                                                                                                                                                      |

|         | In I <sup>2</sup> C Slave mode only, used in conjunction with the SCLREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                                                                                                                                                                                            |

| bit 5   | ACKDT: Acknowledge Data bit                                                                                                                                                                                                                                                                                                                                                                               |

|         | In I <sup>2</sup> C Master mode, during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.<br>In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.<br>1 = NACK is sent<br>0 = ACK is sent |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                                                                                                                                                                                                |

| bit 3   | <b>RCEN:</b> Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C, automatically cleared by hardware at the end of 8-bit receive data byte</li> <li>0 = Receive sequence is not in progress</li> </ul>                                                                                                                                                                                                                 |

| bit 2   | PEN: Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins</li> <li>0 = Stop condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                                |

| bit 1   | RSEN: Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                    |

|         | <ul> <li>1 = Initiates Restart condition on SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                          |

| bit 0   | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                              |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                                                                                                                                                                                          |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

### REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

| bit 1 | <ul> <li>BUFM: Buffer Fill Mode Select bit</li> <li>1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt</li> <li>0 = Always starts filling the buffer from the Start address</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | ALTS: Alternate Input Sample Mode Select bit<br>1 = Uses channel input selects for Sample MUX A on the first sample and Sample MUX B on the next sample<br>0 = Always uses channel input selects for Sample MUX A                                                         |

Note 1: The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

| U-0          | U-0                                                                              | U-0                | U-0            | U-0              | U-0                                | U-0                | R/W-0            |  |  |  |

|--------------|----------------------------------------------------------------------------------|--------------------|----------------|------------------|------------------------------------|--------------------|------------------|--|--|--|

|              | —                                                                                | —                  | —              | _                | —                                  | _                  | ADDMAEN          |  |  |  |

| bit 15       |                                                                                  | •<br>•             |                |                  |                                    |                    | bit 8            |  |  |  |

|              |                                                                                  |                    |                |                  |                                    |                    |                  |  |  |  |

| U-0          | U-0                                                                              | U-0                | U-0            | U-0              | R/W-0                              | R/W-0              | R/W-0            |  |  |  |

| _            | —                                                                                | —                  | —              | —                | DMABL2                             | DMABL1             | DMABL0           |  |  |  |

| bit 7        |                                                                                  |                    |                |                  |                                    |                    | bit 0            |  |  |  |

|              |                                                                                  |                    |                |                  |                                    |                    |                  |  |  |  |

| Legend:      |                                                                                  |                    |                |                  |                                    |                    |                  |  |  |  |

| R = Readab   | le bit                                                                           | W = Writable bit   |                |                  | U = Unimplemented bit, read as '0' |                    |                  |  |  |  |

| -n = Value a | t POR                                                                            | '1' = Bit is set   |                | '0' = Bit is cle | eared                              | x = Bit is unknown |                  |  |  |  |

|              |                                                                                  |                    |                |                  |                                    |                    |                  |  |  |  |

| bit 15-9     | Unimplemen                                                                       | ted: Read as '0    | )'             |                  |                                    |                    |                  |  |  |  |

| bit 8        | ADDMAEN: A                                                                       | ADCx DMA Ena       | able bit       |                  |                                    |                    |                  |  |  |  |

|              |                                                                                  |                    |                |                  | ster for transfer                  |                    |                  |  |  |  |

|              | 0 = Conversio                                                                    | on results are sto | red in the ADC | 1BUF0 throug     | h ADC1BUFF re                      | egisters; DMA v    | vill not be used |  |  |  |

| bit 7-3      | Unimplemented: Read as '0'                                                       |                    |                |                  |                                    |                    |                  |  |  |  |

| bit 2-0      | bit 2-0 DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits |                    |                |                  |                                    |                    |                  |  |  |  |

|              |                                                                                  | es 128 words o     |                | Ų I              | :                                  |                    |                  |  |  |  |

|              |                                                                                  | es 64 words of     |                | • •              |                                    |                    |                  |  |  |  |

|              |                                                                                  | es 32 words of     |                | 0 1              |                                    |                    |                  |  |  |  |

|              |                                                                                  | es 16 words of     |                |                  |                                    |                    |                  |  |  |  |

|              |                                                                                  | es 8 words of b    |                |                  |                                    |                    |                  |  |  |  |

|              | 010 = Allocates 4 words of buffer to each analog input                           |                    |                |                  |                                    |                    |                  |  |  |  |

#### REGISTER 24-4: ADxCON4: ADCx CONTROL REGISTER 4

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

#### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

- bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(3)</sup>

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

$\frac{\text{If CPOL} = 1 \text{ (inverted polarity):}}{\text{Low-to-high transition of the comparator output.}}$  $\frac{\text{If CPOL} = 0 \text{ (non-inverted polarity):}}{\text{High-to-low transition of the comparator output.}}$

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

- If CPOL = 0 (non-inverted polarity):

- Low-to-high transition of the comparator output.

- 00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to the internal CVREFIN voltage

- 0 = VIN+ input connects to the CxIN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator x Channel Select bits<sup>(1)</sup>

- 11 = Inverting input of op amp/comparator connects to the CxIN4- pin

- 10 = Inverting input of op amp/comparator connects to the CxIN3- pin

- 01 = Inverting input of op amp/comparator connects to the CxIN2- pin

- 00 = Inverting input of op amp/comparator connects to the CxIN1- pin

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- 3: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

# 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| AC CHARACTERISTICS  |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |           |         |       |                                                  |

|---------------------|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-------|--------------------------------------------------|

| Param<br>No.        | Symbol | Symbol Characteristic          |                                                                                                                                                                                                                                                                                                  | Тур.      | Max.    | Units | Conditions                                       |

|                     |        | ADC A                          | Accuracy                                                                                                                                                                                                                                                                                         | (10-Bit   | Mode)   |       |                                                  |

| AD20b Nr Resolution |        |                                | 1(                                                                                                                                                                                                                                                                                               | ) data bi | ts      | bits  |                                                  |

| AD21b               | INL    | Integral Nonlinearity          | -1.5                                                                                                                                                                                                                                                                                             | —         | +1.5    | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 5.5V |

| AD22b               | DNL    | Differential Nonlinearity      | ≥ 1                                                                                                                                                                                                                                                                                              | —         | < 1     | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD23b               | Gerr   | Gain Error                     | 1                                                                                                                                                                                                                                                                                                | 3         | 6       | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD24b               | EOFF   | Offset Error                   | 1                                                                                                                                                                                                                                                                                                | 2         | 4       | LSb   | Vinl = AVss = Vrefl = 0V,<br>AVdd = Vrefh = 5.5V |

| AD25b               | —      | Monotonicity <sup>(2)</sup>    | _                                                                                                                                                                                                                                                                                                |           | _       |       | Guaranteed                                       |

|                     |        | Dynamic                        | Performa                                                                                                                                                                                                                                                                                         | nce (10-  | Bit Mod | e)    |                                                  |

| AD30b               | THD    | Total Harmonic Distortion      | _                                                                                                                                                                                                                                                                                                |           | -64     | dB    |                                                  |

| AD31b               | SINAD  | Signal to Noise and Distortion | 57                                                                                                                                                                                                                                                                                               | 58.5      | _       | dB    |                                                  |

| AD32b               | SFDR   | Spurious Free Dynamic<br>Range | 72                                                                                                                                                                                                                                                                                               | _         | —       | dB    |                                                  |

| AD33b               | Fnyq   | Input Signal Bandwidth         | _                                                                                                                                                                                                                                                                                                | —         | 550     | kHz   |                                                  |

| AD34b               | ENOB   | Effective Number of Bits       | 9.16                                                                                                                                                                                                                                                                                             | 9.4       |         | bits  |                                                  |

# TABLE 30-56: ADC MODULE SPECIFICATIONS (10-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

2: The conversion result never decreases with an increase in the input voltage.

# dsPIC33EVXXXGM00X/10X FAMILY

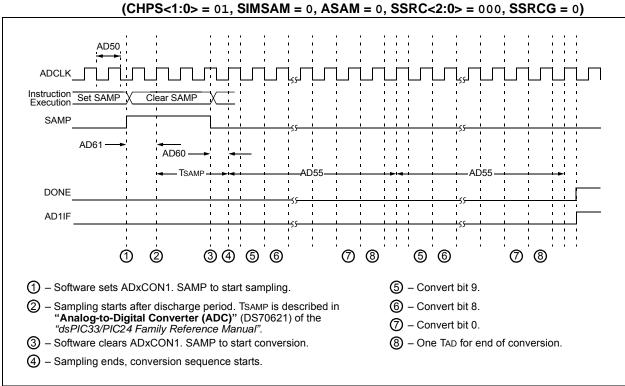

# FIGURE 30-35: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS

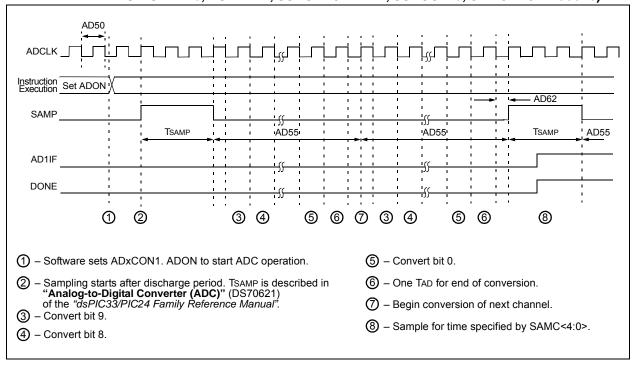

#### FIGURE 30-36: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

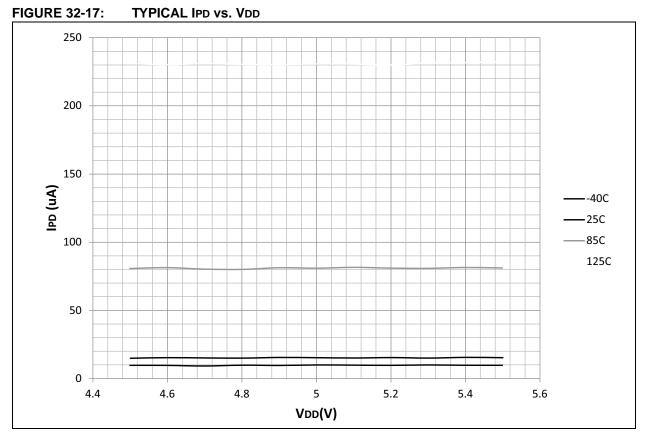

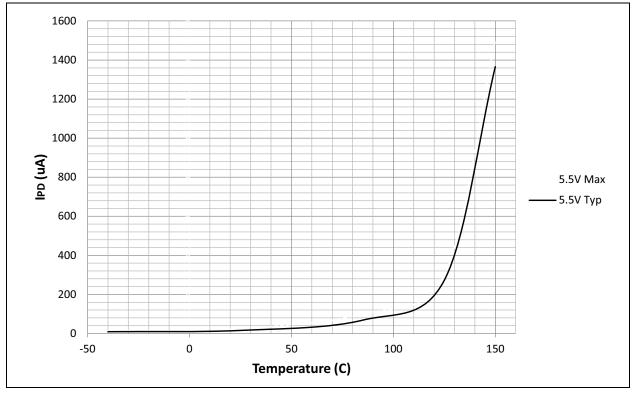

## 32.4 IPD

© 2013-2016 Microchip Technology Inc.

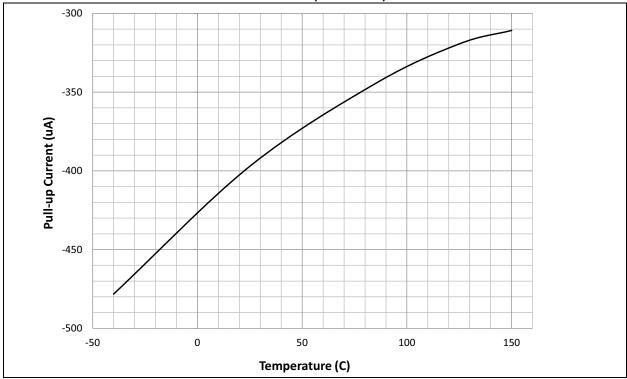

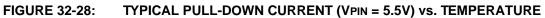

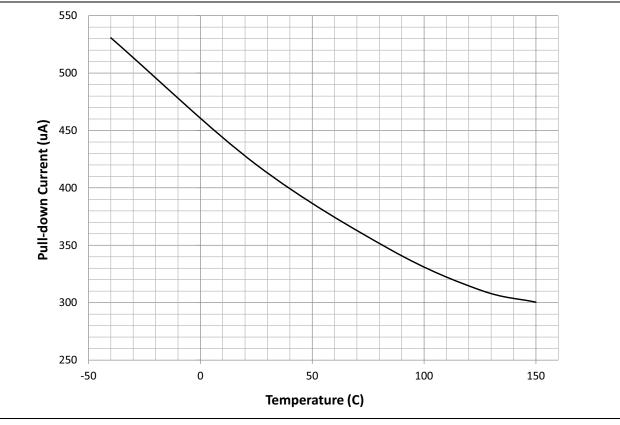

# 32.8 Pull-up and Pull-Down Current

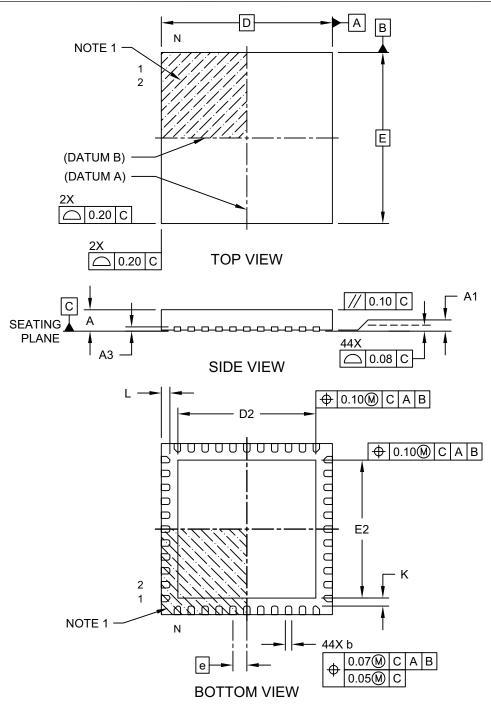

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging