Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (43K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 36x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev128gm106t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

| R/SO-0            |                       | R/W-0                          | R/W-0                  | U-0                       | U-0                       | R/W-0                     | R/W-0                    |

|-------------------|-----------------------|--------------------------------|------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| WR <sup>(1)</sup> | WREN <sup>(1)</sup>   | WRERR <sup>(1)</sup>           | NVMSIDL <sup>(2)</sup> |                           |                           | RPDF                      | URERR                    |

| bit 15            |                       |                                |                        |                           |                           | •                         | bit 8                    |

|                   |                       |                                |                        |                           |                           |                           |                          |

| U-0               | U-0                   | U-0                            | U-0                    | R/W-0                     | R/W-0                     | R/W-0                     | R/W-0                    |

| —                 | —                     | —                              | —                      | NVMOP3 <sup>(1,3,4)</sup> | NVMOP2 <sup>(1,3,4)</sup> | NVMOP1 <sup>(1,3,4)</sup> | NVMOP0 <sup>(1,3,4</sup> |

| bit 7             |                       |                                |                        |                           |                           |                           | bit (                    |

| Legend:           |                       | SO = Settable                  | e Onlv bit             |                           |                           |                           |                          |

| R = Reada         | able bit              | W = Writable                   | 3                      | U = Unimplem              | ented bit, read a         | <b>as</b> '0'             |                          |

| -n = Value        | at POR                | '1' = Bit is set               | t                      | '0' = Bit is clea         |                           | x = Bit is unkn           | own                      |

|                   |                       |                                |                        |                           |                           |                           |                          |

| bit 15            | WR: Write C           | Control bit <sup>(1)</sup>     |                        |                           |                           |                           |                          |

|                   |                       |                                |                        |                           |                           | ion is self-time          | d and the bit is         |

|                   |                       |                                |                        | tion is complete          |                           |                           |                          |

| bit 14            | -                     | e Enable bit <sup>(1)</sup>    | ation is comp          | lete and inactive         | <del>J</del>              |                           |                          |

| 011 14            |                       | ogram or erase                 | operations a           | re enabled                |                           |                           |                          |

|                   |                       | ogram or erase                 |                        |                           |                           |                           |                          |

| bit 13            | =                     | rite Sequence I                |                        |                           |                           |                           |                          |

|                   |                       |                                |                        | nce attempt, or t         | termination has           | occurred (bit is s        | et automaticall          |

|                   |                       | set attempt of th              |                        |                           |                           |                           |                          |

| L:1 10            | -                     | -                              | -                      | npleted normally          | /                         |                           |                          |

| bit 12            |                       | NVM Stop in Idl                |                        |                           | ce enters Idle m          |                           |                          |

|                   |                       |                                |                        |                           | enters Idle mod           |                           |                          |

| bit 11-10         | -                     | nted: Read as                  |                        |                           |                           |                           |                          |

| bit 9             | RPDF: Row             | Programming                    | Data Format (          | Control bit               |                           |                           |                          |

|                   |                       |                                |                        | compressed fo             | rmat                      |                           |                          |

|                   | 0 = Row data          | a to be stored i               | in RAM is in a         | n uncompresse             | d format                  |                           |                          |

| bit 8             |                       | -                              | -                      | run Error Flag b          |                           |                           |                          |

|                   |                       | gramming ope<br>underrun has o |                        | en terminated du          | ue to a data unc          | lerrun error              |                          |

| bit 7-4           | Unimpleme             | nted: Read as                  | <b>'</b> 0'            |                           |                           |                           |                          |

| Note 1:           | These bits can c      | only be reset or               | n a POR                |                           |                           |                           |                          |

|                   | If this bit is set, t | -                              |                        | avings (lidle). a         | and upon exiting          | ldle mode, the            | re is a delav            |

|                   | (TVREG) before I      |                                |                        |                           |                           | ,,                        | · · · <b>j</b>           |

| ٥.                |                       |                                |                        |                           |                           |                           |                          |

- 3: All other combinations of NVMOP<3:0> are unimplemented.

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- **5:** Two adjacent words on a 4-word boundary are programmed during execution of this operation.

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

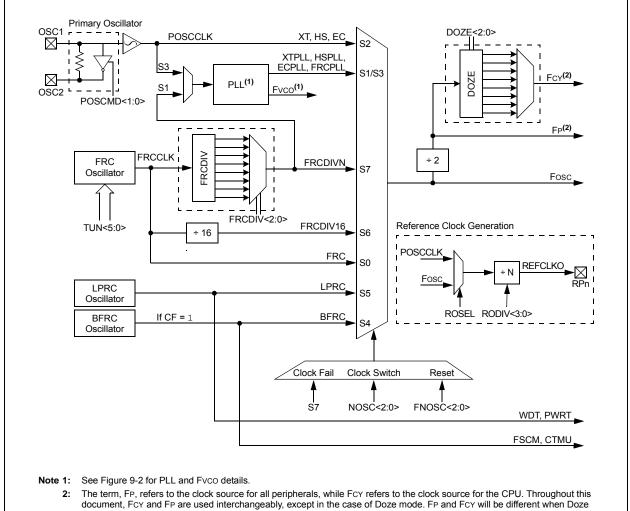

**OSCILLATOR SYSTEM DIAGRAM**

FIGURE 9-1:

The dsPIC33EVXXXGM00X/10X family oscillator system provides:

- On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- On-the-Fly Clock Switching between Various Clock Sources

- · Doze mode for System Power Savings

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown.

- Backup FRC (BFRC) Function that Provides a System Clock when there is a Failure in the FRC Clock

- Configuration bits for Clock Source Selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

| R/W-0         | R/W-0                                 | R/W-0                                                                  | R/W-0    | R/W-0            | U-0            | R/W-0               | U-0          |  |  |

|---------------|---------------------------------------|------------------------------------------------------------------------|----------|------------------|----------------|---------------------|--------------|--|--|

| T5MD          | T4MD                                  | T3MD                                                                   | T2MD     | T1MD             | —              | PWMMD               | —            |  |  |

| bit 15        |                                       |                                                                        |          |                  |                |                     | bit 8        |  |  |

| R/W-0         | R/W-0                                 | R/W-0                                                                  | R/W-0    | R/W-0            | U-0            | R/W-0               | R/W-0        |  |  |

| I2C1MD        |                                       |                                                                        |          |                  | 0-0            | C1MD <sup>(1)</sup> |              |  |  |

| bit 7         | U2MD                                  | U1MD                                                                   | SPI2MD   | SPI1MD           | —              | CTMD                | AD1MD<br>bit |  |  |

|               |                                       |                                                                        |          |                  |                |                     |              |  |  |

| Legend:       |                                       |                                                                        |          |                  |                |                     |              |  |  |

| R = Readable  |                                       | W = Writable                                                           |          | •                | mented bit, re | ad as '0'           |              |  |  |

| -n = Value at | POR                                   | '1' = Bit is set                                                       |          | '0' = Bit is cle | ared           | x = Bit is unkn     | own          |  |  |

| bit 15        | T5MD: Timer                           | 5 Module Disal                                                         | ole bit  |                  |                |                     |              |  |  |

|               |                                       | odule is disable<br>odule is enable                                    |          |                  |                |                     |              |  |  |

| bit 14        | T4MD: Timer                           | 4 Module Disal                                                         | ole bit  |                  |                |                     |              |  |  |

|               | 1 = Timer4 m                          | odule is disable                                                       | ed       |                  |                |                     |              |  |  |

| bit 13        |                                       | ) = Timer4 module is enabled<br><b>T3MD:</b> Timer3 Module Disable bit |          |                  |                |                     |              |  |  |

|               |                                       | odule is disable<br>odule is enable                                    |          |                  |                |                     |              |  |  |

| bit 12        | T2MD: Timer                           | er2 Module Disable bit                                                 |          |                  |                |                     |              |  |  |

|               | -                                     | odule is disable<br>odule is enable                                    |          |                  |                |                     |              |  |  |

| bit 11        | T1MD: Timer                           | : Timer1 Module Disable bit                                            |          |                  |                |                     |              |  |  |

|               | -                                     | odule is disable<br>odule is enable                                    |          |                  |                |                     |              |  |  |

| bit 10        | Unimplemen                            | ted: Read as '                                                         | 0'       |                  |                |                     |              |  |  |

| bit 9         | PWMMD: PW                             | /M Module Dis                                                          | able bit |                  |                |                     |              |  |  |

|               |                                       | dule is disabled<br>dule is enabled                                    |          |                  |                |                     |              |  |  |

| bit 8         | Unimplemen                            | ted: Read as '                                                         | 0'       |                  |                |                     |              |  |  |

| bit 7         | 12C1MD: 12C                           | 1 Module Disal                                                         | ole bit  |                  |                |                     |              |  |  |

|               |                                       | lule is disabled<br>lule is enabled                                    |          |                  |                |                     |              |  |  |

| bit 6         | U2MD: UART                            | 2 Module Disa                                                          | ble bit  |                  |                |                     |              |  |  |

|               | -                                     | nodule is disabl<br>nodule is enable                                   |          |                  |                |                     |              |  |  |

| bit 5         | <b>U1MD:</b> UART1 Module Disable bit |                                                                        |          |                  |                |                     |              |  |  |

|               |                                       | nodule is disabl<br>nodule is enable                                   |          |                  |                |                     |              |  |  |

| bit 4         | SPI2MD: SPI                           | 2 Module Disa                                                          | ole bit  |                  |                |                     |              |  |  |

|               |                                       | lule is disabled<br>lule is enabled                                    |          |                  |                |                     |              |  |  |

| bit 3         | SPI1MD: SPI                           | 1 Module Disa                                                          | ole bit  |                  |                |                     |              |  |  |

|               |                                       | dule is disabled<br>dule is enabled                                    |          |                  |                |                     |              |  |  |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** This bit is available on dsPIC33EVXXXGM10X devices only.

## 17.3 PWMx Control Registers

#### REGISTER 17-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS-0, HC | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|----------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT   | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |          |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 |                         |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15 | PTEN: PWMx Module Enable bit                                                                                                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 = PWMx module is enabled                                                                                                                              |

|        | 0 = PWMx module is disabled                                                                                                                             |

| bit 14 | Unimplemented: Read as '0'                                                                                                                              |

| bit 13 | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|        | 1 = PWMx time base halts in CPU Idle mode<br>0 = PWMx time base runs in CPU Idle mode                                                                   |

| bit 12 | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|        | <ul><li>1 = Special event interrupt is pending</li><li>0 = Special event interrupt is not pending</li></ul>                                             |

| bit 11 | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|        | 1 = Special event interrupt is enabled                                                                                                                  |

|        | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10 | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|        | 1 = Active Period register is updated immediately                                                                                                       |

|        | 0 = Active Period register updates occur on PWMx cycle boundaries                                                                                       |

| bit 9  | <b>SYNCPOL:</b> Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                |

|        | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

| 1.11.0 | 0 = SYNCI1/SYNCO1  is active-high                                                                                                                       |

| bit 8  | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|        | 1 = SYNCO1 output is enabled<br>0 = SYNCO1 output is disabled                                                                                           |

| bit 7  | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|        |                                                                                                                                                         |

|        | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|        |                                                                                                                                                         |

| Note 1 | : These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the us                                                   |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

## dsPIC33EVXXXGM00X/10X FAMILY

## REGISTER 17-18: AUXCONx: PWMx AUXILIARY CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | R/W-0     | R/W-0     | R/W-0     | R/W-0     |

|--------|-----|-----|-----|-----------|-----------|-----------|-----------|

| —      | —   |     | —   | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | BLANKSEL0 |

| bit 15 |     |     |     |           |           |           | bit 8     |

| U-0   | U-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   |

|-------|-----|----------|----------|----------|----------|---------|---------|

| —     | —   | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN | CHOPLEN |

| bit 7 |     |          |          |          |          |         | bit 0   |

| Legend:      |                                                                                                                                                                                                                                                         |                                                                                                                                      |                                |                                       |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------|--|--|--|--|--|--|

| R = Readab   | ole bit                                                                                                                                                                                                                                                 | W = Writable bit                                                                                                                     | U = Unimplemented bit,         | read as '0'                           |  |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                                                                                                                                                  | '1' = Bit is set                                                                                                                     | '0' = Bit is cleared           | x = Bit is unknown                    |  |  |  |  |  |  |

| bit 15-12    | Unimple                                                                                                                                                                                                                                                 | mented: Read as '0'                                                                                                                  |                                |                                       |  |  |  |  |  |  |

| bit 11-8     | BLANKS                                                                                                                                                                                                                                                  | SEL<3:0>: PWMx State Bla                                                                                                             | nk Source Select bits          |                                       |  |  |  |  |  |  |

|              | the BCH<br>1001 = F<br>•<br>•<br>0100 = F                                                                                                                                                                                                               | and BCL bits in the LEBCO<br>Reserved                                                                                                | Nx register).                  | ult input signals (if enabled through |  |  |  |  |  |  |

|              | 0001 = F                                                                                                                                                                                                                                                | 0010 = PWM2H is selected as the state blank source<br>0001 = PWM1H is selected as the state blank source<br>0000 = No state blanking |                                |                                       |  |  |  |  |  |  |

| bit 7-6      | Unimple                                                                                                                                                                                                                                                 | mented: Read as '0'                                                                                                                  |                                |                                       |  |  |  |  |  |  |

| bit 5-2      | CHOPSEL<3:0>: PWMx Chop Clock Source Select bits                                                                                                                                                                                                        |                                                                                                                                      |                                |                                       |  |  |  |  |  |  |

|              | The sele<br>1001 = F<br>•                                                                                                                                                                                                                               |                                                                                                                                      | lisable (Chop) the selected PW | /Mx outputs.                          |  |  |  |  |  |  |

|              | •<br>0100 = Reserved<br>0011 = PWM3H is selected as the chop clock source<br>0010 = PWM2H is selected as the chop clock source<br>0001 = PWM1H is selected as the chop clock source<br>0000 = Chop clock generator is selected as the chop clock source |                                                                                                                                      |                                |                                       |  |  |  |  |  |  |

| bit 1        | 1 = PWN                                                                                                                                                                                                                                                 | EN: PWMxH Output Choppi<br>IxH chopping function is en<br>IxH chopping function is dis                                               | abled                          |                                       |  |  |  |  |  |  |

| bit 0        | L = PWN                                                                                                                                                                                                                                                 | EN: PWMxL Output Choppin<br>IxL chopping function is ena<br>IxL chopping function is disa                                            | ng Enable bit<br>abled         |                                       |  |  |  |  |  |  |

## 18.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

**Note:** This insures that the first frame transmission after initialization is not shifted or corrupted.

- 2. In Non-Framed 3-Wire mode (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = <u>0</u>, always place a pull-down resistor on SSx.

- **Note:** This will insure that during power-up and initialization, the master/slave will not lose sync due to an errant SCKx transition that would cause the slave to accumulate data shift errors, for both transmit and receive, appearing as corrupted data.

- 3. FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame Sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. For more information, refer to the SPI specifications in Section 30.0 "Electrical Characteristics".

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

To avoid invalid slave read data to the master, the user's master software must ensure enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF Transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPIx Shift register and is empty once the data transmission begins.

## 20.2 Transmit Mode

By default, the SENTx module is configured for transmit operation. The module can be configured for continuous asynchronous message frame transmission, or alternatively, for Synchronous mode triggered by software. When enabled, the transmitter will send a Sync followed by the appropriate number of data nibbles, an optional CRC and optional pause pulse. The tick period used by the SENTx transmitter is set by writing a value to the TICKTIME<15:0> (SENTxCON2<15:0>) bits. The tick period calculations are shown in Equation 20-1.

#### EQUATION 20-1: TICK PERIOD CALCULATION

$TICKTIME < 15:0 > = \frac{TTICK}{TCLK} - 1$

An optional pause pulse can be used in Asynchronous mode to provide a fixed message frame time period. The frame period used by the SENTx transmitter is set by writing a value to the FRAMETIME<15:0> (SENTxCON3<15:0>) bits. The formulas used to calculate the value of frame time are shown in Equation 20-2.

#### EQUATION 20-2: FRAME TIME CALCULATIONS

FRAMETIME<15:0> = TTICK/TFRAME

*FRAMETIME*<15:0>  $\geq$  122 + 27*N*

$FRAMETIME < 15:0 \ge 848 + 12N$

Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6

**Note:** The module will not produce a pause period with less than 12 ticks, regardless of the FRAMETIME<15:0> value. FRAMETIME<15:0> values beyond 2047 will have no effect on the length of a data frame.

### 20.2.1 TRANSMIT MODE CONFIGURATION

#### 20.2.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 0 for Transmit mode.

- Write TXM (SENTxCON1<10>) = 0 for Asynchronous Transmit mode or TXM = 1 for Synchronous mode.

- 3. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 4. Write CRCEN (SENTxCON1<8>) for hardware or software CRC calculation.

- 5. Write PPP (SENTxCON1<7>) for optional pause pulse.

- 6. If PPP = 1, write TFRAME to SENTxCON3.

- 7. Write SENTxCON2 with the appropriate value for desired tick period.

- 8. Enable interrupts and set interrupt priority.

- 9. Write initial status and data values to SENTxDATH/L.

- 10. If CRCEN = 0, calculate CRC and write the value to CRC<3:0> (SENTxDATL<3:0>).

- 11. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

User software updates to SENTxDATH/L must be performed after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt to trigger data writes.

## REGISTER 21-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Baud rate measurement on the next character is enabled – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or has completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                                     |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                                  |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                               |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                       |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                                    |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                                    |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                            |

| Note 1: | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the                                                                                                                                                                |

- "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- **3:** This feature is only available on 44-pin and 64-pin devices.

- **4:** This feature is only available on 64-pin devices.

## REGISTER 22-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                | R/W-0            | R/W-0             | R/W-0                              | R/W-0                         | R/W-0              | R/W-0  |  |

|---------------|----------------------|------------------|-------------------|------------------------------------|-------------------------------|--------------------|--------|--|

| F11BP3        | F11BP2               | F11BP1           | F11BP0            | F10BP3                             | F10BP2                        | F10BP1             | F10BP0 |  |

| bit 15        |                      |                  |                   |                                    |                               |                    | bit 8  |  |

|               |                      |                  |                   |                                    |                               |                    |        |  |

| R/W-0         | R/W-0                | R/W-0            | R/W-0             | R/W-0                              | R/W-0                         | R/W-0              | R/W-0  |  |

| F9BP3         | F9BP2                | F9BP1            | F9BP0             | F8BP3                              | F8BP2                         | F8BP1              | F8BP0  |  |

| bit 7         |                      |                  |                   |                                    |                               | •                  | bit 0  |  |

|               |                      |                  |                   |                                    |                               |                    |        |  |

| Legend:       |                      |                  |                   |                                    |                               |                    |        |  |

| R = Readable  | e bit                | W = Writable     | bit               | U = Unimplemented bit, read as '0' |                               | <b>as</b> '0'      |        |  |

| -n = Value at | POR                  | '1' = Bit is set |                   | '0' = Bit is cleared               |                               | x = Bit is unknown |        |  |

|               |                      |                  |                   |                                    |                               |                    |        |  |

| bit 15-12     | F11BP<3:0>:          | RX Buffer Mas    | sk for Filter 11  | bits                               |                               |                    |        |  |

|               |                      | hits received in |                   |                                    |                               |                    |        |  |

|               | 1110 <b>= Filter</b> | hits received in | RX Buffer 14      | ł                                  |                               |                    |        |  |

|               | •                    |                  |                   |                                    |                               |                    |        |  |

|               | •                    |                  |                   |                                    |                               |                    |        |  |

|               | 0001 = Filter        | hits received in | RX Buffer 1       |                                    |                               |                    |        |  |

|               | 0000 = Filter        | hits received in | RX Buffer 0       |                                    |                               |                    |        |  |

| bit 11-8      | F10BP<3:0>           | RX Buffer Ma     | sk for Filter 10  | ) bits (same va                    | lues as bits 15- <sup>,</sup> | 12)                |        |  |

| bit 7-4       | F9BP<3:0>:           | RX Buffer Masl   | c for Filter 9 b  | its (same value                    | es as bits 15-12)             | )                  |        |  |

| bit 3-0       | F8BP<3:0>:           | RX Buffer Masl   | c for Filter 8 bi | its (same value                    | es as bits 15-12)             | )                  |        |  |

|               |                      |                  |                   |                                    |                               |                    |        |  |

| R/W-0         | U-0                                                                                                         | R/W-0                                        | R/W-0                            | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------|------------------|----------------------------------------|----------------|-------|--|--|--|--|

| HLMS          | 0-0                                                                                                         | OCEN                                         | OCNEN                            | OBEN             | OBNEN                                  | OAEN           | OANEN |  |  |  |  |

|               |                                                                                                             | OCEN                                         | OCINEIN                          | OBEN             | OBINEIN                                | UAEN           |       |  |  |  |  |

| bit 15        |                                                                                                             |                                              |                                  |                  |                                        |                | bit 8 |  |  |  |  |

| R/W-0         | R/W-0                                                                                                       | R/W-0                                        | R/W-0                            | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |  |  |  |  |

| NAGS          | PAGS                                                                                                        | ACEN                                         | ACNEN                            | ABEN             | ABNEN                                  | AAEN           | AANEN |  |  |  |  |

| bit 7         |                                                                                                             |                                              |                                  |                  |                                        |                | bit   |  |  |  |  |

|               |                                                                                                             |                                              |                                  |                  |                                        |                |       |  |  |  |  |

| Legend:       |                                                                                                             |                                              |                                  |                  |                                        |                |       |  |  |  |  |

| R = Readabl   | e bit                                                                                                       | W = Writable                                 | bit                              | U = Unimple      | mented bit, read                       | <b>as</b> '0'  |       |  |  |  |  |

| -n = Value at | POR                                                                                                         | '1' = Bit is se                              | t                                | '0' = Bit is cle | eared                                  | x = Bit is unk | nown  |  |  |  |  |

| bit 15        | 1 = The mask                                                                                                | ing (blanking)                               |                                  | event any asse   | erted ('0') compa<br>erted ('1') compa |                |       |  |  |  |  |

| bit 14        | Unimplemen                                                                                                  | ted: Read as                                 | ·0'                              | -                |                                        | -              |       |  |  |  |  |

| bit 13        | OCEN: OR G                                                                                                  | ate C Input E                                | nable bit                        |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             | nnected to OF                                | 0                                |                  |                                        |                |       |  |  |  |  |

| bit 12        | <ul> <li>0 = MCI is not connected to OR gate</li> <li>OCNEN: OR Gate C Input Inverted Enable bit</li> </ul> |                                              |                                  |                  |                                        |                |       |  |  |  |  |

|               | 1 = Inverted I                                                                                              | 1 = Inverted MCI is connected to OR gate     |                                  |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             | 0 = Inverted MCI is not connected to OR gate |                                  |                  |                                        |                |       |  |  |  |  |

| bit 11        |                                                                                                             | OBEN: OR Gate B Input Enable bit             |                                  |                  |                                        |                |       |  |  |  |  |

|               | 1 = MBI is connected to OR gate<br>0 = MBI is not connected to OR gate                                      |                                              |                                  |                  |                                        |                |       |  |  |  |  |

| bit 10        | OBNEN: OR Gate B Input Inverted Enable bit                                                                  |                                              |                                  |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             | MBI is connected to OR gate                  |                                  |                  |                                        |                |       |  |  |  |  |

| bit 9         |                                                                                                             | OAEN: OR Gate A Input Enable bit             |                                  |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             | 1 = MAI is connected to OR gate              |                                  |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             | t connected to                               | -                                |                  |                                        |                |       |  |  |  |  |

| bit 8         |                                                                                                             | •                                            | Inverted Enable                  | e bit            |                                        |                |       |  |  |  |  |

|               |                                                                                                             |                                              | ted to OR gate<br>nected to OR g | ate              |                                        |                |       |  |  |  |  |

| bit 7         | NAGS: AND Gate Output Inverted Enable bit                                                                   |                                              |                                  |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             |                                              | cted to OR gate<br>nnected to OR |                  |                                        |                |       |  |  |  |  |

| bit 6         | PAGS: AND Gate Output Enable bit                                                                            |                                              |                                  |                  |                                        |                |       |  |  |  |  |

|               | 1 = ANDI is connected to OR gate<br>0 = ANDI is not connected to OR gate                                    |                                              |                                  |                  |                                        |                |       |  |  |  |  |

| bit 5         |                                                                                                             | Gate C Input I                               | -                                |                  |                                        |                |       |  |  |  |  |

|               | 1 = MCI is co                                                                                               | nnected to AN                                | ID gate                          |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             | t connected to                               | •                                |                  |                                        |                |       |  |  |  |  |

| bit 4         |                                                                                                             | -                                            | t Inverted Enab                  |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             |                                              | ted to AND gate<br>nected to AND |                  |                                        |                |       |  |  |  |  |

|               |                                                                                                             |                                              |                                  |                  |                                        |                |       |  |  |  |  |

## 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EV instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into following five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the Status Flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have the following three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

## **30.1 DC Characteristics**

| Characteristic | VDD Range                     | Temperature Range | Maximum MIPS                 |  |  |

|----------------|-------------------------------|-------------------|------------------------------|--|--|

| Characteristic | (in Volts)                    | (in °C)           | dsPIC33EVXXXGM00X/10X Family |  |  |

| I-Temp         | 4.5V to 5.5V <sup>(1,2)</sup> | -40°C to +85°C    | 70                           |  |  |

| E-Temp         | 4.5V to 5.5V <sup>(1,2)</sup> | -40°C to +125°C   | 60                           |  |  |

#### TABLE 30-1: OPERATING MIPS vs. VOLTAGE

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, op amp/comparator and comparator voltage reference will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

2: When BOR is enabled, the device will work from 4.7V to 5.5V.

**Note 1:** Customer operating voltage range is specified as: 4.5V to 5.5V.

### TABLE 30-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                           | Symbol | Min.        | Тур.        | Max. | Unit |

|--------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices:                                                                  |        |             |             |      |      |

| Operating Junction Temperature Range                                                             | TJ     | -40         | _           | +125 | °C   |

| Operating Ambient Temperature Range                                                              | TA     | -40         | —           | +85  | °C   |

| Extended Temperature Devices:                                                                    |        |             |             |      |      |

| Operating Junction Temperature Range                                                             | TJ     | -40         | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                              | TA     | -40         | —           | +125 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD \times (IDD - \Sigma IOH)$ | PD     | PINT + PI/O |             |      | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$          |        |             |             |      |      |

| Maximum Allowed Power Dissipation                                                                | PDMAX  | (           | TJ — TA)/θJ | IA   | W    |

#### TABLE 30-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                       | Symbol | Тур. | Max. | Unit | Notes |

|------------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-Pin QFN, 9x9x0.9 mm   | θJA    | 28.0 |      | °C/W | 1     |

| Package Thermal Resistance, 64-Pin TQFP, 10x10x1 mm  | θJA    | 48.3 | —    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin QFN, 8x8 mm       | θJA    | 29.0 | —    | °C/W | 1     |

| Package Thermal Resistance, 44-Pin TQFP, 10x10x1 mm  | θJA    | 49.8 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin QFN-S, 6x6x0.9 mm | θJA    | 30.0 | —    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SOIC, 7.50 mm     | θJA    | 69.7 | _    | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SSOP, 5.30 mm     | θJA    | 71.0 |      | °C/W | 1     |

| Package Thermal Resistance, 28-Pin SPDIP, 300 mil    | θJA    | 60.0 | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

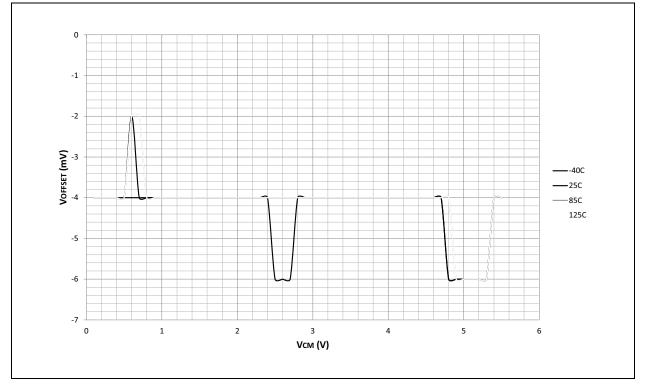

#### TABLE 30-50: OP AMP/COMPARATOR x SPECIFICATIONS

| DC CHARACTERISTICS |                 |                                           | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |              |       |                                                    |  |

|--------------------|-----------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|-------|----------------------------------------------------|--|

| Param<br>No.       | Symbol          | Characteristic                            | Min.                                                                                                                                                                                                                                                                                                 | Тур. <sup>(1)</sup> | Max.         | Units | Conditions                                         |  |

|                    |                 | Con                                       | parator AC C                                                                                                                                                                                                                                                                                         | haracte             | ristics      |       |                                                    |  |

| CM10               | Tresp           | Response Time                             | _                                                                                                                                                                                                                                                                                                    | 19                  | 80           | ns    | V+ input step of 100 mV,<br>V- input held at VDD/2 |  |

| CM11               | TMC2OV          | Comparator Mode<br>Change to Output Valid | —                                                                                                                                                                                                                                                                                                    | _                   | 10           | μs    |                                                    |  |

|                    |                 | Con                                       | nparator DC C                                                                                                                                                                                                                                                                                        | haracte             | ristics      |       |                                                    |  |

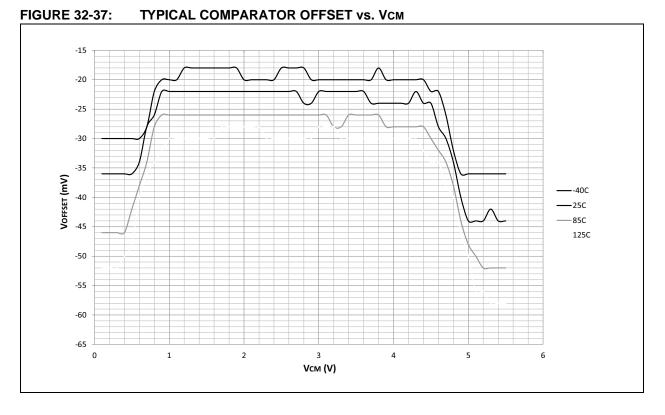

| CM30               | VOFFSET         | Comparator Offset<br>Voltage              | -80                                                                                                                                                                                                                                                                                                  | ±60                 | 80           | mV    |                                                    |  |

| CM31               | VHYST           | Input Hysteresis Voltage                  |                                                                                                                                                                                                                                                                                                      | 30                  | —            | mV    |                                                    |  |

| CM32               | Trise/<br>Tfall | Comparator Output<br>Rise/Fall Time       | —                                                                                                                                                                                                                                                                                                    | 20                  | —            | ns    | 1 pF load capacitance<br>on input                  |  |

| CM33               | Vgain           | Open-Loop Voltage Gain                    | —                                                                                                                                                                                                                                                                                                    | 90                  | —            | db    |                                                    |  |

| CM34               | VICM            | Input Common-Mode<br>Voltage              | AVss                                                                                                                                                                                                                                                                                                 | —                   | AVDD         | V     |                                                    |  |

|                    |                 | Or                                        | o Amp AC Cha                                                                                                                                                                                                                                                                                         | aracteris           | stics        |       |                                                    |  |

| CM20               | SR              | Slew Rate                                 | _                                                                                                                                                                                                                                                                                                    | 9                   | _            | V/µs  | 10 pF load                                         |  |

| CM21               | Рм              | Phase Margin                              | —                                                                                                                                                                                                                                                                                                    | 35                  | —            | °C    | G = 100V/V, 10 pF load                             |  |

| CM22               | Gм              | Gain Margin                               | —                                                                                                                                                                                                                                                                                                    | 20                  | —            | db    | G = 100V/V, 10 pF load                             |  |

| CM23               | GBW             | Gain Bandwidth                            | —                                                                                                                                                                                                                                                                                                    | 10                  | —            | MHz   | 10 pF load                                         |  |

|                    |                 | Op                                        | o Amp DC Cha                                                                                                                                                                                                                                                                                         | aracteris           | stics        |       |                                                    |  |

| CM40               | VCMR            | Common-Mode Input<br>Voltage Range        | AVss                                                                                                                                                                                                                                                                                                 | —                   | AVDD         | V     |                                                    |  |

| CM41               | CMRR            | Common-Mode<br>Rejection Ratio            | —                                                                                                                                                                                                                                                                                                    | 45                  | —            | db    | Vcm = AVdd/2                                       |  |

| CM42               | VOFFSET         | Op Amp Offset Voltage                     | -50                                                                                                                                                                                                                                                                                                  | ±6                  | 50           | mV    |                                                    |  |

| CM43               | Vgain           | Open-Loop Voltage Gain                    | _                                                                                                                                                                                                                                                                                                    | 90                  | —            | db    |                                                    |  |

| CM44               | los             | Input Offset Current                      | —                                                                                                                                                                                                                                                                                                    | —                   | —            | _     | See pad leakage<br>currents in Table 30-10         |  |

| CM45               | lв              | Input Bias Current                        | _                                                                                                                                                                                                                                                                                                    |                     | —            | _     | See pad leakage<br>currents in Table 30-10         |  |

| CM46               | Ιουτ            | Output Current                            | —                                                                                                                                                                                                                                                                                                    | _                   | 420          | μA    | With minimum value of RFEEDBACK (CM48)             |  |