#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm002-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

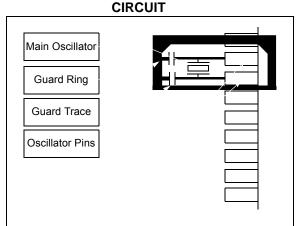

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

# FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

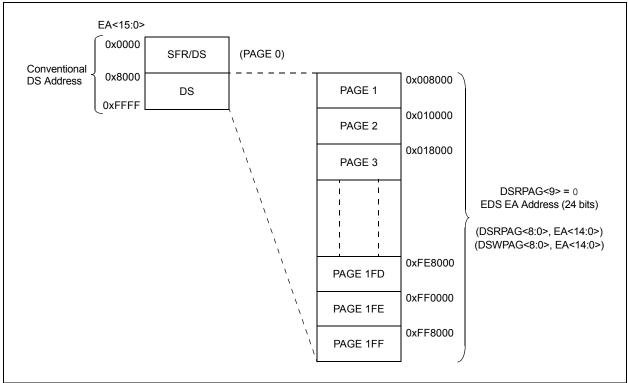

#### 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

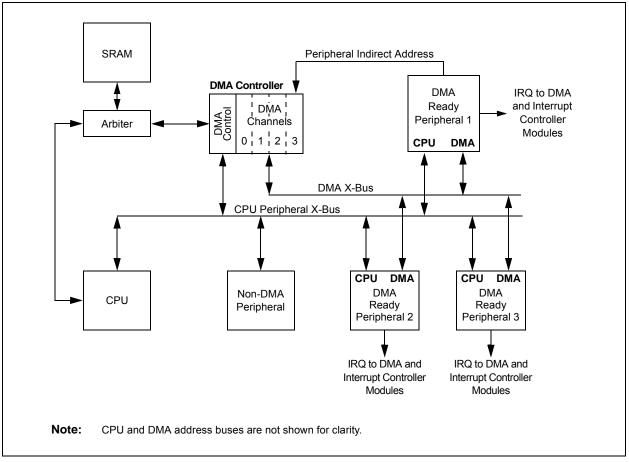

Figure 8-2 illustrates the DMA Controller block diagram.

### 8.1 DMAC Controller Registers

Each DMAC Channel x (where x = 0 to 3) contains the following registers:

- 16-Bit DMA Channel x Control Register (DMAxCON)

- 16-Bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-Bit DMA Channel x Start Address Register A High/Low (DMAxSTAH/L)

- 32-Bit DMA Channel x Start Address Register B High/Low (DMAxSTBH/L)

- 16-Bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-Bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRH/L) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The DMA Interrupt Flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding DMA Interrupt Enable bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding DMA Interrupt Priority bits (DMAxIP) are located in an IPCx register in the interrupt controller.

### **REGISTER 8-7:** DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|----------------------------------------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

|                                                                      |       |       | PAD   | <15:8>                                  |       |       |       |  |

| bit 15                                                               |       |       |       |                                         |       |       | bit 8 |  |

|                                                                      |       |       |       |                                         |       |       |       |  |

| R/W-0                                                                | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                                                      |       |       | PAI   | )<7:0>                                  |       |       |       |  |

| bit 7                                                                |       |       |       |                                         |       |       | bit 0 |  |

|                                                                      |       |       |       |                                         |       |       |       |  |

| Legend:                                                              |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |                                         |       |       |       |  |

| -n = Value at POR '1' = Bit is set                                   |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0            | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|------------------|-------|-------|

| —      | —   |       |       | CNT<  | 13:8> <b>(2)</b> |       |       |

| bit 15 |     |       |       |       |                  |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <b>(2)</b> |       |       |       |

| bit 7 |       |       |       |                 |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- **2:** The number of DMA transfers = CNT<13:0> + 1.

x = Bit is unknown

| U-0             | U-0 | U-0              | U-0   | U-0          | U-0              | U-0    | U-0   |

|-----------------|-----|------------------|-------|--------------|------------------|--------|-------|

| —               | —   | —                | —     | —            |                  | _      | —     |

| bit 15          |     |                  |       |              |                  |        | bit 8 |

|                 |     |                  |       |              |                  |        |       |

| R-0             | R-0 | R-0              | R-0   | R-0          | R-0              | R-0    | R-0   |

|                 |     |                  | DSADR | <23:16>      |                  |        |       |

| bit 7           |     |                  |       |              |                  |        | bit 0 |

|                 |     |                  |       |              |                  |        |       |

| Legend:         |     |                  |       |              |                  |        |       |

| R = Readable bi | it  | W = Writable bit |       | U = Unimpler | nented bit, read | as '0' |       |

'0' = Bit is cleared

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

bit 15-8 **Unimplemented:** Read as '0'

-n = Value at POR

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

'1' = Bit is set

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0                                                                  | R-0                                                                   | R-0 | R-0  | R-0      | R-0  | R-0 | R-0   |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------|-----|------|----------|------|-----|-------|--|--|

|                                                                      |                                                                       |     | DSAI | DR<15:8> |      |     |       |  |  |

| bit 15                                                               |                                                                       |     |      |          |      |     | bit 8 |  |  |

|                                                                      |                                                                       |     |      |          |      |     |       |  |  |

| R-0                                                                  | R-0                                                                   | R-0 | R-0  | R-0      | R-0  | R-0 | R-0   |  |  |

|                                                                      | DSADR<7:0>                                                            |     |      |          |      |     |       |  |  |

| bit 7                                                                |                                                                       |     |      |          |      |     | bit 0 |  |  |

|                                                                      |                                                                       |     |      |          |      |     |       |  |  |

| Legend:                                                              |                                                                       |     |      |          |      |     |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                       |     |      |          |      |     |       |  |  |

| -n = Value at POR                                                    | Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |      |          | iown |     |       |  |  |

|                                                                      |                                                                       |     |      |          |      |     |       |  |  |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

### 11.4 Slew Rate Selection

The slew rate selection feature allows the device to have control over the slew rate selection on the required I/O pin which supports this feature. For this purpose, for each I/O port, there are two registers: SR1x and SR0x, which configure the selection of the slew rate. The register outputs are directly connected to the associated I/O pins, which support the slew rate selection function. The SR1x register specifies the MSb and the SR0x register provides the LSb of the 2-bit field that selects the desired slew rate. For example, slew rate selections for PORTA are as follows:

#### EXAMPLE 11-2: SLEW RATE SELECTIONS FOR PORTA

SR1Ax, SR0Ax = 00 = Fastest Slew rate SR1Ax, SR0Ax = 01 = 4x slower Slew rate SR1Ax, SR0Ax = 10 = 8x slower Slew rate SR1Ax, SR0Ax = 11 = 16x slower Slew rate

## 11.5 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping after it has been established.

### 11.5.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.5.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and Interrupt-on-Change (IOC) inputs.

In comparison, some digital only peripheral modules are never included in the PPS feature, because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between the remappable and nonremappable peripherals is that the remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, the non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all the other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.5.3 CONTROLLING PERIPHERAL PIN SELECT

The PPS features are controlled through two sets of SFRs: one to map the peripheral inputs and the other to map the outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

### 11.5.4 INPUT MAPPING

The inputs of the PPS options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Table 11-1 and Register 11-1 through Register 11-17). Each register contains sets of 8-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 8-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selects supported by the device.

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EVXXXGM00X/10X device family offers two SPI modules on a single device, SPI1 and SPI2, that are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

**Note:** In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of this module, but results in a lower maximum speed. See **Section 30.0 "Electrical Characteristics"** for more information.

The SPIx serial interface consists of the following four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

**Note:** All of the 4 pins of the SPIx serial interface must be configured as digital in the ANSELx registers.

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

### REGISTER 21-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Baud rate measurement on the next character is enabled – requires reception of a Sync field (55h) before other data; cleared in hardware upon completion</li> <li>0 = Baud rate measurement is disabled or has completed</li> </ul> |

| bit 4   | URXINV: UARTx Receive Polarity Inversion bit                                                                                                                                                                                                     |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                                                         |

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                                                                                  |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul>                                                               |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                                                       |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                                                    |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                                                                                    |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                                                                                            |

| Note 1: | Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the                                                                                                                                                                |

- "dsPIC33/PIC24 Family Reference Manual" for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

- **3:** This feature is only available on 44-pin and 64-pin devices.

- **4:** This feature is only available on 64-pin devices.

| R/W-0         | R/W-0                                                                                    | R/W-0                                                                                | R/W-0            | R/W-0            | R/W-0                          | R/W-0              | R/W-0 |  |

|---------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------|------------------|--------------------------------|--------------------|-------|--|

| F7BP3         | F7BP2                                                                                    | F7BP1 F7BP0                                                                          |                  | F6BP3            | F6BP2                          | F6BP1              | F6BP0 |  |

| bit 15        |                                                                                          |                                                                                      |                  |                  |                                |                    | bit 8 |  |

|               |                                                                                          |                                                                                      |                  |                  |                                |                    |       |  |

| R/W-0         | R/W-0                                                                                    | R/W-0                                                                                | R/W-0            | R/W-0            | R/W-0                          | R/W-0              | R/W-0 |  |

| F5BP3         | F5BP2                                                                                    | F5BP1                                                                                | F5BP0            | F4BP3            | F4BP2                          | F4BP1              | F4BP0 |  |

| bit 7         |                                                                                          |                                                                                      |                  |                  |                                |                    | bit 0 |  |

|               |                                                                                          |                                                                                      |                  |                  |                                |                    |       |  |

| Legend:       |                                                                                          |                                                                                      |                  |                  |                                |                    |       |  |

| R = Readable  | e bit                                                                                    | W = Writable bit                                                                     |                  | U = Unimpler     | nented bit, read               | <b>as</b> '0'      |       |  |

| -n = Value at | POR                                                                                      | '1' = Bit is set                                                                     |                  | '0' = Bit is cle | ared                           | x = Bit is unknown |       |  |

|               |                                                                                          |                                                                                      |                  |                  |                                |                    |       |  |

| bit 15-12     | F7BP<3:0>:                                                                               | RX Buffer Masl                                                                       | k for Filter 7 b | its              |                                |                    |       |  |

|               | 1111 = Filter                                                                            | hits received in                                                                     | NRX FIFO bu      | ffer             |                                |                    |       |  |

|               | 1110 <b>= Filter</b>                                                                     | hits received in                                                                     | RX Buffer 14     | 1                |                                |                    |       |  |

|               | •                                                                                        |                                                                                      |                  |                  |                                |                    |       |  |

|               | •                                                                                        |                                                                                      |                  |                  |                                |                    |       |  |

|               | •<br>0001 - Filtor                                                                       | hito received in                                                                     |                  |                  |                                |                    |       |  |

|               | 0001 = Filter hits received in RX Buffer 1<br>0000 = Filter hits received in RX Buffer 0 |                                                                                      |                  |                  |                                |                    |       |  |

| bit 11-8      |                                                                                          |                                                                                      |                  | its (same value  | $a_{\rm r}$ as hits $15_{-12}$ |                    |       |  |

|               |                                                                                          | <b>F6BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 6 bits (same values as bits 15-12) |                  |                  |                                |                    |       |  |

| bit 7-4       | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits 15-12)                  |                                                                                      |                  |                  |                                |                    |       |  |

#### REGISTER 22-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

bit 3-0 **F4BP<3:0>:** RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

33EVXXXGM00X/10X FAMIL

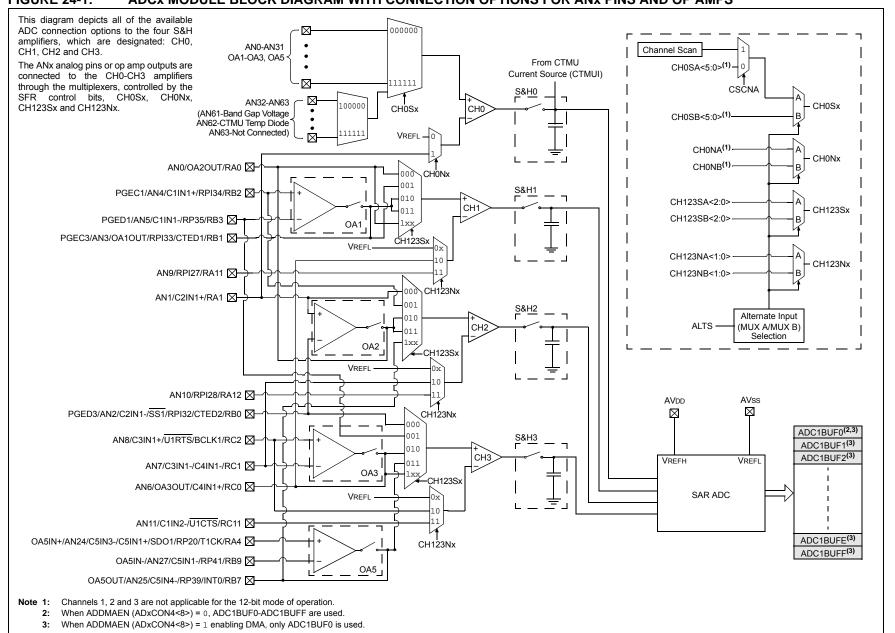

#### FIGURE 24-1: ADCX MODULE BLOCK DIAGRAM WITH CONNECTION OPTIONS FOR ANX PINS AND OP AMPS

#### REGISTER 24-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:                                                                                                                                                         |

|         | 111 = Reserved<br>110 = Reserved                                                                                                                                      |

|         | 101 = Reserved                                                                                                                                                        |

|         | 100 = Reserved                                                                                                                                                        |

|         | 011 = Reserved                                                                                                                                                        |

|         | 010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | 001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | 000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion                                                                                     |

|         | If SSRCG = 0:                                                                                                                                                         |

|         | 111 = Internal counter ends sampling and starts conversion (auto-convert)                                                                                             |

|         | 110 = CTMU ends sampling and starts conversion                                                                                                                        |

|         | 101 = Reserved                                                                                                                                                        |

|         | 100 = Timer5 compare ends sampling and starts conversion                                                                                                              |

|         | 011 = PWM primary Special Event Trigger ends sampling and starts conversion<br>010 = Timer3 compare ends sampling and starts conversion                               |

|         | 001 = Active transition on the INTO pin ends sampling and starts conversion                                                                                           |

|         | 000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)                                                                                |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                |

| 511 4   | See SSRC<2:0> for details.                                                                                                                                            |

| h # 0   |                                                                                                                                                                       |

| bit 3   | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                    |

|         | In 12-Bit Mode (AD12B = 1), SIMSAM is Unimplemented and is Read as '0':<br>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS<1:0> = 1x) or samples CH0 and CH1 |

|         | simultaneously (when CHPS<1:0> = 01)                                                                                                                                  |

|         | 0 = Samples multiple channels individually in sequence                                                                                                                |

| bit 2   | ASAM: ADCx Sample Auto-Start bit                                                                                                                                      |

|         | 1 = Sampling begins immediately after last conversion; SAMP bit is auto-set                                                                                           |

|         | 0 = Sampling begins when SAMP bit is set                                                                                                                              |

| bit 1   | SAMP: ADCx Sample Enable bit                                                                                                                                          |

|         | 1 = ADCx Sample-and-Hold amplifiers are sampling                                                                                                                      |

|         | 0 = ADCx Sample-and-Hold amplifiers are holding                                                                                                                       |

|         | If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If                                                                  |

|         | SSRC<2:0> = 000, software can write '0' to end sampling and start conversion. If SSRC<2:0> $\neq$ 000,                                                                |

|         | automatically cleared by hardware to end sampling and start conversion.                                                                                               |

| bit 0   | DONE: ADCx Conversion Status bit <sup>(1)</sup>                                                                                                                       |

|         | 1 = ADCx conversion cycle is completed.                                                                                                                               |

|         | 0 = ADCx conversion has not started or is in progress                                                                                                                 |

|         | Automatically set by hardware when conversion is complete. Software can write '0' to clear DONE bit                                                                   |

|         | status (software not allowed to write '1'). Clearing this bit does NOT affect any operation in progress.                                                              |

|         | Automatically cleared by hardware at the start of a new conversion.                                                                                                   |

**Note 1:** Do not clear the DONE bit in software if auto-sample is enabled (ASAM = 1).

# **REGISTER 24-7:** ADxCSSH: ADCx INPUT SCAN SELECT REGISTER HIGH<sup>(2)</sup> (CONTINUED)

- bit 1 CSS17: ADCx Input Scan Selection bit 1 = Selects ANx for input scan

- 0 = Skips ANx for input scan

- bit 0 CSS16: ADCx Input Scan Selection bit

- 1 = Selects ANx for input scan

- 0 = Skips ANx for input scan

- **Note 1:** If the op amp is selected (OPAEN bit (CMxCON<10>) = 1), the OAx input is used; otherwise, the ANx input is used.

- 2: All bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

# dsPIC33EVXXXGM00X/10X FAMILY

#### **FIGURE 30-2: EXTERNAL CLOCK TIMING** Q1 Q2 Q3 Q4 Q1 Q2 ı, Q3 Q4 OSC1 **OS20** OS30 **OS30** 0531 0531 **OS25** CLKO **OS41** OS40

| AC CHARACTERISTICS |               |                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |              |            |                               |  |  |

|--------------------|---------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|------------|-------------------------------|--|--|

| Param<br>No.       | Sym           | Characteristic                                                                     | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(1)</sup> | Max.         | Units      | Conditions                    |  |  |

| OS10               | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                                                                                                                    | _                   | 40           | MHz        | EC                            |  |  |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                                                                                                                                                                                                                                                             | _                   | 10<br>25     | MHz<br>MHz | XT<br>HS                      |  |  |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                                                                                                                                                                                                                                                  |                     | DC           | ns         | TA = +125°C                   |  |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                                                                                                                                                                                                                                                    |                     | DC           | ns         | TA = +125°C                   |  |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                                                                                                                                                                                                                                                          | —                   | 0.625 x Tosc | ns         | EC                            |  |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                                                                                                                                                                                                                                                     | —                   | 20           | ns         | EC                            |  |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      | —                                                                                                                                                                                                                                                                                     | 5.2                 | —            | ns         |                               |  |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      |                                                                                                                                                                                                                                                                                       | 5.2                 | —            | ns         |                               |  |  |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | —                                                                                                                                                                                                                                                                                     | 12                  | _            | mA/V       | HS, VDD = 5.0V,<br>TA = +25°C |  |  |

|                    |               |                                                                                    | —                                                                                                                                                                                                                                                                                     | 6                   | —            | mA/V       | XT, VDD = 5.0V,<br>TA = +25°C |  |  |

#### TABLE 30-17: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Instruction cycle period (TCY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Minimum" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Maximum" cycle time limit is "DC" (no clock) for all devices.

3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

4: This parameter is characterized but not tested in manufacturing.

# TABLE 30-22:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                                 |  |

|--------------------|-----------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                     | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                      |  |

| SY00               | Tpu       | Power-up Period                                                   | _                                                                                                                                                                                                                                                                                     | 400                 | 600  | μs    |                                                                                                                 |  |

| SY10               | Tost      | Oscillator Start-up<br>Time                                       | —                                                                                                                                                                                                                                                                                     | 1024 Tos<br>C       | —    | —     | Tosc = OSC1 period                                                                                              |  |

| SY11               | TPWRT     | Power-up Timer<br>Period                                          | —                                                                                                                                                                                                                                                                                     | 1                   | —    | ms    | Using LPRC parameters indicated in F21a/F21b (see Table 30-20)                                                  |  |

| SY12               | Тwdt      | Watchdog Timer<br>Time-out Period                                 | 0.8                                                                                                                                                                                                                                                                                   | _                   | 1.2  | ms    | WDTPRE = 0, WDTPS<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 30-20) at<br>+85°C |  |

|                    |           |                                                                   | 3.2                                                                                                                                                                                                                                                                                   | _                   | 4.8  | ms    | WDTPRE = 1, WDTPS<3:0> = 0000,<br>using LPRC tolerances indicated in<br>F21a/F21b (see Table 30-20) at<br>+85°C |  |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer<br>Reset | 0.68                                                                                                                                                                                                                                                                                  | 0.72                | 1.2  | μs    |                                                                                                                 |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                            | 2                                                                                                                                                                                                                                                                                     | —                   | -    | μs    |                                                                                                                 |  |

| SY30               | TBOR      | BOR Pulse Width<br>(low)                                          | 1                                                                                                                                                                                                                                                                                     | —                   | _    | ms    |                                                                                                                 |  |

| SY35               | TFSCM     | Fail-Safe Clock<br>Monitor Delay                                  | —                                                                                                                                                                                                                                                                                     | 500                 | 900  | μs    | -40°C to +85°C                                                                                                  |  |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active<br>mode Transition Time    | —                                                                                                                                                                                                                                                                                     | _                   | 30   | μs    |                                                                                                                 |  |

| SY37               | TOSCDFRC  | FRC Oscillator<br>Start-up Delay                                  | 46                                                                                                                                                                                                                                                                                    | 48                  | 54   | μs    |                                                                                                                 |  |

| SY38               | TOSCDLPRC | LPRC Oscillator<br>Start-up Delay                                 | —                                                                                                                                                                                                                                                                                     | —                   | 70   | μs    |                                                                                                                 |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

# dsPIC33EVXXXGM00X/10X FAMILY

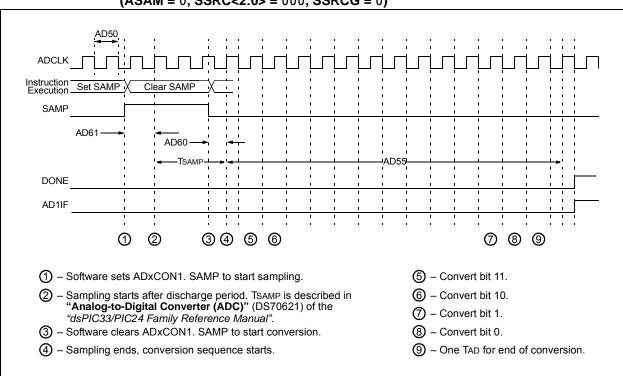

#### FIGURE 30-34: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

# dsPIC33EVXXXGM00X/10X FAMILY

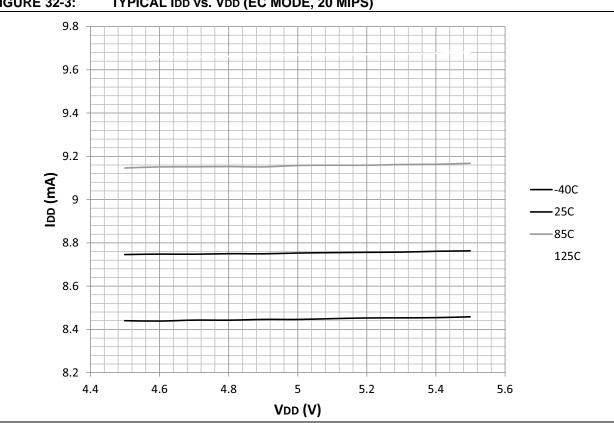

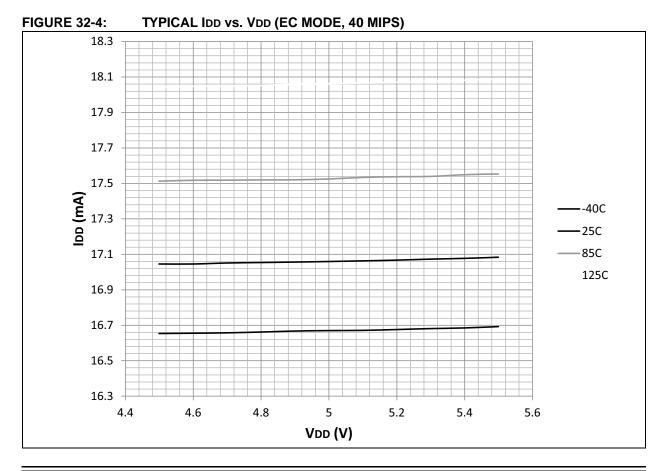

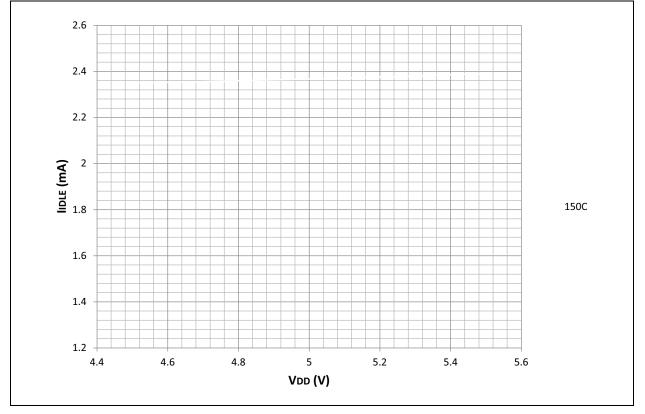

**FIGURE 32-3:** TYPICAL IDD vs. VDD (EC MODE, 20 MIPS)

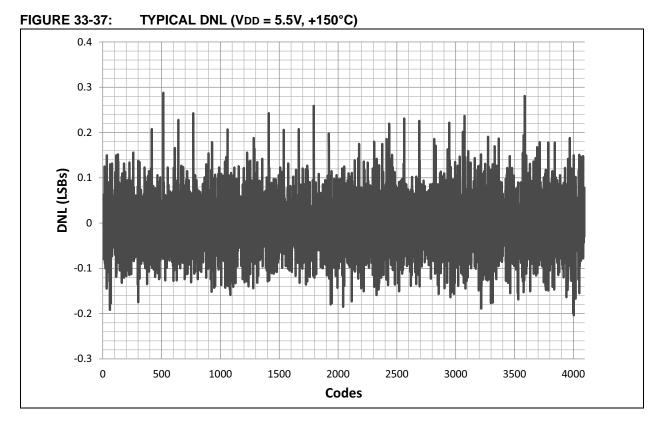

## 33.17 ADC DNL

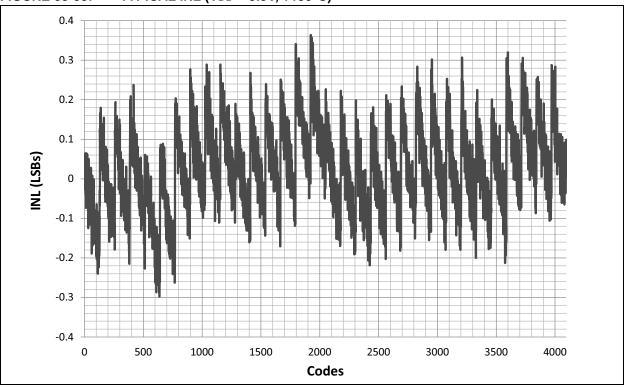

# 33.18 ADC INL

FIGURE 33-38: TYPICAL INL (VDD = 5.5V, +150°C)

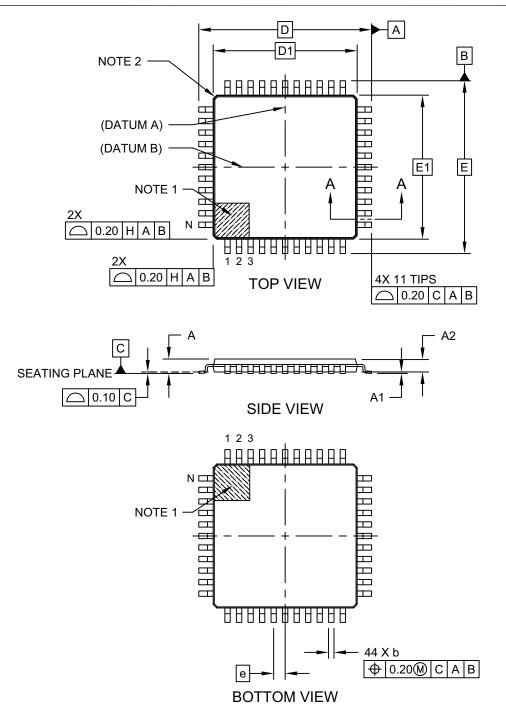

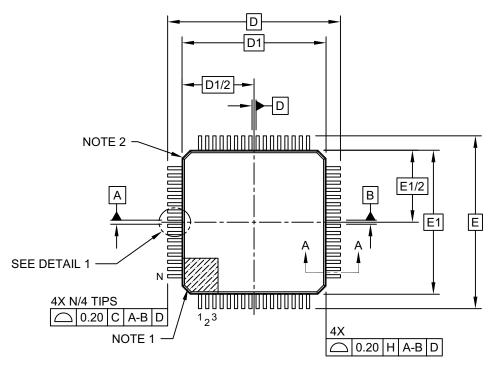

# 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2

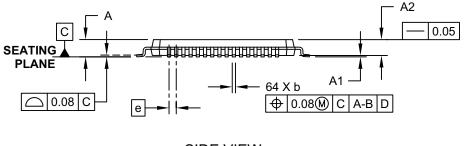

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2