Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm002-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

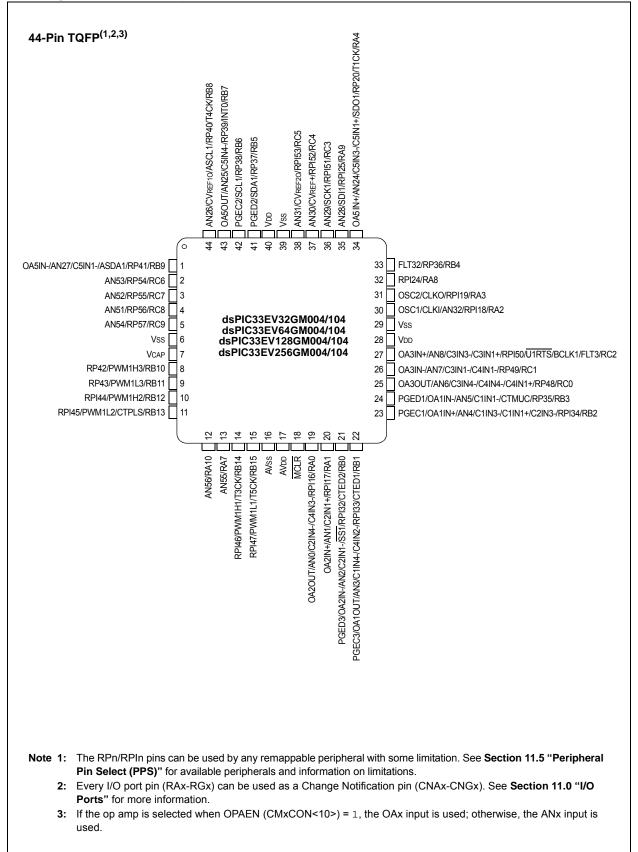

## **Pin Diagrams (Continued)**

## 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

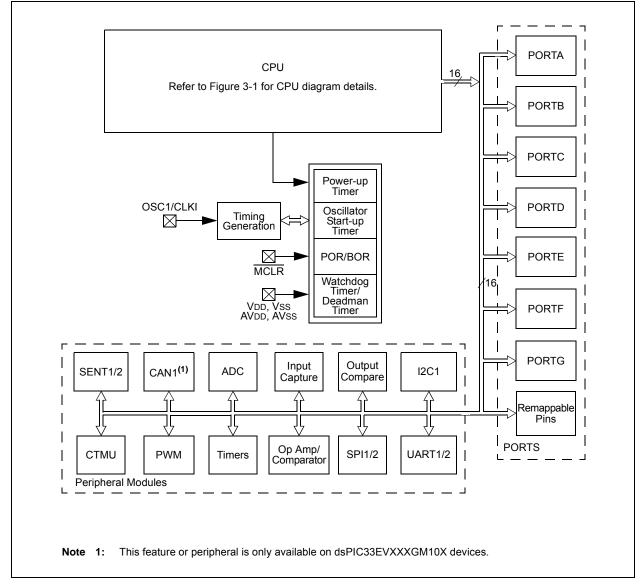

This document contains device-specific information for the dsPIC33EVXXXGM00X/10X family Digital Signal Controller (DSC) devices.

dsPIC33EVXXXGM00X/10X family devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EVXXXGM00X/10X FAMILY BLOCK DIAGRAM

## 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EVXXXGM00X/10X family of 16-bit microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors")

VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins"**)

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Note: The AVDD and AVSS pins must be connected, regardless of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10V-20V is recommended. This capacitor should be a Low Equivalent Series Resistance (low-ESR), and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the Printed Circuit Board (PCB): The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing the PCB track inductance.

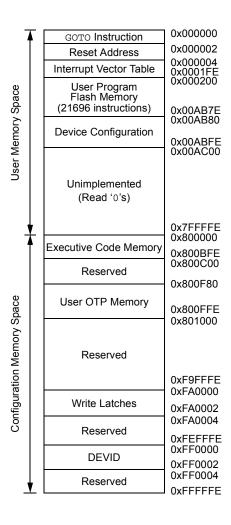

**Note 1:** Memory areas are not shown to scale.

## 4.3.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating the SSP (for example, creating stack frames).

| Note: | To protect against misaligned stack     |

|-------|-----------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the |

|       | hardware.                               |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EVXXXGM00X/10X family devices and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within the Data Space.

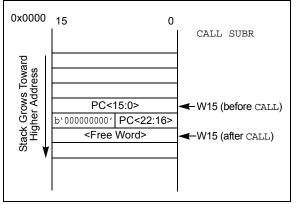

The SSP always points to the first available free word and fills the software stack, working from lower toward higher addresses. Figure 4-14 illustrates how it predecrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-14. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register (SR). This allows the contents of SRL to be preserved automatically during interrupt processing.

- Note 1: To maintain system SSP (W15) coherency, W15 is never subject to (EDS) paging, and is therefore, restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a 'C' development environment.

#### FIGURE 4-14:

#### CALL STACK FRAME

## 4.4 Instruction Addressing Modes

The addressing modes shown in Table 4-45 form the basis of the addressing modes optimized to support the specific features of the individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

## 4.4.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a Working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.4.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where, Operand 1 is always a Working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

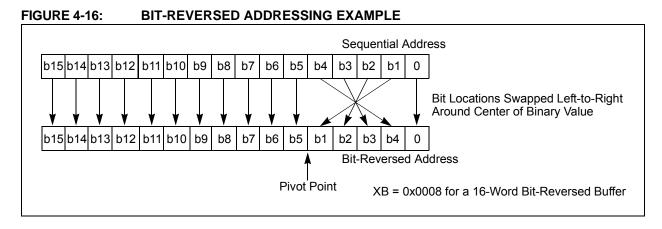

## TABLE 4-46: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    | Normal Address |    |    |         |    |    | Bit-Rev | ersed Ac | Idress  |

|----|----------------|----|----|---------|----|----|---------|----------|---------|

| A3 | A2             | A1 | A0 | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0              | 0  | 0  | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0              | 0  | 1  | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0              | 1  | 0  | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0              | 1  | 1  | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1              | 0  | 0  | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1              | 0  | 1  | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1              | 1  | 0  | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1              | 1  | 1  | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0              | 0  | 0  | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0              | 0  | 1  | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0              | 1  | 0  | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0              | 1  | 1  | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1              | 0  | 0  | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1              | 0  | 1  | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1              | 1  | 0  | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1              | 1  | 1  | 15      | 1  | 1  | 1       | 1        | 15      |

| U-0                          | U-0                                     | U-0              | R/W-0       | R/W-0             | U-0              | U-0             | R/W-0 |

|------------------------------|-----------------------------------------|------------------|-------------|-------------------|------------------|-----------------|-------|

|                              | —                                       |                  | SENT2MD     | SENT1MD           | _                | _               | DMTMD |

| bit 15                       | ÷                                       |                  | •           | •                 |                  |                 | bit 8 |

|                              |                                         |                  |             |                   |                  |                 |       |

| U-0                          | U-0                                     | U-0              | U-0         | U-0               | U-0              | U-0             | U-0   |

| _                            | —                                       |                  | —           | —                 | —                | —               | —     |

| bit 7                        |                                         |                  |             |                   |                  |                 | bit 0 |

|                              |                                         |                  |             |                   |                  |                 |       |

| Legend:                      |                                         |                  |             |                   |                  |                 |       |

| R = Readabl                  | le bit                                  | W = Writable     | bit         | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value at                | t POR                                   | '1' = Bit is set |             | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|                              |                                         |                  |             |                   |                  |                 |       |

| bit 15-13                    | Unimplemen                              | ted: Read as '   | כי          |                   |                  |                 |       |

| bit 12                       | SENT2MD: S                              | ENT2 Module      | Disable bit |                   |                  |                 |       |

|                              |                                         | odule is disable |             |                   |                  |                 |       |

|                              |                                         | odule is enable  |             |                   |                  |                 |       |

| bit 11                       |                                         | ENT1 Module      |             |                   |                  |                 |       |

| 1 = SENT1 module is disabled |                                         |                  |             |                   |                  |                 |       |

|                              | 0 = SENT1 module is enabled             |                  |             |                   |                  |                 |       |

| bit 10-9                     | Unimplemented: Read as '0'              |                  |             |                   |                  |                 |       |

| bit 8                        | <b>DMTMD:</b> Deadman Timer Disable bit |                  |             |                   |                  |                 |       |

|                              |                                         | Timer is disab   |             |                   |                  |                 |       |

|                              |                                         | Timer is enabl   |             |                   |                  |                 |       |

| bit 7-0                      | Unimplemen                              | ted: Read as '   | כ'          |                   |                  |                 |       |

## REGISTER 10-7: PMD8: PERIPHERAL MODULE DISABLE CONTROL REGISTER 8

| U-0                                      | U-0              | U-0              | U-0                      | U-0          | U-0              | U-0              | U-0   |

|------------------------------------------|------------------|------------------|--------------------------|--------------|------------------|------------------|-------|

| —                                        | —                | —                | —                        | —            | —                | —                | —     |

| bit 15                                   |                  |                  |                          |              |                  |                  | bit 8 |

|                                          |                  |                  |                          |              |                  |                  |       |

| R/W-0                                    | R/W-0            | R/W-0            | R/W-0                    | R/W-0        | R/W-0            | R/W-0            | R/W-0 |

|                                          |                  |                  | STEP                     | 2<7:0>       |                  |                  |       |

| bit 7                                    |                  |                  |                          |              |                  |                  | bit 0 |

|                                          |                  |                  |                          |              |                  |                  |       |

| Legend:                                  |                  |                  |                          |              |                  |                  |       |

| R = Readable b                           | bit              | W = Writable     | bit                      | U = Unimplei | mented bit, read | <b>as</b> '0'    |       |

| -n = Value at POR '1' = Bit is set       |                  |                  | '0' = Bit is cleared x = |              | x = Bit is unkr  | = Bit is unknown |       |

|                                          |                  |                  |                          |              |                  |                  |       |

| bit 15-8 Unimplemented: Read as '0'      |                  |                  |                          |              |                  |                  |       |

| bit 7-0 STEP2<7:0>: DMT Clear Timer bits |                  |                  |                          |              |                  |                  |       |

| -n = Value at P<br>bit 15-8              | OR<br>Unimplemen | '1' = Bit is set | 0'                       |              |                  |                  | nown  |

#### REGISTER 14-3: DMTCLR: DEADMAN TIMER CLEAR REGISTER

00001000 = Clears STEP1<7:0>, STEP2<7:0> and the Deadman Timer if preceded by the correct loading of the STEP1<7:0> bits in the correct sequence. The write to these bits may be verified by reading the DMTCNTL/H register and observing the counter being reset.

All Other

Write Patterns = Sets the BAD2 bit; the value of STEP1<7:0> will remain unchanged and the new value being written to STEP2<7:0> will be captured. These bits are cleared when a DMT Reset event occurs.

## 22.3 CAN Control Registers

## REGISTER 22-1: CxCTRL1: CANx CONTROL REGISTER 1

| U-0     | U-0     | R/W-0   | R/W-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  |

|---------|---------|---------|-------|--------|--------|--------|--------|

| —       | —       | CSIDL   | ABAT  | CANCKS | REQOP2 | REQOP1 | REQOP0 |

| bit 15  |         |         |       |        |        |        | bit 8  |

|         |         |         |       |        |        |        |        |

| R-1     | R-0     | R-0     | U-0   | R/W-0  | U-0    | U-0    | R/W-0  |

| OPMODE2 | OPMODE1 | OPMODE0 | _     | CANCAP | —      | _      | WIN    |

| bit 7   |         |         |       | •      |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>d as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | CSIDL: CANx Stop in Idle Mode bit                                                                                                                     |

| bit 10    | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>           |

| bit 12    | ABAT: Abort All Pending Transmissions bit                                                                                                             |

|           | <ul> <li>1 = Signals all transmit buffers to abort transmission</li> <li>0 = Module will clear this bit when all transmissions are aborted</li> </ul> |

| bit 11    | CANCKS: CANx Module Clock (FCAN) Source Select bit                                                                                                    |

|           | 1 = FCAN is equal to 2 * FP<br>0 = FCAN is equal to FP                                                                                                |

| bit 10-8  | REQOP<2:0>: Request Operation Mode bits                                                                                                               |

|           | 111 = Sets Listen All Messages mode                                                                                                                   |

|           | 110 = Reserved                                                                                                                                        |

|           | 101 = Reserved<br>100 = Sets Configuration mode                                                                                                       |

|           | 011 = Sets Listen Only mode                                                                                                                           |

|           | 010 = Sets Loopback mode                                                                                                                              |

|           | 001 = Sets Disable mode<br>000 = Sets Normal Operation mode                                                                                           |

| bit 7-5   | OPMODE<2:0>: Operation Mode bits                                                                                                                      |

|           | 111 = Module is in Listen All Messages mode                                                                                                           |

|           | 110 = Reserved                                                                                                                                        |

|           | 101 = Reserved                                                                                                                                        |

|           | 100 = Module is in Configuration mode<br>011 = Module is in Listen Only mode                                                                          |

|           | 010 = Module is in Loopback mode                                                                                                                      |

|           | 001 = Module is in Disable mode                                                                                                                       |

| bit 4     | 000 = Module is in Normal Operation mode                                                                                                              |

|           | Unimplemented: Read as '0'                                                                                                                            |

| bit 3     | CANCAP: CANx Message Receive Timer Capture Event Enable bit<br>1 = Enables input capture based on CAN message receive                                 |

|           | 0 = Disables CAN capture                                                                                                                              |

| bit 2-1   | Unimplemented: Read as '0'                                                                                                                            |

| bit 0     | WIN: SFR Map Window Select bit                                                                                                                        |

|           | 1 = Uses filter window                                                                                                                                |

|           | 0 = Uses buffer window                                                                                                                                |

### REGISTER 22-8: CxEC: CANx TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0             | R-0 | R-0              | R-0  | R-0                  | R-0          | R-0             | R-0   |

|-----------------|-----|------------------|------|----------------------|--------------|-----------------|-------|

|                 |     |                  | TERR | CNT<7:0>             |              |                 |       |

| bit 15          |     |                  |      |                      |              |                 | bit 8 |

|                 |     |                  |      |                      |              |                 |       |

| R-0             | R-0 | R-0              | R-0  | R-0                  | R-0          | R-0             | R-0   |

|                 |     |                  | RERR | CNT<7:0>             |              |                 |       |

| bit 7           |     |                  |      |                      |              |                 | bit 0 |

|                 |     |                  |      |                      |              |                 |       |

| Legend:         |     |                  |      |                      |              |                 |       |

| R = Readable I  | bit | W = Writable bi  | it   | U = Unimplemen       | ted bit, rea | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cleared | d            | x = Bit is unkr | nown  |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

### REGISTER 22-9: CxCFG1: CANx BAUD RATE CONFIGURATION REGISTER 1

| U-0                 | U-0                                                                                                                                                       | U-0                                                                                                                   | U-0                                                   | U-0               | U-0              | U-0             | U-0    |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------------------|-----------------|--------|

| 0-0                 | 0-0                                                                                                                                                       | 0-0                                                                                                                   | 0-0                                                   |                   | 0-0              | 0-0             | 0-0    |

|                     |                                                                                                                                                           |                                                                                                                       | _                                                     | _                 |                  |                 |        |

| bit 15              |                                                                                                                                                           |                                                                                                                       |                                                       |                   |                  |                 | bit    |

|                     | 5444.6                                                                                                                                                    | 5.4.4.6                                                                                                               |                                                       |                   | 54446            |                 | 5444.6 |

| R/W-0               | R/W-0                                                                                                                                                     | R/W-0                                                                                                                 | R/W-0                                                 | R/W-0             | R/W-0            | R/W-0           | R/W-0  |

| SJW1                | SJW0                                                                                                                                                      | BRP5                                                                                                                  | BRP4                                                  | BRP3              | BRP2             | BRP1            | BRP0   |

| bit 7               |                                                                                                                                                           |                                                                                                                       |                                                       |                   |                  |                 | bit    |

|                     |                                                                                                                                                           |                                                                                                                       |                                                       |                   |                  |                 |        |

| Legend:             |                                                                                                                                                           |                                                                                                                       |                                                       |                   |                  |                 |        |

| R = Readable        | e bit                                                                                                                                                     | W = Writable                                                                                                          | bit                                                   | U = Unimplen      | nented bit, read | <b>as</b> '0'   |        |

| -n = Value at I     | POR                                                                                                                                                       | '1' = Bit is set                                                                                                      |                                                       | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|                     | ••••                                                                                                                                                      | 1 Dit 10 001                                                                                                          | •                                                     |                   |                  |                 |        |

|                     |                                                                                                                                                           |                                                                                                                       | ·                                                     |                   |                  |                 |        |

| bit 15-8            |                                                                                                                                                           | ted: Read as '                                                                                                        |                                                       |                   |                  |                 |        |

| bit 15-8<br>bit 7-6 | Unimplemen                                                                                                                                                |                                                                                                                       | 0'                                                    | bits              |                  |                 | -      |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i                                                                                                                | <b>ted:</b> Read as '<br>ynchronization<br>s 4 x Tq                                                                   | 0'                                                    | oits              |                  |                 | -      |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i                                                                                               | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ                                                              | 0'                                                    | pits              |                  |                 |        |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i                                                                              | ted: Read as '<br>ynchronization<br>s 4 x To<br>s 3 x To<br>s 2 x To                                                  | 0'                                                    | bits              |                  |                 | -      |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i                                                             | <b>ted:</b> Read as <sup>4</sup><br>synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 2 x TQ<br>s 1 x TQ       | 0'<br>I Jump Width I                                  | pits              |                  |                 | -      |

|                     | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                                              | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits         | pits              |                  |                 | -      |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                                              | <b>ted:</b> Read as <sup>4</sup><br>synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 2 x TQ<br>s 1 x TQ       | <sup>0'</sup><br>I Jump Width I<br>caler bits         | bits              |                  |                 | -      |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                                              | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits         | pits              |                  |                 | -      |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B                                              | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits         | pits              |                  |                 | -      |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B<br>11 1111 = T<br>•                          | ted: Read as '<br>synchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres<br>Q = 2 x 64 x 1/ | <sup>0'</sup><br>I Jump Width I<br>caler bits<br>FCAN | bits              |                  |                 | -      |

| bit 7-6             | Unimplemen<br>SJW<1:0>: S<br>11 = Length i<br>10 = Length i<br>01 = Length i<br>00 = Length i<br>BRP<5:0>: B<br>11 1111 = T<br>•<br>•<br>•<br>00 0010 = T | ted: Read as '<br>ynchronization<br>s 4 x TQ<br>s 3 x TQ<br>s 2 x TQ<br>s 1 x TQ<br>aud Rate Pres                     | <sup>0'</sup><br>I Jump Width I<br>caler bits<br>FCAN | bits              |                  |                 |        |

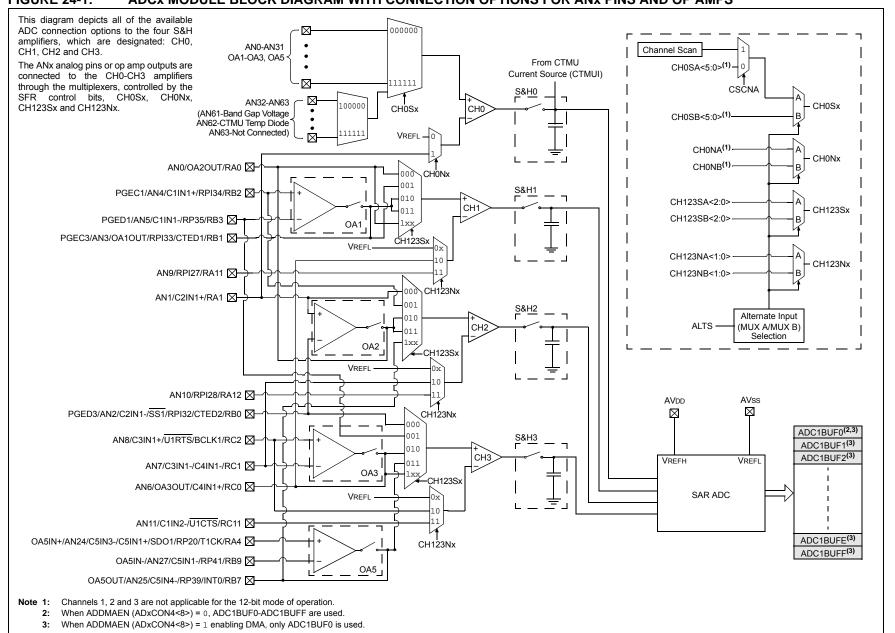

#### FIGURE 24-1: ADCX MODULE BLOCK DIAGRAM WITH CONNECTION OPTIONS FOR ANX PINS AND OP AMPS

## 27.6 In-Circuit Serial Programming

The dsPIC33EVXXXGM00X/10X family devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to "dsPIC33EVXXXGM00X/10X Families Flash Programming Specification" (DS70005137) for details about In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

Any of the following three pairs of programming clock/ data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

## 27.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>TM</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB X IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the following three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

## 27.8 Code Protection and CodeGuard™ Security

The dsPIC33EVXXXGM00X/10X family devices offer Intermediate CodeGuard Security that supports General Segment (GS) security, Boot Segment (BS) security and Configuration Segment (CS) security. This feature helps protect individual Intellectual Properties.

| Note: | Refer to "CodeGuard™ Intermediate           |

|-------|---------------------------------------------|

|       | Security" (DS70005182) in the "dsPIC33/     |

|       | PIC24 Family Reference Manual" for          |

|       | further information on usage, configuration |

|       | and operation of CodeGuard Security.        |

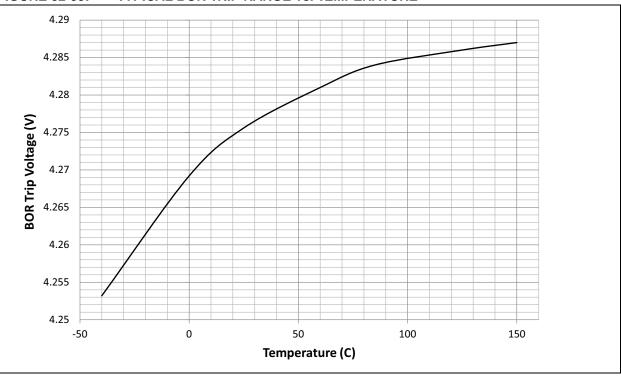

## 32.12 VBOR

FIGURE 32-35: TYPICAL BOR TRIP RANGE vs. TEMPERATURE

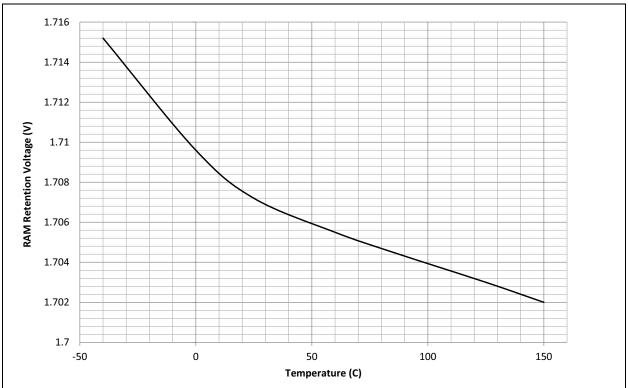

## 32.13 RAM Retention

FIGURE 32-36: TYPICAL RAM RETENTION VOLTAGE vs. TEMPERATURE

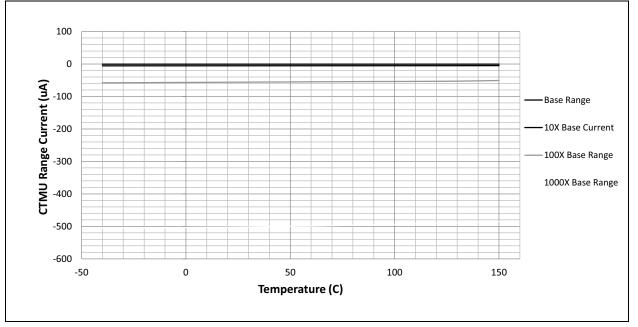

## FIGURE 32-39: TYPICAL CTMU CURRENT (IRNG) vs. TEMPERATURE

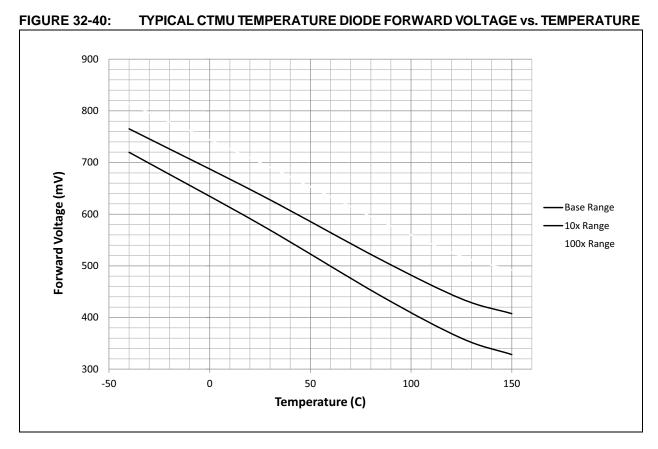

## 32.16 CTMU Temperature Forward Diode

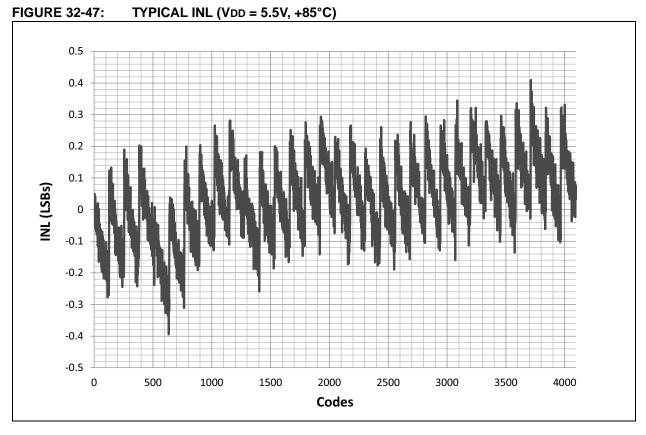

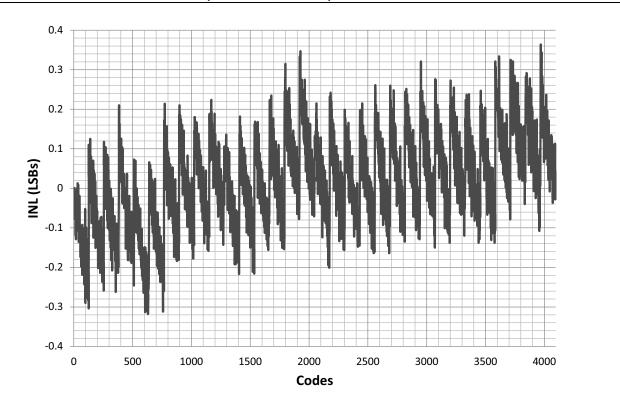

FIGURE 32-48: TYPICAL INL (VDD = 5.5V, +125°C)

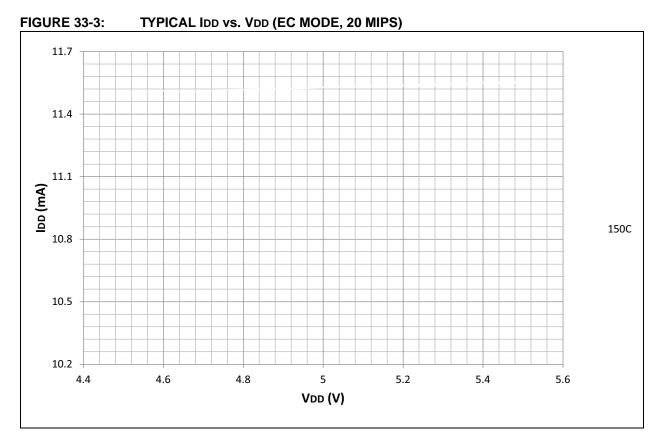

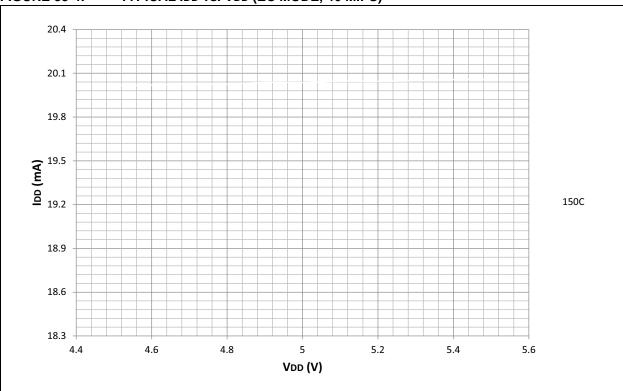

FIGURE 33-4: TYPICAL IDD vs. VDD (EC MODE, 40 MIPS)

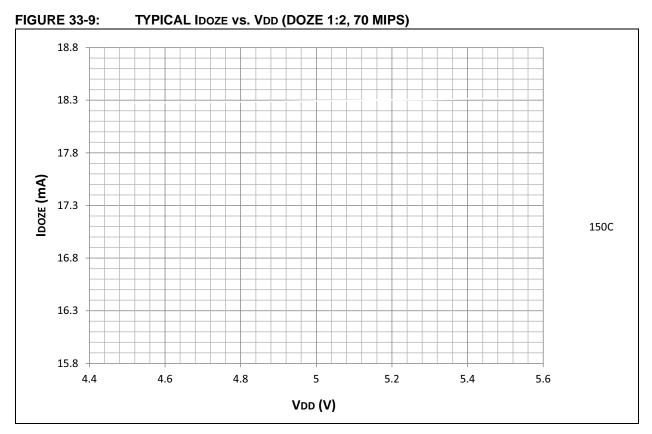

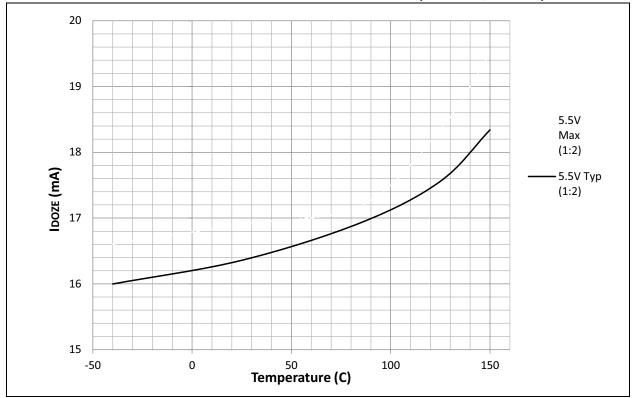

FIGURE 33-10: TYPICAL/MAXIMUM IDOZE vs. TEMPERATURE (DOZE 1:2, 70 MIPS)

© 2013-2016 Microchip Technology Inc.

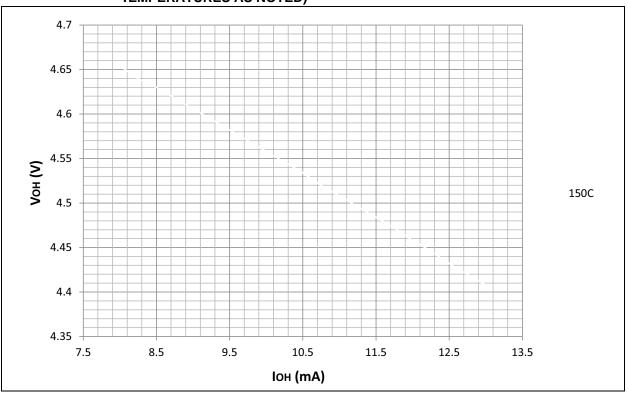

FIGURE 33-27: TYPICAL VOH 4x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

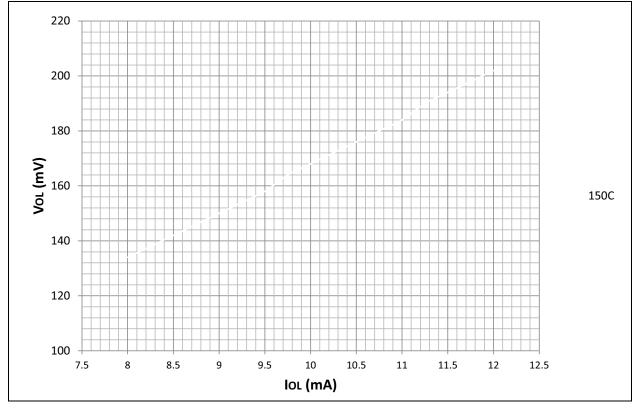

FIGURE 33-28: TYPICAL Vol 8x DRIVER PINS vs. Iol (GENERAL PURPOSE I/Os, TEMPERATURES AS NOTED)

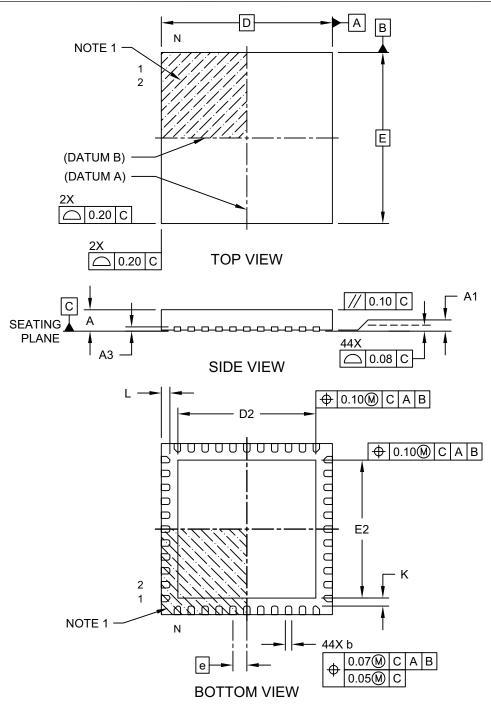

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging