#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

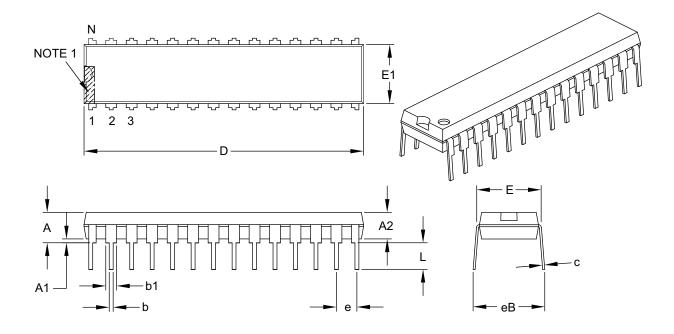

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm002-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| -                          | GOTO Instruction                                     | 0x000000                         |  |

|----------------------------|------------------------------------------------------|----------------------------------|--|

|                            | Reset Address                                        | 0x000002                         |  |

|                            | Interrupt Vector Table                               | 0x000004<br>0x0001FE<br>0x000200 |  |

| Space                      | User Program<br>Flash Memory<br>(44736 instructions) | 0x000200<br>0x01577E<br>0x015780 |  |

| User Memory Space          | Device Configuration                                 | 0x015780<br>0x0157FE<br>0x015800 |  |

| C                          | Unimplemented<br>(Read '0's)                         |                                  |  |

|                            | Executive Code Memory                                | 0x7FFFE<br>0x800000<br>0x800BFE  |  |

|                            | Reserved                                             | 0x800C00<br>0x800F80             |  |

| ø                          | User OTP Memory                                      | 0x800FFE                         |  |

| ory Spac                   | Reserved                                             | 0x801000                         |  |

| on Mem                     | Write Latches                                        | 0xF9FFFE<br>0xFA0000<br>0xFA0002 |  |

| Configuration Memory Space | Reserved                                             | 0xFA0004                         |  |

|                            | DEVID                                                | 0xFEFFFE<br>0xFF0000<br>0xFF0002 |  |

| ,                          | Reserved                                             | 0xFF0004<br>0xFFFFFE             |  |

## 4.2.5 X AND Y DATA SPACES

The dsPIC33EVXXXGM00X/10X family core has two Data Spaces: X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified, linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X DS is used by all instructions and supports all addressing modes. The X DS has separate read and write data buses. The X read data bus is the read data path for all instructions that view the DS as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class). The Y DS is used in concert with the X DS by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to the X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

## REGISTER 14-5: DMTCNTL: DEADMAN TIMER COUNT REGISTER LOW

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                          | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|------------------------------------------------|----------------------------------------|-------|-------|-------|

|                 |       |                  | COUNT                                          | ER<15:8>                               |       |       |       |

| bit 15          |       |                  |                                                |                                        |       |       | bit 8 |

|                 |       |                  |                                                |                                        |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                          | R/W-0                                  | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | COUN                                           | ΓER<7:0>                               |       |       |       |

| bit 7           |       |                  |                                                |                                        |       |       | bit 0 |

|                 |       |                  |                                                |                                        |       |       |       |

| Legend:         |       |                  |                                                |                                        |       |       |       |

| R = Readable    | bit   | W = Writable b   | ritable bit U = Unimplemented bit, read as '0' |                                        |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |                                                | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |

bit 15-0 COUNTER<15:0>: Read Current Contents of Lower DMT Counter bits

### REGISTER 14-6: DMTCNTH: DEADMAN TIMER COUNT REGISTER HIGH

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|

|                 |       |                  | COUNT | ER<31:24>                               |       |       |       |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |

|                 |       |                  |       |                                         |       |       |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |

|                 |       |                  | COUNT | ER<23:16>                               |       |       |       |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |

|                 |       |                  |       |                                         |       |       |       |

| Legend:         |       |                  |       |                                         |       |       |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplemented bit, read as '0'      |       |       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-0 COUNTER<31:16>: Read Current Contents of Higher DMT Counter bits

# dsPIC33EVXXXGM00X/10X FAMILY

## REGISTER 17-12: TRGCONX: PWMx TRIGGER CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 | —   | —   | —   | —     |

| bit 15  |         |         |         |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                   |

|-------|-----|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| —     | —   | TRGSTRT5 <sup>(1)</sup> | TRGSTRT4 <sup>(1)</sup> | TRGSTRT3 <sup>(1)</sup> | TRGSTRT2 <sup>(1)</sup> | TRGSTRT1 <sup>(1)</sup> | TRGSTRT0 <sup>(1)</sup> |

| bit 7 |     |                         |                         |                         |                         |                         | bit 0                   |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

### bit 15-12 TRGDIV<3:0>: Trigger Output Divider bits

- 1111 = Triggers output for every 16th trigger event

- 1110 = Triggers output for every 15th trigger event

- 1101 = Triggers output for every 14th trigger event

- 1100 = Triggers output for every 13th trigger event

- 1011 = Triggers output for every 12th trigger event

- 1010 = Triggers output for every 11th trigger event

- 1001 = Triggers output for every 10th trigger event

- 1000 = Triggers output for every 9th trigger event

- 0111 = Triggers output for every 8th trigger event

- 0110 = Triggers output for every 7th trigger event

- 0101 = Triggers output for every 6th trigger event

- 0100 = Triggers output for every 5th trigger event 0011 = Triggers output for every 4th trigger event

- 0010 = Triggers output for every 3rd trigger event

- 0001 = Triggers output for every 2nd trigger event

- 0000 = Triggers output for every trigger event

- bit 11-6 **Unimplemented:** Read as '0'

### bit 5-0 TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits<sup>(1)</sup>

111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled

- •

- •

000010 = Waits 2 PWM cycles before generating the first trigger event after the module is enabled 000001 = Waits 1 PWM cycle before generating the first trigger event after the module is enabled 000000 = Waits 0 PWM cycles before generating the first trigger event after the module is enabled

### **Note 1:** The secondary PWM generator cannot generate PWMx trigger interrupts.

# REGISTER 17-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

| bit 7-3 | FLTSRC<4:0>: Fault Control Signal Source Select for PWM Generator x bits<br>11111 = Fault 32 (default)<br>11110 = Reserved                                                                                                                                                                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                                                                                                                           |

|         | •                                                                                                                                                                                                                                                                                                                           |

|         | •                                                                                                                                                                                                                                                                                                                           |

|         | 01100 = Op Amp/Comparator 5<br>01011 = Comparator 4<br>01010 = Op Amp/Comparator 3<br>01001 = Op Amp/Comparator 2<br>01000 = Op Amp/Comparator 1<br>00111 = Fault 8<br>00110 = Fault 7<br>00101 = Fault 7<br>00101 = Fault 6<br>00100 = Fault 5<br>00011 = Fault 4<br>00010 = Fault 3<br>00001 = Fault 2<br>00000 = Fault 1 |

| bit 2   | <b>FLTPOL:</b> Fault Polarity for PWM Generator x bit <sup>(2)</sup>                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = The selected Fault source is active-low</li> <li>0 = The selected Fault source is active-high</li> </ul>                                                                                                                                                                                                       |

| bit 1-0 | FLTMOD<1:0>: Fault Mode for PWM Generator x bits                                                                                                                                                                                                                                                                            |

|         | <ul> <li>11 = Fault input is disabled</li> <li>10 = Reserved</li> <li>01 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDAT&lt;1:0&gt; values (cycle)</li> <li>00 = The selected Fault source forces the PWMxH, PWMxL pins to FLTDAT&lt;1:0&gt; values (latched condition)</li> </ul>                       |

- **Note 1:** If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the FCLCONx register can only be written after the unlock sequence has been executed.

- 2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

| R/W-0           | R/W-0                                                                                                                                                                                       | R/W-0                                      | R/W-0                         | R/W-0                                           | R/W-0              | U-0             | U-0            |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------|-------------------------------------------------|--------------------|-----------------|----------------|--|--|--|--|

| PHR             | PHF                                                                                                                                                                                         | PLR                                        | PLF                           | FLTLEBEN                                        | CLLEBEN            |                 | _              |  |  |  |  |

| bit 15          |                                                                                                                                                                                             | L                                          |                               | •                                               |                    |                 | bit 8          |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| U-0             | U-0                                                                                                                                                                                         | R/W-0                                      | R/W-0                         | R/W-0                                           | R/W-0              | R/W-0           | R/W-0          |  |  |  |  |

| —               |                                                                                                                                                                                             | BCH <sup>(1)</sup>                         | BCL <sup>(1)</sup>            | BPHH                                            | BPHL               | BPLH            | BPLL           |  |  |  |  |

| bit 7           |                                                                                                                                                                                             |                                            |                               |                                                 |                    |                 | bit (          |  |  |  |  |

| Legend:         |                                                                                                                                                                                             |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| R = Readable b  | nit                                                                                                                                                                                         | W = Writable                               | hit                           | II = I Inimpler                                 | mented bit, read   | as '0'          |                |  |  |  |  |

| -n = Value at P |                                                                                                                                                                                             | '1' = Bit is set                           |                               | '0' = Bit is cle                                |                    | x = Bit is unk  | nown           |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               |                                                 |                    | X Bitle dill    |                |  |  |  |  |

| bit 15          | PHR: PWMxH                                                                                                                                                                                  | Rising Edge                                | Trigger Enabl                 | e bit                                           |                    |                 |                |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               |                                                 | Blanking count     | ter             |                |  |  |  |  |

|                 | 0 = Leading-E                                                                                                                                                                               | Edge Blanking                              | gnores the ri                 | sing edge of PV                                 | VMxH               |                 |                |  |  |  |  |

| bit 14          |                                                                                                                                                                                             | I Falling Edge                             |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | 0                                                                                                                                                                                           | 0                                          | 00                            | e Leading-Edge<br>alling edge of P <sup>1</sup> | e Blanking coun    | ter             |                |  |  |  |  |

| bit 13          | -                                                                                                                                                                                           | Rising Edge T                              | -                             |                                                 |                    |                 |                |  |  |  |  |

| DIL 15          |                                                                                                                                                                                             | • •                                        |                               |                                                 | Blanking count     | er              |                |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               | sing edge of PV                                 |                    |                 |                |  |  |  |  |

| bit 12          | PLF: PWMxL                                                                                                                                                                                  | PLF: PWMxL Falling Edge Trigger Enable bit |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | 1 = Falling edge of PWMxL will trigger the Leading-Edge Blanking counter                                                                                                                    |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | 0 = Leading-Edge Blanking ignores the falling edge of PWMxL                                                                                                                                 |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| bit 11          | <b>FLTLEBEN:</b> Fault Input Leading-Edge Blanking Enable bit<br>1 = Leading-Edge Blanking is applied to the selected Fault input                                                           |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| bit 10          | ELeading-Edge Blanking is not applied to the selected Fault input<br>CLLEBEN: Current-Limit Input Leading-Edge Blanking Enable bit                                                          |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | 1 = Leading-Edge Blanking is applied to the selected current-limit input                                                                                                                    |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | 0 = Leading-E                                                                                                                                                                               | Edge Blanking                              | s not applied                 | to the selected                                 | l current-limit in | put             |                |  |  |  |  |

| bit 9-6         | -                                                                                                                                                                                           | ted: Read as '                             |                               |                                                 |                    |                 |                |  |  |  |  |

| bit 5           |                                                                                                                                                                                             |                                            |                               | al High Enable                                  |                    |                 |                |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               | Fault input sigr<br>ng signal is hig            | nals) when seled   | cted blanking s | signal is high |  |  |  |  |

| bit 4           |                                                                                                                                                                                             | •                                          |                               | al Low Enable b                                 |                    |                 |                |  |  |  |  |

|                 |                                                                                                                                                                                             | •                                          | •••                           |                                                 |                    | cted blanking s | signal is low  |  |  |  |  |

|                 | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when the selected blanking signal is low</li> </ul> |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| bit 3           |                                                                                                                                                                                             | ing in PWMxH                               | -                             |                                                 |                    |                 |                |  |  |  |  |

|                 | 1 = State blanking (of current-limit and/or Fault input signals) when the PWMxH output is high                                                                                              |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| h:# 0           | 0 = No blanking when the PWMxH output is high                                                                                                                                               |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| bit 2           | <b>BPHL:</b> Blanking in PWMxH Low Enable bit                                                                                                                                               |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when the PWMxH output is low</li> <li>0 = No blanking when the PWMxH output is low</li> </ul>                     |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

| bit 1           |                                                                                                                                                                                             | ng in PWMxL I                              |                               |                                                 |                    |                 |                |  |  |  |  |

|                 |                                                                                                                                                                                             | -                                          | -                             |                                                 | nals) when the F   | PWMxL output    | is hiah        |  |  |  |  |

|                 |                                                                                                                                                                                             |                                            |                               |                                                 |                    |                 |                |  |  |  |  |

|                 | 0 = No blankii                                                                                                                                                                              | ng when the P                              | WMxL output                   | is high                                         |                    |                 |                |  |  |  |  |

| bit 0           | BPLL: Blanki                                                                                                                                                                                | ng when the P<br>ng in PWMxL L             | ow Enable b                   | it                                              |                    |                 | -              |  |  |  |  |

| bit 0           | <b>BPLL:</b> Blankii<br>1 = State blan                                                                                                                                                      | ng when the P<br>ng in PWMxL L             | ow Enable b<br>t-limit and/or | it<br>Fault input sigr                          | nals) when the F   | PWMxL output    | -              |  |  |  |  |

Note 1: The blanking signal is selected through the BLANKSEL<3:0> bits in the AUXCONx register.

NOTES:

| U-0                 | U-0                                                                                                           | U-0                                 | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|--|--|--|

|                     |                                                                                                               |                                     | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |

| bit 15              |                                                                                                               |                                     | Diocon               | DICCDO                                 | MODEIO               | Olin                 | bit                  |  |  |  |

|                     |                                                                                                               |                                     |                      |                                        |                      |                      |                      |  |  |  |

| R/W-0               | R/W-0                                                                                                         | R/W-0                               | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                           | MSTEN                               | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |

| bit 7               |                                                                                                               |                                     |                      | 1                                      |                      |                      | bit                  |  |  |  |

|                     |                                                                                                               |                                     |                      |                                        |                      |                      |                      |  |  |  |

| Legend:             |                                                                                                               |                                     |                      |                                        |                      |                      |                      |  |  |  |

| R = Readab          | le bit                                                                                                        | W = Writable                        | bit                  | U = Unimplen                           | nented bit, read     | <b>l as</b> '0'      |                      |  |  |  |

| -n = Value a        | t POR                                                                                                         | '1' = Bit is set                    |                      | '0' = Bit is clea                      | ared                 | x = Bit is unkr      | nown                 |  |  |  |

|                     |                                                                                                               |                                     | _ 1                  |                                        |                      |                      |                      |  |  |  |

| bit 15-13           | -                                                                                                             | ted: Read as '                      |                      |                                        |                      |                      |                      |  |  |  |

| bit 12              |                                                                                                               | PI clock is disa                    | -                    | er modes only)                         |                      |                      |                      |  |  |  |

|                     |                                                                                                               | PI clock is disa<br>PI clock is ena |                      | ao 1/U                                 |                      |                      |                      |  |  |  |

| bit 11              |                                                                                                               | able SDOx Pin                       |                      |                                        |                      |                      |                      |  |  |  |

|                     | 1 = SDOx pin                                                                                                  | is not used by                      | the module; p        | oin functions as                       | ; I/O                |                      |                      |  |  |  |

|                     |                                                                                                               | is controlled b                     |                      |                                        |                      |                      |                      |  |  |  |

| bit 10              | MODE16: Word/Byte Communication Select bit                                                                    |                                     |                      |                                        |                      |                      |                      |  |  |  |

|                     | <ul> <li>1 = Communication is word-wide (16 bits)</li> <li>0 = Communication is byte-wide (8 bits)</li> </ul> |                                     |                      |                                        |                      |                      |                      |  |  |  |

|                     |                                                                                                               | •                                   | . ,                  |                                        |                      |                      |                      |  |  |  |

| bit 9               |                                                                                                               | ata Input Samp                      | ole Phase bit        |                                        |                      |                      |                      |  |  |  |

|                     | Master mode:                                                                                                  | :<br>a is sampled at                | the end of da        | ta output time                         |                      |                      |                      |  |  |  |

|                     |                                                                                                               |                                     |                      | data output time                       | ie                   |                      |                      |  |  |  |

|                     | Slave mode:                                                                                                   | -                                   |                      | n Slave mode.                          |                      |                      |                      |  |  |  |

| bit 8               | CKE: Clock E                                                                                                  | dge Select bit                      | 1)                   |                                        |                      |                      |                      |  |  |  |

|                     |                                                                                                               |                                     |                      |                                        | clock state to Id    |                      |                      |  |  |  |

| bit 7               | SSEN: Slave                                                                                                   | Select Enable                       | bit (Slave mo        | de) <sup>(2)</sup>                     |                      |                      |                      |  |  |  |

|                     | $1 = \overline{SSx}$ pin is used for Slave mode                                                               |                                     |                      |                                        |                      |                      |                      |  |  |  |

|                     | 0 = SSx pin is                                                                                                | s not used by the                   | ne module; pir       | n is controlled b                      | y port function      |                      |                      |  |  |  |

| bit 6               |                                                                                                               | olarity Select I                    |                      |                                        |                      |                      |                      |  |  |  |

|                     |                                                                                                               |                                     |                      | ve state is a low<br>e state is a high |                      |                      |                      |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                    | ter Mode Enab                       | le bit               |                                        |                      |                      |                      |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                  |                                     |                      |                                        |                      |                      |                      |  |  |  |

|                     | he CKE bit is not<br>FRMEN = 1).                                                                              | used in Frame                       | d SPI modes.         | Program this b                         | oit to '0' for Frai  | med SPI modes        | S                    |  |  |  |

| -                   | his bit must be cl                                                                                            | eared when FF                       | RMEN = 1.            |                                        |                      |                      |                      |  |  |  |

|                     | o not set both pri                                                                                            |                                     |                      | ers to the value                       | e of 1:1.            |                      |                      |  |  |  |

### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

**3:** Do not set both primary and secondary prescalers to the value of 1:1.

# 21.2 UART Control Registers

# REGISTER 21-1: UxMODE: UARTx MODE REGISTER

| REGISTER              | 21-1: UxMO                                                                                                      | DE: UARTx N                                                        |                                                             | TER                             |                                          |                  |                           |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------|------------------------------------------|------------------|---------------------------|--|--|--|--|

| R/W-0                 | U-0                                                                                                             | R/W-0                                                              | R/W-0                                                       | R/W-0                           | U-0                                      | R/W-0            | R/W-0                     |  |  |  |  |

| UARTEN <sup>(1)</sup> |                                                                                                                 | USIDL                                                              | IREN <sup>(2)</sup>                                         | RTSMD                           |                                          | UEN1             | UEN0                      |  |  |  |  |

| bit 15                |                                                                                                                 |                                                                    |                                                             | ·                               |                                          |                  | bit 8                     |  |  |  |  |

| R/W-0, HC             | R/W-0                                                                                                           | R/W-0, HC                                                          | R/W-0                                                       | R/W-0                           | R/W-0                                    | R/W-0            | R/W-0                     |  |  |  |  |

| WAKE                  | LPBACK                                                                                                          | ABAUD                                                              | URXINV                                                      | BRGH                            | PDSEL1                                   | PDSEL0           | STSEL                     |  |  |  |  |

| bit 7                 |                                                                                                                 | 101100                                                             | Orodity                                                     | ыкоп                            | TDOLLI                                   | TDOLLO           | bit (                     |  |  |  |  |

|                       |                                                                                                                 |                                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| Legend:               |                                                                                                                 | HC = Hardwar                                                       | e Clearable bit                                             | t                               |                                          |                  |                           |  |  |  |  |

| R = Readable          | e bit                                                                                                           | W = Writable I                                                     | oit                                                         | U = Unimple                     | mented bit, rea                          | ad as '0'        |                           |  |  |  |  |

| -n = Value at         | POR                                                                                                             | '1' = Bit is set                                                   |                                                             | '0' = Bit is cle                | eared                                    | x = Bit is unk   | nown                      |  |  |  |  |

| bit 15                | 1 = UARTx is                                                                                                    | ARTx Enable bit<br>s enabled; all U<br>s disabled; all U           | ARTx pins are                                               |                                 |                                          |                  |                           |  |  |  |  |

|                       | is minima                                                                                                       |                                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 14                | •                                                                                                               | ted: Read as '0                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 13                | <b>USIDL:</b> UARTx Stop in Idle Mode bit<br>1 = Discontinues module operation when the device enters Idle mode |                                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       |                                                                                                                 | iues module op<br>es module opera                                  |                                                             |                                 | s Idle mode                              |                  |                           |  |  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                           |                                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       | <ul> <li>1 = IrDA encoder and decoder are enabled</li> <li>0 = IrDA encoder and decoder are disabled</li> </ul> |                                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 11                |                                                                                                                 | <b>RTSMD:</b> Mode Selection for $\overline{\text{UxRTS}}$ Pin bit |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       | 1 = UxRTS p                                                                                                     | oin is in Simplex<br>oin is in Flow Co                             | mode                                                        |                                 |                                          |                  |                           |  |  |  |  |

| bit 10                |                                                                                                                 | ited: Read as '0                                                   |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| bit 9-8               | -                                                                                                               | IARTx Pin Enab                                                     |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                                                                    | JxRX and BCLK<br>JxRX, UxCTS a<br>JxRX and UxRT<br>nd UxRX pins a  | x p <u>ins are</u> enal<br>nd UxRTS pins<br>S pins are enal | are enabled a<br>bled and used; | nd used <sup>(4)</sup><br>UxCTS pin is o | controlled by P  | ORT latches <sup>(4</sup> |  |  |  |  |

| bit 7                 | WAKE: UAR                                                                                                       | Tx Wake-up on                                                      | Start bit Detect                                            | During Sleep                    | Mode Enable I                            | oit              |                           |  |  |  |  |

|                       | in hardwa                                                                                                       | ontinues to sam<br>are on the follow<br>is not enabled             |                                                             |                                 | generated on                             | the falling edge | , bit is cleare           |  |  |  |  |

| bit 6                 | -                                                                                                               | RTx Loopback                                                       | Mode Select b                                               | it                              |                                          |                  |                           |  |  |  |  |

|                       |                                                                                                                 | k mode is enab                                                     |                                                             |                                 |                                          |                  |                           |  |  |  |  |

|                       |                                                                                                                 | k mode is disab                                                    |                                                             |                                 |                                          |                  |                           |  |  |  |  |

| "d:<br>tra            | efer to " <b>Univers</b><br>sPIC33/PIC24 F<br>insmit operation                                                  | amily Referenc                                                     | e <i>Manual"</i> for i                                      | nformation on e                 | enabling the U                           |                  |                           |  |  |  |  |

|                       | is feature is only                                                                                              | -                                                                  |                                                             |                                 | )).                                      |                  |                           |  |  |  |  |

| <b>3:</b> Th          | is feature is only                                                                                              | y available on 4                                                   | s feature is only available on 44-pin and 64-pin devices.   |                                 |                                          |                  |                           |  |  |  |  |

4: This feature is only available on 64-pin devices.

# 24.2 ADC Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADC analog scan channel list, defined in the ADxCSSL/ADxCSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using the DMA peripheral.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1.c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADCxBUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUX A selections use ANO-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. For configuration examples, refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual".

### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5) (CONTINUED)

- bit 7-6 EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits<sup>(3)</sup>

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

$\frac{\text{If CPOL} = 1 \text{ (inverted polarity):}}{\text{Low-to-high transition of the comparator output.}}$  $\frac{\text{If CPOL} = 0 \text{ (non-inverted polarity):}}{\text{High-to-low transition of the comparator output.}}$

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

- If CPOL = 0 (non-inverted polarity):

- Low-to-high transition of the comparator output.

- 00 = Trigger/event/interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator x Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to the internal CVREFIN voltage

- 0 = VIN+ input connects to the CxIN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Op Amp/Comparator x Channel Select bits<sup>(1)</sup>

- 11 = Inverting input of op amp/comparator connects to the CxIN4- pin

- 10 = Inverting input of op amp/comparator connects to the CxIN3- pin

- 01 = Inverting input of op amp/comparator connects to the CxIN2- pin

- 00 = Inverting input of op amp/comparator connects to the CxIN1- pin

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- 3: After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| U-0                           | U-0                                                      | U-0                                                     | U-0              | U-0               | U-0              | U-0                | U-0    |  |  |  |  |

|-------------------------------|----------------------------------------------------------|---------------------------------------------------------|------------------|-------------------|------------------|--------------------|--------|--|--|--|--|

|                               | _                                                        |                                                         | _                | —                 | _                | _                  | _      |  |  |  |  |

| bit 15                        |                                                          |                                                         |                  |                   |                  |                    | bit 8  |  |  |  |  |

| U-0                           | R/W-0                                                    | R/W-0                                                   | R/W-0            | R/W-0             | R/W-0            | R/W-0              | R/W-0  |  |  |  |  |

|                               | CFSEL2                                                   | CFSEL1                                                  | CFSEL0           | CFLTREN           | CFDIV2           | CFDIV1             | CFDIV0 |  |  |  |  |

| oit 7                         | 010222                                                   | 010221                                                  | 010220           | or Entert         | 010112           | 012111             | bit (  |  |  |  |  |

|                               |                                                          |                                                         |                  |                   |                  |                    |        |  |  |  |  |

| L <b>egend:</b><br>R = Readab | le hit                                                   | W = Writable                                            | bit              | II = I Inimplen   | nented bit, read | <b>as</b> '0'      |        |  |  |  |  |

| -n = Value a                  |                                                          | '1' = Bit is set                                        |                  | '0' = Bit is clea |                  | x = Bit is unknown |        |  |  |  |  |

|                               |                                                          |                                                         |                  |                   |                  |                    |        |  |  |  |  |

| oit 15-7                      | Unimplemer                                               | ted: Read as                                            | ʻ0'              |                   |                  |                    |        |  |  |  |  |

| oit 6-4                       | -                                                        |                                                         |                  | lock Select hits  | 2                |                    |        |  |  |  |  |

| 511 0 4                       |                                                          | CFSEL<2:0>: Comparator x Filter Input Clock Select bits |                  |                   |                  |                    |        |  |  |  |  |

|                               |                                                          | $111 = T5CLK^{(1)}$                                     |                  |                   |                  |                    |        |  |  |  |  |

|                               |                                                          | $110 = T4CLK^{(2)}$<br>$101 = T3CLK^{(1)}$              |                  |                   |                  |                    |        |  |  |  |  |

|                               |                                                          | $101 = 13CLK^{(1)}$<br>$100 = T2CLK^{(2)}$              |                  |                   |                  |                    |        |  |  |  |  |

|                               |                                                          | 100 = T2CLK**/<br>011 = Reserved                        |                  |                   |                  |                    |        |  |  |  |  |

|                               |                                                          | 011 = Reserved<br>010 = SYNCO1 <sup>(3)</sup>           |                  |                   |                  |                    |        |  |  |  |  |

|                               | 010 = SYNCO1(4)<br>001 = Fosc(4)                         |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | $001 = POSC^{(4)}$                                       |                                                         |                  |                   |                  |                    |        |  |  |  |  |

| bit 3                         | CFLTREN: C                                               | omparator x F                                           | ilter Enable bit |                   |                  |                    |        |  |  |  |  |

|                               | 1 = Digital filter is enabled                            |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 0 = Digital filter is disabled                           |                                                         |                  |                   |                  |                    |        |  |  |  |  |

| bit 2-0                       | CFDIV<2:0>: Comparator x Filter Clock Divide Select bits |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 111 = Clock divide 1:128                                 |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 110 = Clock divide 1:64                                  |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 101 = Clock divide 1:32                                  |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 100 = Clock divide 1:16                                  |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 011 = Clock divide 1:8                                   |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 010 = Clock                                              |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 001 = Clock                                              |                                                         |                  |                   |                  |                    |        |  |  |  |  |

|                               | 000 = Clock                                              | divide 1:1                                              |                  |                   |                  |                    |        |  |  |  |  |

| Note 1: S                     | See the Type C Ti                                        | mer Block Diad                                          | gram (Figure 1   | 3-2).             |                  |                    |        |  |  |  |  |

| -                             | 21                                                       | - •                                                     |                  | ,                 |                  |                    |        |  |  |  |  |

# REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 2: See the Type B Timer Block Diagram (Figure 13-1).

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 17-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

## 30.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EVXXXGM00X/10X family AC characteristics and timing parameters.

### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 4.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for ExtendedOperating voltage VDD range as described in Section 30.1 "DCCharacteristics". |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

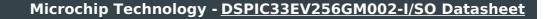

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    |      | 400  | pF    | In I <sup>2</sup> C mode                                            |

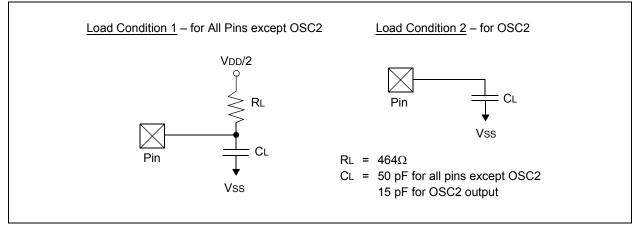

# FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

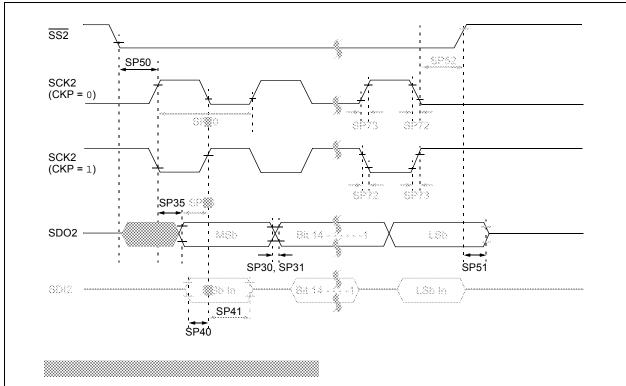

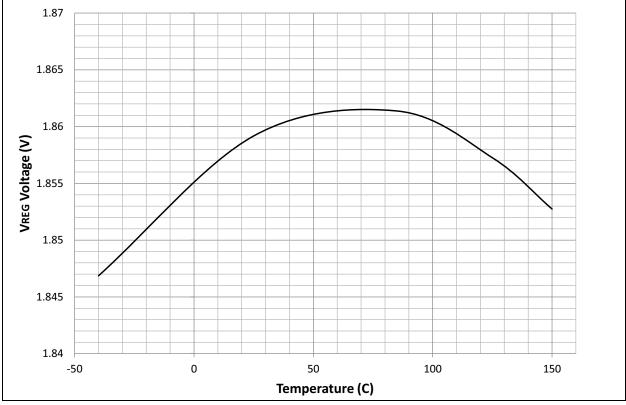

# 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EVXXXGM00X/10X family electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EVXXXGM00X/10X family high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                | 40°C to +150°C |