Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

$\sim$

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm002-i-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

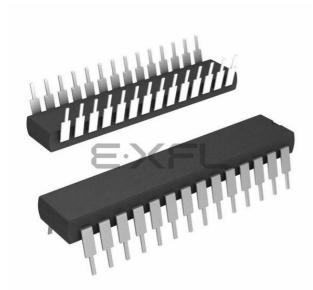

# Pin Diagrams (Continued)

| -                          | GOTO Instruction                                     | 0x000000                         |  |

|----------------------------|------------------------------------------------------|----------------------------------|--|

|                            | Reset Address                                        | 0x000002                         |  |

|                            | Interrupt Vector Table                               | 0x000004<br>0x0001FE<br>0x000200 |  |

| Space                      | User Program<br>Flash Memory<br>(44736 instructions) | 0x000200<br>0x01577E<br>0x015780 |  |

| User Memory Space          | Device Configuration                                 | 0x015780<br>0x0157FE<br>0x015800 |  |

| C                          | Unimplemented<br>(Read '0's)                         |                                  |  |

|                            | Executive Code Memory                                | 0x7FFFE<br>0x800000<br>0x800BFE  |  |

|                            | Reserved                                             | 0x800C00<br>0x800F80             |  |

| ø                          | User OTP Memory                                      | 0x800FFE                         |  |

| ory Spac                   | Reserved                                             | 0x801000                         |  |

| on Mem                     | Write Latches                                        | 0xF9FFFE<br>0xFA0000<br>0xFA0002 |  |

| Configuration Memory Space | Reserved                                             | 0xFA0004                         |  |

|                            | DEVID                                                | 0xFEFFFE<br>0xFF0000<br>0xFF0002 |  |

| ,                          | Reserved                                             | 0xFF0004<br>0xFFFFFE             |  |

| IABLE       | 4-3:  | INP    | UICA                              | APIUR  | EIH        | ROUGI      |             | CAP      | IURE 4    | REGIS      |               | ,     |          |          |          |          |          |               |

|-------------|-------|--------|-----------------------------------|--------|------------|------------|-------------|----------|-----------|------------|---------------|-------|----------|----------|----------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14                            | Bit 13 | Bit 12     | Bit 11     | Bit 10      | Bit 9    | Bit 8     | Bit 7      | Bit 6         | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IC1CON1     | 0140  | _      | _                                 | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | _        | —         | —          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2     | 0142  | _      | _                                 | _      | _          | _          | _           | -        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF      | 0144  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 1 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC1TMR      | 0146  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 1 Timer Regis | ster  |          |          |          |          |          | 0000          |

| IC2CON1     | 0148  | _      | _                                 | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | -        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2     | 014A  | _      | _                                 | _      | _          | _          | _           | -        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF      | 014C  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 2 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC2TMR      | 014E  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 2 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| IC3CON1     | 0150  | _      | _                                 | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | -        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2     | 0152  | _      | _                                 | _      | _          | _          | _           | _        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF      | 0154  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 3 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC3TMR      | 0156  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 3 Timer Regi  | ster  |          |          |          |          |          | 0000          |

| IC4CON1     | 0158  |        |                                   | ICSIDL | ICTSEL2    | ICTSEL1    | ICTSEL0     | _        | _         | _          | ICI1          | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2     | 015A  |        |                                   | —      | —          | _          | _           | _        | IC32      | ICTRIG     | TRIGSTAT      | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF      | 015C  |        |                                   |        |            |            |             |          | Inp       | ut Capture | 4 Buffer Regi | ster  |          |          |          |          |          | xxxx          |

| IC4TMR      | 015E  |        | Input Capture 4 Timer Register 00 |        |            |            |             |          |           |            | 0000          |       |          |          |          |          |          |               |

| Lamandi     |       |        |                                   | aati - | unimanlama | optod road | Loo '0' Boo | at value | ara ahawa | in hovedor | simal         |       |          |          |          |          |          |               |

#### TABLE 4-3: INDUT CARTINE 1 THROUGH INDUT CARTINE A REGISTER MAD

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: **I2C1 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                     | Bit 8     | Bit 7       | Bit 6    | Bit 5       | Bit 4        | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|---------|--------|---------|--------|--------|--------|---------------------------|-----------|-------------|----------|-------------|--------------|-------|-------|-------|-------|---------------|

| I2C1CON1    | 0200  | I2CEN   | —      | I2CSIDL | SCLREL | STRICT | A10M   | DISSLW                    | SMEN      | GCEN        | STREN    | ACKDT       | ACKEN        | RCEN  | PEN   | RSEN  | SEN   | 1000          |

| I2C1CON2    | 0202  | _       | _      | _       | _      | _      | _      | _                         | _         | _           | PCIE     | SCIE        | BOEN         | SDAHT | SBCDE | AHEN  | DHEN  | 1000          |

| I2C1STAT    | 0204  | ACKSTAT | TRSTAT | ACKTIM  |        | _      | BCL    | GCSTAT                    | ADD10     | IWCOL       | I2COV    | D_A         | Р            | S     | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD     | 0206  |         |        |         |        | _      |        |                           |           |             |          | I2C1 Addr   | ess Register |       |       |       |       | 0000          |

| I2C1MSK     | 0208  |         |        |         |        | _      |        |                           |           |             | 12       | 2C1 Address | Mask Regis   | ster  |       |       |       | 0000          |

| I2C1BRG     | 020A  |         |        |         |        |        |        | E                         | Baud Rate | Generator F | Register |             |              |       |       |       |       | 0000          |

| I2C1TRN     | 020C  |         |        |         |        | _      |        | I2C1 Transmit Register    |           |             |          |             |              | OOFF  |       |       |       |               |

| I2C1RCV     | 020E  |         |        |         |        | _      |        | — — I2C1 Receive Register |           |             |          |             |              |       | 0000  |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

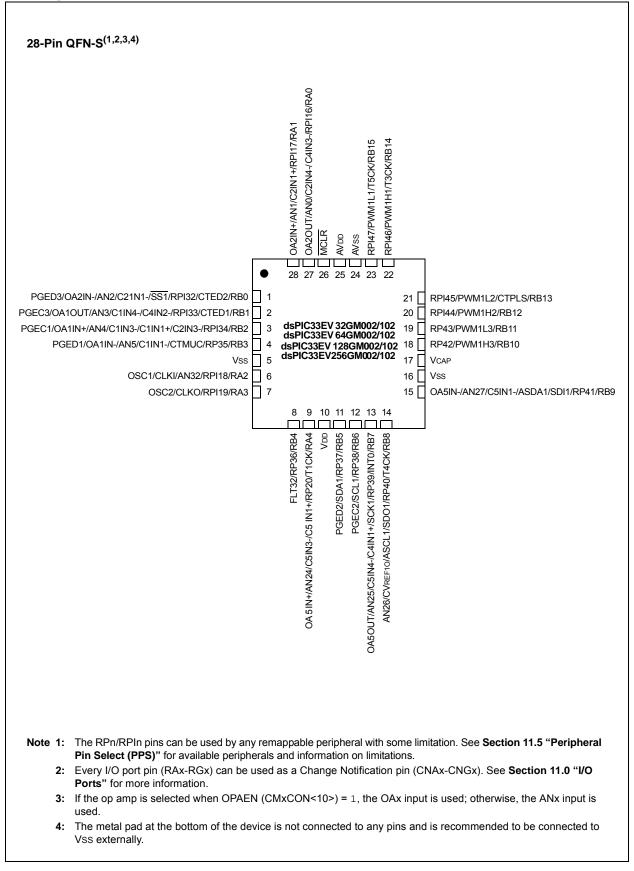

# FIGURE 4-11: PAGED DATA MEMORY SPACE

DS70005144E-page 70

| R/W-0         | R/W-0                                | R/W-0                | R/W-0                | R/W-0                             | R/W-0                     | R/W-0           | R/W-1          |

|---------------|--------------------------------------|----------------------|----------------------|-----------------------------------|---------------------------|-----------------|----------------|

| ROI           | DOZE2 <sup>(3)</sup>                 | DOZE1 <sup>(3)</sup> | DOZE0 <sup>(3)</sup> | DOZEN <sup>(1,4)</sup>            | FRCDIV2                   | FRCDIV1         | FRCDIV0        |

| bit 15        |                                      | •                    | -                    | -                                 |                           | •               | bit 8          |

|               |                                      |                      | DAMO                 |                                   |                           | R/W-0           | DAMA           |

| R/W-0         | R/W-0                                | U-0                  | R/W-0                | R/W-0                             | R/W-0                     |                 | R/W-0          |

| PLLPOST1      | PLLPOST0                             | —                    | PLLPRE4              | PLLPRE3                           | PLLPRE2                   | PLLPRE1         | PLLPRE0        |

| bit 7         |                                      |                      |                      |                                   |                           |                 | bit C          |

| Legend:       |                                      |                      |                      |                                   |                           |                 |                |

| R = Readable  | bit                                  | W = Writable         | bit                  | U = Unimpler                      | nented bit, read          | l as '0'        |                |

| -n = Value at | POR                                  | '1' = Bit is set     |                      | '0' = Bit is cle                  | ared                      | x = Bit is unkr | nown           |

| bit 15        |                                      | on Interrupt b       | i+                   |                                   |                           |                 |                |

|               |                                      | will clear the E     |                      |                                   |                           |                 |                |

|               |                                      | have no effect       |                      | N bit                             |                           |                 |                |

| bit 14-12     | •                                    | Processor Clo        |                      |                                   |                           |                 |                |

|               | 111 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 110 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 101 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 100 = FCY div<br>011 = FCY div       |                      |                      |                                   |                           |                 |                |

|               | 010 = FCY div                        |                      |                      |                                   |                           |                 |                |

|               | 001 = Fcy div                        |                      |                      |                                   |                           |                 |                |

|               |                                      | vided by 1 (def      |                      |                                   |                           |                 |                |

| bit 11        |                                      | e Mode Enable        |                      |                                   |                           |                 |                |

|               |                                      |                      |                      | tween the peri<br>atio are forced |                           | nd the process  | or clocks      |

| bit 10-8      | FRCDIV<2:0>                          | -: Internal Fast     | RC Oscillator        | Postscaler bit                    | S                         |                 |                |

|               | 111 <b>= FRC d</b> i                 | vided by 256         |                      |                                   |                           |                 |                |

|               | 110 <b>= FRC di</b>                  |                      |                      |                                   |                           |                 |                |

|               | 101 = FRC di                         | •                    |                      |                                   |                           |                 |                |

|               | 100 = FRC di<br>011 = FRC di         |                      |                      |                                   |                           |                 |                |

|               | 010 = FRC di                         |                      |                      |                                   |                           |                 |                |

|               |                                      | vided by 2 (de       | fault)               |                                   |                           |                 |                |

|               | 000 <b>= FRC di</b>                  | •                    |                      |                                   |                           |                 |                |

| bit 7-6       | PLLPOST<1:                           | 0>: PLL VCO          | Output Divide        | r Select bits (al                 | so denoted as             | 'N2', PLL posts | caler)         |

|               | 11 = Output d                        |                      |                      |                                   |                           |                 |                |

|               | 10 = Reserve<br>01 = Output d        |                      |                      |                                   |                           |                 |                |

|               | 00 = Output d                        |                      |                      |                                   |                           |                 |                |

| bit 5         |                                      | ted: Read as '       | 0'                   |                                   |                           |                 |                |

| Note 1: Th    | is bit is cleared v                  | when the ROI         | bit is set and a     | an interrupt occ                  | urs.                      |                 |                |

| <b>2:</b> Th  | is register resets                   | s only on a Pov      | wer-on Reset         | (POR).                            |                           |                 |                |

|               | )ZE<2:0> bits ca<br>)ZE<2:0> are igi |                      | en to when th        | e DOZEN bit is                    | clear. If DOZE            | N = 1, any wri  | tes to         |

|               | o DOZEN bit cou                      |                      | 075-2.05 -           |                                   | $2 \cdot 0 > - 0 = 0 = 0$ | attempt by up   | or ooftwara to |

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0          | U-0        | U-0              | U-0             | U-0              | U-0              | U-0            | R/W-0   |

|--------------|------------|------------------|-----------------|------------------|------------------|----------------|---------|

|              | —          | —                | _               | —                | —                | —              | PLLDIV8 |

| bit 15       |            |                  |                 |                  |                  |                | bit 8   |

|              |            |                  |                 |                  |                  |                |         |

| R/W-0        | R/W-0      | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0          | R/W-0   |

|              |            |                  | PLLD            | IV<7:0>          |                  |                |         |

| bit 7        |            |                  |                 |                  |                  |                | bit 0   |

|              |            |                  |                 |                  |                  |                |         |

| Legend:      |            |                  |                 |                  |                  |                |         |

| R = Readab   | ole bit    | W = Writable     | bit             | U = Unimpler     | mented bit, read | as '0'         |         |

| -n = Value a | at POR     | '1' = Bit is set | :               | '0' = Bit is cle | ared             | x = Bit is unk | nown    |

|              |            |                  |                 |                  |                  |                |         |

| bit 15-9     | Unimplemer | nted: Read as '  | 0'              |                  |                  |                |         |

| bit 8-0      | PLLDIV<8:0 | >: PLL Feedba    | ck Divisor bits | s (also denoted  | as 'M', PLL mul  | tiplier)       |         |

|              | 111111111  | = 513            |                 |                  |                  |                |         |

|              | •          |                  |                 |                  |                  |                |         |

|              | •          |                  |                 |                  |                  |                |         |

|              | 000110000  | = 50 (default)   |                 |                  |                  |                |         |

|              | •          |                  |                 |                  |                  |                |         |

|              | •          |                  |                 |                  |                  |                |         |

|              | •          |                  |                 |                  |                  |                |         |

|              | 000000010  |                  |                 |                  |                  |                |         |

|              | 000000000  | -                |                 |                  |                  |                |         |

|              |            |                  |                 |                  |                  |                |         |

# REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

# REGISTER 22-26: CxTRmnCON: CANx TX/RX BUFFER mn CONTROL REGISTER

| R/W-0                          | R-0                            | R-0                              | R-0                            | R/W-0                   | R/W-0            | R/W-0           | R/W-0          |

|--------------------------------|--------------------------------|----------------------------------|--------------------------------|-------------------------|------------------|-----------------|----------------|

| TXENn                          | TXABTn                         | TXLARBn                          | TXERRn                         | TXREQn                  | RTRENn           | TXnPRI1         | TXnPRI0        |

| bit 15                         |                                |                                  |                                |                         |                  |                 | bit 8          |

| R/W-0                          | R-0                            | R-0                              | R-0                            | R/W-0                   | R/W-0            | R/W-0           | R/W-0          |

| TXENm                          | TXABTm <sup>(1)</sup>          | TXLARBm <sup>(1)</sup>           | TXERRm <sup>(1)</sup>          | TXREQm                  | RTRENm           | TXmPRI1         | TXmPRI0        |

| bit 7                          | 170 DTH                        | TXDARDIN                         | TALKAII                        | IXILQIII                |                  |                 | bit (          |

| Logondy                        |                                |                                  |                                |                         |                  |                 |                |

| <b>Legend:</b><br>R = Readable | hit                            | W = Writable                     | hit                            | II – Unimplor           | monted bit read  |                 |                |

|                                |                                |                                  |                                | -                       | nented bit, read |                 |                |

| -n = Value at P                | OR                             | '1' = Bit is set                 |                                | '0' = Bit is cle        | ared             | x = Bit is unkr | lown           |

| bit 15-8                       | See Definition                 | n for bits 7-0, co               | ontrols Buffer n               | 1                       |                  |                 |                |

| bit 7                          |                                | RX Buffer Selec                  |                                |                         |                  |                 |                |

|                                |                                | RBm, is a transi                 |                                |                         |                  |                 |                |

|                                |                                | RBm, is a receiv                 |                                |                         |                  |                 |                |

| bit 6                          | TXABTm: Me                     | essage Abortec                   | l bit <sup>(1)</sup>           |                         |                  |                 |                |

|                                | 1 = Message<br>0 = Message     | was aborted completed trar       | smission succ                  | essfully                |                  |                 |                |

| bit 5                          | TXLARBm: N                     | /lessage Lost A                  | vrbitration bit <sup>(1)</sup> |                         |                  |                 |                |

|                                |                                | lost arbitration                 |                                |                         |                  |                 |                |

|                                | 0 = Message                    | did not lose arl                 | pitration while I              | being sent              |                  |                 |                |

| bit 4                          | TXERRm: Er                     | ror Detected D                   | uring Transmis                 | sion bit <sup>(1)</sup> |                  |                 |                |

|                                |                                | or occurred whi                  |                                |                         |                  |                 |                |

| bit 3                          | TXREQm: Me                     | essage Send R                    | equest bit                     |                         |                  |                 |                |

|                                | 1 = Requests sent              | s that a messag                  | je be sent; the                | bit automatica          | ally clears when | the message     | is successfull |

|                                | 0 = Clearing                   | the bit to '0' wh                | ile set request                | s a message             | abort            |                 |                |

| bit 2                          | RTRENm: Au                     | ito-Remote Tra                   | nsmit Enable b                 | oit                     |                  |                 |                |

|                                |                                | emote transmit<br>emote transmit |                                |                         |                  |                 |                |

| bit 1-0                        | TXmPRI<1:0                     | >: Message Tra                   | ansmission Pri                 | ority bits              |                  |                 |                |

|                                | 11 = Highest<br>10 = High inte | message priori                   |                                |                         |                  |                 |                |

Note: The buffers, SID, EID, DLC, Data Field and Receive Status registers, are located in DMA RAM.

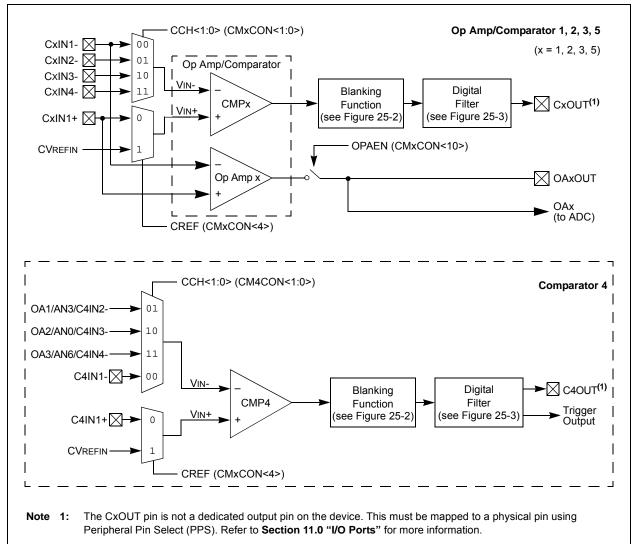

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "**Op Amp/Comparator**" (DS70000357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family devices contain up to five comparators that can be configured in various ways. CMP1, CMP2, CMP3 and CMP5 also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

The following options allow users to:

- Select the Edge for Trigger and Interrupt Generation

- Configure the Comparator Voltage Reference

- Configure Output Blanking and Masking

- Configure as a Comparator or Op Amp (CMP1, CMP2, CMP3 and CMP5 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM

| R/W-0                 | R/W-0                                                    | R/W-0                                  | U-0                 | U-0              | R/W-0                | R/W-0               | R-0                 |

|-----------------------|----------------------------------------------------------|----------------------------------------|---------------------|------------------|----------------------|---------------------|---------------------|

| CON                   | COE                                                      | CPOL                                   | _                   |                  | OPAEN <sup>(2)</sup> | CEVT                | COUT                |

| bit 15                |                                                          |                                        |                     |                  |                      |                     | bit 8               |

|                       |                                                          |                                        |                     |                  |                      |                     |                     |

| R/W-0                 | R/W-0                                                    | U-0                                    | R/W-0               | U-0              | U-0                  | R/W-0               | R/W-0               |

| EVPOL1 <sup>(3)</sup> | EVPOL0 <sup>(3)</sup>                                    | _                                      | CREF <sup>(1)</sup> |                  |                      | CCH1 <sup>(1)</sup> | CCH0 <sup>(1)</sup> |

| bit 7                 |                                                          |                                        |                     |                  |                      |                     | bit C               |

| Legend:               |                                                          |                                        |                     |                  |                      |                     |                     |

| R = Readable          | bit                                                      | W = Writable                           | bit                 | U = Unimpler     | mented bit, read     | <b>as</b> '0'       |                     |

| -n = Value at I       | POR                                                      | '1' = Bit is set                       |                     | '0' = Bit is cle | ared                 | x = Bit is unkr     | nown                |

|                       |                                                          |                                        |                     |                  |                      |                     |                     |

| bit 15                | CON: Op Am                                               | p/Comparator                           | x Enable bit        |                  |                      |                     |                     |

|                       |                                                          | Comparator x is                        |                     |                  |                      |                     |                     |

|                       |                                                          | Comparator x is                        |                     |                  |                      |                     |                     |

| bit 14                |                                                          | rator x Output                         |                     |                  |                      |                     |                     |

|                       |                                                          | tor output is pro<br>tor output is int |                     | xout pin         |                      |                     |                     |

| bit 13                |                                                          | arator x Outpu                         | •                   | ct bit           |                      |                     |                     |

|                       | •                                                        | tor output is inv                      |                     |                  |                      |                     |                     |

|                       | 0 = Comparat                                             | tor output is no                       | t inverted          |                  |                      |                     |                     |

| bit 12-11             | Unimplemen                                               | ted: Read as '                         | 0'                  |                  |                      |                     |                     |

| bit 10                | OPAEN: Op A                                              | Amp x Enable I                         | oit <sup>(2)</sup>  |                  |                      |                     |                     |

|                       | 1 = Op Amp ><br>0 = Op Amp >                             |                                        |                     |                  |                      |                     |                     |

| bit 9                 | CEVT: Compa                                              | arator x Event                         | bit                 |                  |                      |                     |                     |

|                       | interrupts                                               | s until the bit is                     | cleared             | POL<1:0> sett    | ings, occurred;      | disables future     | e triggers and      |

|                       | •                                                        | ator event did n                       |                     |                  |                      |                     |                     |

| bit 8                 |                                                          | arator x Outpu                         |                     |                  |                      |                     |                     |

|                       | $\frac{\text{When CPOL}}{1 = \text{Vin} + > \text{Vin}}$ | = 0 (non-invert                        | ed polarity):       |                  |                      |                     |                     |

|                       | 1 = VIN + > VII $0 = VIN + < VII$                        | -                                      |                     |                  |                      |                     |                     |

|                       | When CPOL                                                | = 1 (inverted p                        | olarity):           |                  |                      |                     |                     |

|                       | 1 = VIN + < VII                                          |                                        | <u> </u>            |                  |                      |                     |                     |

|                       | 0 = VIN + > VII                                          | -                                      |                     |                  |                      |                     |                     |

### **REGISTER 25-2:** CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2, 3 OR 5)

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- **2:** The op amp and the comparator can be used simultaneously in these devices. The OPAEN bit only enables the op amp while the comparator is still functional.

- **3:** After configuring the comparator, either for a high-to-low or low-to-high COUT transition (EVPOL<1:0> (CMxCON<7:6>) = 10 or 01), the Comparator x Event bit, CEVT (CMxCON<9>), and the Comparator Interrupt Flag, CMPIF (IFS1<2>), must be cleared before enabling the Comparator Interrupt Enable bit, CMPIE (IEC1<2>).

| Bit Field     | Register  | Description                                                                                                                                                                                                                                                                                                 |

|---------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCIOFNC      | FOSC      | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is the general purpose digital I/O pin                                                                                                                                                                        |

| IOL1WAY       | FOSC      | Peripheral Pin Select Configuration bit<br>1 = Allows only one reconfiguration<br>0 = Allows multiple reconfigurations                                                                                                                                                                                      |

| FCKSM<1:0>    | FOSC      | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                           |

| PLLKEN        | FOSC      | PLL Lock Wait Enable bit<br>1 = Clock switches to the PLL source; will wait until the PLL lock signal is valid<br>0 = Clock switch will not wait for PLL lock                                                                                                                                               |

| WDTPS<3:0>    | FWDT      | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                       |

| WDTPRE        | FWDT      | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                       |

| FWDTEN<1:0>   | FWDT      | <ul> <li>Watchdog Timer Enable bits</li> <li>11 = WDT is enabled in hardware</li> <li>10 = WDT is controlled through the SWDTEN bit</li> <li>01 = WDT is enabled only while device is active and disabled in Sleep; the SWDTEN bit is disabled</li> <li>00 = WDT and the SWDTEN bit are disabled</li> </ul> |

| WINDIS        | FWDT      | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer is in Non-Window mode<br>0 = Watchdog Timer is in Window mode                                                                                                                                                                                        |

| WDTWIN<1:0>   | FWDT      | Watchdog Timer Window Select bits<br>11 = WDT window is 25% of WDT period<br>10 = WDT window is 37.5% of WDT period<br>01 = WDT window is 50% of WDT period<br>00 = WDT window is 75% of WDT period                                                                                                         |

| BOREN         | FPOR      | Brown-out Reset (BOR) Detection Enable bit<br>1 = BOR is enabled<br>0 = BOR is disabled                                                                                                                                                                                                                     |

| ICS<1:0>      | FICD      | ICD Communication Channel Select bits<br>11 = Communicates on PGEC1 and PGED1<br>10 = Communicates on PGEC2 and PGED2<br>01 = Communicates on PGEC3 and PGED3<br>00 = Reserved, do not use                                                                                                                  |

| DMTIVT<15:0>  | FDMTINTVL | Lower 16 Bits of 32-Bit Field that Configures the DMT Window Interval bits                                                                                                                                                                                                                                  |

| DMTIVT<31:16> | FDMTINTVH | Upper 16 Bits of 32-Bit Field that Configures the DMT Window Interval bits                                                                                                                                                                                                                                  |

| DMTCNT<15:0>  | FDMTCNTL  | Lower 16 Bits of 32-Bit Field that Configures the DMT Instruction Count Time-out Value bits                                                                                                                                                                                                                 |

| TABLE 27-2: | dsPIC33EVXXXGM00X/10X CONFIGURATION BITS DESCRIPTION (CONTINUED) |

|-------------|------------------------------------------------------------------|

|-------------|------------------------------------------------------------------|

# 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EV instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into following five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the Status Flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have the following three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

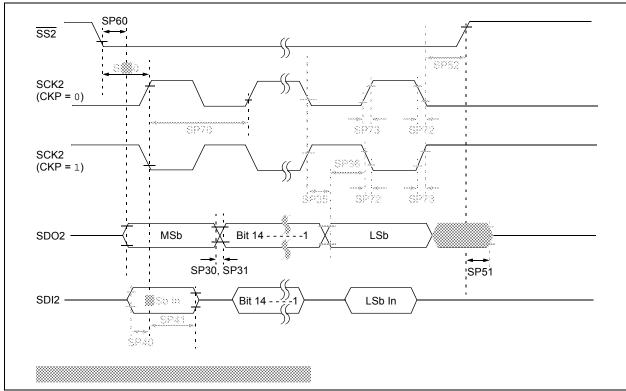

# FIGURE 30-17: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

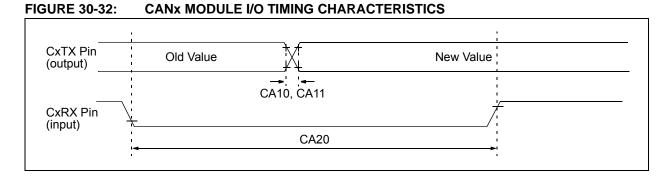

# TABLE 30-48: CANx MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                    |  |  |

|--------------------|--------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|

| Param<br>No.       | Symbol                                                 | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| CA10               | TIOF                                                   | Port Output Fall Time         | —                                                                                                                                                                                                                                                                                     | _                   |      | ns    | See Parameter DO32 |  |  |

| CA11               | TIOR                                                   | Port Output Rise Time         | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 |  |  |

| CA20               | CA20 TCWF Pulse Width to Trigger<br>CAN Wake-up Filter |                               | 120                                                                                                                                                                                                                                                                                   |                     |      | ns    |                    |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

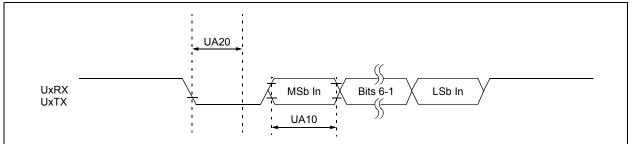

# FIGURE 30-33: UARTX MODULE I/O TIMING CHARACTERISTICS

# TABLE 30-49: UARTx MODULE I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                      |                                                   | Standard Operating Conditions: 4.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                     |      |       |            |  |

|--------------------|--------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|--|

| Param<br>No.       | Symbol Characteristic <sup>(1)</sup> |                                                   | Min.                                                                                                                              | Тур. <sup>(2)</sup> | Max. | Units | Conditions |  |

| UA10               | TUABAUD                              | UARTx Baud Time                                   | 66.67                                                                                                                             | —                   | _    | ns    |            |  |

| UA11               | FBAUD                                | UARTx Baud Frequency                              | —                                                                                                                                 | —                   | 15   | Mbps  |            |  |

| UA20               | TCWF                                 | Start Bit Pulse Width to Trigger<br>UARTx Wake-up | 500                                                                                                                               | _                   |      | ns    |            |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

# dsPIC33EVXXXGM00X/10X FAMILY

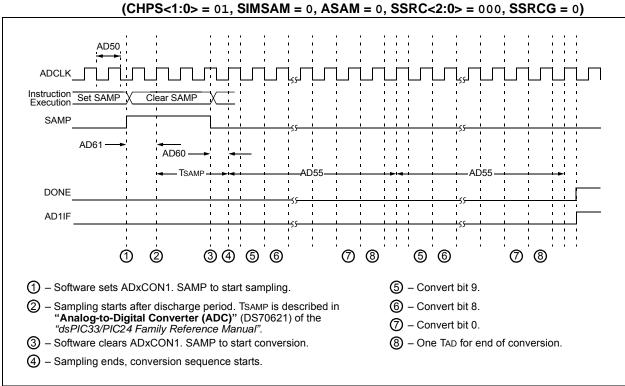

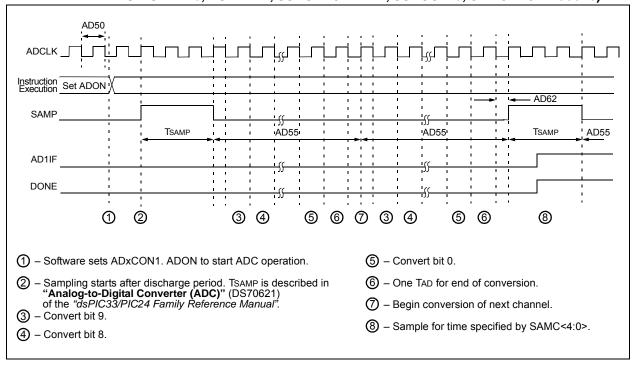

# FIGURE 30-35: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS

### FIGURE 30-36: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 1): 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |           |                     |      |       |                                      |

|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------|------|-------|--------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                                                                                                                                                                                                                                                   | Min.      | Тур. <sup>(4)</sup> | Max. | Units | Conditions                           |

|                    |        | Cloc                                                                                                                                                                                                                                                                                             | k Parame  | eters               |      |       |                                      |

| AD50               | TAD    | ADC Clock Period                                                                                                                                                                                                                                                                                 | 75        | _                   | _    | ns    |                                      |

| AD51               | tRC    | ADC Internal RC Oscillator Period                                                                                                                                                                                                                                                                | —         | 250                 |      | ns    |                                      |

|                    |        | Con                                                                                                                                                                                                                                                                                              | version F | Rate                |      |       |                                      |

| AD55               | tCONV  | Conversion Time                                                                                                                                                                                                                                                                                  | —         | 12                  | _    | TAD   |                                      |

| AD56               | FCNV   | Throughput Rate                                                                                                                                                                                                                                                                                  | —         | —                   | 1.1  | Msps  | Using simultaneous sampling          |

| AD57a              | TSAMP  | Sample Time When Sampling Any<br>ANx Input                                                                                                                                                                                                                                                       | 2         | —                   | _    | Tad   |                                      |

| AD57b              | TSAMP  | Sample Time When Sampling the<br>Op Amp Outputs                                                                                                                                                                                                                                                  | 4         | —                   | _    | TAD   |                                      |

|                    |        | Timin                                                                                                                                                                                                                                                                                            | ng Param  | eters               |      |       |                                      |

| AD60               | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                                                                                                                                                                                                                                           | 2         | —                   | 3    | TAD   | Auto-convert trigger is not selected |

| AD61               | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>                                                                                                                                                                                                                                    | 2         | —                   | 3    | TAD   |                                      |

| AD62               | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>                                                                                                                                                                                                                               | —         | 0.5                 | —    | TAD   |                                      |

| AD63               | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2)</sup>                                                                                                                                                                                                                          | —         | —                   | 20   | μS    | See Note 3                           |

### TABLE 30-58: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but is not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

- **2:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

- **3:** The parameter, tDPU, is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (ADxCON1<15>) = 1). During this time, the ADC result is indeterminate.

- 4: These parameters are characterized but not tested in manufacturing.

### TABLE 30-59: DMA MODULE TIMING REQUIREMENTS

|              |                                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |            |

|--------------|--------------------------------|-------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No. | Characteristic                 | Min.                                                  | Тур. <sup>(1)</sup> | Max. | Units | Conditions |

| DM1          | DMA Byte/Word Transfer Latency | 1 Tcy <b>(2)</b>                                      | —                   | —    | ns    |            |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Because DMA transfers use the CPU data bus, this time is dependent on other functions on the bus.

# dsPIC33EVXXXGM00X/10X FAMILY

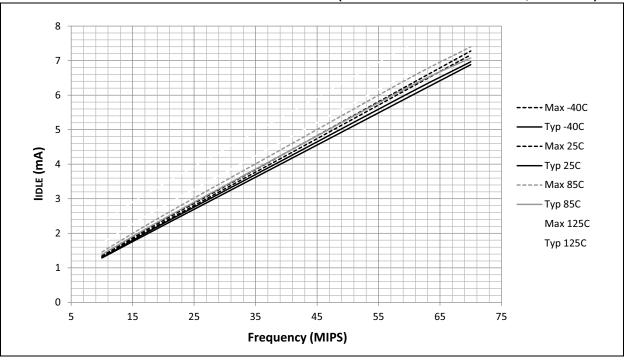

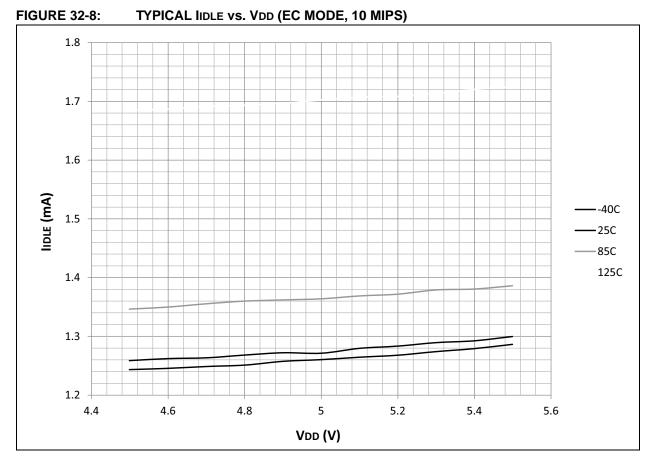

# 32.2 IIDLE

FIGURE 32-7: TYPICAL/MAXIMUM lidle vs. Fosc (EC MODE 10 MHz TO 70 MHz, 5.5V MAX)

DS70005144E-page 416

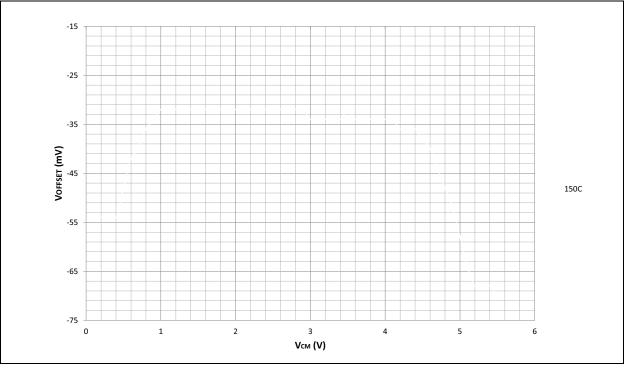

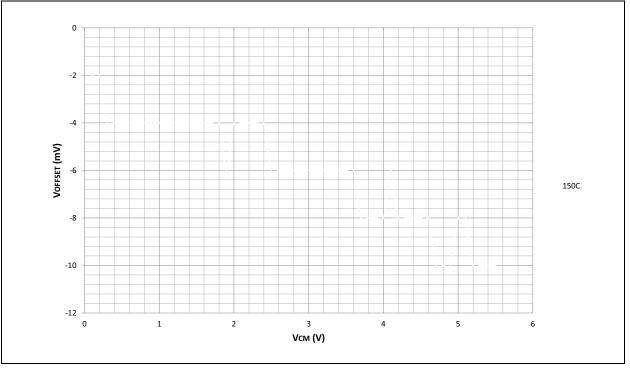

# 33.14 Comparator Op Amp Offset

# FIGURE 33-33: TYPICAL COMPARATOR OFFSET vs. Vcm

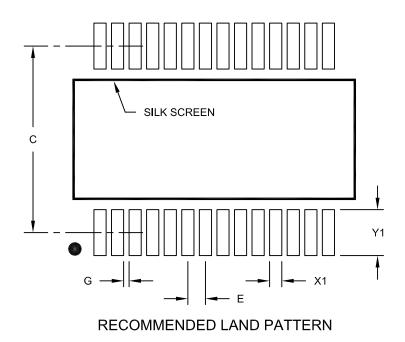

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Contact Pitch            | E  |             | 0.65 BSC |      |

| Contact Pad Spacing      | С  |             | 7.20     |      |

| Contact Pad Width (X28)  | X1 |             |          | 0.45 |

| Contact Pad Length (X28) | Y1 |             |          | 1.75 |

| Distance Between Pads    | G  | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

# Е

| Electrical Characteristics       |          |

|----------------------------------|----------|

| AC                               | 351, 408 |

| Equations                        |          |

| BRG Formula                      | 229      |

| Device Operating Frequency       | 124      |

| Fosc Calculation                 |          |

| Frame Time Calculations          |          |

| FSCL Frequency                   | 229      |

| Fvco Calculation                 |          |

| SYNCMIN and SYNCMAX Calculations |          |

| Tick Period Calculation          | 239      |

| Errata                           | 11       |

|                                  |          |

# F

| Flash Program Memory        | 83 |

|-----------------------------|----|

| Control Registers           | 85 |

| Error Correcting Code (ECC) |    |

| Operations                  |    |

| Resources                   |    |

| RTSP Operation              | 84 |

| Table Instructions          |    |

| Flexible Configuration      |    |

| -                           |    |

# G

| Catting Started with 16 Dit DCCa               | 17 |

|------------------------------------------------|----|

| Getting Started with 16-Bit DSCs               |    |

| Connection Requirements                        | 17 |

| CPU Logic Filter Capacitor Connection (VCAP)   | 18 |

| Decoupling Capacitors                          | 17 |

| External Oscillator Pins                       | 19 |

| ICSP Pins                                      | 19 |

| Master Clear (MCLR) Pin                        | 18 |

| Oscillator Value Conditions on Device Start-up | 19 |

| Unused I/Os                                    | 19 |

# Н

| High Temperature                            |     |

|---------------------------------------------|-----|

| Thermal Operating Conditions                | 404 |

| High-Speed PWM                              | 199 |

| Control Registers                           | 204 |

| Faults                                      | 199 |

| Resources                                   | 203 |

| High-Temperature Electrical Characteristics | 403 |

| Absolute Maximum Ratings                    | 403 |

# I

| I/O Ports                            | 143        |

|--------------------------------------|------------|

| Configuring Analog/Digital Port Pins | 144        |

| Helpful Tips                         | 151        |

| High-Voltage Detect (HVD)            | 151        |

| Open-Drain Configuration             | 144        |

| Parallel I/O (PIO)                   | 143        |

| Peripheral Pin Select (PPS)          | 145        |

| Slew Rate Selection                  | 145        |

| Write/Read Timing                    | 144        |

| In-Circuit Debugger                  | 326        |

| MPLAB ICD 3                          | 339        |

| PICkit 3 Programmer                  | 339        |

| In-Circuit Emulation                 |            |

| In-Circuit Serial Programming (ICSP) | . 317, 326 |

| Input Capture                        |            |

| Control Registers                    | 190        |

| Input Change Notification (ICN)      | 144        |

| Instruction Addressing Modes                    | 74  |

|-------------------------------------------------|-----|

| File Register Instructions                      | 74  |

| Fundamental Modes Supported                     | 75  |

| MAC Instructions                                |     |

| MCU Instructions                                | 74  |

| Move and Accumulator Instructions               | 75  |

| Other Instructions                              | 75  |

| Instruction Set                                 |     |

| Overview                                        | 330 |

| Summary                                         | 327 |

| Symbols Used in Opcode                          |     |

| Interfacing Program and Data Memory Spaces      | 79  |

| Inter-Integrated Circuit (I <sup>2</sup> C)     |     |

| Baud Rate Generator                             | 229 |

| Control Registers                               | 231 |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |     |

| Internal LPRC Oscillator                        |     |

| Use with WDT                                    |     |

| Internet Address                                | 493 |

| Interrupt Controller                            |     |

| Control and Status Registers                    |     |

| IECx                                            |     |

| IFSx                                            |     |

| INTCON1                                         |     |

| INTCON2                                         |     |

| INTCON3                                         |     |

| INTCON4                                         |     |

| INTTREG                                         |     |

| IPCx                                            |     |

| Reset Sequence                                  |     |

| Interrupt Vector Table (IVT)                    |     |

| Details                                         | 98  |

#### Μ

| Memory Maps                                 |     |

|---------------------------------------------|-----|

| EDS                                         | 72  |

| Memory Organization                         | 31  |

| Microchip Internet Web Site                 |     |

| Modulo Addressing                           | 76  |

| Applicability                               |     |

| Operation Example                           | 76  |

| Start and End Address                       |     |

| W Address Register Selection                |     |

| MPLAB PM3 Device Programmer                 | 339 |

| MPLAB REAL ICE In-Circuit Emulator System   | 339 |

| MPLAB X Integrated Development              |     |

| Environment Software                        | 337 |

| MPLINK Object Linker/MPLIB Object Librarian | 338 |

| 0                                           |     |

| Op Amp/Comparator                           | 301 |

| Control Registers                           | 303 |

| Oscillator Configuration                    | 400 |

| e en le el le egieter e ninnen internet e el e |     |

|---------------------------------------------------------------------------------|-----|

| Oscillator Configuration                                                        | 123 |

| Bit Values for Clock Selection                                                  | 125 |

| CPU Clocking System                                                             | 124 |

| Output Compare                                                                  | 193 |

| Control Registers                                                               | 194 |

| Р                                                                               |     |

| Packaging                       |          |

|---------------------------------|----------|

| Details                         |          |

| Marking                         | 461, 462 |

| Peripheral Module Disable (PMD) | 135      |

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0975-5