#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·>>F

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm002-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EVXXXGM00X/10X family Digital Signal Controller (DSC) devices.

dsPIC33EVXXXGM00X/10X family devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

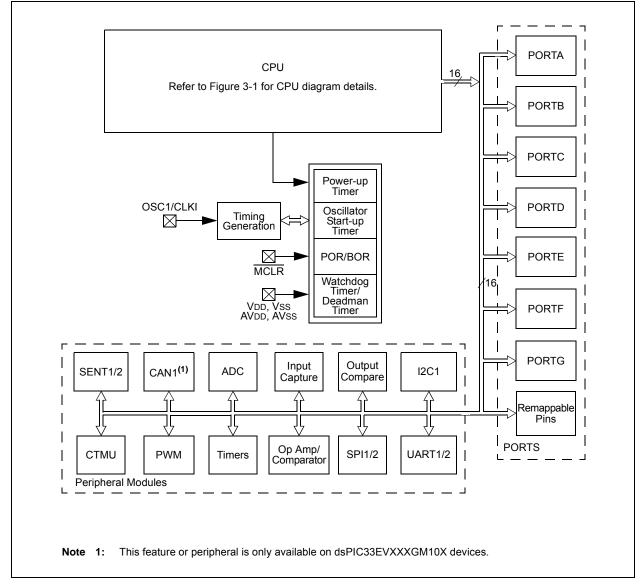

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

### FIGURE 1-1: dsPIC33EVXXXGM00X/10X FAMILY BLOCK DIAGRAM

| R/W-0               | U-0                          | R/W-0                                                 | R/W-0                                                | EGISTER             | R-0             | R-0             | R-0        |

|---------------------|------------------------------|-------------------------------------------------------|------------------------------------------------------|---------------------|-----------------|-----------------|------------|

| VAR                 | 0-0                          | US1                                                   | US0                                                  | EDT <sup>(1)</sup>  | DL2             | DL1             | R-0<br>DL0 |

| pit 15              | _                            | 031                                                   | 030                                                  | EDI                 | DL2             |                 | bLU        |

| R/W-0               | R/W-0                        | R/W-1                                                 | R/W-0                                                | R/C-0               | R-0             | R/W-0           | R/W-0      |

| SATA                | SATB                         | SATDW                                                 | ACCSAT                                               | IPL3 <sup>(2)</sup> | SFA             | RND             | IF         |

| bit 7               | SAID                         | SAIDW                                                 | ACCOAL                                               | IF LOV /            | SFA             | RIND            | bit        |

| Legend:             |                              | C = Clearable                                         | - bit                                                |                     |                 |                 |            |

| R = Readable        | bit                          | W = Writable                                          |                                                      | U = Unimplem        | onted hit rea   | d as '0'        |            |

| -n = Value at F     |                              | '1' = Bit is set                                      |                                                      | '0' = Bit is clea   |                 | x = Bit is unkr |            |

|                     | -                            |                                                       |                                                      |                     |                 |                 |            |

| bit 15              | 1 = Variable e               | exception proce                                       | ocessing Later<br>essing latency                     | is enabled          |                 |                 |            |

| L:4 4 4             |                              |                                                       | sing latency is                                      | enabled             |                 |                 |            |

| bit 14<br>bit 13-12 | •                            | ted: Read as '                                        | 0<br>igned/Signed (                                  | Control hito        |                 |                 |            |

|                     | 01 = DSP eng<br>00 = DSP eng | gine multiplies<br>gine multiplies<br>gine multiplies | are signed                                           |                     |                 |                 |            |

| bit 11              |                              |                                                       | ation Control bi<br>e $DO$ loop at th                | e end of the cu     | rrent loop iter | ation           |            |

| bit 10-8            | 111 = 7 DO lo                | ops are active                                        |                                                      | ts                  |                 |                 |            |

| bit 7               |                              | Saturation En                                         |                                                      |                     |                 |                 |            |

|                     |                              | ator A saturatio<br>ator A saturatio                  |                                                      |                     |                 |                 |            |

| bit 6               | 1 = Accumula                 | Saturation En<br>ator B saturatio<br>ator B saturatio | n is enabled                                         |                     |                 |                 |            |

| bit 5               | 1 = Data Space               | ce write satura                                       | from DSP Engi<br>tion is enabled<br>tion is disabled |                     | Enable bit      |                 |            |

| bit 4               | -                            | cumulator Satu                                        | ration Mode S                                        |                     |                 |                 |            |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

# 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33EVXXXGM00X/10X family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. The data for the ALU operation can come from the W register array or from the data memory, depending on the addressing mode of the instruction. Similarly, the output data from the ALU can be written to the W register array or a data memory location.

For information on the SR bits affected by each instruction, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

## 3.7.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes the single-cycle per bit of the divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.8 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON) as follows:

- Fractional or Integer DSP Multiply (IF)

- Signed, Unsigned or Mixed-Sign DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- · Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

# TABLE 3-2:DSP INSTRUCTIONSSUMMARY

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

# TABLE 4-1: CPU CORE REGISTER MAP (CONTINUED)

|             |       |               |                           |         |                 |         | -       |        |          |        |        |        |        |        |        |        |        | T                 |

|-------------|-------|---------------|---------------------------|---------|-----------------|---------|---------|--------|----------|--------|--------|--------|--------|--------|--------|--------|--------|-------------------|

| SFR<br>Name | Addr. | Bit 15        | Bit 14                    | Bit 13  | Bit 12          | Bit 11  | Bit 10  | Bit 9  | Bit 8    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Reset<br>s |

| DOENDH      | 0040  | _             | —                         | _       | —               | —       | —       | —      | —        | —      | —      |        |        | DOEND  | H<5:0> |        |        | 00xx              |

| SR          | 0042  | OA            | OB                        | SA      | SB              | OAB     | SAB     | DA     | DC       | IPL2   | IPL1   | IPL0   | RA     | Ν      | OV     | Z      | С      | 0000              |

| CORCON      | 0044  | VAR           | _                         | US1     | US0             | EDT     | DL2     | DL1    | DL0      | SATA   | SATB   | SATDW  | ACCSAT | IPL3   | SFA    | RND    | IF     | 0020              |

| MODCON      | 0046  | XMODEN        | YMODEN                    | _       | —               | BWM3    | BWM2    | BWM1   | BWM0     | YWM3   | YWM2   | YWM1   | YWM0   | XWM3   | XWM2   | XWM1   | XWM0   | 0000              |

| XMODSRT     | 0048  | XMODSRT<15:1> |                           |         |                 |         |         |        |          |        | 0      | xxxx   |        |        |        |        |        |                   |

| XMODEND     | 004A  |               |                           |         | XMODEND<15:1>   |         |         |        |          |        |        |        | 1      | xxxx   |        |        |        |                   |

| YMODSRT     | 004C  |               |                           |         |                 |         |         | YMC    | DSRT<15: | 1>     |        |        |        |        |        |        | 0      | xxxx              |

| YMODEND     | 004E  |               |                           |         |                 |         |         | YMC    | DEND<15: | 1>     |        |        |        |        |        |        | 1      | xxxx              |

| XBREV       | 0050  | BREN          | XBREV14                   | XBREV13 | XBREV12         | XBREV11 | XBREV10 | XBREV9 | XBREV8   | XBREV7 | XBREV6 | XBREV5 | XBREV4 | XBREV3 | XBREV2 | XBREV1 | XBREV0 | 8xxx              |

| DISICNT     | 0052  | _             | _                         |         | DISICNT<13:0> x |         |         |        |          |        | xxxx   |        |        |        |        |        |        |                   |

| TBLPAG      | 0054  | _             | — — — — — — — TBLPAG<7:0> |         |                 |         |         |        |          |        |        | 0000   |        |        |        |        |        |                   |

| MSTRPR      | 0058  |               | MSTRPR<15:0>              |         |                 |         |         |        |          |        | 0000   |        |        |        |        |        |        |                   |

| CTXTSTAT    | 005A  | _             | —                         | _       | —               | —       | CCTXI2  | CCTXI1 | CCTXI0   | —      | —      | _      | _      | —      | MCTXI2 | MCTXI1 | MCTXI0 | 0000              |

dsPIC33EVXXXGM00X/10X FAMILY

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4     | -9:   | CAN1     | I REGIS  | STER M   | AP WHE   | N WIN (  | C1CTR    | L<0>) =  | 0 <b>OR</b> 1 | FOR ds   | PIC33E   | VXXXGN   | 110X DE  | VICES    |            |          |          |               |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|---------------|----------|----------|----------|----------|----------|------------|----------|----------|---------------|

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8         | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2      | Bit 1    | Bit 0    | All<br>Resets |

| C1CTRL1     | 0400  | _        | —        | CSIDL    | ABAT     | CANCKS   | REQOP2   | REQOP1   | REQOP0        | OPMODE2  | OPMODE1  | OPMODE0  | —        | CANCAP   | —          | -        | WIN      | 0480          |

| C1CTRL2     | 0402  | _        | —        | —        | —        | _        | —        | —        | —             | —        | —        | _        |          | l        | DNCNT<4:0> |          |          | 0000          |

| C1VEC       | 0404  | —        | _        | —        | FILHIT4  | FILHIT3  | FILHIT2  | FILHIT1  | FILHIT0       | _        | ICODE6   | ICODE5   | ICODE4   | ICODE3   | ICODE2     | ICODE1   | ICODE0   | 0000          |

| C1FCTRL     | 0406  | DMABS2   | DMABS1   | DMABS0   | _        | _        | —        | —        | —             | _        | —        | FSA5     | FSA4     | FSA3     | FSA2       | FSA1     | FSA0     | 0000          |

| C1FIFO      | 0408  | -        | —        | FBP5     | FBP4     | FBP3     | FBP2     | FBP1     | FBP0          | —        | —        | FNRB5    | FNRB4    | FNRB3    | FNRB2      | FNRB1    | FNRB0    | 0000          |

| C1INTF      | 040A  | -        | —        | ТХВО     | TXBP     | RXBP     | TXWAR    | RXWAR    | EWARN         | IVRIF    | WAKIF    | ERRIF    | —        | FIFOIF   | RBOVIF     | RBIF     | TBIF     | 0000          |

| C1INTE      | 040C  |          | —        | —        | -        | —        | —        | —        | —             | IVRIE    | WAKIE    | ERRIE    | —        | FIFOIE   | RBOVIE     | RBIE     | TBIE     | 0000          |

| C1EC        | 040E  | TERRCNT7 | TERRCNT6 | TERRCNT5 | TERRCNT4 | TERRCNT3 | TERRCNT2 | TERRCNT1 | TERRCNT0      | RERRCNT7 | RERRCNT6 | RERRCNT5 | RERRCNT4 | RERRCNT3 | RERRCNT2   | RERRCNT1 | RERRCNT0 | 0000          |

| C1CFG1      | 0410  |          | —        | —        | -        | —        | —        | —        | —             | SJW1     | SJW0     | BRP5     | BRP4     | BRP3     | BRP2       | BRP1     | BRP0     | 0000          |

| C1CFG2      | 0412  |          | WAKFIL   | —        | -        | —        | SEG2PH2  | SEG2PH1  | SEG2PH0       | SEG2PHTS | SAM      | SEG1PH2  | SEG1PH1  | SEG1PH0  | PRSEG2     | PRSEG1   | PRSEG0   | 0000          |

| C1FEN1      | 0414  |          |          |          |          |          |          |          | FLTE          | N<15:0>  |          |          |          |          |            |          |          | FFFF          |

| C1FMSKSEL1  | 0418  | F7MSK1   | F7MSK0   | F6MSK1   | F6MSK0   | F5MSK1   | F5MSK0   | F4MSK1   | F4MSK0        | F3MSK1   | F3MSK0   | F2MSK1   | F2MSK0   | F1MSK1   | F1MSK0     | F0MSK1   | F0MSK0   | 0000          |

| C1FMSKSEL2  | 041A  | F15MSK1  | F15MSK0  | F14MSK1  | F14MSK0  | F13MSK1  | F13MSK0  | F12MSK1  | F12MSK0       | F11MSK1  | F11MSK0  | F10MSK1  | F10MSK0  | F9MSK1   | F9MSK0     | F8MSK1   | F8MSK0   | 0000          |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# TABLE 4-10: CAN1 REGISTER MAP WHEN WIN (C1CTRL<0>) = 0 FOR dsPIC33EVXXXGM10X DEVICES

| SFR<br>Name | Addr.         | Bit 15                              | Bit 14                                                                                                             | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0   | All<br>Resets |

|-------------|---------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------|--------|--------|--------|---------|---------|---------|---------|---------|--------|--------|--------|---------|---------|---------------|

|             | 0400-<br>041E |                                     | See definition when WIN = x                                                                                        |         |        |        |        |         |         |         |         |         |        |        |        |         |         |               |

| C1RXFUL1    | 0420          |                                     | RXFUL<15:0> 00                                                                                                     |         |        |        |        |         |         |         |         |         | 0000   |        |        |         |         |               |

| C1RXFUL2    | 0422          |                                     | RXFUL<31:16> 00                                                                                                    |         |        |        |        |         |         |         |         |         | 0000   |        |        |         |         |               |

| C1RXOVF1    | 0428          |                                     | RXOVF<15:0> 00                                                                                                     |         |        |        |        |         |         |         |         |         | 0000   |        |        |         |         |               |

| C1RXOVF2    | 042A          |                                     |                                                                                                                    |         |        |        |        |         | RXOVF   | <31:16> |         |         |        |        |        |         |         | 0000          |

| C1TR01CON   | 0430          | TXEN1                               | TXABT1                                                                                                             | TXLARB1 | TXERR1 | TXREQ1 | RTREN1 | TX1PRI1 | TX1PRI0 | TXEN0   | TXABAT0 | TXLARB0 | TXERR0 | TXREQ0 | RTREN0 | TX0PRI1 | TX0PRI0 | 0000          |

| C1TR23CON   | 0432          | TXEN3                               | TXABT3                                                                                                             | TXLARB3 | TXERR3 | TXREQ3 | RTREN3 | TX3PRI1 | TX3PRI0 | TXEN2   | TXABAT2 | TXLARB2 | TXERR2 | TXREQ2 | RTREN2 | TX2PRI1 | TX2PRI0 | 0000          |

| C1TR45CON   | 0434          | TXEN5                               | TXABT5                                                                                                             | TXLARB5 | TXERR5 | TXREQ5 | RTREN5 | TX5PRI1 | TX5PRI0 | TXEN4   | TXABAT4 | TXLARB4 | TXERR4 | TXREQ4 | RTREN4 | TX4PRI1 | TX4PRI0 | 0000          |

| C1TR67CON   | 0436          | TXEN7                               | TXABT7 TXLARB7 TXERR7 TXREQ7 RTREN7 TX7PRI1 TX7PRI0 TXEN6 TXABAT6 TXLARB6 TXER6 TXREQ6 RTREN6 TX6PRI1 TX6PRI0 XXXX |         |        |        |        |         |         |         |         |         | xxxx   |        |        |         |         |               |

| C1RXD       | 0440          |                                     | CAN1 Receive Data Word Register                                                                                    |         |        |        |        |         |         |         |         |         | xxxx   |        |        |         |         |               |

| C1TXD       | 0442          | CAN1 Transmit Data Word Register xx |                                                                                                                    |         |        |        |        |         |         | xxxx    |         |         |        |        |        |         |         |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-24: OUTPUT COMPARE REGISTER MAP

| SFR<br>Name | Addr. | Bit 15                                    | Bit 14                                                                                                       | Bit 13   | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8    | Bit 7      | Bit 6        | Bit 5  | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|-------|----------|------------|--------------|--------|----------|----------|----------|----------|----------|---------------|

| OC1CON1     | 0900  | _                                         | —                                                                                                            | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     | —        | ENFLTA     | _            | —      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC1CON2     | 0902  | FLTMD                                     | TMD FLTOUT FLTTRIEN OCINV — — — OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 SYNCSEL1 SYNCSEL0 000 |          |         |         |         |       |          |            |              |        | 000C     |          |          |          |          |               |

| OC1RS       | 0904  |                                           | Output Compare 1 Secondary Register                                                                          |          |         |         |         |       |          |            |              |        | xxxx     |          |          |          |          |               |

| OC1R        | 0906  |                                           |                                                                                                              |          |         |         |         |       | Outpu    | ut Compare | e 1 Register |        |          |          |          |          |          | xxxx          |

| OC1TMR      | 0908  |                                           |                                                                                                              |          |         |         |         | Out   | put Com  | pare 1 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC2CON1     | 090A  | _                                         | —                                                                                                            | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC2CON2     | 090C  | FLTMD                                     | FLTOUT                                                                                                       | FLTTRIEN | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC2RS       | 090E  |                                           |                                                                                                              |          |         |         |         | Ou    | tput Con | npare 2 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC2R        | 0910  |                                           | Output Compare 2 Register                                                                                    |          |         |         |         |       |          |            |              | xxxx   |          |          |          |          |          |               |

| OC2TMR      | 0912  |                                           |                                                                                                              |          |         |         |         | Out   | put Com  | pare 2 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC3CON1     | 0914  | _                                         | —                                                                                                            | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC3CON2     | 0916  | FLTMD                                     | FLTOUT                                                                                                       | FLTTRIEN | OCINV   | _       |         | -     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC3RS       | 0918  |                                           |                                                                                                              |          |         |         |         | Ou    | tput Con | npare 3 Se | condary Re   | gister |          |          |          |          |          | xxxx          |

| OC3R        | 091A  |                                           |                                                                                                              |          |         |         |         |       | Outpu    | ut Compare | e 3 Register |        |          |          |          |          |          | xxxx          |

| OC3TMR      | 091C  |                                           |                                                                                                              |          |         |         |         | Out   | put Com  | pare 3 Tin | ner Value Re | gister |          |          |          |          |          | xxxx          |

| OC4CON1     | 091E  | _                                         | —                                                                                                            | OCSIDL   | OCTSEL2 | OCTSEL1 | OCTSEL0 | _     |          | ENFLTA     | _            | _      | OCFLTA   | TRIGMODE | OCM2     | OCM1     | OCM0     | 0000          |

| OC4CON2     | 0920  | FLTMD                                     | FLTOUT                                                                                                       | FLTTRIEN | OCINV   | _       | _       | _     | OC32     | OCTRIG     | TRIGSTAT     | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000C          |

| OC4RS       | 0922  |                                           |                                                                                                              |          |         |         |         | Ou    | tput Con | npare 4 Se | condary Reg  | gister |          |          |          |          |          | xxxx          |

| OC4R        | 0924  | Output Compare 4 Register x2              |                                                                                                              |          |         |         |         |       |          |            | xxxx         |        |          |          |          |          |          |               |

| OC4TMR      | 0926  | Output Compare 4 Timer Value Register xxx |                                                                                                              |          |         |         |         |       |          | xxxx       |              |        |          |          |          |          |          |               |

| Logondu     |       |                                           |                                                                                                              |          |         |         |         |       |          |            | <i>.</i>     |        |          |          |          |          |          |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

The address boundaries check for addresses less than or greater than the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

| Note: | The modulo corrected Effective Address    |

|-------|-------------------------------------------|

|       | is written back to the register only when |

|       | Pre-Modify or Post-Modify Addressing      |

|       | mode is used to compute the Effective     |

|       | Address. When an address offset, such as  |

|       | [W7 + W2] is used, Modulo Addressing      |

|       | correction is performed, but the contents |

|       | of the register remain unchanged.         |

# 4.6 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.6.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all of these conditions are met:

- BWM<3:0> bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word-sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed        |

|-------|-------------------------------------------|

|       | Addressing can be enabled simultaneously  |

|       | using the same W register, but Bit-       |

|       | Reversed Addressing operation will always |

|       | take precedence for data writes when      |

|       | enabled.                                  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

The operation of Bit-Reversed Addressing is shown in Figure 4-16 and Table 4-46.

#### REGISTER 5-2: NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER

| U-0              | U-0   | U-0              | U-0    | U-0          | U-0             | U-0    | U-0   |

|------------------|-------|------------------|--------|--------------|-----------------|--------|-------|

| —                |       | —                | _      | —            | —               |        | —     |

| bit 15           |       | · · ·            |        |              |                 |        | bit 8 |

|                  |       |                  |        |              |                 |        |       |

| R/W-x            | R/W-x | R/W-x            | R/W-x  | R/W-x        | R/W-x           | R/W-x  | R/W-x |

|                  |       |                  | NVMADF | RU<23:16>    |                 |        |       |

| bit 7            |       |                  |        |              |                 |        | bit 0 |

|                  |       |                  |        |              |                 |        |       |

| Legend:          |       |                  |        |              |                 |        |       |

| R = Readable bit | ł     | W = Writable bit |        | U = Unimplem | ented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADRU<23:16>:** NVM Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

### REGISTER 5-3: NVMADR: NONVOLATILE MEMORY LOWER ADDRESS REGISTER

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|-------|-------|-------|----------------------------|--------------|-----------------------------------------|-----------------------------------------------|

|       |       | NVMAD | R<15:8>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 8                                         |

| R/W-x | R/W-x | R/W-x | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x                                         |

|       |       | NVMAD | )R<7:0>                    |              |                                         |                                               |

|       |       |       |                            |              |                                         | bit 0                                         |

|       |       |       | NVMAD<br>R/W-x R/W-x R/W-x | NVMADR<15:8> | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x | NVMADR<15:8><br>R/W-x R/W-x R/W-x R/W-x R/W-x |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0 NVMADR<15:0>: NVM Memory Lower Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written to by the user application.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 3 | ADDRERR: Address Error Trap Status bit             |

|-------|----------------------------------------------------|

|       | 1 = Address error trap has occurred                |

|       | 0 = Address error trap has not occurred            |

| bit 2 | STKERR: Stack Error Trap Status bit                |

|       | 1 = Stack error trap has occurred                  |

|       | 0 = Stack error trap has not occurred              |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit |

|       | 1 = Oscillator failure trap has occurred           |

|       | 0 = Oscillator failure trap has not occurred       |

| bit 0 | Unimplemented: Read as '0'                         |

| R/W-0         | R/W-0                                                         | R/W-0                               | R/W-0    | R/W-0            | U-0            | R/W-0               | U-0          |

|---------------|---------------------------------------------------------------|-------------------------------------|----------|------------------|----------------|---------------------|--------------|

| T5MD          | T4MD                                                          | T3MD                                | T2MD     | T1MD             | —              | PWMMD               | —            |

| bit 15        |                                                               |                                     |          |                  |                |                     | bit 8        |

| R/W-0         | R/W-0                                                         | R/W-0                               | R/W-0    | R/W-0            | U-0            | R/W-0               | R/W-0        |

| I2C1MD        |                                                               |                                     |          |                  | 0-0            | C1MD <sup>(1)</sup> |              |

| bit 7         | U2MD                                                          | U1MD                                | SPI2MD   | SPI1MD           | —              | CTMD                | AD1MD<br>bit |

|               |                                                               |                                     |          |                  |                |                     |              |

| Legend:       |                                                               |                                     |          |                  |                |                     |              |

| R = Readable  |                                                               | W = Writable                        |          | •                | mented bit, re | ad as '0'           |              |

| -n = Value at | POR                                                           | '1' = Bit is set                    |          | '0' = Bit is cle | ared           | x = Bit is unkn     | own          |

| bit 15        | T5MD: Timer                                                   | 5 Module Disal                      | ole bit  |                  |                |                     |              |

|               |                                                               | odule is disable<br>odule is enable |          |                  |                |                     |              |

| bit 14        | T4MD: Timer                                                   | 4 Module Disal                      | ole bit  |                  |                |                     |              |

|               | 1 = Timer4 m                                                  | odule is disable                    | ed       |                  |                |                     |              |

| bit 13        |                                                               | 3 Module Disal                      |          |                  |                |                     |              |

|               | 1 = Timer3 module is disabled<br>0 = Timer3 module is enabled |                                     |          |                  |                |                     |              |

| bit 12        | <b>T2MD:</b> Timer2 Module Disable bit                        |                                     |          |                  |                |                     |              |

|               | 1 = Timer2 module is disabled<br>0 = Timer2 module is enabled |                                     |          |                  |                |                     |              |

| bit 11        | <b>T1MD:</b> Timer1 Module Disable bit                        |                                     |          |                  |                |                     |              |

|               | -                                                             | odule is disable<br>odule is enable |          |                  |                |                     |              |

| bit 10        | Unimplemen                                                    | ted: Read as '                      | 0'       |                  |                |                     |              |

| bit 9         | PWMMD: PW                                                     | /M Module Dis                       | able bit |                  |                |                     |              |

|               |                                                               | dule is disabled<br>dule is enabled |          |                  |                |                     |              |

| bit 8         | Unimplemen                                                    | ted: Read as '                      | 0'       |                  |                |                     |              |

| bit 7         | 12C1MD: 12C                                                   | 1 Module Disal                      | ole bit  |                  |                |                     |              |

|               |                                                               | lule is disabled<br>lule is enabled |          |                  |                |                     |              |

| bit 6         | U2MD: UART2 Module Disable bit                                |                                     |          |                  |                |                     |              |

|               | 1 = UART2 module is disabled<br>0 = UART2 module is enabled   |                                     |          |                  |                |                     |              |

| bit 5         | <b>U1MD:</b> UART1 Module Disable bit                         |                                     |          |                  |                |                     |              |

|               | 1 = UART1 module is disabled<br>0 = UART1 module is enabled   |                                     |          |                  |                |                     |              |

| bit 4         | SPI2MD: SPI                                                   | 2 Module Disa                       | ole bit  |                  |                |                     |              |

|               |                                                               | lule is disabled<br>lule is enabled |          |                  |                |                     |              |

| bit 3         | SPI1MD: SPI                                                   | 1 Module Disa                       | ole bit  |                  |                |                     |              |

|               |                                                               | dule is disabled<br>dule is enabled |          |                  |                |                     |              |

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** This bit is available on dsPIC33EVXXXGM10X devices only.

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| —       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | T2CK  | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | <b>d as</b> '0'    |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **T2CKR<7:0>:** Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

• 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

# 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

These modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 and Timer4/5 operate in the following three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules

- ADC1 Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. The T3CON and T5CON registers are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw). Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, the T3CON and T5CON control bits are ignored. Only the T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

Block diagrams for the Type B and Type C timers are shown in Figure 13-1 and Figure 13-2, respectively.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

Note: Only Timer2, Timer3, Timer4 and Timer5 can trigger a DMA data transfer.

# REGISTER 17-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1

SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to the PWMxL pin; PWMxL output signal is connected to the PWMxH pin

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0

OSYNC: Output Override Synchronization bit

1 = Output overrides through the OVRDAT<1:0> bits are synchronized to the PWMx time base

0 = Output overrides through the OVRDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FDEVOPT<0>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

#### REGISTER 17-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|--------------|-------|------------------|-------|--------------|------------------|-----------------|-------|

|              |       |                  | TRGCI | MP<15:8>     |                  |                 |       |

| bit 15       |       |                  |       |              |                  |                 | bit 8 |

|              |       |                  |       |              |                  |                 |       |

| R/W-0        | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0            | R/W-0           | R/W-0 |

|              |       |                  | TRGC  | MP<7:0>      |                  |                 |       |

| bit 7        |       |                  |       |              |                  |                 | bit 0 |

|              |       |                  |       |              |                  |                 |       |

| Legend:      |       |                  |       |              |                  |                 |       |

| R = Readable | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | <b>d as</b> '0' |       |

|              |       |                  |       |              |                  |                 |       |

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

'1' = Bit is set

When the primary PWMx functions in the local time base, this register contains the compare values that can trigger the ADC module.

'0' = Bit is cleared

-n = Value at POR

x = Bit is unknown

| R/W-0         | R/W-0                                                                                                                                                   | R/W-0                               | U-0      | U-0              | U-0             | U-0             | U-0   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------|------------------|-----------------|-----------------|-------|

| DMABS2        | DMABS1                                                                                                                                                  | DMABS0                              | _        | —                | _               | _               | —     |

| pit 15        |                                                                                                                                                         |                                     |          |                  |                 |                 | bit 8 |

|               |                                                                                                                                                         |                                     |          |                  |                 |                 |       |

| U-0           | U-0                                                                                                                                                     | R/W-0                               | R/W-0    | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|               |                                                                                                                                                         | FSA5                                | FSA4     | FSA3             | FSA2            | FSA1            | FSA0  |

| oit 7         |                                                                                                                                                         |                                     |          |                  |                 |                 | bit ( |

| Legend:       |                                                                                                                                                         |                                     |          |                  |                 |                 |       |

| R = Readable  | e bit                                                                                                                                                   | W = Writable t                      | oit      | U = Unimplen     | nented bit, rea | id as '0'       |       |

| -n = Value at | POR                                                                                                                                                     | '1' = Bit is set                    |          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 12-6      | <pre>101 = 24 buffers in RAM 100 = 16 buffers in RAM 011 = 12 buffers in RAM 010 = 8 buffers in RAM 001 = 6 buffers in RAM 000 = 4 buffers in RAM</pre> |                                     |          |                  |                 |                 |       |

| bit 5-0       | -                                                                                                                                                       | ited: Read as '0<br>IFO Area Starts |          | oits             |                 |                 |       |

|               | 11111 = Rec                                                                                                                                             | eive Buffer RB3<br>eive Buffer RB3  | 31<br>30 |                  |                 |                 |       |

# REGISTER 22-4: CxFCTRL: CANx FIFO CONTROL REGISTER

### REGISTER 22-20: CxRXMnSID: CANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER REGISTER (n = 0-2)

|                                   |                                          | •                                                                                                                                                                        | •                                    |               |                                                            |                 |                |  |

|-----------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|------------------------------------------------------------|-----------------|----------------|--|

| R/W-x                             | R/W-x                                    | R/W-x                                                                                                                                                                    | R/W-x                                | R/W-x         | R/W-x                                                      | R/W-x           | R/W-x          |  |

| SID10                             | SID9                                     | SID8                                                                                                                                                                     | SID7                                 | SID6          | SID5                                                       | SID4            | SID3           |  |

| bit 15                            |                                          |                                                                                                                                                                          |                                      |               | •                                                          |                 | bit 8          |  |

| R/W-x                             | R/W-x                                    | R/W-x                                                                                                                                                                    | U-0                                  | R/W-x         | U-0                                                        | R/W-x           | R/W-x          |  |

| SID2                              | SID1                                     | SID0                                                                                                                                                                     | _                                    | MIDE          | _                                                          | EID17           | EID16          |  |

| bit 7                             |                                          |                                                                                                                                                                          |                                      |               |                                                            |                 | bit C          |  |

|                                   |                                          |                                                                                                                                                                          |                                      |               |                                                            |                 |                |  |

| Legend:                           |                                          |                                                                                                                                                                          |                                      |               |                                                            |                 |                |  |

| R = Readable bit W = Writable bit |                                          |                                                                                                                                                                          |                                      | U = Unimple   | mented bit, read                                           | <b>d as</b> '0' |                |  |

| -n = Value at                     | POR                                      | '1' = Bit is set                                                                                                                                                         | et '0' = Bit is cleared x = Bit is u |               |                                                            |                 | Iown           |  |

| bit 15-5<br>bit 4                 | 1 = Includes<br>0 = Bit, SIDx,           | SID<10:0>: Standard Identifier bits<br>1 = Includes bit, SIDx, in filter comparison<br>0 = Bit, SIDx, is a don't care in filter comparison<br>Unimplemented: Read as '0' |                                      |               |                                                            |                 |                |  |

| bit 3                             | 1 = Matches<br>the filter<br>0 = Matches | either standard                                                                                                                                                          | types (standa                        | address messa | address) that c<br>ge if filters match<br>/lessage SID/EII | n, i.e., if:    | e EXIDE bit ir |  |

| bit 2                             | Unimplemer                               | nted: Read as                                                                                                                                                            | 0'                                   |               |                                                            |                 |                |  |

| bit 1-0                           | 1 = Includes                             | EID<17:16>: Extended Identifier bits<br>1 = Includes bit, EIDx, in filter comparison<br>0 = Bit, EIDx, is a don't care in filter comparison                              |                                      |               |                                                            |                 |                |  |

|                                   |                                          |                                                                                                                                                                          |                                      |               |                                                            |                 |                |  |

## REGISTER 22-21: CxRXMnEID: CANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x                             | R/W-x                                                      | R/W-x | R/W-x           | R/W-x           | R/W-x           | R/W-x | R/W-x |

|-----------------------------------|------------------------------------------------------------|-------|-----------------|-----------------|-----------------|-------|-------|

|                                   |                                                            |       | EID             | <15:8>          |                 |       |       |

| bit 15                            |                                                            |       |                 |                 |                 |       | bit 8 |

| R/W-x                             | R/W-x                                                      | R/W-x | R/W-x           | R/W-x           | R/W-x           | R/W-x | R/W-x |

|                                   |                                                            |       | EID             | <7:0>           |                 |       |       |

| bit 7                             |                                                            |       |                 |                 |                 |       | bit 0 |

| Legend:                           |                                                            |       |                 |                 |                 |       |       |

| R = Readable bit W = Writable bit |                                                            | bit   | U = Unimpler    | nented bit, rea | <b>d as</b> '0' |       |       |

| -n = Value at P                   | Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit |       | x = Bit is unkr | nown            |                 |       |       |

bit 15-0

- EID<15:0>: Extended Identifier bits

- 1 = Includes bit, EIDx, in filter comparison

- 0 = Bit, EIDx, is a don't care in filter comparison

# dsPIC33EVXXXGM00X/10X FAMILY

| R/W-x                              | R/W-x               | R/W-x                              | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|------------------------------------|---------------------|------------------------------------|---------------|------------------------------------|-------|-----------------|-------|--|

| EID5                               | EID4                | EID3                               | EID2          | EID1                               | EID0  | RTR             | RB1   |  |

| bit 15                             |                     |                                    |               |                                    |       |                 | bit 8 |  |

|                                    |                     |                                    | D////         |                                    | D///  | D///            |       |  |

| U-x                                | U-x                 | U-x                                | R/W-x         | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

| _                                  |                     | —                                  | RB0           | DLC3                               | DLC2  | DLC1            | DLC0  |  |

| bit 7                              |                     |                                    |               |                                    |       |                 | bit ( |  |

| Legend:                            |                     |                                    |               |                                    |       |                 |       |  |

| R = Readab                         | le bit              | W = Writable                       | bit           | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1' = Bit is set |                     |                                    | t             | '0' = Bit is cle                   |       | x = Bit is unkr | nown  |  |

|                                    |                     |                                    |               |                                    |       |                 |       |  |

| bit 15-10                          | EID<5:0>: E>        | EID<5:0>: Extended Identifier bits |               |                                    |       |                 |       |  |

| bit 9                              | RTR: Remote         | e Transmission                     | Request bit   |                                    |       |                 |       |  |

|                                    | When IDE =          |                                    |               |                                    |       |                 |       |  |

|                                    | -                   | will request re                    | mote transmi  | ssion                              |       |                 |       |  |

|                                    | 0 = Normal m        | 0                                  |               |                                    |       |                 |       |  |

|                                    | When IDE =          |                                    |               |                                    |       |                 |       |  |

|                                    | The RTR bit i       | -                                  |               |                                    |       |                 |       |  |

| bit 8                              | RB1: Reserved Bit 1 |                                    |               |                                    |       |                 |       |  |

|                                    |                     | et this bit to '0' p               | -             | ocol.                              |       |                 |       |  |

| bit 7-5                            | Unimplemer          | nted: Read as '                    | 0'            |                                    |       |                 |       |  |

| bit 4                              | RB0: Reserv         | ed Bit 0                           |               |                                    |       |                 |       |  |

|                                    | User must se        | et this bit to '0' p               | per CAN proto | ocol.                              |       |                 |       |  |

|                                    |                     |                                    |               |                                    |       |                 |       |  |

### BUFFER 22-3: CANx MESSAGE BUFFER WORD 2

| bit 3-0 | DLC<3:0>: Data Length Code bits |

|---------|---------------------------------|

|         |                                 |

## BUFFER 22-4: CANx MESSAGE BUFFER WORD 3

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

|-------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|--|--|

| Byte 1<15:8>      |       |                  |       |                                    |       |                    |       |  |  |  |  |

| bit 15            |       |                  |       |                                    |       |                    | bit 8 |  |  |  |  |

|                   |       |                  |       |                                    |       |                    |       |  |  |  |  |

| R/W-x             | R/W-x | R/W-x            | R/W-x | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |  |

| Byte 0<7:0>       |       |                  |       |                                    |       |                    |       |  |  |  |  |

| bit 7             |       |                  |       |                                    |       |                    | bit 0 |  |  |  |  |

|                   |       |                  |       |                                    |       |                    |       |  |  |  |  |

| Legend:           |       |                  |       |                                    |       |                    |       |  |  |  |  |

| R = Readable bit  |       | W = Writable bit |       | U = Unimplemented bit, read as '0' |       |                    |       |  |  |  |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |  |  |  |

bit 15-8 Byte 1<15:8>: CANx Message Byte 1 bits

bit 7-0 Byte 0<7:0>: CANx Message Byte 0 bits

# 27.2 User OTP Memory

Locations, 800F80h-800FFEh, are a One-Time-Programmable (OTP) memory area. The user OTP words can be used for storing product information, such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

# 27.3 On-Chip Voltage Regulator

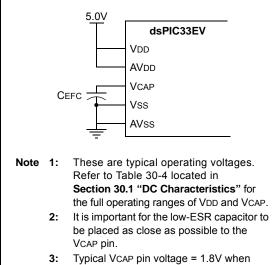

All of the dsPIC33EVXXXGM00X/10X family devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 5.0V. To simplify system design, all devices in the dsPIC33EVXXXGM00X/10X family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5, located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

3: Typical VCAP pin voltage = 1.8V when VDD ≥ VDDMIN.

# 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).