Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm003-i-m5 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

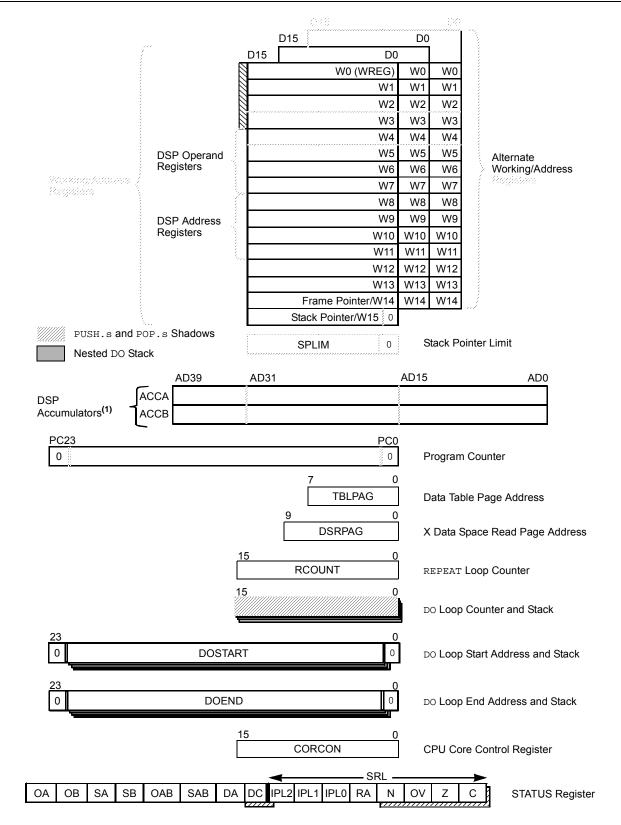

#### 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

#### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

## 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

#### FIGURE 3-2: PROGRAMMER'S MODEL

| Informent Course                           | Vector  | tor IRQ |                        | Interrupt Bit Location |           |              |  |

|--------------------------------------------|---------|---------|------------------------|------------------------|-----------|--------------|--|

| Interrupt Source                           | No. No. |         | IVT Address            | Flag                   | Enable    | Priority     |  |

| UART1 Error Interrupt (U1E)                | 73      | 65      | 0x000096               | IFS4<1>                | IEC4<1>   | IPC16<6:4>   |  |

| UART2 Error Interrupt (U2E)                | 74      | 66      | 0x000098               | IFS4<2>                | IEC4<2>   | IPC16<10:8>  |  |

| Reserved                                   | 76-77   | 68–69   | 0x00009C-0x00009E      | _                      | —         | _            |  |

| CAN1 TX Data Request (C1TX) <sup>(1)</sup> | 78      | 70      | 0x0000A0               | IFS4<6>                | IEC4<6>   | IPC17<10:8>  |  |

| Reserved                                   | 80      | 72      | 0x0000A4               | _                      | —         | _            |  |

| Reserved                                   | 82      | 74      | 0x0000A8               | _                      | _         | _            |  |

| Reserved                                   | 84      | 76      | 0x0000AC               | _                      | _         | _            |  |

| CTMU Interrupt (CTMU)                      | 85      | 77      | 0x0000AE               | IFS4<13>               | IEC4<13>  | IPC19<6:4>   |  |

| Reserved                                   | 86-88   | 78-80   | 0x0000B0-0x0000B4      | _                      | —         | —            |  |

| Reserved                                   | 92-94   | 84-86   | 0x0000BC-0x0000C0      | _                      | —         | —            |  |

| Reserved                                   | 100-101 | 92-93   | 0x0000CC-0x0000CE      | _                      | _         |              |  |

| PWM Generator 1 (PWM1)                     | 102     | 94      | 0x0000D0               | IFS5<14>               | IEC5<14>  | IPC23<10:8>  |  |

| PWM Generator 2 (PWM2)                     | 103     | 95      | 0x0000D2               | IFS5<15>               | IEC5<15>  | IPC23<14:12> |  |

| PWM Generator 3 (PWM3)                     | 104     | 96      | 0x0000D4               | IFS6<0>                | IEC6<0>   | IPC24<2:0>   |  |

| Reserved                                   | 108-149 | 100-141 | 0x0000DC-0x00012E      | _                      | —         | _            |  |

| ICD Application (ICD)                      | 150     | 142     | 0x000142               | IFS8<14>               | IEC8<14>  | IPC35<10:8>  |  |

| Reserved                                   | 152     | 144     | 0x000134               | _                      | —         | —            |  |

| Bus Collision (I2C1)                       | —       | 173     | 0x00016E               | IFS10<13>              | IEC10<13> | IPC43<4:6>   |  |

| SENT1 Error (SENT1ERR)                     | _       | 182     | 0x000180               | IFS11<6>               | IEC11<6>  | IPC45<10:8>  |  |

| SENT1 TX/RX (SENT1)                        | _       | 183     | 0x000182               | IFS11<7>               | IEC11<7>  | IPC45<14:12> |  |

| SENT2 Error (SENT2ERR)                     | _       | 184     | 0x000184               | IFS11<8>               | IEC11<8>  | IPC46<2:0>   |  |

| SENT2 TX/RX (SENT2)                        | _       | 185     | 0x000186               | IFS11<9>               | IEC11<9>  | IPC46<6:4>   |  |

| ECC Single-Bit Error (ECCSBE)              | —       | 186     | 0x000188               | IFS11<10>              | IEC11<10> | IPC45<10:8>  |  |

| Reserved                                   | 159-245 | 187-245 | 0x000142-0x0001FE      | _                      | _         | —            |  |

|                                            |         | Lowest  | Natural Order Priority |                        |           |              |  |

| TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTIN |

|---------------------------------------------|

|---------------------------------------------|

Note 1: This interrupt source is available on dsPIC33EVXXXGM10X devices only.

## **REGISTER 9-2:** CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

- **Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register resets only on a Power-on Reset (POR).

- **3:** DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 4: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the power-saving modes. In some circumstances, this may not be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation. For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode, with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

## **10.4** Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled, using the appropriate PMDx control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have any effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMDx register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMDx register by default.

Note: If a PMDx bit is set, the corresponding module is disabled after a delay of one instruction cycle. Similarly, if a PMDx bit is cleared, the corresponding module is enabled after a delay of one instruction cycle (assuming the module control registers are already configured to enable module operation).

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| —       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | T2CK  | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 **T2CKR<7:0>:** Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 •

• 00000001 = Input tied to CMP1 00000000 = Input tied to Vss

| U-0                 | U-0                                                                                                                     | U-0                                     | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|--|

|                     |                                                                                                                         |                                         | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |

| bit 15              |                                                                                                                         |                                         | Diocon               | DICCDO                                 | MODEIO               | Olin                 | bit                  |  |

|                     |                                                                                                                         |                                         |                      |                                        |                      |                      |                      |  |

| R/W-0               | R/W-0                                                                                                                   | R/W-0                                   | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                     | MSTEN                                   | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |

| bit 7               |                                                                                                                         |                                         |                      | 1                                      |                      |                      | bit                  |  |

|                     |                                                                                                                         |                                         |                      |                                        |                      |                      |                      |  |

| Legend:             |                                                                                                                         |                                         |                      |                                        |                      |                      |                      |  |

| R = Readab          | le bit                                                                                                                  | W = Writable                            | bit                  | U = Unimplen                           | nented bit, read     | <b>l as</b> '0'      |                      |  |

| -n = Value a        | t POR                                                                                                                   | '1' = Bit is set                        |                      | '0' = Bit is clea                      | ared                 | x = Bit is unkr      | nown                 |  |

|                     |                                                                                                                         |                                         | _ 1                  |                                        |                      |                      |                      |  |

| bit 15-13           | -                                                                                                                       | ted: Read as '                          |                      |                                        |                      |                      |                      |  |

| bit 12              | <b>DISSCK:</b> Disable SCKx Pin bit (SPI Master modes only)<br>1 = Internal SPI clock is disabled, pin functions as I/O |                                         |                      |                                        |                      |                      |                      |  |

|                     |                                                                                                                         | PI clock is disa<br>PI clock is ena     |                      | ao 1/U                                 |                      |                      |                      |  |

| bit 11              | DISSDO: Disable SDOx Pin bit                                                                                            |                                         |                      |                                        |                      |                      |                      |  |

|                     | 1 = SDOx pin is not used by the module; pin functions as I/O                                                            |                                         |                      |                                        |                      |                      |                      |  |

|                     |                                                                                                                         | is controlled b                         |                      |                                        |                      |                      |                      |  |

| bit 10              | MODE16: Wo                                                                                                              | ord/Byte Comm                           | unication Sele       | ect bit                                |                      |                      |                      |  |

|                     | 1 = Communication is word-wide (16 bits)                                                                                |                                         |                      |                                        |                      |                      |                      |  |

|                     |                                                                                                                         | 0 = Communication is byte-wide (8 bits) |                      |                                        |                      |                      |                      |  |

| bit 9               |                                                                                                                         | ata Input Samp                          | ole Phase bit        |                                        |                      |                      |                      |  |

|                     | Master mode:                                                                                                            | :<br>a is sampled at                    | the end of da        | ta output time                         |                      |                      |                      |  |

|                     |                                                                                                                         |                                         |                      | data output time                       | ie                   |                      |                      |  |

|                     | Slave mode:                                                                                                             | -                                       |                      | n Slave mode.                          |                      |                      |                      |  |

| bit 8               | CKE: Clock E                                                                                                            | dge Select bit                          | 1)                   |                                        |                      |                      |                      |  |

|                     |                                                                                                                         |                                         |                      |                                        | clock state to Id    |                      |                      |  |

| bit 7               | SSEN: Slave                                                                                                             | Select Enable                           | bit (Slave mo        | de) <sup>(2)</sup>                     |                      |                      |                      |  |

|                     |                                                                                                                         | s used for Slav                         |                      |                                        |                      |                      |                      |  |

|                     | 0 = SSx pin is                                                                                                          | s not used by the                       | ne module; pir       | n is controlled b                      | y port function      |                      |                      |  |

| bit 6               |                                                                                                                         | olarity Select I                        |                      |                                        |                      |                      |                      |  |

|                     |                                                                                                                         |                                         |                      | ve state is a low<br>e state is a high |                      |                      |                      |  |

| bit 5               | MSTEN: Mas                                                                                                              | ter Mode Enab                           | le bit               |                                        |                      |                      |                      |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                            |                                         |                      |                                        |                      |                      |                      |  |

|                     | he CKE bit is not<br>FRMEN = 1).                                                                                        | used in Frame                           | d SPI modes.         | Program this b                         | oit to '0' for Frai  | med SPI modes        | S                    |  |

| -                   | his bit must be cl                                                                                                      | eared when FF                           | RMEN = 1.            |                                        |                      |                      |                      |  |

|                     | o not set both pri                                                                                                      |                                         |                      | ers to the value                       | e of 1:1.            |                      |                      |  |

#### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

**3:** Do not set both primary and secondary prescalers to the value of 1:1.

## REGISTER 22-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

| R/W-0             | R/W-0                | R/W-0                                                                                | R/W-0            | R/W-0                              | R/W-0                         | R/W-0  | R/W-0              |  |

|-------------------|----------------------|--------------------------------------------------------------------------------------|------------------|------------------------------------|-------------------------------|--------|--------------------|--|

| F11BP3            | F11BP2               | F11BP1                                                                               | F11BP0           | F10BP3                             | F10BP2                        | F10BP1 | F10BP0             |  |

| bit 15            |                      |                                                                                      |                  |                                    |                               |        | bit 8              |  |

|                   |                      |                                                                                      |                  |                                    |                               |        |                    |  |

| R/W-0             | R/W-0                | R/W-0                                                                                | R/W-0            | R/W-0                              | R/W-0                         | R/W-0  | R/W-0              |  |

| F9BP3             | F9BP2                | F9BP1                                                                                | F9BP0            | F8BP3                              | F8BP2                         | F8BP1  | F8BP0              |  |

| bit 7             |                      |                                                                                      |                  |                                    |                               | •      | bit 0              |  |

|                   |                      |                                                                                      |                  |                                    |                               |        |                    |  |

| Legend:           |                      |                                                                                      |                  |                                    |                               |        |                    |  |

| R = Readable bit  |                      | W = Writable bit                                                                     |                  | U = Unimplemented bit, read as '0' |                               |        |                    |  |

| -n = Value at POR |                      | '1' = Bit is set                                                                     | '1' = Bit is set |                                    | '0' = Bit is cleared          |        | x = Bit is unknown |  |

|                   |                      |                                                                                      |                  |                                    |                               |        |                    |  |

| bit 15-12         | F11BP<3:0>:          | RX Buffer Mas                                                                        | sk for Filter 11 | bits                               |                               |        |                    |  |

|                   |                      | hits received in                                                                     |                  |                                    |                               |        |                    |  |

|                   | 1110 <b>= Filter</b> | hits received in                                                                     | RX Buffer 14     | ł                                  |                               |        |                    |  |

|                   | •                    |                                                                                      |                  |                                    |                               |        |                    |  |

|                   | •                    |                                                                                      |                  |                                    |                               |        |                    |  |

|                   | 0001 = Filter        | hits received in                                                                     | RX Buffer 1      |                                    |                               |        |                    |  |

|                   | 0000 = Filter        | hits received in                                                                     | NRX Buffer 0     |                                    |                               |        |                    |  |

| bit 11-8          | F10BP<3:0>           | RX Buffer Ma                                                                         | sk for Filter 10 | ) bits (same va                    | lues as bits 15- <sup>,</sup> | 12)    |                    |  |

| bit 7-4           | F9BP<3:0>:           | RX Buffer Masl                                                                       | c for Filter 9 b | its (same value                    | es as bits 15-12)             | )      |                    |  |

| bit 3-0           | F8BP<3:0>:           | <b>F8BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 8 bits (same values as bits 15-12) |                  |                                    |                               |        |                    |  |

|                   |                      |                                                                                      |                  |                                    |                               |        |                    |  |

## REGISTER 22-22: CxRXFUL1: CANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0                                                                | R/C-0 | R/C-0            | R/C-0            | R/C-0                                   | R/C-0 | R/C-0 | R/C-0 |  |

|----------------------------------------------------------------------|-------|------------------|------------------|-----------------------------------------|-------|-------|-------|--|

|                                                                      |       |                  | RXFU             | L<15:8>                                 |       |       |       |  |

| bit 15                                                               |       |                  |                  |                                         |       |       | bit 8 |  |

|                                                                      |       |                  |                  |                                         |       |       |       |  |

| R/C-0                                                                | R/C-0 | R/C-0            | R/C-0            | R/C-0                                   | R/C-0 | R/C-0 | R/C-0 |  |

|                                                                      |       |                  | RXFL             | JL<7:0>                                 |       |       |       |  |

| bit 7                                                                |       |                  |                  |                                         |       |       | bit 0 |  |

|                                                                      |       |                  |                  |                                         |       |       |       |  |

| Legend: C = Writable bit, but only                                   |       |                  | oit, but only '( | ly '0' can be written to clear the bit  |       |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |                  |                                         |       |       |       |  |

| -n = Value at F                                                      | POR   | '1' = Bit is set |                  | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 RXFUL<15:0>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 22-23: CxRXFUL2: CANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0                             | R/C-0                                                                      | R/C-0          | R/C-0           | R/C-0                              | R/C-0          | R/C-0 | R/C-0 |

|-----------------------------------|----------------------------------------------------------------------------|----------------|-----------------|------------------------------------|----------------|-------|-------|

|                                   |                                                                            |                | RXFU            | _<31:24>                           |                |       |       |

| bit 15                            |                                                                            |                |                 |                                    |                |       | bit 8 |

|                                   |                                                                            |                |                 |                                    |                |       |       |

| R/C-0                             | R/C-0                                                                      | R/C-0          | R/C-0           | R/C-0                              | R/C-0          | R/C-0 | R/C-0 |

|                                   |                                                                            |                | RXFU            | _<23:16>                           |                |       |       |

| bit 7                             |                                                                            |                |                 |                                    |                |       | bit 0 |

|                                   |                                                                            |                |                 |                                    |                |       |       |

| Legend: C = Writable bit, but onl |                                                                            |                | it, but only '( | )' can be written                  | to clear the b | bit   |       |

| R = Readable                      | bit                                                                        | W = Writable b | bit             | U = Unimplemented bit, read as '0' |                |       |       |

| -n = Value at F                   | -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                |                 |                                    |                | nown  |       |

bit 15-0 RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

| R/W-0                                                   | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|---------------------------------------------------------|-------|-------|------------------------------------|--------|-------|-------|-------|

|                                                         |       |       | CSS                                | <15:8> |       |       |       |

| bit 15                                                  |       |       |                                    |        |       |       | bit 8 |

| R/W-0                                                   | R/W-0 | R/W-0 | R/W-0                              | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|                                                         |       |       | CSS                                | <7:0>  |       |       |       |

| bit 7                                                   |       |       |                                    |        |       |       | bit C |

| Legend:                                                 |       |       |                                    |        |       |       |       |

| R = Readable bit W = Writable bit                       |       | oit   | U = Unimplemented bit, read as '0' |        |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |       | ared  | x = Bit is unk                     | nown   |       |       |       |

bit 15-0 CSS<15:0>: ADCx Input Scan Selection bits

1 = Selects ANx for input scan

0 = Skips ANx for input scan

**Note 1:** On devices with less than 16 analog inputs, all bits in this register can be selected by the user application. However, inputs selected for scan without a corresponding input on the device convert VREFL.

**2:** CSSx = ANx, where 'x' = 0-5.

## 27.2 User OTP Memory

Locations, 800F80h-800FFEh, are a One-Time-Programmable (OTP) memory area. The user OTP words can be used for storing product information, such as serial numbers, system manufacturing dates, manufacturing lot numbers and other application-specific information.

## 27.3 On-Chip Voltage Regulator

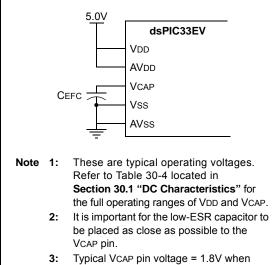

All of the dsPIC33EVXXXGM00X/10X family devices power their core digital logic at a nominal 1.8V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 5.0V. To simplify system design, all devices in the dsPIC33EVXXXGM00X/10X family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. A low-ESR (less than 1 Ohm) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (see Figure 27-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 30-5, located in **Section 30.0 "Electrical Characteristics"**.

Note: It is important for the low-ESR capacitor to be placed as close as possible to the VCAP pin.

#### FIGURE 27-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### Typical VCAP pin voltage = 1.8V when VDD ≥ VDDMIN.

#### 27.4 Brown-out Reset (BOR)

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated supply voltage, VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the Power-up Timer (PWRT) Time-out (TPWRT) is applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM is applied. The total delay in this case is TFSCM. Refer to Parameter SY35 in Table 30-22 of **Section 30.0 "Electrical Characteristics"** for specific TFSCM values.

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle mode and resets the device should VDD fall below the BOR threshold voltage.

| TABLE 30-10: | DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS |

|--------------|--------------------------------------------------|

|--------------|--------------------------------------------------|

| DC CHARACTERISTICS |        |                                                                       | Standard Ope<br>(unless other<br>Operating tem | onditions: 4.5V to 5.5V<br>ed)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |       |                                                                                                                                        |

|--------------------|--------|-----------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                        | Min.                                           | Тур. <sup>(1)</sup>                                                                                                                             | Max.                | Units | Conditions                                                                                                                             |

|                    | VIL    | Input Low Voltage                                                     |                                                |                                                                                                                                                 |                     |       |                                                                                                                                        |

| DI10               |        | I/O Pins                                                              | Vss                                            |                                                                                                                                                 | 0.2 Vdd             | V     |                                                                                                                                        |

|                    | Vih    | Input High Voltage                                                    |                                                |                                                                                                                                                 |                     |       |                                                                                                                                        |

| DI20               |        | I/O Pins                                                              | 0.75 VDD                                       |                                                                                                                                                 | 5.5                 | V     |                                                                                                                                        |

| DI30               | ICNPU  | Change Notification Pull-up<br>Current                                | 200                                            | 375                                                                                                                                             | 600                 | μA    | VDD = 5.0V, VPIN = VSS                                                                                                                 |

| DI31               | ICNPD  | Change Notification<br>Pull-Down Current <sup>(7)</sup>               | 175                                            | 400                                                                                                                                             | 625                 | μA    | VDD = 5.0V, VPIN = VDD                                                                                                                 |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                |                                                |                                                                                                                                                 |                     |       |                                                                                                                                        |

| DI50               |        | I/O Pins                                                              | -100                                           | -                                                                                                                                               | 100                 | nA    | $Vss \le VPIN \le VDD,$ pin at high-impedance                                                                                          |

| DI55               |        | MCLR                                                                  | -700                                           |                                                                                                                                                 | 700                 | nA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                               |

| DI56               |        | OSC1                                                                  | -200                                           | _                                                                                                                                               | 200                 | nA    | $\label{eq:VSS} \begin{split} &VSS \leq V PIN \leq V DD, \\ &XT \text{ and } HS \text{ modes} \end{split}$                             |

| Dl60a              | licl   | Input Low Injection Current                                           | 0                                              | _                                                                                                                                               | <sub>-5</sub> (4,6) |       | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR,<br>VCAP and RB7                                                                         |

| DI60b              | ІІСН   | Input High Injection Current                                          | 0                                              | —                                                                                                                                               | +5 <sup>(5,6)</sup> | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR,<br>VCAP, RB7 and all 5V<br>tolerant pins <sup>(5)</sup>                                 |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | <sub>-20</sub> (7)                             | _                                                                                                                                               | +20(7)              |       | Absolute instantaneous<br>sum of all $\pm$ input<br>injection currents from all<br>I/O pins<br>(   IICL  +   IICH   ) $\leq \sum$ IICT |

**Note 1:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

- 5: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 6: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 7: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted, provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

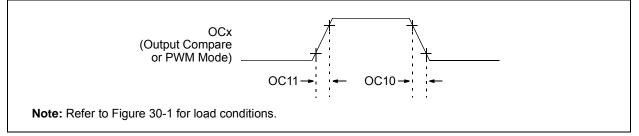

### FIGURE 30-8: OUTPUT COMPARE x (OCx) TIMING CHARACTERISTICS

#### TABLE 30-27: OUTPUT COMPARE x (OCx) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                    |  |

|--------------------|--------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                                                     | _    |      | ns    | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                                                     | _    | —    | ns    | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

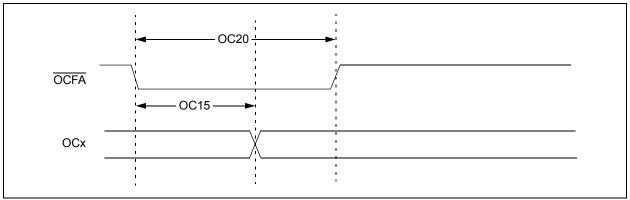

#### FIGURE 30-9: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |      |          |       |            |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                                                                                                                                                                                                                                              | Тур. | Max.     | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWMx I/O<br>Change | _                                                                                                                                                                                                                                                                                 | _    | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width           | Tcy + 20                                                                                                                                                                                                                                                                          |      | —        | ns    |            |

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 30-50: OP AMP/COMPARATOR x SPECIFICATIONS

| DC CHARACTERISTICS |                 |                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |              |       |                                                    |  |

|--------------------|-----------------|-------------------------------------------|------------------------------------------------------|---------------------|--------------|-------|----------------------------------------------------|--|

| Param<br>No.       | Symbol          | Characteristic                            | Min.                                                 | Тур. <sup>(1)</sup> | Max.         | Units | Conditions                                         |  |

|                    |                 | Con                                       | parator AC C                                         | haracte             | ristics      |       |                                                    |  |

| CM10               | Tresp           | Response Time                             | _                                                    | 19                  | 80           | ns    | V+ input step of 100 mV,<br>V- input held at VDD/2 |  |

| CM11               | TMC2OV          | Comparator Mode<br>Change to Output Valid | —                                                    | _                   | 10           | μs    |                                                    |  |

|                    |                 | Con                                       | nparator DC C                                        | haracte             | ristics      |       |                                                    |  |

| CM30               | VOFFSET         | Comparator Offset<br>Voltage              | -80                                                  | ±60                 | 80           | mV    |                                                    |  |

| CM31               | VHYST           | Input Hysteresis Voltage                  |                                                      | 30                  | —            | mV    |                                                    |  |

| CM32               | Trise/<br>Tfall | Comparator Output<br>Rise/Fall Time       | —                                                    | 20                  | —            | ns    | 1 pF load capacitance<br>on input                  |  |

| CM33               | Vgain           | Open-Loop Voltage Gain                    | —                                                    | 90                  | —            | db    |                                                    |  |

| CM34               | VICM            | Input Common-Mode<br>Voltage              | AVss                                                 | —                   | AVDD         | V     |                                                    |  |

|                    |                 | Or                                        | o Amp AC Cha                                         | aracteris           | stics        |       |                                                    |  |

| CM20               | SR              | Slew Rate                                 | _                                                    | 9                   | _            | V/µs  | 10 pF load                                         |  |

| CM21               | Рм              | Phase Margin                              | —                                                    | 35                  | —            | °C    | G = 100V/V, 10 pF load                             |  |

| CM22               | Gм              | Gain Margin                               | —                                                    | 20                  | —            | db    | G = 100V/V, 10 pF load                             |  |

| CM23               | GBW             | Gain Bandwidth                            | —                                                    | 10                  | —            | MHz   | 10 pF load                                         |  |

|                    |                 | Op                                        | o Amp DC Cha                                         | aracteris           | stics        |       |                                                    |  |

| CM40               | VCMR            | Common-Mode Input<br>Voltage Range        | AVss                                                 | —                   | AVDD         | V     |                                                    |  |

| CM41               | CMRR            | Common-Mode<br>Rejection Ratio            | —                                                    | 45                  | —            | db    | Vcm = AVdd/2                                       |  |

| CM42               | VOFFSET         | Op Amp Offset Voltage                     | -50                                                  | ±6                  | 50           | mV    |                                                    |  |

| CM43               | Vgain           | Open-Loop Voltage Gain                    | _                                                    | 90                  | —            | db    |                                                    |  |

| CM44               | los             | Input Offset Current                      | —                                                    | —                   | —            | _     | See pad leakage<br>currents in Table 30-10         |  |

| CM45               | lв              | Input Bias Current                        | _                                                    |                     | —            | _     | See pad leakage<br>currents in Table 30-10         |  |

| CM46               | Ιουτ            | Output Current                            | —                                                    | _                   | 420          | μA    | With minimum value of RFEEDBACK (CM48)             |  |

| CM48               | RFEEDBACK       | Feedback Resistance<br>Value              | 8                                                    |                     | —            | kΩ    | Note 2                                             |  |

| CM49a              | Vout            | Output Voltage                            | AVss + 0.075                                         | _                   | AVDD - 0.075 | V     | Ιουτ = 420 μΑ                                      |  |

Note 1: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: Resistances can vary by ±10% between op amps.

**3:** Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules: ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

© 2013-2016 Microchip Technology Inc.

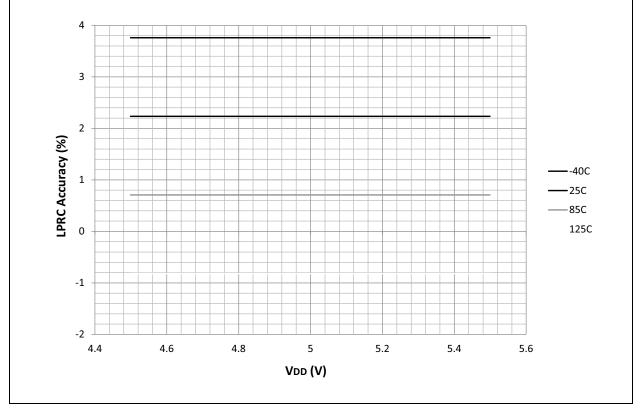

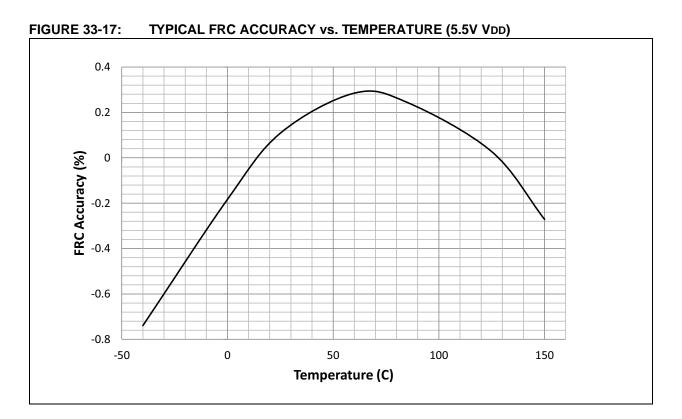

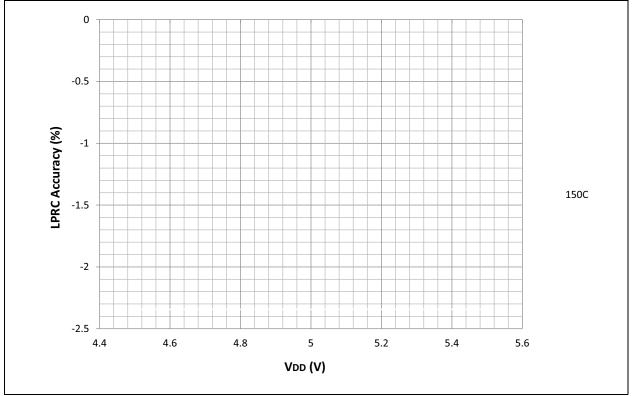

#### 32.6 LPRC

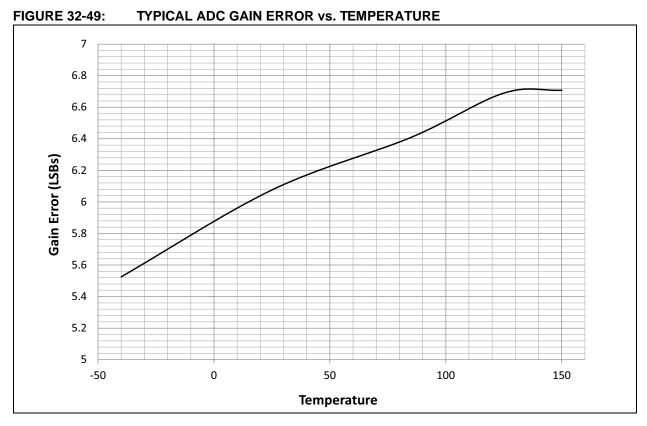

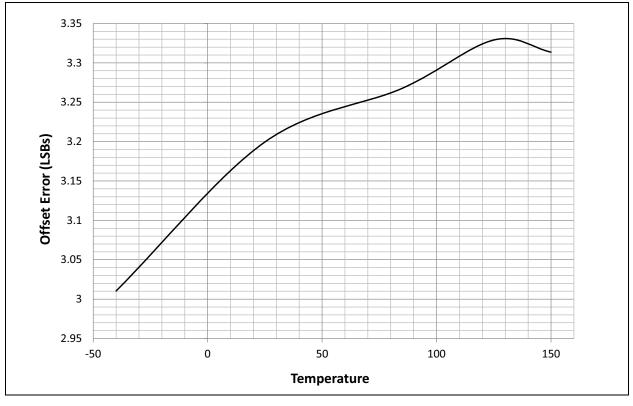

## 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

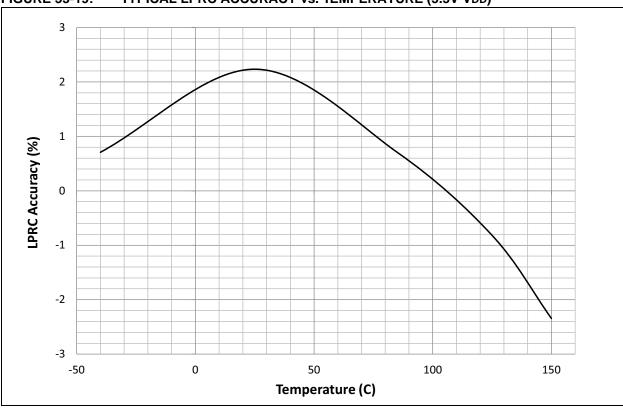

## FIGURE 33-19: TYPICAL LPRC ACCURACY vs. TEMPERATURE (5.5V VDD)

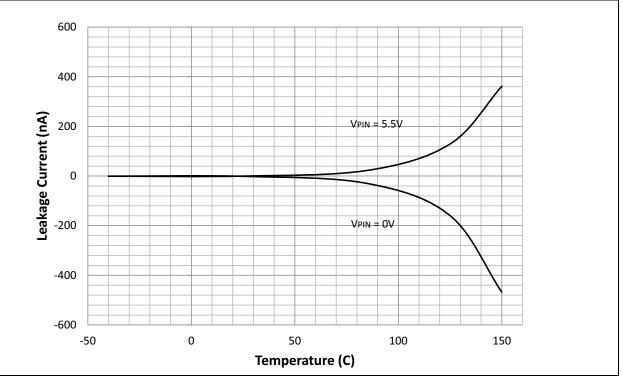

### 33.7 Leakage Current

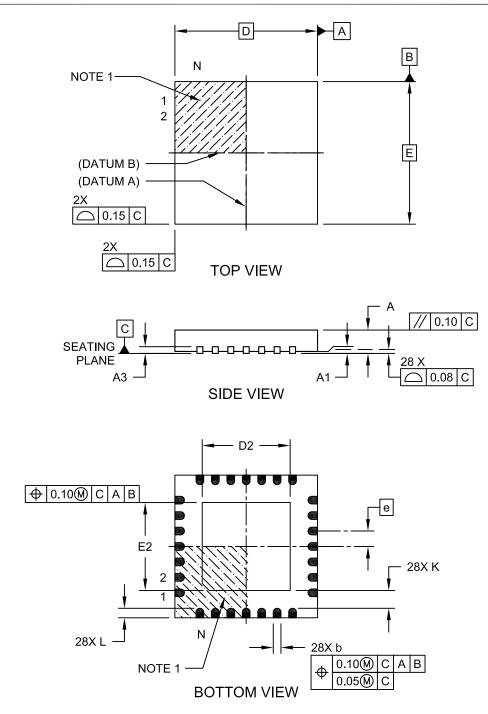

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2