Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 25                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

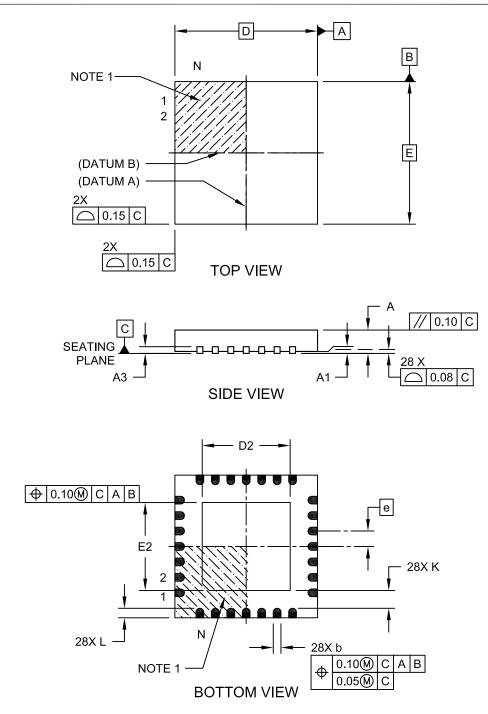

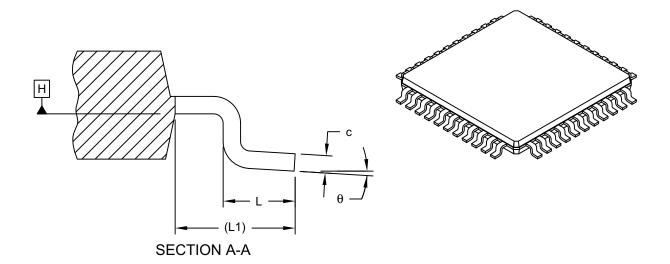

| Package / Case             | 36-UFQFN Exposed Pad                                                              |

| Supplier Device Package    | 36-UQFN (5x5)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm003t-i-m5 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not exceeding 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site (www.microchip.com).

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS51765)

- *"MPLAB<sup>®</sup> ICD 3 Design Advisory"* (DS51764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

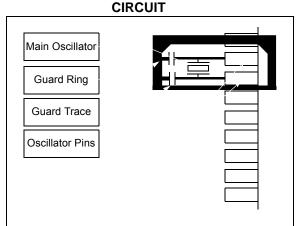

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. For more information, see **Section 9.0 "Oscillator Configuration"**.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed as shown in Figure 2-3.

## FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 5 MHz < FIN < 13.6 MHz to comply with device PLL start-up conditions. This intends that, if the external oscillator frequency is outside this range, the application must start up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source.

**Note:** Clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 3.7 Arithmetic Logic Unit (ALU)

The dsPIC33EVXXXGM00X/10X family ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. The data for the ALU operation can come from the W register array or from the data memory, depending on the addressing mode of the instruction. Similarly, the output data from the ALU can be written to the W register array or a data memory location.

For information on the SR bits affected by each instruction, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.7.1 MULTIPLIER

Using the high-speed, 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.7.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes the single-cycle per bit of the divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.8 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON) as follows:

- Fractional or Integer DSP Multiply (IF)

- Signed, Unsigned or Mixed-Sign DSP Multiply (US)

- Conventional or Convergent Rounding (RND)

- · Automatic Saturation On/Off for ACCA (SATA)

- Automatic Saturation On/Off for ACCB (SATB)

- Automatic Saturation On/Off for Writes to Data Memory (SATDW)

- Accumulator Saturation mode Selection (ACCSAT)

## TABLE 3-2:DSP INSTRUCTIONSSUMMARY

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

#### TABLE 4-41: PORTF REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 Bit ( | All<br>Resets |

|-------------|-------|--------|---------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|---------------|

| TRISF       | 0E64  | _      | —       | —      | —      | —      | —      | —     | —     | _     | —     | —     | —     | —     | —     | TRISF<1:0>  | 0003          |

| PORTF       | 0E66  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | RF<1:0>     | xxxx          |

| LATF        | 0E68  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | LATF<1:0>   | xxxx          |

| ODCF        | 0E6A  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | ODCF<1:0>   | 0000          |

| CNENF       | 0E6C  | _      | _       | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | —     | —     | CNIEF<1:0>  | 0000          |

| CNPUF       | 0E6E  | _      | _       | _      | _      | —      | _      | _     | _     | —     | _     | —     | _     | _     | _     | CNPUF<1:0>  | 0000          |

| CNPDF       | 0E70  | _      | _       | _      | _      | —      | _      | _     | _     | _     | _     | —     | _     | _     | _     | CNPDF<1:0>  | 0000          |

| Lawsurds    |       |        | n Decet |        |        |        |        |       |       |       |       |       |       |       |       |             |               |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-42: PORTG REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG       | 0E78  | _      | _      |        | —      |        | —      |       | TRISC | 6<9:6> |       | —     | _     |       | —     | —     | —     | 03C0          |

| PORTG       | 0E7A  |        | _      | _      | _      | _      | _      |       | RG<   | 9:6>   |       | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG        | 0E7C  |        | _      | _      | _      | _      | _      |       | LATG  | <9:6>  |       | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG        | 0E7E  |        | _      | _      | _      | _      | _      |       | ODCO  | i<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG       | 0E80  |        | _      | _      | _      | _      | _      |       | CNIEC | 6<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG       | 0E82  |        | _      | _      | _      | _      | _      |       | CNPU  | G<9:6> |       | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG       | 0E84  | _      | _      |        | —      |        | —      |       | CNPD  | G<9:6> |       | —     | -     | _     | _     | —     | _     | 0000          |

| ANSELG      | 0E86  | _      | _      |        | -      |        | -      |       | ANSG  | <9:6>  |       | -     | _     | _     | —     | _     |       | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

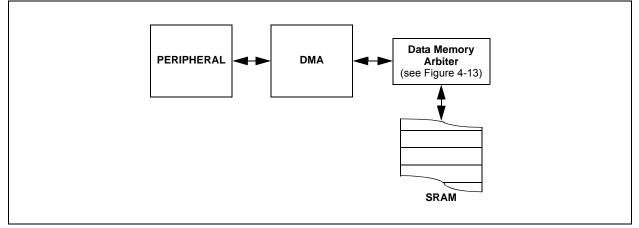

## 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 2 Unimplemented: Read as '0'

- bit 1 C1MD: CAN1 Module Disable bit<sup>(1)</sup>

- 1 = CAN1 module is disabled0 = CAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

- Note 1: This bit is available on dsPIC33EVXXXGM10X devices only.

#### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-------|-------|-------|-------|

| —      | —   | —   | —   | IC4MD | IC3MD | IC2MD | IC1MD |

| bit 15 |     |     |     |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | _   | —   | OC4MD | OC3MD | OC2MD | OC1MD |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-12 | Unimplemented: Read as '0'                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------|

| bit 11-8  | <b>IC4MD:IC1MD:</b> Input Capture x (x = 1-4) Module Disable bits                                           |

|           | 1 = Input Capture x module is disabled                                                                      |

|           | 0 = Input Capture x module is enabled                                                                       |

| bit 7-4   | Unimplemented: Read as '0'                                                                                  |

| bit 3-0   | <b>OC4MD:OC1MD:</b> Output Compare x (x = 1-4) Module Disable bits                                          |

|           | <ul> <li>1 = Output Compare x module is disabled</li> <li>0 = Output Compare x module is enabled</li> </ul> |

| U-0                               | U-0                                | R/W-0  | R/W-0  | R/W-0                              | R/W-0                                   | R/W-0  | R/W-0  |  |  |  |

|-----------------------------------|------------------------------------|--------|--------|------------------------------------|-----------------------------------------|--------|--------|--|--|--|

| —                                 | —                                  | RP55R5 | RP55R4 | RP55R3                             | RP55R2                                  | RP55R1 | RP55R0 |  |  |  |

| bit 15                            |                                    |        |        |                                    |                                         |        | bit 8  |  |  |  |

|                                   |                                    |        |        |                                    |                                         |        |        |  |  |  |

| U-0                               | U-0                                | R/W-0  | R/W-0  | R/W-0                              | R/W-0                                   | R/W-0  | R/W-0  |  |  |  |

| —                                 | —                                  | RP54R5 | RP54R4 | RP54R3                             | RP54R2                                  | RP54R1 | RP54R0 |  |  |  |

| bit 7                             |                                    |        |        |                                    |                                         |        | bit 0  |  |  |  |

|                                   |                                    |        |        |                                    |                                         |        |        |  |  |  |

| Legend:                           |                                    |        |        |                                    |                                         |        |        |  |  |  |

| R = Readable bit W = Writable bit |                                    |        |        | U = Unimplemented bit, read as '0' |                                         |        |        |  |  |  |

| -n = Value at P                   | -n = Value at POR '1' = Bit is set |        |        |                                    | '0' = Bit is cleared x = Bit is unknown |        |        |  |  |  |

## REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6<sup>(1)</sup>

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | RP54R<5:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits                                                               |

(see Table 11-3 for peripheral function numbers)

Note 1: This register is present in dsPIC33EVXXXGM004/104/006/106 devices only

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7<sup>(1)</sup>

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | RP57R5 | RP57R4 | RP57R3 | RP57R2 | RP57R1 | RP57R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0    | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| —      | —   | RP56R5 | RP56R4 | RP56R3 | RP56R2 | RP56R1 | RP56R0 |

| bit 7  |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>d as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP57R<5:0>:** Peripheral Output Function is Assigned to RP57 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP56R<5:0>:** Peripheral Output Function is Assigned to RP56 Output Pin bits (see Table 11-3 for peripheral function numbers)

**Note 1:** This register is present in dsPIC33EVXXXGM004/104/006/106 devices only.

## 15.1 Input Capture Control Registers

## REGISTER 15-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| REGISTER     | 15-1: ICxCO    | N1: INPUT C                                                                                    | CAPTURE x CO       | ONTROL REG           | ISTER 1          |                 |              |  |

|--------------|----------------|------------------------------------------------------------------------------------------------|--------------------|----------------------|------------------|-----------------|--------------|--|

| U-0          | U-0            | R/W-0                                                                                          | R/W-0              | R/W-0                | R/W-0            | U-0             | U-0          |  |

| _            |                | ICSIDL                                                                                         | ICTSEL2            | ICTSEL1              | ICTSEL0          | —               | _            |  |

| bit 15       |                | •                                                                                              |                    |                      |                  |                 | bit          |  |

| U-0          | R/W-0          | R/W-0                                                                                          | R-0, HC, HS        | R-0, HC, HS          | R/W-0            | R/W-0           | R/W-0        |  |

| _            | ICI1           | ICI0                                                                                           | ICOV               | ICBNE                | ICM2             | ICM1            | ICM0         |  |

| bit 7        |                |                                                                                                |                    |                      |                  |                 | bit          |  |

| Legend:      |                | HC = Hardwa                                                                                    | re Clearable bit   | HS = Hardwar         | re Settable bit  |                 |              |  |

| R = Readab   | le bit         | W = Writable                                                                                   | bit                | U = Unimplem         | nented bit, read | <b>l as</b> '0' |              |  |

| -n = Value a | t POR          | '1' = Bit is set                                                                               |                    | '0' = Bit is clea    | ared             | x = Bit is un   | known        |  |

| bit 15-14    | Unimplemen     | ted: Read as '                                                                                 | 0'                 |                      |                  |                 |              |  |

| bit 13       | -              |                                                                                                | p in Idle Mode C   | control bit          |                  |                 |              |  |

|              |                | -                                                                                              | t in CPU Idle mod  |                      |                  |                 |              |  |

|              |                |                                                                                                | tinue to operate   |                      | de               |                 |              |  |

| bit 12-10    |                |                                                                                                | e x Timer Select   |                      |                  |                 |              |  |

|              |                |                                                                                                | is the clock sour  | ce of the ICx        |                  |                 |              |  |

|              | 110 = Reserv   |                                                                                                |                    |                      |                  |                 |              |  |

|              | 101 = Reserv   |                                                                                                | ource of the ICx ( | only the synchr      | onous clock is   | supported)      |              |  |

|              |                |                                                                                                | ource of the ICx   | Unity the Synem      |                  | supported)      |              |  |

|              |                |                                                                                                | ource of the ICx   |                      |                  |                 |              |  |

|              |                |                                                                                                | ource of the ICx   |                      |                  |                 |              |  |

| bit 9-7      |                | ted: Read as '                                                                                 |                    |                      |                  |                 |              |  |

| bit 6-5      | ICI<1:0>: Nur  | mber of Captur                                                                                 | es per Interrupt S | Select bits (this fi | eld is not used  | if ICM<2:0> =   | 001 or 111   |  |

|              | 11 = Interrupt | t on every four                                                                                | th capture event   |                      |                  |                 |              |  |

|              |                |                                                                                                | l capture event    |                      |                  |                 |              |  |

|              |                |                                                                                                | ond capture ever   | nt                   |                  |                 |              |  |

|              | -              | t on every cap                                                                                 |                    |                      |                  |                 |              |  |

| bit 4        | -              | -                                                                                              | flow Status Flag   |                      |                  |                 |              |  |

|              |                |                                                                                                | overflow has occu  |                      |                  |                 |              |  |

| bit 3        |                | -                                                                                              | fer Not Empty St   |                      | nlv)             |                 |              |  |

|              | -              | -                                                                                              | s not empty, at le | -                    | • •              | an be read      |              |  |

|              |                | pture x buffer i                                                                               |                    |                      |                  |                 |              |  |

| bit 2-0      | ICM<2:0>: In   | put Capture x                                                                                  | Mode Select bits   |                      |                  |                 |              |  |

|              |                | 111 = Input Capture x functions as an interrupt pin only in CPU Sleep and Idle modes (rising e |                    |                      |                  |                 |              |  |

|              |                | detect only, all other control bits are not applicable)<br>110 = Unused (module is disabled)   |                    |                      |                  |                 |              |  |

|              |                |                                                                                                | ,                  |                      | nturo modo)      |                 |              |  |

|              |                |                                                                                                | / 16th rising edge |                      |                  |                 |              |  |

|              |                |                                                                                                | / rising edge (Sir |                      |                  |                 |              |  |

|              |                |                                                                                                | / falling edge (Si |                      |                  |                 |              |  |

|              |                | re mode, every                                                                                 | edge, rising and   |                      |                  | CI<1:0>) is not | t used in th |  |

|              | ,              |                                                                                                | ule is turned off  |                      |                  |                 |              |  |

000 = Input Capture x module is turned off

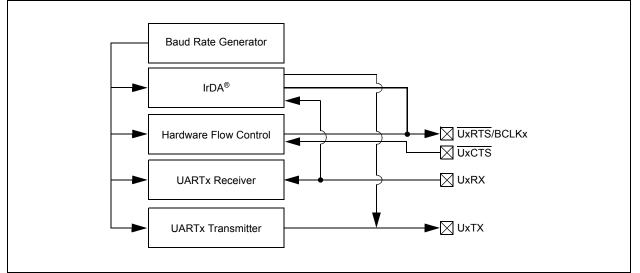

## 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EVXXXGM00X/10X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a

hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

| Note: | Hardware flow control using UxRTS and   |

|-------|-----------------------------------------|

|       | UxCTS is not available on all pin count |

|       | devices. See the "Pin Diagrams" section |

|       | for availability.                       |

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

## FIGURE 21-1: UARTX SIMPLIFIED BLOCK DIAGRAM

| U-0                     | U-0            | R-0                                     | R-0              | R-0                             | R-0                | R-0             | R-0   |

|-------------------------|----------------|-----------------------------------------|------------------|---------------------------------|--------------------|-----------------|-------|

|                         | _              | TXBO                                    | TXBP             | RXBP                            | TXWAR              | RXWAR           | EWARN |

| bit 15                  |                |                                         |                  |                                 | 1                  |                 | bit 8 |

|                         |                |                                         |                  |                                 |                    |                 |       |

| R/C-0                   | R/C-0          | R/C-0                                   | U-0              | R/C-0                           | R/C-0              | R/C-0           | R/C-0 |

| IVRIF                   | WAKIF          | ERRIF                                   | —                | FIFOIF                          | RBOVIF             | RBIF            | TBIF  |

| bit 7                   |                |                                         |                  |                                 |                    |                 | bit ( |

|                         |                | 0                                       | h:t ht a         | V                               |                    |                 |       |

| Legend:<br>R = Readable | , hit          | C = Writable<br>W = Writable            | -                |                                 | n to clear the bit |                 |       |

| -n = Value at           |                | '1' = Bit is set                        |                  | 0 = Onimple<br>'0' = Bit is cle | mented bit, read   |                 | 0.000 |

| -n = value at           | PUR            | I = BILIS SE                            |                  |                                 | eared              | x = Bit is unkr | IOWN  |

| bit 15-14               | Unimplemer     | nted: Read as '                         | 0'               |                                 |                    |                 |       |

| bit 13                  | -              | smitter in Error                        |                  | bit                             |                    |                 |       |

|                         | 1 = Transmit   | ter is in Bus Of<br>ter is not in Bus   | fstate           |                                 |                    |                 |       |

| bit 12                  | TXBP: Trans    | smitter in Error                        | State Bus Pas    | sive bit                        |                    |                 |       |

|                         |                | ter is in Bus Pa<br>ter is not in Bus   |                  | e                               |                    |                 |       |

| bit 11                  | RXBP: Rece     | eiver in Error Sta                      | ate Bus Passiv   | ve bit                          |                    |                 |       |

|                         |                | is in Bus Pass<br>is not in Bus P       |                  |                                 |                    |                 |       |

| bit 10                  | TXWAR: Tra     | Insmitter in Erro                       | or State Warni   | ng bit                          |                    |                 |       |

|                         |                | ter is in Error W<br>ter is not in Erro |                  | ate                             |                    |                 |       |

| bit 9                   | RXWAR: Re      | ceiver in Error                         | State Warning    | bit                             |                    |                 |       |

|                         |                | is in Error War                         | •                |                                 |                    |                 |       |

| <b>L</b> H 0            |                | is not in Error                         | •                |                                 | . 1. 14            |                 |       |

| bit 8                   |                | ansmitter or Reo<br>ter or receiver i   |                  | •                               | DIT                |                 |       |

|                         |                | ter or receiver i                       |                  |                                 |                    |                 |       |

| bit 7                   | IVRIF: Invalio | d Message Inte                          | rrupt Flag bit   |                                 |                    |                 |       |

|                         | •              | request has oc<br>request has no        |                  |                                 |                    |                 |       |

| bit 6                   | WAKIF: Bus     | Wake-up Activ                           | ity Interrupt Fl | lag bit                         |                    |                 |       |

|                         | •              | request has oc<br>request has no        |                  |                                 |                    |                 |       |

| bit 5                   | ERRIF: Error   | r Interrupt Flag                        | bit (multiple s  | ources in CxIN                  | TF<13:8> regist    | er)             |       |

|                         |                | request has oc<br>request has no        |                  |                                 |                    |                 |       |

| bit 4                   | Unimplemer     | nted: Read as '                         | 0'               |                                 |                    |                 |       |

| bit 3                   | FIFOIF: FIFO   | O Almost Full In                        | terrupt Flag b   | it                              |                    |                 |       |

|                         |                | request has oc<br>request has no        |                  |                                 |                    |                 |       |

| bit 2                   | RBOVIF: RX     | Buffer Overflo                          | w Interrupt Fla  | ag bit                          |                    |                 |       |

|                         | 1 – Interrunt  | request has oc                          | ourrod           |                                 |                    |                 |       |

## REGISTER 22-6: CXINTF: CANX INTERRUPT FLAG REGISTER

| 1                                            |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 |                  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|------------------|--|

| R/W-0                                        | R/W-0                                                                                                                                             | R/W-0                                                                                                                                     | R/W-0                                                                                                                                                                                     | R/W-0                                                                                            | R/W-0                                                                                  | R/W-0           | R/W-0            |  |

| F7MSK1                                       | F7MSK0                                                                                                                                            | F6MSK1                                                                                                                                    | F6MSK0                                                                                                                                                                                    | F5MSK1                                                                                           | F5MSK0                                                                                 | F4MSK1          | F4MSK0           |  |

| bit 15                                       |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 | bit 8            |  |

|                                              |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 |                  |  |

| R/W-0                                        | R/W-0                                                                                                                                             | R/W-0                                                                                                                                     | R/W-0                                                                                                                                                                                     | R/W-0                                                                                            | R/W-0                                                                                  | R/W-0           | R/W-0            |  |

| F3MSK1                                       | F3MSK0                                                                                                                                            | F2MSK1                                                                                                                                    | F2MSK0                                                                                                                                                                                    | F1MSK1                                                                                           | F1MSK0                                                                                 | F0MSK1          | F0MSK0           |  |

| bit 7                                        |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 | bit C            |  |

|                                              |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 |                  |  |

| Legend:                                      |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 |                  |  |

| R = Readable                                 | e bit                                                                                                                                             | W = Writable                                                                                                                              | bit                                                                                                                                                                                       | U = Unimpler                                                                                     | nented bit, reac                                                                       | <b>l as</b> '0' |                  |  |

| -n = Value at POR                            |                                                                                                                                                   | '1' = Bit is set                                                                                                                          | ł                                                                                                                                                                                         | 0' = Bit is cleared x = E                                                                        |                                                                                        | x = Rit is unkr | = Bit is unknown |  |

|                                              |                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                                           |                                                                                                  |                                                                                        |                 |                  |  |

| bit 15-14                                    | F7MSK<1:0><br>11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                                        | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re                                                                     | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain                                                                                                               | the mask<br>the mask<br>the mask                                                                 |                                                                                        |                 |                  |  |

| bit 13-12                                    | <b>F7MSK&lt;1:0&gt;</b><br>11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br><b>F6MSK&lt;1:0&gt;</b>                                | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source                                                    | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit                                                                                         | the mask<br>the mask<br>the mask<br>(same values                                                 | as bits 15-14)                                                                         |                 |                  |  |

| bit 13-12<br>bit 11-10                       | F7MSK<1:0><br>11 = Reserver<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0>                                           | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source<br>: Mask Source                                   | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit                                                                   | the mask<br>the mask<br>the mask<br>(same values<br>(same values                                 | as bits 15-14)<br>as bits 15-14)                                                       |                 |                  |  |

| bit 13-12<br>bit 11-10<br>bit 9-8            | F7MSK<1:0><br>11 = Reserver<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0>                                           | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source<br>: Mask Source                                   | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit                                                                   | the mask<br>the mask<br>the mask<br>(same values                                                 | as bits 15-14)<br>as bits 15-14)                                                       |                 |                  |  |

| bit 13-12<br>bit 11-10                       | F7MSK<1:0><br>11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0>                                            | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source<br>: Mask Source<br>: Mask Source                  | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit                                             | the mask<br>the mask<br>the mask<br>(same values<br>(same values                                 | as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)                                     |                 |                  |  |

| bit 13-12<br>bit 11-10<br>bit 9-8            | F7MSK<1:0><br>11 = Reserver<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0><br>F4MSK<1:0><br>F3MSK<1:0>               | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>nce Mask 0 re<br>: Mask Source<br>: Mask Source<br>: Mask Source<br>: Mask Source | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit<br>e for Filter 3 bit                       | the mask<br>the mask<br>the mask<br>(same values<br>(same values<br>(same values                 | as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)                   |                 |                  |  |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6 | F7MSK<1:0><br>11 = Reserver<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F6MSK<1:0><br>F5MSK<1:0><br>F4MSK<1:0><br>F3MSK<1:0><br>F3MSK<1:0> | : Mask Source<br>d<br>nce Mask 2 re<br>nce Mask 1 re<br>Mask Source<br>Mask Source<br>Mask Source<br>Mask Source<br>Mask Source           | e for Filter 7 bit<br>gisters contain<br>gisters contain<br>gisters contain<br>e for Filter 6 bit<br>e for Filter 5 bit<br>e for Filter 4 bit<br>e for Filter 3 bit<br>e for Filter 2 bit | the mask<br>the mask<br>the mask<br>(same values<br>(same values<br>(same values<br>(same values | as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)<br>as bits 15-14)<br>as bits 15-14) |                 |                  |  |

#### REGISTER 22-18: CxFMSKSEL1: CANx FILTERS 7-0 MASK SELECTION REGISTER 1

### REGISTER 22-22: CxRXFUL1: CANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0           | R/C-0 | R/C-0            | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|-----------------|-------|------------------|------------------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | RXFU             | L<15:8>           |                 |                 |       |

| bit 15          |       |                  |                  |                   |                 |                 | bit 8 |

|                 |       |                  |                  |                   |                 |                 |       |

| R/C-0           | R/C-0 | R/C-0            | R/C-0            | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|                 |       |                  | RXFL             | JL<7:0>           |                 |                 |       |

| bit 7           |       |                  |                  |                   |                 |                 | bit 0 |

|                 |       |                  |                  |                   |                 |                 |       |

| Legend:         |       | C = Writable b   | oit, but only '( | )' can be written | to clear the b  | it              |       |

| R = Readable    | bit   | W = Writable     | bit              | U = Unimplem      | nented bit, rea | <b>d as</b> '0' |       |

| -n = Value at P | POR   | '1' = Bit is set |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 RXFUL<15:0>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 22-23: CxRXFUL2: CANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0           | R/C-0 | R/C-0            | R/C-0           | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|-----------------|-------|------------------|-----------------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | RXFU            | _<31:24>          |                 |                 |       |

| bit 15          |       |                  |                 |                   |                 |                 | bit 8 |

|                 |       |                  |                 |                   |                 |                 |       |

| R/C-0           | R/C-0 | R/C-0            | R/C-0           | R/C-0             | R/C-0           | R/C-0           | R/C-0 |

|                 |       |                  | RXFU            | _<23:16>          |                 |                 |       |

| bit 7           |       |                  |                 |                   |                 |                 | bit 0 |

|                 |       |                  |                 |                   |                 |                 |       |

| Legend:         |       | C = Writable b   | it, but only '( | )' can be written | to clear the b  | bit             |       |

| R = Readable    | bit   | W = Writable b   | bit             | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at F | POR   | '1' = Bit is set |                 | '0' = Bit is cle  | ared            | x = Bit is unkr | nown  |

bit 15-0 RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

| Base<br>Instr<br>#Assembly<br>Mnemonic25CTXTSWP |      | Assembly Syntax CTXTSWP #lit3 |                     | Description                                            | # of<br>Words<br>1 | # of<br>Cycles | Status Flags<br>Affected<br>None |

|-------------------------------------------------|------|-------------------------------|---------------------|--------------------------------------------------------|--------------------|----------------|----------------------------------|

|                                                 |      |                               |                     | Switch CPU register context to context defined by lit3 |                    |                |                                  |

|                                                 |      | CTXTSWP                       | Wn                  | Switch CPU register context to context defined by Wn   | 1                  | 2              | None                             |

| 26                                              | DAW  | DAW                           | Wn                  | Wn = decimal adjust Wn                                 | 1                  | 1              | С                                |

| 27                                              | DEC  | DEC                           | f                   | f = f - 1                                              | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | DEC                           | f,WREG              | WREG = f – 1                                           | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | DEC                           | Ws,Wd               | Wd = Ws - 1                                            | 1                  | 1              | C,DC,N,OV,Z                      |

| 28                                              | DEC2 | DEC2                          | f                   | f = f - 2                                              | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | DEC2                          | f,WREG              | WREG = f – 2                                           | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | DEC2                          | Ws,Wd               | Wd = Ws - 2                                            | 1                  | 1              | C,DC,N,OV,Z                      |

| 29                                              | DISI | DISI                          | #lit14              | Disable Interrupts for k instruction cycles            | 1                  | 1              | None                             |

| 30                                              | DIV  | DIV.S                         | Wm,Wn               | Signed 16/16-bit Integer Divide                        | 1                  | 18             | N,Z,C,OV                         |

|                                                 |      | DIV.SD                        | Wm,Wn               | Signed 32/16-bit Integer Divide                        | 1                  | 18             | N,Z,C,OV                         |

|                                                 |      | DIV.U                         | Wm,Wn               | Unsigned 16/16-bit Integer Divide                      | 1                  | 18             | N,Z,C,OV                         |

|                                                 |      | DIV.UD                        | Wm,Wn               | Unsigned 32/16-bit Integer Divide                      | 1                  | 18             | N,Z,C,OV                         |

| 31                                              | DIVF | DIVF                          | Wm,Wn               | Signed 16/16-bit Fractional Divide                     | 1                  | 18             | N,Z,C,OV                         |

| 32                                              | DO   | DO                            | #lit15,Expr         | Do code to PC + Expr, lit15 + 1 times                  | 2                  | 2              | None                             |

|                                                 |      | DO                            | Wn,Expr             | Do code to PC + Expr, (Wn) + 1 times                   | 2                  | 2              | None                             |

| 33                                              | ED   | ED                            | Wm*Wm,Acc,Wx,Wy,Wxd | Euclidean Distance (no accumulate)                     | 1                  | 1              | OA,OB,OAB<br>SA,SB,SAB           |

| 34                                              | EDAC | EDAC                          | Wm*Wm,Acc,Wx,Wy,Wxd | Euclidean Distance                                     | 1                  | 1              | OA,OB,OAB<br>SA,SB,SAB           |

| 35                                              | EXCH | EXCH                          | Wns,Wnd             | Swap Wns with Wnd                                      | 1                  | 1              | None                             |

| 36                                              | FBCL | FBCL                          | Ws,Wnd              | Find Bit Change from Left (MSb) Side                   | 1                  | 1              | С                                |

| 37                                              | FF1L | FF1L                          | Ws,Wnd              | Find First One from Left (MSb) Side                    | 1                  | 1              | С                                |

| 38                                              | FF1R | FF1R                          | Ws,Wnd              | Find First One from Right (LSb) Side                   | 1                  | 1              | С                                |

| 39                                              | GOTO | GOTO                          | Expr                | Go to address                                          | 2                  | 4              | None                             |

|                                                 |      | GOTO                          | Wn                  | Go to indirect                                         | 1                  | 4              | None                             |

|                                                 |      | GOTO.L                        | Wn                  | Go to indirect (long address)                          | 1                  | 4              | None                             |

| 40                                              | INC  | INC                           | f                   | f = f + 1                                              | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | INC                           | f,WREG              | WREG = f + 1                                           | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | INC                           | Ws,Wd               | Wd = Ws + 1                                            | 1                  | 1              | C,DC,N,OV,Z                      |

| 41                                              | INC2 | INC2                          | f                   | f = f + 2                                              | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | INC2                          | f,WREG              | WREG = f + 2                                           | 1                  | 1              | C,DC,N,OV,Z                      |

|                                                 |      | INC2                          | Ws,Wd               | Wd = Ws + 2                                            | 1                  | 1              | C,DC,N,OV,Z                      |

| 42                                              | IOR  | IOR                           | f                   | f = f .IOR. WREG                                       | 1                  | 1              | N,Z                              |

|                                                 |      | IOR                           | f,WREG              | WREG = f .IOR. WREG                                    | 1                  | 1              | N,Z                              |

|                                                 |      | IOR                           | #lit10,Wn           | Wd = lit10 .IOR. Wd                                    | 1                  | 1              | N,Z                              |

|                                                 |      | IOR                           | Wb,Ws,Wd            | Wd = Wb .IOR. Ws                                       | 1                  | 1              | N,Z                              |

|                                                 |      | IOR                           | Wb,#lit5,Wd         | Wd = Wb .IOR. lit5                                     | 1                  | 1              | N,Z                              |

| 43                                              | LAC  | LAC                           | Wso,#Slit4,Acc      | Load Accumulator                                       | 1                  | 1              | OA,OB,OAB,<br>SA,SB,SAB          |

| 44                                              | LNK  | LNK                           | #lit14              | Link Frame Pointer                                     | 1                  | 1              | SFA                              |

| 45                                              | LSR  | LSR                           | f                   | f = Logical Right Shift f                              | 1                  | 1              | C,N,OV,Z                         |

|                                                 |      | LSR                           | f,WREG              | WREG = Logical Right Shift f                           | 1                  | 1              | C,N,OV,Z                         |

|                                                 |      | LSR                           | Ws,Wd               | Wd = Logical Right Shift Ws                            | 1                  | 1              | C,N,OV,Z                         |

|                                                 |      | LSR                           | Wb,Wns,Wnd          | Wnd = Logical Right Shift Wb by Wns                    | 1                  | 1              | N,Z                              |

|                                                 |      | LSR                           | Wb,#lit5,Wnd        | Wnd = Logical Right Shift Wb by lit5                   | 1                  | 1              | N,Z                              |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax                                                     |              | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------------------------------------------------------------------|--------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 53                 | MUL                  | MUL.SS                                                              | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1              | None                     |

|                    |                      | MUL.SS                                                              | Wb,Ws,Acc    | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                     |

|                    |                      | MUL.SU     Wb,Ws,Wnd     {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws) |              | 1                                                 | 1             | None           |                          |

|                    |                      | MUL.SU                                                              | Wb,Ws,Acc    | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU                                                              | Wb,#lit5,Acc | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                     |

|                    |                      | MUL.US                                                              | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US                                                              | Wb,Ws,Acc    | Accumulator = unsigned(Wb) *<br>signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU                                                              | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.UU                                                              | Wb,#lit5,Acc | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU                                                              | Wb,Ws,Acc    | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                     |

|                    |                      | MULW.SS                                                             | Wb,Ws,Wnd    | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                     |

|                    |                      | MULW.SU                                                             | Wb,Ws,Wnd    | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.US                                                             | Wb,Ws,Wnd    | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.UU                                                             | Wb,Ws,Wnd    | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                     |

|                    |                      | MUL.SU                                                              | Wb,#lit5,Wnd | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.SU                                                              | Wb,#lit5,Wnd | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                     |