Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm004-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

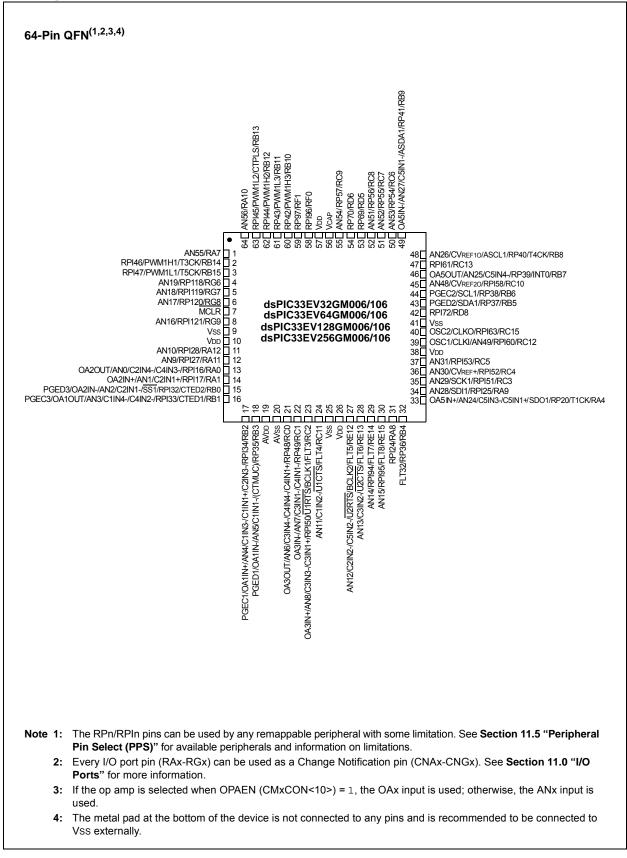

#### Pin Diagrams (Continued)

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

#### 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

# 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

## 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

| R/W-0               | U-0                          | R/W-0                                                 | R/W-0                                                | EGISTER             | R-0             | R-0             | R-0        |

|---------------------|------------------------------|-------------------------------------------------------|------------------------------------------------------|---------------------|-----------------|-----------------|------------|

| VAR                 | 0-0                          | US1                                                   | US0                                                  | EDT <sup>(1)</sup>  | DL2             | DL1             | R-0<br>DL0 |

| pit 15              | _                            | 031                                                   | 030                                                  | EDI                 | DL2             |                 | bLU        |

| R/W-0               | R/W-0                        | R/W-1                                                 | R/W-0                                                | R/C-0               | R-0             | R/W-0           | R/W-0      |

| SATA                | SATB                         | SATDW                                                 | ACCSAT                                               | IPL3 <sup>(2)</sup> | SFA             | RND             | IF         |

| bit 7               | SAID                         | SAIDW                                                 | ACCOAL                                               | IF LOV /            | SFA             | RIND            | bit        |

| Legend:             |                              | C = Clearable                                         | - bit                                                |                     |                 |                 |            |

| R = Readable        | bit                          | W = Writable                                          |                                                      | U = Unimplem        | onted hit rea   | d as '0'        |            |

| -n = Value at F     |                              | '1' = Bit is set                                      |                                                      | '0' = Bit is clea   |                 | x = Bit is unkr |            |

|                     | -                            |                                                       |                                                      |                     |                 |                 |            |

| bit 15              | 1 = Variable e               | exception proce                                       | ocessing Later<br>essing latency                     | is enabled          |                 |                 |            |

| L:4 4 4             |                              |                                                       | sing latency is                                      | enabled             |                 |                 |            |

| bit 14<br>bit 13-12 | •                            | ted: Read as '                                        | 0<br>igned/Signed (                                  | Control hito        |                 |                 |            |

|                     | 01 = DSP eng<br>00 = DSP eng | gine multiplies<br>gine multiplies<br>gine multiplies | are signed                                           |                     |                 |                 |            |

| bit 11              |                              |                                                       | ation Control bi<br>e $DO$ loop at th                | e end of the cu     | rrent loop iter | ation           |            |

| bit 10-8            | 111 = 7 DO lo                | ops are active                                        |                                                      | ts                  |                 |                 |            |

| bit 7               |                              | Saturation En                                         |                                                      |                     |                 |                 |            |

|                     |                              | ator A saturatio<br>ator A saturatio                  |                                                      |                     |                 |                 |            |

| bit 6               | 1 = Accumula                 | Saturation En<br>ator B saturatio<br>ator B saturatio | n is enabled                                         |                     |                 |                 |            |

| bit 5               | 1 = Data Space               | ce write satura                                       | from DSP Engi<br>tion is enabled<br>tion is disabled |                     | Enable bit      |                 |            |

| bit 4               | -                            | cumulator Satu                                        | ration Mode S                                        |                     |                 |                 |            |

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### TABLE 4-19: NVM REGISTER MAP

|             |       |        |                 |          |              |            |               |       | -     |                  |       | -     |       |         |        |        | -      |               |

|-------------|-------|--------|-----------------|----------|--------------|------------|---------------|-------|-------|------------------|-------|-------|-------|---------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14          | Bit 13   | Bit 12       | Bit 11     | Bit 10        | Bit 9 | Bit 8 | Bit 7            | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| NVMCON      | 0728  | WR     | WREN            | WRERR    | NVMSIDL      | _          | _             | RPDF  | URERR | _                | —     | _     | _     | NVMOP3  | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        | NVMADR<15:0> 00 |          |              |            |               |       |       |                  | 0000  |       |       |         |        |        |        |               |

| NVMADRU     | 072C  | _      | _               | _        | _            |            | _             | _     | _     | NVMADRU<23:16>   |       |       |       |         | 0000   |        |        |               |

| NVMKEY      | 072E  | _      | _               | _        | _            |            | _             | _     | _     |                  |       |       | NVMK  | EY<7:0> |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |                 |          |              |            |               |       | NVMSF | RCADR<15:        | 1>    |       |       |         |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  | _      | _               | _        | _            |            | _             | _     | _     | NVMSRCADR<23:16> |       |       |       |         | 0000   |        |        |               |

| Lonondy     |       |        |                 | Desetual | an are chour | a in harve | d a stress al |       |       |                  |       |       |       |         |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | _      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0000          |

| PLLFBD      | 0746  | -      | —      |        | —      | _      | _       | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0000          |

| OSCTUN      | 0748  | -      | —      |        | —      | _      | _       | —       |         | _        | _        |        |           | TUN     | <5:0>   |         |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

## TABLE 4-21: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   | -      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     | _     | _     | —     | _     | _     | _     | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EVXXXGM00X/10X FAMILY

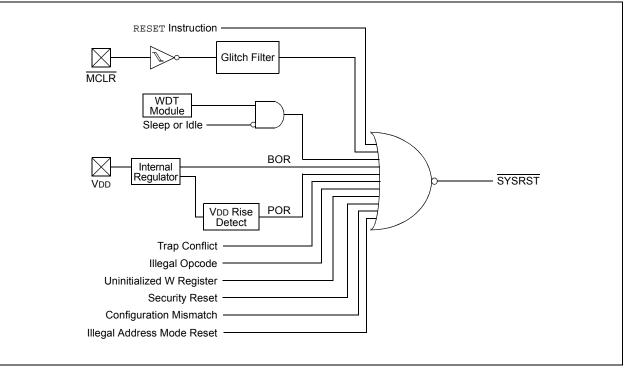

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

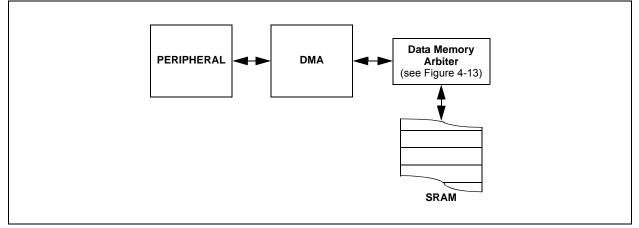

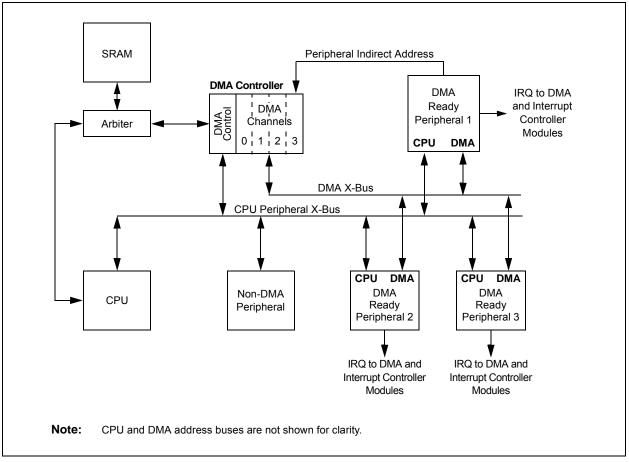

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

#### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

Figure 8-2 illustrates the DMA Controller block diagram.

## 8.1 DMAC Controller Registers

Each DMAC Channel x (where x = 0 to 3) contains the following registers:

- 16-Bit DMA Channel x Control Register (DMAxCON)

- 16-Bit DMA Channel x IRQ Select Register (DMAxREQ)

- 32-Bit DMA Channel x Start Address Register A High/Low (DMAxSTAH/L)

- 32-Bit DMA Channel x Start Address Register B High/Low (DMAxSTBH/L)

- 16-Bit DMA Channel x Peripheral Address Register (DMAxPAD)

- 14-Bit DMA Channel x Transfer Count Register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADRH/L) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The DMA Interrupt Flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding DMA Interrupt Enable bits (DMAxIE) are located in an IECx register in the interrupt controller and the corresponding DMA Interrupt Priority bits (DMAxIP) are located in an IPCx register in the interrupt controller.

| U-0          | R-0                                     | R-0                                              | R-0              | U-0              | R/W-y                        | R/W-y                | R/W-y                |

|--------------|-----------------------------------------|--------------------------------------------------|------------------|------------------|------------------------------|----------------------|----------------------|

| _            | COSC2                                   | COSC1                                            | COSC0            | —                | NOSC2 <sup>(2)</sup>         | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |

| bit 15       |                                         |                                                  |                  |                  |                              |                      | bit 8                |

|              |                                         |                                                  |                  |                  |                              |                      |                      |

| R/W-0        | R/W-0                                   | R-0                                              | U-0              | R/C-0            | U-0                          | U-0                  | R/W-0                |

| CLKLOCK      | IOLOCK                                  | LOCK                                             | —                | CF               |                              |                      | OSWEN                |

| bit 7        |                                         |                                                  |                  |                  |                              |                      | bit (                |

| Legend:      |                                         | C = Clearable                                    | hit              | v = Value set    | from Configura               | tion hits on PO      | R                    |

| R = Readab   | le hit                                  | W = Writable                                     |                  | ,                | mented bit, read             |                      |                      |

| -n = Value a |                                         | '1' = Bit is set                                 |                  | '0' = Bit is cle |                              | x = Bit is unkr      | าดพุท                |

|              |                                         |                                                  |                  |                  |                              |                      | IOWIT                |

| bit 15       | Unimplemen                              | ted: Read as '                                   | 0'               |                  |                              |                      |                      |

| bit 14-12    | -                                       | Current Oscilla                                  |                  | bits (read-only  | ()                           |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | · · ·            | ,                            |                      |                      |

|              | 110 <b>= Fast R</b>                     | C Oscillator (F                                  | RC) with Divid   |                  |                              |                      |                      |

|              |                                         | ower RC Oscill                                   |                  |                  |                              |                      |                      |

|              |                                         | p FRC Oscillator<br>y Oscillator (X <sup>-</sup> |                  | ыры              |                              |                      |                      |

|              |                                         | y Oscillator (X                                  |                  | II PLL           |                              |                      |                      |

|              |                                         | C Oscillator (F                                  | ,                | y N and PLL      |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | ,                |                              |                      |                      |

| bit 11       | -                                       | ted: Read as '                                   |                  |                  |                              |                      |                      |

| bit 10-8     | NOSC<2:0>:                              | New Oscillator                                   | r Selection bits | <sub>S</sub> (2) |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  |                  |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | le-by-16         |                              |                      |                      |

|              | 101 = Low-P                             | ower RC Oscill<br><sub>/ed</sub> (5)             |                  |                  |                              |                      |                      |

|              |                                         | y Oscillator (X <sup>-</sup>                     | Г, HS, EC) wit   | h PLL            |                              |                      |                      |

|              |                                         | y Oscillator (X                                  |                  |                  |                              |                      |                      |

|              |                                         | C Oscillator (F                                  |                  | y N and PLL      |                              |                      |                      |

| hit 7        |                                         | C Oscillator (F                                  | ,                |                  |                              |                      |                      |

| bit 7        |                                         | Clock Lock Ena                                   |                  | onfigurations a  | re locked; if FCk            | (SM0 = 0  then)      | clock and Pl         |

|              |                                         | ations may be r                                  |                  |                  |                              |                      |                      |

|              |                                         |                                                  |                  | ked, configurat  | ions may be mo               | odified              |                      |

| bit 6        | IOLOCK: I/O                             | Lock Enable b                                    | oit              |                  |                              |                      |                      |

|              | 1 = I/O lock is                         |                                                  |                  |                  |                              |                      |                      |

|              | 0 = I/O lock is                         |                                                  |                  |                  |                              |                      |                      |

| bit 5        |                                         | ock Status bit                                   |                  |                  |                              |                      |                      |

|              |                                         | that PLL is in that PLL is ou                    |                  |                  | satisfied<br>progress or PLL | is disabled          |                      |

|              |                                         |                                                  |                  |                  | -                            |                      |                      |

|              | Vrites to this regis<br>dsPIC33/PIC24 F |                                                  |                  |                  |                              |                      | ils.                 |

|              | irect clock switch                      | -                                                | -                |                  | -                            | -                    |                      |

| te           | ed. This applies to                     | o clock switche                                  | s in either dire | ection. In these | instances, the               |                      |                      |

|              | RC mode as a tra                        |                                                  |                  |                  | L modes.                     |                      |                      |

|              | his register reset                      | -                                                |                  |                  |                              |                      |                      |

| <b>4</b> : C | OSC<2:0> bits w                         | viii be set to '0k                               | DIOU when H      | to fails.        |                              |                      |                      |

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

5: User cannot write '0b100' to NOSC<2:0>. COSC<2:0> will be set to '0b100' (BFRC) when the FRC fails.

NOTES:

#### REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6       | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled<br>01 = Negative dead time is actively applied for Complementary Output mode<br>00 = Positive dead time is actively applied for all Output modes |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | DTCP: Dead-Time Compensation Polarity bit <sup>(3)</sup><br><u>When Set to '1':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                           |

|               | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.<br>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                       |

| bit 4-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

| bit 2         | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                      |

|               | 1 = Center-Aligned mode is enabled<br>0 = Edge-Aligned mode is enabled                                                                                                                                                                                                    |

| bit 1         | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                     |

|               | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode</li> <li>0 = External pins do not affect PWMx time base</li> </ul>                                                                                   |

| bit 0         | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                                                                                                           |

|               | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                 |

| Note 1:<br>2: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.<br>These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                    |

| 3:            | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.                                                                                                                                                                                                            |

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# dsPIC33EVXXXGM00X/10X FAMILY

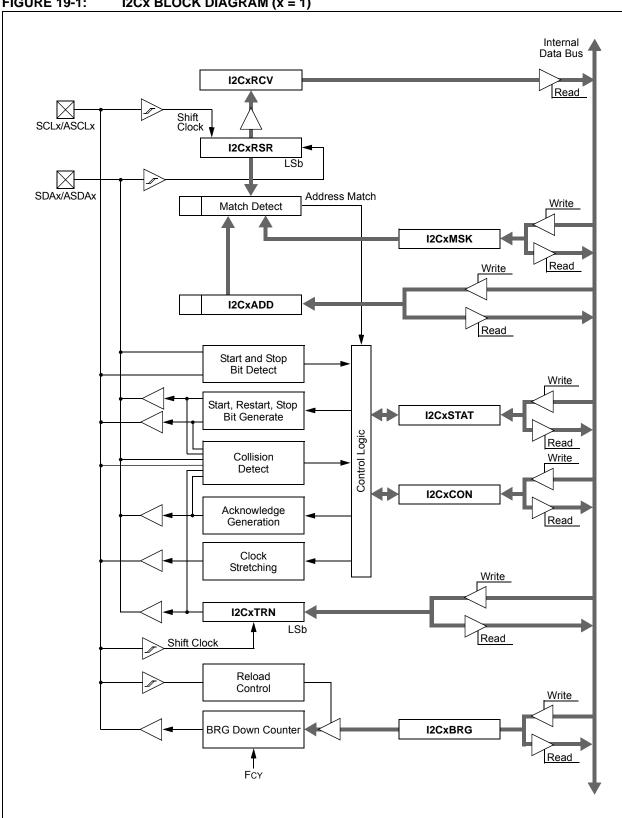

# REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1 (CONTINUED)

| bit 7   | GCEN: General Call Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception</li> <li>0 = General call address is disabled.</li> </ul>                                                                                                                                                                                                                              |

| bit 6   | STREN: SCLx Clock Stretch Enable bit                                                                                                                                                                                                                                                                                                                                                                      |

|         | In I <sup>2</sup> C Slave mode only, used in conjunction with the SCLREL bit.<br>1 = Enables clock stretching<br>0 = Disables clock stretching                                                                                                                                                                                                                                                            |

| bit 5   | ACKDT: Acknowledge Data bit                                                                                                                                                                                                                                                                                                                                                                               |

|         | In I <sup>2</sup> C Master mode, during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.<br>In I <sup>2</sup> C Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.<br>1 = NACK is sent<br>0 = ACK is sent |

| bit 4   | ACKEN: Acknowledge Sequence Enable bit                                                                                                                                                                                                                                                                                                                                                                    |

|         | In I <sup>2</sup> C Master mode only; applicable during Master Receive mode.<br>1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit<br>0 = Acknowledge sequence is Idle                                                                                                                                                                                                |

| bit 3   | <b>RCEN:</b> Receive Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | 1 = Enables Receive mode for $I^2C$ , automatically cleared by hardware at the end of 8-bit receive data byte 0 = Receive sequence is not in progress                                                                                                                                                                                                                                                     |

| bit 2   | <b>PEN:</b> Stop Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins</li> <li>0 = Stop condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                                |

| bit 1   | <b>RSEN:</b> Restart Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = Initiates Restart condition on SDAx and SCLx pins</li> <li>0 = Restart condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                          |

| bit 0   | SEN: Start Condition Enable bit (I <sup>2</sup> C Master mode only)                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins</li> <li>0 = Start condition is Idle</li> </ul>                                                                                                                                                                                                                                                                                              |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                                                                                                                                                                                          |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0            | R/W-0             | R/W-0           | R/W-0 |

|---------------|----------------------|------------------|------------------|------------------|-------------------|-----------------|-------|

| F7BP3         | F7BP2                | F7BP1            | F7BP0            | F6BP3            | F6BP2             | F6BP1           | F6BP0 |

| bit 15        |                      | -                |                  |                  |                   |                 | bit 8 |

|               |                      |                  |                  |                  |                   |                 |       |

| R/W-0         | R/W-0                | R/W-0            | R/W-0            | R/W-0            | R/W-0             | R/W-0           | R/W-0 |

| F5BP3         | F5BP2                | F5BP1            | F5BP0            | F4BP3            | F4BP2             | F4BP1           | F4BP0 |

| bit 7         |                      |                  |                  |                  |                   |                 | bit 0 |

|               |                      |                  |                  |                  |                   |                 |       |

| Legend:       |                      |                  |                  |                  |                   |                 |       |

| R = Readable  | e bit                | W = Writable     | bit              | U = Unimpler     | nented bit, read  | <b>as</b> '0'   |       |

| -n = Value at | POR                  | '1' = Bit is set |                  | '0' = Bit is cle | ared              | x = Bit is unkr | nown  |

|               |                      |                  |                  |                  |                   |                 |       |

| bit 15-12     | F7BP<3:0>:           | RX Buffer Masl   | k for Filter 7 b | its              |                   |                 |       |

|               | 1111 = Filter        | hits received in | NRX FIFO bu      | ffer             |                   |                 |       |

|               | 1110 <b>= Filter</b> | hits received in | RX Buffer 14     | 1                |                   |                 |       |

|               | •                    |                  |                  |                  |                   |                 |       |

|               | •                    |                  |                  |                  |                   |                 |       |

|               | •<br>0001 - Filtor   | hits received in |                  |                  |                   |                 |       |

|               | 0001                 | hits received in |                  |                  |                   |                 |       |

| bit 11-8      |                      |                  |                  | its (same value  | es as bits 15-12) |                 |       |

|               |                      |                  |                  | -                | -                 |                 |       |

| bit 7-4       | F3BP<3:0>:1          | KA Builer Masi   | CION FILTER 5 D  | its (same value  | es as bits 15-12) | )               |       |

### REGISTER 22-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

bit 3-0 **F4BP<3:0>:** RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

### REGISTER 24-2: ADxCON2: ADCx CONTROL REGISTER 2 (CONTINUED)

| bit 1 | <ul> <li>BUFM: Buffer Fill Mode Select bit</li> <li>1 = Starts buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on the next interrupt</li> <li>0 = Always starts filling the buffer from the Start address</li> </ul> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 0 | <ul> <li>ALTS: Alternate Input Sample Mode Select bit</li> <li>1 = Uses channel input selects for Sample MUX A on the first sample and Sample MUX B on the next sample</li> <li>0 = Always uses channel input selects for Sample MUX A</li> </ul>                         |

Note 1: The ADCx VREFH Input is connected to AVDD and the VREFL input is connected to AVss.

# 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EVXXXGM00X/10X family electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EVXXXGM00X/10X family high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                | 40°C to +150°C |

|--------------------------------------------------------------|----------------|

| Storage temperature                                          | 65°C to +160°C |

| Voltage on VDD with respect to Vss                           | -0.3V to +6.0V |

| Maximum current out of Vss pin                               |                |

| Maximum current into Vod pin <sup>(3)</sup>                  |                |

| Maximum junction temperature                                 |                |

| Maximum current sunk by any I/O pin                          |                |

| Maximum current sourced by I/O pin                           |                |

| Maximum current sunk by all ports combined                   |                |

| Maximum current sourced by all ports combined <sup>(3)</sup> | 200 mA         |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

## 31.1 High-Temperature DC Characteristics

#### TABLE 31-1: OPERATING MIPS vs. VOLTAGE

| Characteristic | VDD Range                     | Temperature Range | Max MIPS                     |

|----------------|-------------------------------|-------------------|------------------------------|

| Characteristic | (in Volts)                    | (in °C)           | dsPIC33EVXXXGM00X/10X Family |

| HDC5           | 4.5V to 5.5V <sup>(1,2)</sup> | -40°C to +150°C   | 40                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules, such as the ADC, op amp/comparator and comparator voltage reference, will have degraded performance. Device functionality is tested but is not characterized. Refer to Parameter BO10 in Table 30-12 for the minimum and maximum BOR values.

2: When BOR is enabled, the device will work from 4.7V to 5.5V.

#### TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min         | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| High-Temperature Devices                                                                                                                                                               |        |             |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40         | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40         | _           | +150 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O |             |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | Pdmax  | (           | TJ — TA)/θJ | IA   | W    |

#### TABLE 31-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                                   |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------|---------------------|------|-------|---------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                      | Min.                                                  | Typ. <sup>(1)</sup> | Max. | Units | Conditions                                        |  |

| Operating Voltage  |        |                                                                     |                                                       |                     |      |       |                                                   |  |

| HDC10              | Vdd    | Supply Voltage <sup>(3)</sup>                                       | VBOR                                                  | _                   | 5.5  | V     |                                                   |  |

| HDC12              | Vdr    | RAM Data Retention<br>Voltage <sup>(2)</sup>                        | 1.8                                                   | _                   | —    | V     |                                                   |  |

| HDC16              | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | —                                                     | —                   | Vss  | V     |                                                   |  |

| HDC17              | Svdd   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 1.0                                                   | _                   | —    | V/ms  | 0V-5.0V in 5 ms                                   |  |

| HDC18              | VCORE  | VDD Core<br>Internal Regulator Voltage                              | 1.62                                                  | 1.8                 | 1.98 | V     | Voltage is dependent on load, temperature and VDD |  |

Note 1: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

2: This is the limit to which VDD may be lowered without losing RAM data.

3: VDD voltage must remain at Vss for a minimum of 200  $\mu$ s to ensure POR.

| TABLE 31-4: | DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) |

|-------------|----------------------------------------------|

|-------------|----------------------------------------------|

| DC CHARACT       | ERISTICS      |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                         |  |  |  |

|------------------|---------------|------|------------------------------------------------------|-----------------------------------------|--|--|--|

| Parameter<br>No. | Typical       | Мах  | Units                                                | its Conditions                          |  |  |  |

| Power-Down (     | Current (IPD) |      |                                                      |                                         |  |  |  |

| HDC60e           | 1300          | 2500 | μA                                                   | +150°C 5V Base Power-Down Current       |  |  |  |

| HDC61c           | 10            | 50   | μA                                                   | +150°C 5V Watchdog Timer Current: ∆IwDT |  |  |  |

#### TABLE 31-5: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

| DC CHARAG        | CTERISTICS |     |       | •                 |  | (unless otherwise stated)<br>for High Temperature |  |  |

|------------------|------------|-----|-------|-------------------|--|---------------------------------------------------|--|--|

| Parameter<br>No. | Typical    | Max | Units | Conditions        |  |                                                   |  |  |

| HDC40e           | 2.6        | 5.0 | mA    | +150°C 5V 10 MIPS |  |                                                   |  |  |

| HDC42e           | 3.6        | 7.0 | mA    | +150°C 5V 20 MIPS |  |                                                   |  |  |

#### TABLE 31-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARAG        | CTERISTICS |      |       | •                 |    | V (unless otherwise stated)<br>C for High Temperature |  |

|------------------|------------|------|-------|-------------------|----|-------------------------------------------------------|--|

| Parameter<br>No. | Typical    | Max  | Units | Conditions        |    |                                                       |  |

| HDC20e           | 5.9        | 8.0  | mA    | +150°C 5V 10 MIPS |    |                                                       |  |

| HDC22e           | 10.3       | 15.0 | mA    | +150°C            | 5V | 20 MIPS                                               |  |

| HDC23e           | 19.0       | 25.0 | mA    | +150°C            | 5V | 40 MIPS                                               |  |

#### TABLE 31-7: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARAG        | CTERISTICS |      | Standard Operating Conditions: 4.5V to 5.5V (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |       |            |    |         |

|------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|----|---------|

| Parameter<br>No. | Typical    | Мах  | Doze Ratio                                                                                                                                                  | Units | Conditions |    |         |

| HDC73a           | 18.5       | 22.0 | 1:2                                                                                                                                                         | mA    | +150°C     | 5V | 40 MIPS |

| HDC73g           | 8.35       | 12.0 | 1:128                                                                                                                                                       | mA    | +150 C     | 50 | 40 WIPS |

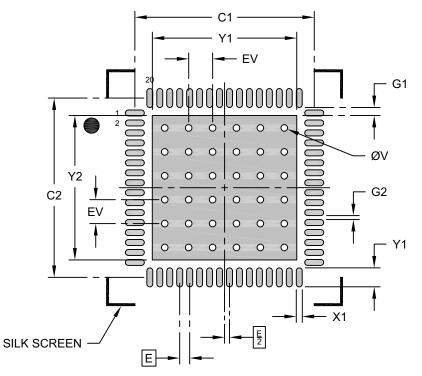

#### 64-Lead Very Thin Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [VQFN] With 7.15 x 7.15 Exposed Pad [Also called QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                    | Units            |      |          |      |  |  |

|------------------------------------|------------------|------|----------|------|--|--|

| Dimension                          | Dimension Limits |      |          |      |  |  |

| Contact Pitch                      | E                |      | 0.50 BSC |      |  |  |

| Optional Center Pad Width          | X2               |      |          | 7.25 |  |  |

| Optional Center Pad Length         | Y2               |      |          | 7.25 |  |  |

| Contact Pad Spacing                | C1               |      | 9.00     |      |  |  |

| Contact Pad Spacing                | C2               |      | 9.00     |      |  |  |

| Contact Pad Width (X64)            | X1               |      |          | 0.30 |  |  |

| Contact Pad Length (X64)           | Y1               |      |          | 0.95 |  |  |

| Contact Pad to Center Pad (X64)    | G1               | 0.40 |          |      |  |  |

| Spacing Between Contact Pads (X60) | G2               | 0.20 |          |      |  |  |

| Thermal Via Diameter               | V                |      | 0.33     |      |  |  |

| Thermal Via Pitch                  | EV               |      | 1.20     |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2149C [MR]

# APPENDIX A: REVISION HISTORY

# **Revision A (December 2013)**

This is the initial version of this document.

# Revision B (June 2014)

This revision incorporates the following updates:

- Sections:

- Added Section 31.0 "High-Temperature Electrical Characteristics"

- Updated the "Power Management" section, the "Input/Output" section, Section 3.3

"Data Space Addressing", Section 4.2

"Data Address Space", Section 4.3.2

"Extended X Data Space", Section 4.6.1

"Bit-Reversed Addressing Implementation", Section 7.4.1 "INTCON1 through INTCON4", Section 11.7 "I/O Helpful Tips"

- Updated note in Section 17.0 "High-Speed PWM Module", Section 18.0 "Serial Peripheral Interface (SPI)", Section 27.8 "Code Protection and CodeGuard™ Security"

- Updated title of Section 20.0 "Single-Edge Nibble Transmission (SENT)"

- Updated Section 34.0 "Packaging Information". Deleted e3, Pb-free and Industrial (I) temperature range indication throughout the section, and updated the packaging diagrams

- Updated the "Product Identification System" section

- Registers:

- Updated Register 3-2, Register 7-2, Register 7-6, Register 9-2, Register 11-3, Register 14-1, Register 14-3, Register 14-11, Register 15-1, Register 22-4

- Figures:

- Added Figure 4-6, Figure 4-8, Figure 4-14, Figure 4-15, Figure 14-1, Figure 16-1, Figure 17-2, Figure 23-1, Figure 24-1

- Tables:

- Updated Table 1, Table 27-1, Table 27-2, Table 30-6, Table 30-7, Table 30-8, Table 30-9, Table 30-10, Table 30-11, Table 30-12, Table 30-38, Table 30-50, Table 30-53 and added Table 31-11,

- Changes to text and formatting were incorporated throughout the document

### **Revision C (November 2014)**

This revision incorporates the following updates:

- · Sections:

- Added note in Section 5.2 "RTSP Operation"

- Updated "Section 5.4 "Error Correcting Code (ECC)"

- Deleted 44-Terminal Very Thin Leadless Array Package (TL) - 6x6x0.9 mm Body With Exposed Pad (VTLA).

- Registers

- Updated Register 7-6

- Figures:

- Updated Figure 4-1, Figure 4-3, Figure 4-4

- · Tables:

- Updated Table 27-2, Table 31-13, Table 31-14, Table 31-15

- Added Table 31-16, Table 31-17

# **Revision D (April 2015)**

This revision incorporates the following updates:

- Sections:

- Updated the Clock Management, Timers/ Output Compare/Input Capture, Communication Interfaces and Input/Output sections at the beginning of the data sheet (Page 1 and Page 2).

- Updated all pin diagrams at the beginning of the data sheet (Page 4 through Page 9).

- Added Section 11.6 "High-Voltage Detect (HVD)"

- Updated Section 13.0 "Timer2/3 and Timer4/5"

- Corrects all Buffer heading numbers in Section 22.4 "CAN Message Buffers"

- Registers

- Updated Register 3-2, Register 25-2, Register 26-2

- Figures

- Updated Figure 26-1, Figure 30-5, Figure 30-32

- Tables

- Updated Table 1, Table 4-25, Table 30-10, Table 30-22, Table 30-53 and Table 31-8

- Changes to text and formatting were incorporated throughout the document