#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm004-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                               |     |

|-------|-------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers         | 17  |

| 3.0   | CPU                                                                           |     |

| 4.0   | Memory Organization                                                           |     |

| 5.0   | Flash Program Memory                                                          | 83  |

| 6.0   | Resets                                                                        |     |

| 7.0   | Interrupt Controller                                                          |     |

| 8.0   | Direct Memory Access (DMA)                                                    | 109 |

| 9.0   | Oscillator Configuration                                                      | 123 |

| 10.0  | Power-Saving Features                                                         | 133 |

| 11.0  | I/O Ports                                                                     | 143 |

| 12.0  | Timer1                                                                        | 173 |

| 13.0  | Timer2/3 and Timer4/5                                                         | 175 |

| 14.0  | Deadman Timer (DMT)                                                           | 181 |

| 15.0  | Input Capture                                                                 | 189 |

| 16.0  | Output Compare                                                                | 193 |

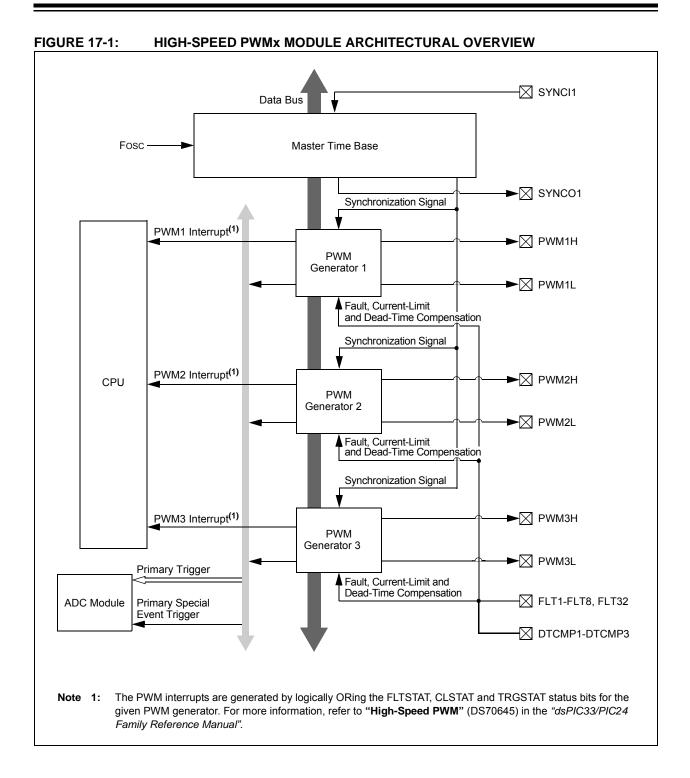

| 17.0  | High-Speed PWM Module                                                         | 199 |

| 18.0  |                                                                               | 221 |

| 19.0  |                                                                               |     |

| 20.0  | Single-Edge Nibble Transmission (SENT)                                        | 237 |

| 21.0  | Universal Asynchronous Receiver Transmitter (UART)                            |     |

| 22.0  | Controller Area Network (CAN) Module (dsPIC33EVXXXGM10X Devices Only)         | 253 |

| 23.0  | Charge Time Measurement Unit (CTMU)                                           | 279 |

| 24.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                               |     |

| 25.0  | Op Amp/Comparator Module                                                      | 301 |

| 26.0  | Comparator Voltage Reference                                                  | 313 |

|       | Special Features                                                              |     |

| 28.0  | Instruction Set Summary                                                       | 327 |

| 29.0  |                                                                               |     |

|       |                                                                               |     |

|       | High-Temperature Electrical Characteristics                                   |     |

|       | Characteristics for Industrial/Extended Temperature Devices (-40°C to +125°C) |     |

| 33.0  | Characteristics for High-Temperature Devices (+150°C)                         | 439 |

|       | Packaging Information                                                         |     |

|       | endix A: Revision History                                                     |     |

|       | Х                                                                             |     |

|       | Microchip Web Site                                                            |     |

|       | omer Change Notification Service                                              |     |

|       | omer Support                                                                  |     |

| Produ | luct Identification System                                                    | 497 |

| TABLE 1-1: PINO                   |             | D DESC         | RIPTI    | ONS (CONTINUED)                                                            |

|-----------------------------------|-------------|----------------|----------|----------------------------------------------------------------------------|

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS      | Description                                                                |

| SCK2                              | I/O         | ST             | Yes      | Synchronous serial clock input/output for SPI2.                            |

| SDI2                              | I           | ST             | Yes      | SPI2 data in.                                                              |

| SDO2                              | 0           | —              | Yes      | SPI2 data out.                                                             |

| SS2                               | I/O         | ST             | Yes      | SPI2 slave synchronization or frame pulse I/O.                             |

| SCL1                              | I/O         | ST             | No       | Synchronous serial clock input/output for I2C1.                            |

| SDA1                              | I/O         | ST             | No       | Synchronous serial data input/output for I2C1.                             |

| ASCL1                             | I/O         | ST             | No       | Alternate synchronous serial clock input/output for I2C1.                  |

| ASDA1                             | I/O         | ST             | No       | Alternate synchronous serial data input/output for I2C1.                   |

| C1RX                              | I           | ST             | Yes      | CAN1 bus receive pin.                                                      |

| C1TX                              | 0           | —              | Yes      | CAN1 bus transmit pin.                                                     |

| SENT1TX                           | 0           | —              | Yes      | SENT1 transmit pin.                                                        |

| SENT1RX                           | 1           | —              | Yes      | SENT1 receive pin.                                                         |

| SENT2TX                           | 0           | —              | Yes      | SENT2 transmit pin.                                                        |

| SENT2RX                           | I.          | —              | Yes      | SENT2 receive pin.                                                         |

| CVREF                             | 0           | Analog         | No       | Comparator Voltage Reference output.                                       |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3- | I           | Analog         | No       | Comparator 1 inputs.                                                       |

| C1OUT                             | 0           | _              | Yes      | Comparator 1 output.                                                       |

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3- | I           | Analog         | No       | Comparator 2 inputs.                                                       |

| C2OUT                             | 0           | —              | Yes      | Comparator 2 output.                                                       |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3- | I           | Analog         | No       | Comparator 3 inputs.                                                       |

| C3OUT                             | 0           |                | Yes      | Comparator 3 output.                                                       |

| C4IN1+, C4IN2-,<br>C4IN1-, C4IN3- | Ι           | Analog         | No       | Comparator 4 inputs.                                                       |

| C4OUT                             | 0           | —              | Yes      | Comparator 4 output.                                                       |

| C5IN1+, C5IN2-,<br>C5IN1-, C5IN3- | I           | Analog         | No       | Comparator 5 inputs.                                                       |

| C5OUT                             | 0           | —              | Yes      | Comparator 5 output.                                                       |

| FLT1-FLT2                         | 1           | ST             | Yes      | PWM Fault Inputs 1 and 2.                                                  |

| FLT3-FLT8                         | 1           | ST             | NO       | PWM Fault Inputs 3 to 8.                                                   |

| FLT32                             | 1           | ST             | NO       | PWM Fault Input 32.                                                        |

| DTCMP1-DTCMP3                     | 1           | ST             | Yes      | PWM Dead-Time Compensation Inputs 1 to 3.                                  |

| PWM1L-PWM3L                       | 0           | _              | No       | PWM Low Outputs 1 to 3.                                                    |

| PWM1H-PWM3H                       | 0           | —              | No       | PWM High Outputs 1 to 3.                                                   |

| SYNCI1                            | 1           | ST             | Yes      | PWM Synchronization Input 1.                                               |

| SYNCO1                            | 0           | —              | Yes      | PWM Synchronization Output 1.                                              |

| PGED1                             | I/O         | ST             | No       | Data I/O pin for Programming/Debugging Communication Channel 1.            |

| PGEC1                             | 1           | ST             | No       | Clock input pin for Programming/Debugging Communication Channel 1          |

| PGED2                             | I/O         | ST             | No       | Data I/O pin for Programming/Debugging Communication Channel 2.            |

| PGEC2                             | 1           | ST             | No       | Clock input pin for Programming/Debugging Communication Channel 2          |

| PGED3                             | I/O         | ST             | No       | Data I/O pin for Programming/Debugging Communication Channel 3.            |

| PGEC3                             | I           | ST             | No       | Clock input pin for Programming/Debugging Communication Channel            |

| MCLR                              | I/P         | ST             | No       | Master Clear (Reset) input. This pin is an active-low Reset to the device. |

| Legend: CMOS = C                  |             |                |          | or output Analog = Analog input P = Power                                  |

| ST = Schm                         | itt Triaa   | er input w     | /ith CIV | IOS levels O = Output I = Input                                            |

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) | ) |

|------------|-------------------------|-------------|---|

|            |                         |             | 1 |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select Analog = Analog inputP = PoweO = OutputI = InputTTL = TTL input buffer

|             | ••    |           | •                      |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

|-------------|-------|-----------|------------------------|--------|--------|--------|--------|------------|-------------|---------------|---------------|-------------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | Addr. | Bit 15    | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7         | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100  |           |                        |        |        |        |        |            | Tim         | ner1 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR1         | 0102  |           |                        |        |        |        |        |            | Peri        | od Register   | 1             |             |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON       | _                      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | TSYNC | TCS   | —     | 0000          |

| TMR2        | 0106  |           |                        |        |        |        |        |            | Tim         | ner2 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108  |           |                        |        |        |        | Time   | er3 Holdin | ig Register | · (For 32-bit | timer operat  | tions only) |        |       |       |       |       | 0000          |

| TMR3        | 010A  |           |                        |        |        |        |        |            | Tim         | ner3 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR2         | 010C  |           |                        |        |        |        |        |            | Peri        | od Register   | 2             |             |        |       |       |       |       | FFFF          |

| PR3         | 010E  |           |                        |        |        |        |        |            | Peri        | od Register   | 3             |             |        |       |       |       |       | FFFF          |

| T2CON       | 0110  | TON       | _                      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | T32   | _     | TCS   | —     | 0000          |

| T3CON       | 0112  | TON       | _                      | TSIDL  | _      | _      | _      | _          | —           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |           |                        |        |        |        |        |            | Tim         | ner4 Registe  | r             |             |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116  |           |                        |        |        |        | Т      | imer5 Hol  | ding Regis  | ster (For 32- | bit operation | ns only)    |        |       |       |       |       | 0000          |

| TMR5        | 0118  |           |                        |        |        |        |        |            | Tim         | ner5 Registe  | r             |             |        |       |       |       |       | 0000          |

| PR4         | 011A  |           |                        |        |        |        |        |            | Peri        | od Register   | 4             |             |        |       |       |       |       | FFFF          |

| PR5         | 011C  |           | Period Register 5 FFFF |        |        |        |        |            |             |               | FFFF          |             |        |       |       |       |       |               |

| T4CON       | 011E  | TON       | _                      | TSIDL  | —      | —      | —      | —          | —           | —             | TGATE         | TCKPS1      | TCKPS0 | T32   | —     | TCS   | —     | 0000          |

| T5CON       | 0120  | TON       | _                      | TSIDL  | _      | _      | _      | _          | _           | _             | TGATE         | TCKPS1      | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| Lonondi     |       | nlamantad | 1 1-                   |        |        |        |        |            |             |               |               |             |        |       |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: PERIPHERAL INPUT REMAP REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14   | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7      | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|----------|----------|----------|----------|----------|----------|----------|----------|------------|------------|----------|----------|----------|----------|----------|----------|---------------|

| RPINR0      | 06A0  |          |          |          | INT1F    | R<7:0>   |          |          |          |            |            | —        | -        | _        | _        |          | —        | 0000          |

| RPINR1      | 06A2  | _        | _        | _        | _        | _        | _        | _        | _        |            |            |          | INT2R    | <7:0>    |          |          |          | 0000          |

| RPINR3      | 06A6  | _        | _        | _        | _        | _        | _        | _        | _        | T2CKR<7:0> |            |          |          |          |          | 0000     |          |               |

| RPINR7      | 06AE  | IC2R7    | IC2R6    | IC2R5    | IC2R4    | IC2R3    | IC2R2    | IC2R1    | IC2R0    | IC1R7      | IC1R6      | IC1R5    | IC1R4    | IC1R3    | IC1R2    | IC1R1    | IC1R0    | 0000          |

| RPINR8      | 06B0  | IC4R7    | IC4R6    | IC4R5    | IC4R4    | IC4R3    | IC4R2    | IC4R1    | IC4R0    | IC3R7      | IC3R6      | IC3R5    | IC3R4    | IC3R3    | IC3R2    | IC3R1    | IC3R0    | 0000          |

| RPINR11     | 06B6  | _        | _        | _        | _        | _        | _        | _        | _        |            |            |          | OCFA     | R<7:0>   |          |          |          | 0000          |

| RPINR12     | 06B8  | FLT2R7   | FLT2R6   | FLT2R5   | FLT2R4   | FLT2R3   | FLT2R2   | FLT2R1   | FLT2R0   | FLT1R7     | FLT1R6     | FLT1R5   | FLT1R4   | FLT1R3   | FLT1R2   | FLT1R1   | FLT1R0   | 0000          |

| RPINR18     | 06C4  | _        | _        | _        | —        | _        | _        | _        | _        |            |            |          | U1RXF    | R<7:0>   |          |          |          | 0000          |

| RPINR19     | 06C6  | _        | _        | _        | _        | _        | _        | _        | _        |            | U2RXR<7:0> |          |          |          |          |          | 0000     |               |

| RPINR22     | 06CC  | SCK2R7   | SCK2R6   | SCK2R5   | SCK2R4   | SCK2R3   | SCK2R2   | SCK2R1   | SCK2R0   | SDI2R7     | SDI2R6     | SDI2R5   | SDI2R4   | SDI2R3   | SDI2R2   | SDI2R1   | SDI2R0   | 0000          |

| RPINR23     | 06CE  | _        | _        | _        | _        | _        | _        | _        | _        |            |            |          | SS2R     | <7:0>    |          |          |          | 0000          |

| RPINR26     | 06D4  | _        | _        | _        | _        | _        | _        | _        | _        |            |            |          | C1RXR    | <7:0>(1) |          |          |          | 0000          |

| RPINR37     | 06EA  |          |          |          | SYNCI    | IR<7:0>  |          |          |          | _          | —          | —        | _        | _        | _        | _        | _        | 0000          |

| RPINR38     | 06EC  |          |          |          | DTCMP    | 1R<7:0>  |          |          |          |            | -          | _        | _        | _        | _        |          | _        | 0000          |

| RPINR39     | 06EE  | DTCMP3R7 | DTCMP3R6 | DTCMP3R5 | DTCMP3R4 | DTCMP3R3 | DTCMP3R2 | DTCMP3R1 | DTCMP3R0 | DTCMP2R7   | DTCMP2R6   | DTCMP2R5 | DTCMP2R4 | DTCMP2R3 | DTCMP2R2 | DTCMP2R1 | DTCMP2R0 | 0000          |

| RPINR44     | 06F8  |          |          |          | SENT1    | R<7:0>   |          |          |          |            | -          | —        | —        | —        | _        |          | —        | 0000          |

| RPINR45     | 06FA  | _        | _        | _        | —        | —        | _        | _        | —        |            |            | •        | SENT2    | R<7:0>   |          |          | •        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

#### TABLE 4-18: DMT REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|-------|---------|---------|-------|----------|-------|-------|-------|-------|--------|---------------|

| DMTCON      | 0700  | ON     |        | _      |        |        | -      | —     |         | _       | _     | —        | _     | —     |       | _     | —      | 0000          |

| DMTPRECLR   | 0704  |        |        |        | STEP1  | <7:0>  |        |       |         | _       | _     | _        | _     | _     | _     | _     | —      | 0000          |

| DMTCLR      | 0708  | _      | _      | _      | _      | _      | _      | _     | _       |         |       |          | STEP2 | <7:0> |       |       |        | 0000          |

| DMTSTAT     | 070C  | _      | _      | _      | _      | _      | _      | _     | _       | BAD1    | BAD2  | DMTEVENT |       | _     | _     | _     | WINOPN | 0000          |

| DMTCNTL     | 0710  |        |        |        |        |        |        |       | COUNTER | <15:0>  |       |          |       |       |       |       |        | 0000          |

| DMTCNTH     | 0712  |        |        |        |        |        |        | (     | COUNTER | <31:16> |       |          |       |       |       |       |        | 0000          |

| DMTHOLDREG  | 0714  |        |        |        |        |        |        |       | UPRCNT  | <15:0>  |       |          |       |       |       |       |        | 0000          |

| DMTPSCNTL   | 0718  |        |        |        |        |        |        |       | PSCNT<  | 15:0>   |       |          |       |       |       |       |        | 0000          |

| DMTPSCNTH   | 071A  |        |        |        |        |        |        |       | PSCNT<  | 31:16>  |       |          |       |       |       |       |        | 0000          |

| DMTPSINTVL  | 071C  |        |        |        |        |        |        |       | PSINTV< | 15:0>   |       |          |       |       |       |       |        | 0000          |

| DMTPSINTVH  | 071E  |        |        |        |        |        |        |       | PSINTV< | 31:16>  |       |          |       |       |       |       |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory, program a row and to program two instruction words at a time. See Table 1 in the "dsPIC33EVXXXGM00X/10X Product Families" section for the page sizes of each device.memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to era

The Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user application to erase a page of program memory, which consists of eight rows (512 instructions) at a time, and to program one row or two adjacent words at a time. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively. Table 30-13 in **Section 30.0 "Electrical Characteristics"** lists the typical erase and programming times.

The basic sequence for RTSP word programming is to use the TBLWTL and TBLWTH instructions to load two of the 24-bit instructions into the write latches found in configuration memory space. See Figure 4-1 to Figure 4-5 for write latch addresses. Programming is performed by unlocking and setting the control bits in the NVMCON register.

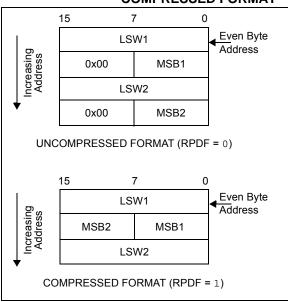

Row programming is performed by loading 192 bytes into data memory and then loading the address of the first byte in that row into the NVMSRCADR register. Once the write has been initiated, the device will automatically load the write latches and increment the NVMSRCADR and the NVMADR(U) registers until all bytes have been programmed. The RPDF bit (NVMCON<9>) selects the format of the stored data in RAM to be either compressed or uncompressed. See Figure 5-2 for data formatting. Compressed data helps to reduce the amount of required RAM by using the upper byte of the second word for the MSB of the second instruction.

For more information on erasing and programming the Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

- Note 1: Before reprogramming either of the two words in a double-word pair, the user must erase the Flash memory page in which it is located.

- 2: Before reprogramming any word in a row, the user must erase the Flash memory page in which it is located.

#### FIGURE 5-2: UNCOMPRESSED/ COMPRESSED FORMAT

#### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, erase the page that contains the desired address of the location the user wants to change. For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **"Flash Programming"** (DS70609) in the *"dsPIC33/PIC24 Family Reference Manual"* for details and code examples on programming using RTSP.

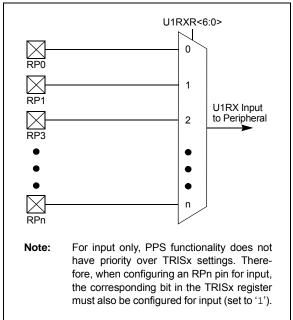

For example, Figure 11-2 shows the remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.5.4.1 Virtual Connections

dsPIC33EVXXXGM00X/10X family devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module").

These devices provide six virtual output pins (RPV0-RPV5) that correspond to the outputs of six peripheral pin output remapper blocks (RP176-RP181). The six virtual remapper outputs (RP176-RP181) are not connected to actual pins. The six virtual pins may be read by any of the input remappers as inputs, RP176-RP181. These virtual pins can be used to connect the internal peripherals, whose signals are of significant use to the other peripherals, but these output signals are not present on the device pin.

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<7:0> bits of the RPINR12 register to the value of 'b0000001', the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

# dsPIC33EVXXXGM00X/10X FAMILY

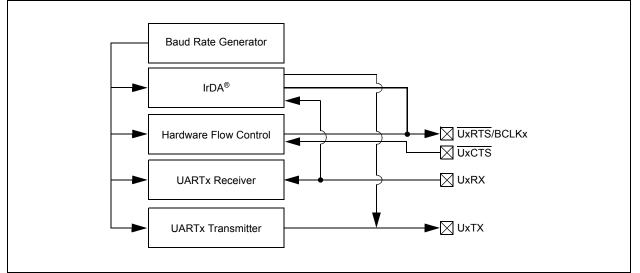

## 21.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EVXXXGM00X/10X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a

hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

| Note: | Hardware flow control using UxRTS and   |

|-------|-----------------------------------------|

|       | UxCTS is not available on all pin count |

|       | devices. See the "Pin Diagrams" section |

|       | for availability.                       |

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UART Error Conditions

#### FIGURE 21-1: UARTX SIMPLIFIED BLOCK DIAGRAM

| U-0           | U-0                                  | U-0                                | R-0      | R-0               | R-0              | R-0             | R-0     |  |  |  |  |

|---------------|--------------------------------------|------------------------------------|----------|-------------------|------------------|-----------------|---------|--|--|--|--|

| 0-0           | 0-0                                  | 0-0                                | FILHIT4  | FILHIT3           | FILHIT2          | FILHIT1         | FILHIT0 |  |  |  |  |

| <br>it 15     |                                      |                                    |          | FILHITS           | FILHI12          |                 |         |  |  |  |  |

| JIL 10        |                                      |                                    |          |                   |                  |                 | bit     |  |  |  |  |

| U-0           | R-1                                  | R-0                                | R-0      | R-0               | R-0              | R-0             | R-0     |  |  |  |  |

|               | ICODE6                               | ICODE5                             | ICODE4   | ICODE3            | ICODE2           | ICODE1          | ICODE0  |  |  |  |  |

| bit 7         | ICODEC                               | ICODEC                             | ICODE    | ICODEO            | ICODEZ           | ICODET          | bit     |  |  |  |  |

|               |                                      |                                    |          |                   |                  |                 |         |  |  |  |  |

| Legend:       |                                      |                                    |          |                   |                  |                 |         |  |  |  |  |

| R = Readable  | e bit                                | W = Writable                       | bit      | U = Unimplem      | nented bit, read | <b>i as</b> '0' |         |  |  |  |  |

| -n = Value at | POR                                  | '1' = Bit is set                   |          | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |

|               |                                      |                                    |          |                   |                  |                 |         |  |  |  |  |

| bit 15-13     | -                                    | ted: Read as '                     |          |                   |                  |                 |         |  |  |  |  |

| bit 12-8      |                                      | Filter Hit Num                     | ber bits |                   |                  |                 |         |  |  |  |  |

|               | 10000-11111<br>01111 = Filte         |                                    |          |                   |                  |                 |         |  |  |  |  |

|               | •                                    | 1 10                               |          |                   |                  |                 |         |  |  |  |  |

|               | •                                    |                                    |          |                   |                  |                 |         |  |  |  |  |

|               | •<br>00001 = Filte                   | r 1                                |          |                   |                  |                 |         |  |  |  |  |

|               | 000001 – Filte                       |                                    |          |                   |                  |                 |         |  |  |  |  |

| bit 7         | Unimplemented: Read as '0'           |                                    |          |                   |                  |                 |         |  |  |  |  |

| bit 6-0       | ICODE<6:0>: Interrupt Flag Code bits |                                    |          |                   |                  |                 |         |  |  |  |  |

|               | 1000101-111                          | 11111 = Resei                      | rved     |                   |                  |                 |         |  |  |  |  |

|               |                                      | IFO almost full                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | eceiver overflo<br>/ake-up interru |          |                   |                  |                 |         |  |  |  |  |

|               | 1000001 = E                          |                                    | P        |                   |                  |                 |         |  |  |  |  |

|               | 1000000 <b>= N</b>                   | o interrupt                        |          |                   |                  |                 |         |  |  |  |  |

|               | •                                    |                                    |          |                   |                  |                 |         |  |  |  |  |

|               | •                                    |                                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | 11111 <b>= Rese</b> i              |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | B15 buffer inte                    | errupt   |                   |                  |                 |         |  |  |  |  |

|               | •                                    |                                    |          |                   |                  |                 |         |  |  |  |  |

|               | •                                    |                                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | B9 buffer inter                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | B8 buffer inter<br>RB7 buffer inte |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | RB6 buffer inte                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | RB5 buffer inte                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | RB4 buffer inte                    |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | RB3 buffer inte<br>RB2 buffer inte |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | вых нинегийе                       |          |                   |                  |                 |         |  |  |  |  |

|               |                                      | RB1 buffer inte                    |          |                   |                  |                 |         |  |  |  |  |

#### REGISTER 22-3: CxVEC: CANx INTERRUPT CODE REGISTER

#### REGISTER 22-14: CxBUFPNT3: CANx FILTERS 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                | R/W-0            | R/W-0             | R/W-0                              | R/W-0                         | R/W-0           | R/W-0  |  |  |

|---------------|----------------------|------------------|-------------------|------------------------------------|-------------------------------|-----------------|--------|--|--|

| F11BP3        | F11BP2               | F11BP1           | F11BP0            | F10BP3                             | F10BP2                        | F10BP1          | F10BP0 |  |  |

| bit 15        |                      |                  |                   |                                    |                               |                 | bit 8  |  |  |

|               |                      |                  |                   |                                    |                               |                 |        |  |  |

| R/W-0         | R/W-0                | R/W-0            | R/W-0             | R/W-0                              | R/W-0                         | R/W-0           | R/W-0  |  |  |

| F9BP3         | F9BP2                | F9BP1            | F9BP0             | F8BP3                              | F8BP2                         | F8BP1           | F8BP0  |  |  |

| bit 7         |                      |                  |                   |                                    |                               | •               | bit 0  |  |  |

|               |                      |                  |                   |                                    |                               |                 |        |  |  |

| Legend:       |                      |                  |                   |                                    |                               |                 |        |  |  |

| R = Readable  | e bit                | W = Writable     | bit               | U = Unimplemented bit, read as '0' |                               |                 |        |  |  |

| -n = Value at | POR                  | '1' = Bit is set |                   | '0' = Bit is cle                   | ared                          | x = Bit is unkr | nown   |  |  |

|               |                      |                  |                   |                                    |                               |                 |        |  |  |

| bit 15-12     | F11BP<3:0>:          | RX Buffer Mas    | sk for Filter 11  | bits                               |                               |                 |        |  |  |

|               |                      | hits received in |                   |                                    |                               |                 |        |  |  |

|               | 1110 <b>= Filter</b> | hits received in | RX Buffer 14      | ł                                  |                               |                 |        |  |  |

|               | •                    |                  |                   |                                    |                               |                 |        |  |  |

|               | •                    |                  |                   |                                    |                               |                 |        |  |  |

|               | 0001 = Filter        | hits received in | RX Buffer 1       |                                    |                               |                 |        |  |  |

|               | 0000 = Filter        | hits received in | NRX Buffer 0      |                                    |                               |                 |        |  |  |

| bit 11-8      | F10BP<3:0>           | RX Buffer Ma     | sk for Filter 10  | ) bits (same va                    | lues as bits 15- <sup>,</sup> | 12)             |        |  |  |

| bit 7-4       | F9BP<3:0>:           | RX Buffer Masl   | c for Filter 9 b  | its (same value                    | es as bits 15-12)             | )               |        |  |  |

| bit 3-0       | F8BP<3:0>:           | RX Buffer Masl   | c for Filter 8 bi | its (same value                    | es as bits 15-12)             | )               |        |  |  |

|               |                      |                  |                   | •                                  | ,                             |                 |        |  |  |

| R/W-0           | R/W-0                                                        | R/W-0                                              | R/W-0                                                 | R/W-0                            | R/W-0            | R/W-0           | R/W-0   |

|-----------------|--------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|----------------------------------|------------------|-----------------|---------|

| F15MSK1         | F15MSK0                                                      | F14MSK1                                            | F14MSK0                                               | F13MSK'                          | F13MSK0          | F12MSK1         | F12MSK0 |

| bit 15          |                                                              |                                                    |                                                       |                                  |                  |                 | bit 8   |

| R/W-0           | R/W-0                                                        | R/W-0                                              | R/W-0                                                 | R/W-0                            | R/W-0            | R/W-0           | R/W-0   |

| F11MSK1         | F11MSK0                                                      | F10MSK1                                            | F10MSK0                                               | F9MSK1                           | F9MSK0           | F8MSK1          | F8MSK0  |

| bit 7           |                                                              |                                                    |                                                       |                                  |                  | 1               | bit (   |

| Legend:         |                                                              |                                                    |                                                       |                                  |                  |                 |         |

| R = Readable    | bit                                                          | W = Writable                                       | bit                                                   | U = Unimpler                     | mented bit, read | <b>l as</b> '0' |         |

| -n = Value at I | POR                                                          | '1' = Bit is set                                   |                                                       | '0' = Bit is cle                 | ared             | x = Bit is unkr | nown    |

| bit 15-14       | 11 = Reserve<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta | nce Mask 2 reg<br>nce Mask 1 reg<br>nce Mask 0 reg | gisters contain<br>gisters contain<br>gisters contain | the mask<br>the mask<br>the mask |                  |                 |         |

| bit 13-12       |                                                              |                                                    |                                                       | ,                                | es as bits 15-14 | ,               |         |

| bit 11-10       |                                                              |                                                    |                                                       | -                                | es as bits 15-14 |                 |         |

| bit 9-8         |                                                              |                                                    |                                                       |                                  | es as bits 15-14 |                 |         |

| bit 7-6         |                                                              |                                                    |                                                       | -                                | es as bits 15-14 | -               |         |

| bit 5-4         | F10MSK<1:0                                                   | >: Mask Sourc                                      | e for Filter 10                                       | bit (same valu                   | es as bits 15-14 | +)              |         |

| bit 3-2         | F9MSK<1:0>                                                   | : Mask Source                                      | for Filter 9 bit                                      | (same values                     | as bits 15-14)   |                 |         |

|                 |                                                              |                                                    |                                                       |                                  |                  |                 |         |

#### REGISTER 22-19: CxFMSKSEL2: CANx FILTERS 15-8 MASK SELECTION REGISTER 2

bit 1-0 **F8MSK<1:0>:** Mask Source for Filter 8 bit (same values as bits 15-14)

## 26.2 Comparator Voltage Reference Registers

## REGISTER 26-1: CVR1CON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0  | R/W-0 | U-0   | U-0   | R/W-0 | R/W-0   | U-0   | U-0   |

|--------|-------|-------|-------|-------|---------|-------|-------|

| CVREN  | CVROE | —     | _     | CVRSS | VREFSEL | —     | _     |

| bit 15 |       |       |       |       |         |       | bit 8 |

|        |       |       |       |       |         |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|        | CVR6  | CVR5  | CVR4  | CVR3  | CVR2    | CVR1  | CVR0  |

| bit 7  |       |       |       |       |         |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15    | CVREN: Comparator Voltage Reference Enable bit                      |

|-----------|---------------------------------------------------------------------|

|           | 1 = Comparator voltage reference circuit is powered on              |

|           | 0 = Comparator voltage reference circuit is powered down            |

| bit 14    | CVROE: Comparator Voltage Reference Output Enable (CVREF10 Pin) bit |

|           | 1 = Voltage level is output on the CVREF10 pin                      |

|           | 0 = Voltage level is disconnected from the CVREF10 pin              |

| bit 13-12 | Unimplemented: Read as '0'                                          |

| bit 11    | CVRSS: Comparator Voltage Reference Source Selection bit            |

|           | 1 = Comparator reference source, CVRSRC = CVREF+ – AVSS             |

|           | 0 = Comparator reference source, CVRSRC = AVDD – AVSS               |

| bit 10    | VREFSEL: Voltage Reference Select bit                               |

|           | 1 = CVREFIN = CVREF+                                                |

|           | 0 = CVREFIN is generated by the resistor network                    |

| bit 9-7   | Unimplemented: Read as '0'                                          |

| bit 6-0   | CVR<6:0>: Comparator Voltage Reference Value Selection bits         |

|           | 1111111 = 127/128 x VREF input voltage                              |

|           | •                                                                   |

|           | •                                                                   |

|           | •                                                                   |

|           | 0000000 = <b>0.0 volts</b>                                          |

#### TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CHARACTERISTICS |                |                                                              | (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                        |      |               |       |                                                                             |

|--------------------|----------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol         | Characteristic <sup>(1)</sup>                                |                                                                                                                                                                  | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TB10               | T⊤xH           | TxCK High<br>Time                                            | Synchronous<br>mode                                                                                                                                              | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB11               | ΤτxL           | TxCK Low<br>Time                                             | Synchronous<br>mode                                                                                                                                              | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous<br>mode                                                                                                                                              | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = Prescaler Value<br>(1, 8, 64, 256)                                      |

| TB20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                  | 0.75 Tcy + 40                          |      | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |               |      |               |       |                                        |

|--------------------|----------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------|-------|----------------------------------------|

| Param<br>No.       | Symbol         | Characteristic <sup>(1)</sup>                                |                                                                                                                                                                                                                                                                                     | Min.          | Тур. | Max.          | Units | Conditions                             |

| TC10               | ТтхН           | TxCK High<br>Time                                            | Synchronous                                                                                                                                                                                                                                                                         | Tcy + 20      |      | _             | ns    | Must also meet<br>Parameter TC15       |

| TC11               | ΤτxL           | TxCK Low<br>Time                                             | Synchronous                                                                                                                                                                                                                                                                         | Tcy + 20      | _    | —             | ns    | Must also meet<br>Parameter TC15       |

| TC15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous,<br>with Prescaler                                                                                                                                                                                                                                                      | 2 Tcy + 40    | _    | —             | ns    | N = Prescaler Value<br>(1, 8, 64, 256) |

| TC20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                                                                                                                                     | 0.75 Tcy + 40 | _    | 1.75 Tcy + 40 | ns    |                                        |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

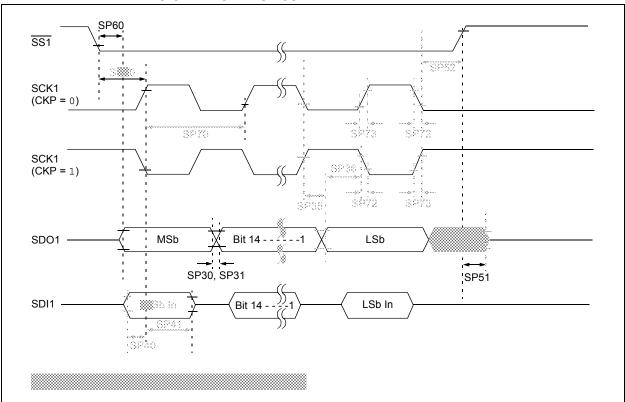

#### FIGURE 30-25: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of the dsPIC33EVXXXGM00X/10X family electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EVXXXGM00X/10X family high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                | 40°C to +150°C |

|--------------------------------------------------------------|----------------|

| Storage temperature                                          | 65°C to +160°C |

| Voltage on VDD with respect to Vss                           | 0.3V to +6.0V  |

| Maximum current out of Vss pin                               | 350 mA         |

| Maximum current into Vod pin <sup>(3)</sup>                  | 350 mA         |

| Maximum junction temperature                                 |                |

| Maximum current sunk by any I/O pin                          | 20 mA          |

| Maximum current sourced by I/O pin                           | 18 mA          |

| Maximum current sunk by all ports combined                   | 200 mA         |

| Maximum current sourced by all ports combined <sup>(3)</sup> | 200 mA         |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

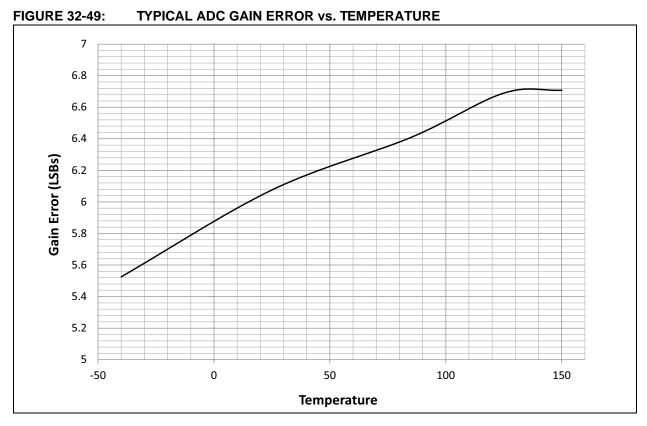

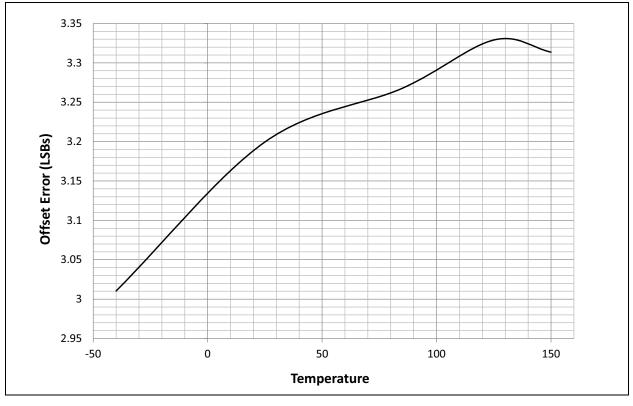

#### 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

## 34.0 PACKAGING INFORMATION

#### 34.1 Package Marking Information

#### 28-Lead SPDIP (.300")

#### 28-Lead SOIC (.300")

#### 28-Lead SSOP

#### 28-Lead QFN-S (6x6x0.9 mm)

Example

| Legenc | I: XXX<br>Y<br>YY<br>WW<br>NNN | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code |

|--------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                     | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                            |

#### Example

## Example

#### Example

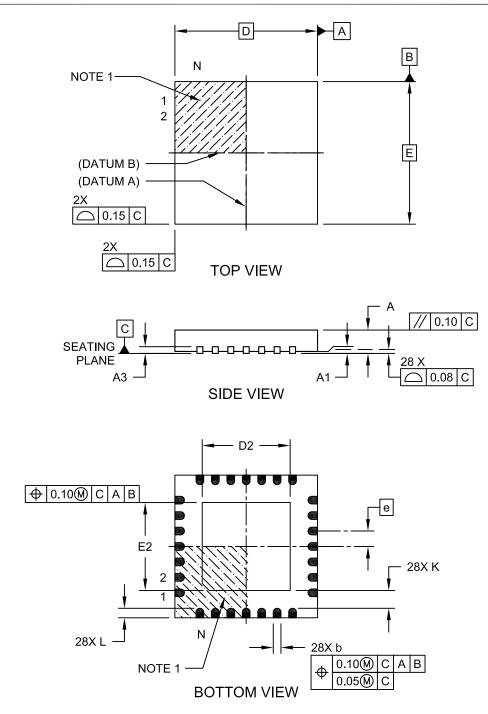

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2

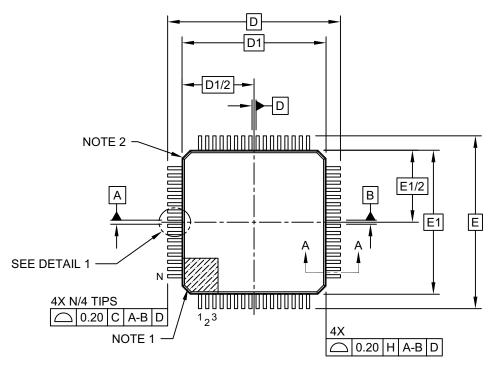

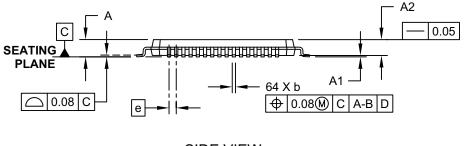

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0975-5