Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 36x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm006t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.3.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x2FFF, is always accessible regardless of the contents of the Data Space Page registers; it is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x002FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of Base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, the DSRPAG and DSWPAG registers are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

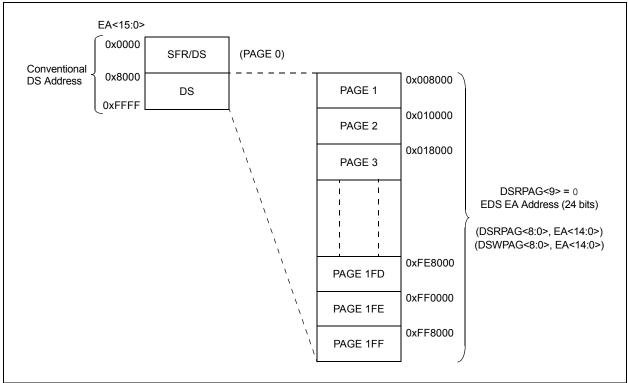

FIGURE 4-12: EDS MEMORY MAP

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where the base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF of the Data Space, will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-12.

For more information on the PSV page access using Data Space Page registers, refer to **Section 5.0 "Program Space Visibility from Data Space"** in **"dsPIC33E/PIC24E Program Memory"** (DS70000613) of the *"dsPIC33/PIC24 Family Reference Manual"*.

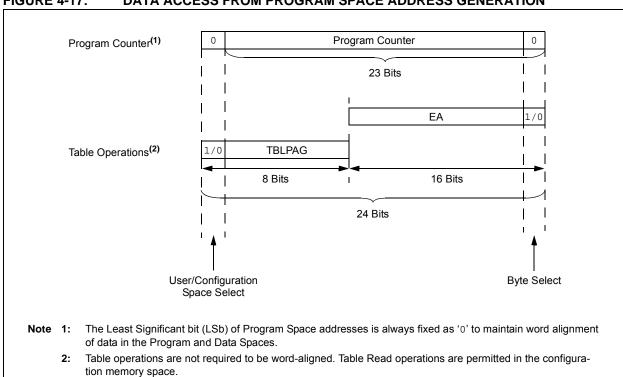

### FIGURE 4-17: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 3 | SLEEP: Wake-up from Sleep Flag bit     |

|-------|----------------------------------------|

|       | 1 = Device has been in Sleep mode      |

|       | 0 = Device has not been in Sleep mode  |

| bit 2 | IDLE: Wake-up from Idle Flag bit       |

|       | 1 = Device was in Idle mode            |

|       | 0 = Device was not in Idle mode        |

| bit 1 | BOR: Brown-out Reset Flag bit          |

|       | 1 = A Brown-out Reset has occurred     |

|       | 0 = A Brown-out Reset has not occurred |

| bit 0 | POR: Power-on Reset Flag bit           |

|       | 1 = A Power-on Reset has occurred      |

|       | 0 = A Power-on Reset has not occurred  |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70000600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EVXXXGM00X/10X CPU. The Interrupt Vector Table (IVT) provides 246 interrupt sources (unused sources are reserved for future use) that can be programmed with different priority levels.

The interrupt controller has the following features:

- · Interrupt Vector Table with up to 246 Vectors

- Alternate Interrupt Vector Table (AIVT)

- Up to Eight Processor Exceptions and Software Traps

- Seven User-Selectable Priority Levels

- Interrupt Vector Table (IVT) with a Unique Vector for Each Interrupt or Exception Source

- Fixed Priority within a Specified User Priority Level

- · Fixed Interrupt Entry and Return Latencies

- Software can Generate any Peripheral Interrupt

- Alternate Interrupt Vector Table (AIVT) is available if Boot Security is Enabled and AIVTEN = 1

## 7.1 Interrupt Vector Table

The dsPIC33EVXXXGM00X/10X family IVT, shown in Figure 7-2, resides in program memory, starting at location, 00004h. The IVT contains seven nonmaskable trap vectors and up to 187 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

# 7.2 Alternate Interrupt Vector Table

The Alternate Interrupt Vector Table (AIVT), shown in Figure 7-1, is available if the Boot Segment (BS) is defined, the AIVTEN bit is set in the INTCON2 register and if the AIVTDIS Configuration bit is set to '1'. The AIVT begins at the start of the last page of the Boot Segment.

# 10.2.1 SLEEP MODE

The following events occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared before entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby mode when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following events occur in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up either from Sleep mode or Idle mode.

# 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

# 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**.

| U-0     | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|--------|-------|-------|-------|

| _       | —     | —     | _     | _      | —     | —     | —     |

| bit 15  |       |       |       |        |       |       | bit 8 |

|         |       |       |       |        |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|         |       |       | U1RXI | R<7:0> |       |       |       |

| bit 7   |       |       |       |        |       |       | bit 0 |

|         |       |       |       |        |       |       |       |

| Legend: |       |       |       |        |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | <b>l as</b> '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

bit 7-0 U1RXR<7:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 10110101 = Input tied to RPI181 • • • • • • • • •

```

00000000 = Input tied to Vss

```

## REGISTER 11-9: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0                               | U-0    | U-0              | U-0   | U-0                                | U-0   | U-0                | U-0   |

|-----------------------------------|--------|------------------|-------|------------------------------------|-------|--------------------|-------|

| _                                 | _      | —                |       | _                                  | _     | _                  | _     |

| bit 15                            | -<br>- |                  |       |                                    |       |                    | bit 8 |

| R/W-0                             | R/W-0  | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|                                   |        |                  | U2R>  | (R<7:0>                            |       |                    |       |

| bit 7                             |        |                  |       |                                    |       |                    | bit 0 |

| Legend:                           |        |                  |       |                                    |       |                    |       |

| R = Readable bit W = Writable bit |        |                  | bit   | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR                 |        | '1' = Bit is set |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |

| • • • • • • • • • • • • • • • • • • • •                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| <b>U2RXR&lt;7:0&gt;:</b> Assign UART2 Receive (U2RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |

| 10110101 = Input tied to RPI181                                                                                                         |

| •                                                                                                                                       |

| •                                                                                                                                       |

| •                                                                                                                                       |

| 00000001 = Input tied to CMP1<br>00000000 = Input tied to Vss                                                                           |

|                                                                                                                                         |

# 12.1 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0              | U-0                                                                                                        | R/W-0                          | U-0             | U-0              | U-0                       | U-0                | U-0         |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------|------------------|---------------------------|--------------------|-------------|--|--|--|

| TON <sup>(1)</sup> | —                                                                                                          | TSIDL                          | —               | —                | _                         | —                  | —           |  |  |  |

| bit 15             |                                                                                                            |                                |                 |                  |                           |                    | bit 8       |  |  |  |

|                    |                                                                                                            |                                |                 |                  |                           |                    |             |  |  |  |

| U-0                | R/W-0                                                                                                      | R/W-0                          | R/W-0           | U-0              | R/W-0                     | R/W-0              | U-0         |  |  |  |

|                    | TGATE                                                                                                      | TCKPS1                         | TCKPS0          | —                | TSYNC <sup>(1)</sup>      | TCS <sup>(1)</sup> | —           |  |  |  |

| bit 7              |                                                                                                            |                                |                 |                  |                           |                    | bit 0       |  |  |  |

|                    |                                                                                                            |                                |                 |                  |                           |                    |             |  |  |  |

| Legend:            |                                                                                                            |                                |                 |                  |                           |                    |             |  |  |  |

| R = Readable       |                                                                                                            | W = Writable                   |                 | -                | mented bit, read          |                    |             |  |  |  |

| -n = Value at F    | POR                                                                                                        | '1' = Bit is set               |                 | '0' = Bit is cle | ared                      | x = Bit is unkr    | nown        |  |  |  |

|                    |                                                                                                            | o                              |                 |                  |                           |                    |             |  |  |  |

| bit 15             | TON: Timer1                                                                                                |                                |                 |                  |                           |                    |             |  |  |  |

|                    | 1 = Starts 16-<br>0 = Stops 16-                                                                            |                                |                 |                  |                           |                    |             |  |  |  |

| bit 14             | •                                                                                                          | ted: Read as '                 | י)              |                  |                           |                    |             |  |  |  |

| bit 13             | -                                                                                                          | 1 Stop in Idle N               |                 |                  |                           |                    |             |  |  |  |

| 2.1.10             |                                                                                                            | ues module op                  |                 | he device ente   | ers Idle mode             |                    |             |  |  |  |

|                    | 0 = Continues                                                                                              | s module opera                 | tion in Idle mo | ode              |                           |                    |             |  |  |  |

| bit 12-7           | Unimplemen                                                                                                 | ted: Read as '                 | כי              |                  |                           |                    |             |  |  |  |

| bit 6              | TGATE: Time                                                                                                | r1 Gated Time                  | Accumulation    | Enable bit       |                           |                    |             |  |  |  |

|                    | <u>When TCS = 1:</u><br>This bit is ignored.                                                               |                                |                 |                  |                           |                    |             |  |  |  |

|                    | When TCS =                                                                                                 |                                |                 |                  |                           |                    |             |  |  |  |

|                    |                                                                                                            | e accumulation                 |                 |                  |                           |                    |             |  |  |  |

| bit 5-4            |                                                                                                            | e accumulation                 |                 | a Salaat hita    |                           |                    |             |  |  |  |

| DIL 3-4            | 11 = 1:256                                                                                                 | : Timer1 Input                 |                 |                  |                           |                    |             |  |  |  |

|                    | 10 = 1:64                                                                                                  |                                |                 |                  |                           |                    |             |  |  |  |

|                    | 01 = 1:8                                                                                                   |                                |                 |                  |                           |                    |             |  |  |  |

|                    | 00 = 1:1                                                                                                   |                                |                 |                  |                           |                    |             |  |  |  |

| bit 3              | -                                                                                                          | ted: Read as '                 |                 |                  | (1)                       |                    |             |  |  |  |

| bit 2              |                                                                                                            | er1 External Clo               | ock Input Synd  | chronization Se  | elect bit <sup>(1)</sup>  |                    |             |  |  |  |

|                    | <u>When TCS =</u><br>1 = External c                                                                        |                                | nchronized      |                  |                           |                    |             |  |  |  |

|                    | <ol> <li>External clock input is synchronized</li> <li>External clock input is not synchronized</li> </ol> |                                |                 |                  |                           |                    |             |  |  |  |

|                    | When TCS =                                                                                                 | =                              | ,               |                  |                           |                    |             |  |  |  |

|                    | This bit is igno                                                                                           |                                |                 |                  |                           |                    |             |  |  |  |

| bit 1              |                                                                                                            | Clock Source S                 |                 |                  |                           |                    |             |  |  |  |

|                    | 1 = External c<br>0 = Internal cl                                                                          | clock is from pii<br>lock (FP) | n, T1CK (on th  | ne rising edge)  |                           |                    |             |  |  |  |

| bit 0              | Unimplemen                                                                                                 | ted: Read as '                 | כי              |                  |                           |                    |             |  |  |  |

|                    | en Timer1 is en<br>mpts by user se                                                                         |                                |                 |                  | ode (TCS = 1, T<br>nored. | SYNC = 1, TO       | N = 1), any |  |  |  |

|                    | _                                                                      |                            |                       |                  |                 |                      |                 |  |  |  |  |

|--------------------|------------------------------------------------------------------------|----------------------------|-----------------------|------------------|-----------------|----------------------|-----------------|--|--|--|--|

| R/W-0              | U-0                                                                    | R/W-0                      | U-0                   | U-0              | U-0             | U-0                  | U-0             |  |  |  |  |

| TON <sup>(1)</sup> |                                                                        | TSIDL <sup>(2)</sup>       | —                     |                  |                 | —                    | —               |  |  |  |  |

| bit 15             |                                                                        |                            |                       |                  |                 |                      | bit 8           |  |  |  |  |

|                    |                                                                        |                            |                       |                  |                 |                      |                 |  |  |  |  |

| U-0                | R/W-0                                                                  | R/W-0                      | R/W-0                 | U-0              | U-0             | R/W-0                | U-0             |  |  |  |  |

|                    | TGATE <sup>(1)</sup>                                                   | TCKPS1 <sup>(1)</sup>      | TCKPS0 <sup>(1)</sup> |                  |                 | TCS <sup>(1,3)</sup> |                 |  |  |  |  |

| bit 7              |                                                                        |                            |                       |                  |                 |                      | bit 0           |  |  |  |  |

| Legend:            |                                                                        |                            |                       |                  |                 |                      |                 |  |  |  |  |

| R = Readable       | e bit                                                                  | W = Writable               | bit                   | U = Unimpler     | mented bit, rea | <b>d as</b> '0'      |                 |  |  |  |  |

| -n = Value at      | POR                                                                    | '1' = Bit is set           |                       | '0' = Bit is cle |                 | x = Bit is unkn      | own             |  |  |  |  |

|                    |                                                                        |                            |                       |                  |                 |                      |                 |  |  |  |  |

| bit 15             | TON: Timery                                                            | On bit <sup>(1)</sup>      |                       |                  |                 |                      |                 |  |  |  |  |

|                    | 1 = Starts 16                                                          | -bit Timery                |                       |                  |                 |                      |                 |  |  |  |  |

|                    | 0 = Stops 16-                                                          | -bit Timery                |                       |                  |                 |                      |                 |  |  |  |  |

| bit 14             | Unimplemer                                                             | nted: Read as '            | 0'                    |                  |                 |                      |                 |  |  |  |  |

| bit 13             | <b>TSIDL:</b> Timery Stop in Idle Mode bit <sup>(2)</sup>              |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    |                                                                        | ues module op              |                       |                  | ers an Idle moo | de                   |                 |  |  |  |  |

|                    |                                                                        | s module opera             |                       | mode             |                 |                      |                 |  |  |  |  |

| bit 12-7           | =                                                                      | Unimplemented: Read as '0' |                       |                  |                 |                      |                 |  |  |  |  |

| bit 6              | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(1)</sup> |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    | When TCS =                                                             |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    | This bit is ignored.<br>When TCS = 0:                                  |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    | 1 = Gated time accumulation is enabled                                 |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    |                                                                        | ne accumulation            |                       |                  |                 |                      |                 |  |  |  |  |

| bit 5-4            | TCKPS<1:0>: Timery Input Clock Prescale Select bits <sup>(1)</sup>     |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    | 11 <b>= 1:256</b>                                                      |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    | 10 = 1:64                                                              |                            |                       |                  |                 |                      |                 |  |  |  |  |

|                    | 01 = 1:8<br>00 = 1:1                                                   |                            |                       |                  |                 |                      |                 |  |  |  |  |

| bit 3-2            |                                                                        | nted: Read as '            | 0'                    |                  |                 |                      |                 |  |  |  |  |

| bit 1              | -                                                                      | Clock Source S             |                       |                  |                 |                      |                 |  |  |  |  |

|                    |                                                                        | clock is from pi           |                       | e rising edge)   |                 |                      |                 |  |  |  |  |

| bit 0              |                                                                        | nted: Read as '            | 0'                    |                  |                 |                      |                 |  |  |  |  |

|                    | hen 32-bit opera<br>nctions are set t                                  |                            |                       | = 1), these bits | have no effect  | on Timery opera      | tion; all timer |  |  |  |  |

|                    |                                                                        |                            |                       |                  |                 |                      |                 |  |  |  |  |

# REGISTER 13-2: TyCON (T3CON AND T5CON) CONTROL REGISTER

2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

# 16.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70005157) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

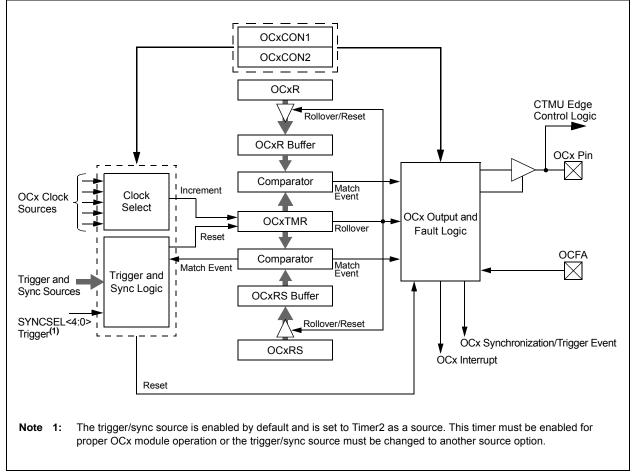

The dsPIC33EVXXXGM00X/10X family devices support up to 4 output compare modules. The output compare module can select one of eight available clock

sources for its time base. The module compares the value of the timer with the value of one or two Compare registers, depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Figure 16-1 shows a block diagram of the output compare module.

Note: For more information on OCxR and OCxRS register restrictions, refer to the "Output Compare" (DS70005157) section in the "dsPIC33/PIC24 Family Reference Manual".

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EVXXXGM00X/10X device family offers two SPI modules on a single device, SPI1 and SPI2, that are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

**Note:** In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of this module, but results in a lower maximum speed. See **Section 30.0 "Electrical Characteristics"** for more information.

The SPIx serial interface consists of the following four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

**Note:** All of the 4 pins of the SPIx serial interface must be configured as digital in the ANSELx registers.

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

## 20.3 Receive Mode

The module can be configured for receive operation by setting the RCVEN (SENTxCON1<11>) bit. The time between each falling edge is compared to SYNCMIN<15:0> (SENTxCON3<15:0>) and SYNCMAX<15:0> (SENTxCON2<15:0>), and if the measured time lies between the minimum and maximum limits, the module begins to receive data. The validated Sync time is captured in the SENTxSYNC register and the tick time is calculated. Subsequent falling edges are verified to be within the valid data width and the data is stored in the SENTxDATH/L register. An interrupt event is generated at the completion of the message and the user software should read the SENTx Data register before the reception of the next nibble. The equation for SYNCMIN<15:0> and SYNCMAX<15:0> is shown in Equation 20-3.

#### EQUATION 20-3: SYNCMIN<15:0> AND SYNCMAX<15:0> CALCULATIONS

$TTICK = TCLK \bullet (TICKTIME < 15:0 > + 1)$

FRAMETIME<15:0> = TTICK/TFRAME

SyncCount = 8 x FRCV x TTICK

SYNCMIN<15:0> = 0.8 x SyncCount

SYNCMAX<15:0> = 1.2 x SyncCount

$FRAMETIME < 15:0 \ge 122 + 27N$

$FRAMETIME < 15:0 \ge 848 + 12N$

#### Where:

$T_{FRAME}$  = Total time of the message from ms N = The number of data nibbles in message, 1-6  $F_{RCV}$  = FCY x prescaler  $T_{CLK}$  = FCY/Prescaler

For TTICK = 3.0  $\mu$ s and FCLK = 4 MHz, SYNCMIN<15:0> = 76.

| Note: | To ensure a Sync period can be identified, |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | the value written to SYNCMIN<15:0>         |  |  |  |  |  |  |  |  |

|       | must be less than the value written to     |  |  |  |  |  |  |  |  |

|       | SYNCMAX<15:0>.                             |  |  |  |  |  |  |  |  |

### 20.3.1 RECEIVE MODE CONFIGURATION

#### 20.3.1.1 Initializing the SENTx Module:

Perform the following steps to initialize the module:

- 1. Write RCVEN (SENTxCON1<11>) = 1 for Receive mode.

- 2. Write NIBCNT<2:0> (SENTxCON1<2:0>) for the desired data frame length.

- 3. Write CRCEN (SENTxCON1<8>) for hardware or software CRC validation.

- 4. Write PPP (SENTxCON1<7>) = 1 if pause pulse is present.

- 5. Write SENTxCON2 with the value of SYNCMAXx (Nominal Sync Period + 20%).

- Write SENTxCON3 with the value of SYNCMINx (Nominal Sync Period – 20%).

- 7. Enable interrupts and set interrupt priority.

- 8. Set the SNTEN (SENTxCON1<15>) bit to enable the module.

The data should be read from the SENTxDATH/L register after the completion of the CRC and before the next message frame's status nibble. The recommended method is to use the message frame completion interrupt trigger.

| U-0             | R/W-x                                                                | U-0                                | U-0              | U-0               | R/W-x            | R/W-x            | R/W-x     |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------------------------|------------------|-------------------|------------------|------------------|-----------|--|--|--|

| —               | WAKFIL                                                               |                                    | —                | _                 | SEG2PH2          | SEG2PH1          | SEG2PH0   |  |  |  |

| bit 15          |                                                                      |                                    |                  |                   |                  |                  | bit 8     |  |  |  |

|                 |                                                                      |                                    |                  |                   |                  |                  |           |  |  |  |

| R/W-x           | R/W-x                                                                | R/W-x                              | R/W-x            | R/W-x             | R/W-x            | R/W-x            | R/W-x     |  |  |  |

| SEG2PHTS        | SAM                                                                  | SEG1PH2                            | SEG1PH1          | SEG1PH0           | PRSEG2           | PRSEG1           | PRSEG0    |  |  |  |

| bit 7           |                                                                      |                                    |                  |                   |                  |                  | bit 0     |  |  |  |

| Legend:         |                                                                      |                                    |                  |                   |                  |                  |           |  |  |  |

| R = Readable    | bit                                                                  | W = Writable                       | bit              | U = Unimplen      | nented bit, read | <b>l as</b> '0'  |           |  |  |  |

| -n = Value at I | POR                                                                  | '1' = Bit is set                   |                  | '0' = Bit is clea |                  | x = Bit is unkr  | nown      |  |  |  |

|                 |                                                                      |                                    |                  |                   |                  |                  |           |  |  |  |

| bit 15          | Unimplemer                                                           | nted: Read as '                    | כ'               |                   |                  |                  |           |  |  |  |

| bit 14          | WAKFIL: Sel                                                          | lect CAN Bus Li                    | ine Filter for V | Vake-up bit       |                  |                  |           |  |  |  |

|                 | 1 = Uses CAN bus line filter for wake-up                             |                                    |                  |                   |                  |                  |           |  |  |  |

|                 |                                                                      | line filter is not                 |                  | e-up              |                  |                  |           |  |  |  |

| bit 13-11       | -                                                                    | nted: Read as '                    |                  |                   |                  |                  |           |  |  |  |

| bit 10-8        | SEG2PH<2:0>: Phase Segment 2 bits                                    |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | 111 = Length is 8 x TQ<br>•                                          |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | •                                                                    |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | •                                                                    |                                    |                  |                   |                  |                  |           |  |  |  |

| =               | 000 = Length is 1 x Tq                                               |                                    |                  |                   |                  |                  |           |  |  |  |

| bit 7           | SEG2PHTS: Phase Segment 2 Time Select bit<br>1 = Freely programmable |                                    |                  |                   |                  |                  |           |  |  |  |

|                 |                                                                      | ogrammable<br>n of SEG1PH<2        | ::0> bits or Inf | ormation Proce    | essing Time (IP  | T), whichever is | s greater |  |  |  |

| bit 6           | SAM: Sample of the CAN Bus Line bit                                  |                                    |                  |                   |                  |                  |           |  |  |  |

|                 |                                                                      | s sampled three<br>is sampled once |                  |                   |                  |                  |           |  |  |  |

| bit 5-3         | SEG1PH<2:0>: Phase Segment 1 bits                                    |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | 111 = Length is 8 x TQ                                               |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | •                                                                    |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | •                                                                    |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | 000 = Length                                                         | n is 1 x Tq                        |                  |                   |                  |                  |           |  |  |  |

| bit 2-0         | PRSEG<2:0                                                            | >: Propagation                     | Time Segmen      | t bits            |                  |                  |           |  |  |  |

|                 | 111 = Length                                                         |                                    | -                |                   |                  |                  |           |  |  |  |

|                 | •                                                                    |                                    |                  |                   |                  |                  |           |  |  |  |

|                 |                                                                      |                                    |                  |                   |                  |                  |           |  |  |  |

|                 | •                                                                    |                                    |                  |                   |                  |                  |           |  |  |  |

# REGISTER 22-10: CxCFG2: CANx BAUD RATE CONFIGURATION REGISTER 2

### REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

- bit 3 ABEN: AND Gate B Input Enable bit

- 1 = MBI is connected to AND gate

- 0 = MBI is not connected to AND gate

- bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate

- 0 = Inverted MBI is not connected to AND gate

- bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate

- bit 0 AANEN: AND Gate A Input Inverted Enable bit

- 1 = Inverted MAI is connected to AND gate

- 0 = Inverted MAI is not connected to AND gate

# 26.0 COMPARATOR VOLTAGE REFERENCE

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70000357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 26.1 Configuring the Comparator Voltage Reference

The comparator voltage reference module is controlled through the CVRxCON registers (Register 26-1 and Register 26-2). The comparator voltage reference provides a range of output voltages with 128 distinct levels. The comparator reference supply voltage can come from either VDD and Vss, or the external CVREF+ and AVss pins. The voltage source is selected by the CVRSS bit (CVRxCON<11>). The settling time of the comparator voltage reference must be considered when changing the CVREF output.

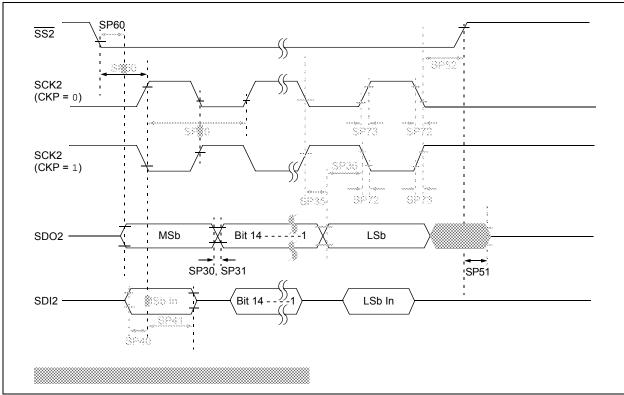

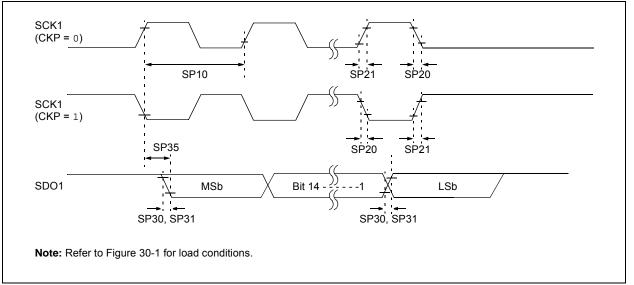

# FIGURE 30-16: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |

|----------------------|------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                              | CKE | СКР | SMP |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                                                                                                                                                                                                                                       | 0,1 | 0,1 | 0,1 |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                                                                                                                                                                                                                                       | 1   | 0,1 | 1   |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                                                                                                                                                                                                                                       | 0   | 0,1 | 1   |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                                                                                                                                                                                                                                             | 1   | 0   | 0   |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                                                                                                                                                                                                                                             | 1   | 1   | 0   |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                                                                                                                                                                                                                                             | 0   | 1   | 0   |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                                                                                                                                                                                                                                             | 0   | 0   | 0   |

## FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

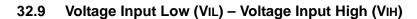

FIGURE 32-29: TYPICAL VIH/VIL vs. TEMPERATURE (GENERAL PURPOSE I/Os)

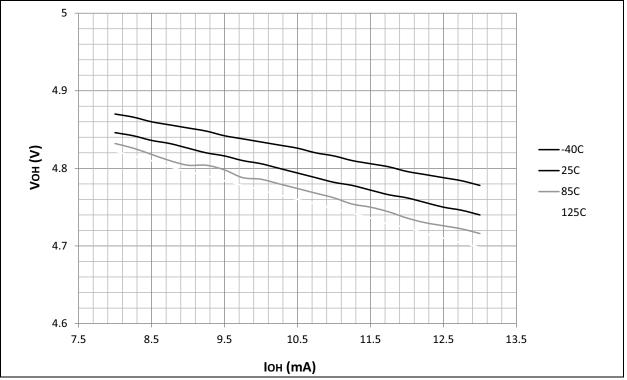

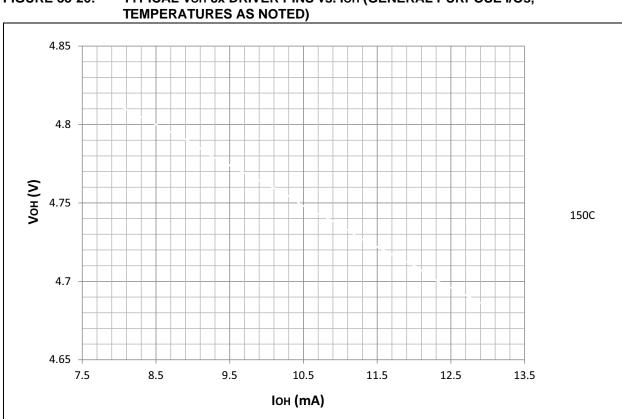

32.10 Voltage Output Low (VOL) – Voltage Output High (VOH)

# 33.10 Voltage Output Low (VOL) – Voltage Output High (VOH)

## FIGURE 33-26: TYPICAL VOH 8x DRIVER PINS vs. IOH (GENERAL PURPOSE I/Os,

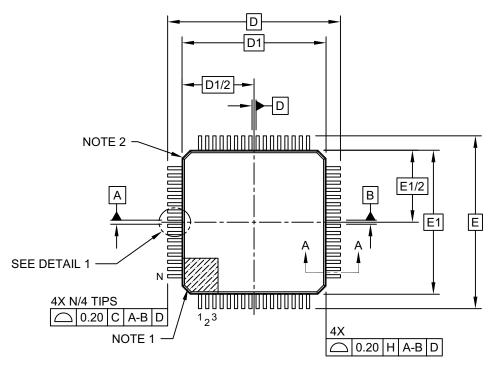

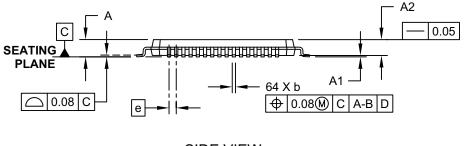

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**TOP VIEW**

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2