Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ХF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm102-e-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

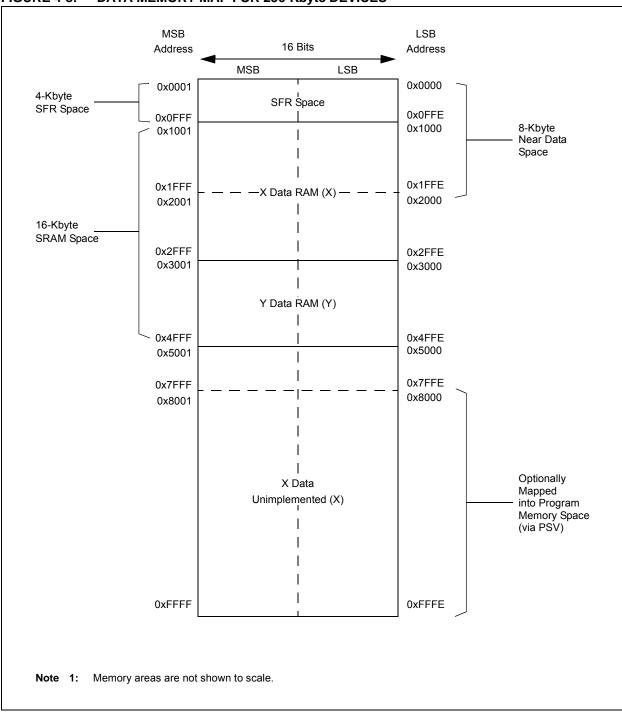

# 4.3.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the MPLAB<sup>®</sup> ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the MPLAB ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities

below that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are listed in Table 4-44.

Figure 4-13 shows the arbiter architecture.

The bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

# TABLE 4-44:DATA MEMORY BUS<br/>ARBITER PRIORITY

| Driarity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |           |  |  |  |

|--------------|-----------------------------------------|-----------|--|--|--|

| Priority     | 0x0000                                  | 0x0020    |  |  |  |

| M0 (highest) | CPU                                     | DMA       |  |  |  |

| M1           | Reserved                                | CPU       |  |  |  |

| M2           | Reserved                                | Reserved  |  |  |  |

| M3           | DMA                                     | Reserved  |  |  |  |

| M4 (lowest)  | MPLAB <sup>®</sup> ICD                  | MPLAB ICD |  |  |  |

Note 1: All other values of MSTRPR<15:0> are reserved.

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Time-out Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

- Illegal Address Mode Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 4.0 "Memory Organization" of this device data sheet for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>) that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in the other sections of this device data sheet.

**Note:** The status bits in the RCON register should be cleared after they are read. Therefore, the next RCON register value after a device Reset is meaningful.

Note: In all types of Resets, to select the device clock source, the contents of OSCCON are initialized from the FNOSCx Configuration bits in the FOSCSEL Configuration register.

#### REGISTER 8-5: DMAxSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0      | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|----------|-------|-------|-------|--------|-------|-------|-------|

| —        | —     | —     | —     | —      | —     | —     | —     |

| bit 15   |       |       |       |        | •     |       | bit 8 |

|          |       |       |       |        |       |       |       |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|          |       |       | STB<2 | 23:16> |       |       |       |

| bit 7    |       |       |       |        |       |       | bit 0 |

|          |       |       |       |        |       |       |       |

| l egend. |       |       |       |        |       |       |       |

| Legenu.           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: DMA Secondary Start Address bits (source or destination)

### REGISTER 8-6: DMAxSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0                              | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|-------------------|------------------------------------|-----------------|-------|-------|

|                                    |       |       | STB               | <15:8>                             |                 |       |       |

| bit 15                             |       |       |                   |                                    |                 |       | bit 8 |

|                                    |       |       |                   |                                    |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0             | R/W-0                              | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | STE               | 3<7:0>                             |                 |       |       |

| bit 7                              |       |       |                   |                                    |                 |       | bit 0 |

|                                    |       |       |                   |                                    |                 |       |       |

| Legend:                            |       |       |                   |                                    |                 |       |       |

| R = Readable bit W = Writable bit  |       |       | bit               | U = Unimplemented bit, read as '0' |                 |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is clea | ared                               | x = Bit is unkr | nown  |       |

bit 15-0 STB<15:0>: DMA Secondary Start Address bits (source or destination)

## **REGISTER 8-7:** DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|------------------------------------|-------|-------|-------|------------------------------------|-------|-----------------|-------|--|

|                                    |       |       | PAD   | <15:8>                             |       |                 |       |  |

| bit 15                             |       |       |       |                                    |       |                 | bit 8 |  |

|                                    |       |       |       |                                    |       |                 |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |

|                                    |       |       | PAI   | )<7:0>                             |       |                 |       |  |

| bit 7                              |       |       |       |                                    |       |                 | bit 0 |  |

|                                    |       |       |       |                                    |       |                 |       |  |

| Legend:                            |       |       |       |                                    |       |                 |       |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cle                   | ared  | x = Bit is unkr | nown  |  |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|--------------------------|-------|-------|-------|-------|--|--|

| —      | —   |       | CNT<13:8> <sup>(2)</sup> |       |       |       |       |  |  |

| bit 15 |     |       |                          |       |       |       | bit 8 |  |  |

| R/W-0 | R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|-------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | CNT<7:0> <sup>(2)</sup> |       |       |       |       |       |       |  |  |  |  |

| bit 7 | bit 7 bit 0             |       |       |       |       |       |       |  |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- **2:** The number of DMA transfers = CNT<13:0> + 1.

## 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS7000598) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the Parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. All the pins in the device are 5V tolerant pins.

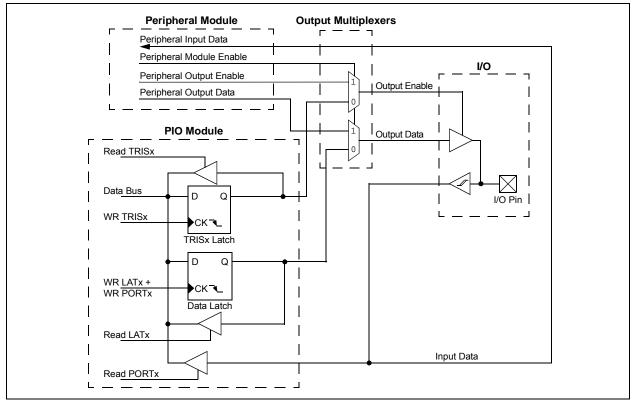

## 11.1 Parallel I/O (PIO) Ports

Generally, a Parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the Data Direction register bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch; writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device are disabled. This means that the corresponding LATx and TRISx registers, and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port, because there is no other competing source of output.

#### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2013-2016 Microchip Technology Inc.

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70005185) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

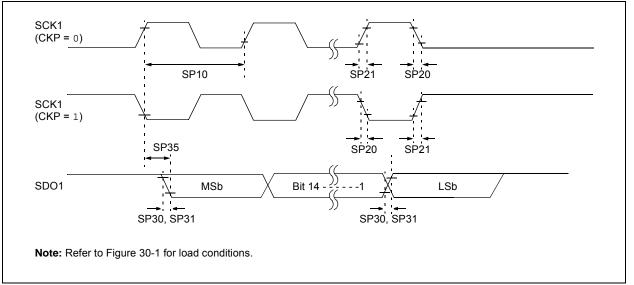

The Serial Peripheral Interface (SPI) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EVXXXGM00X/10X device family offers two SPI modules on a single device, SPI1 and SPI2, that are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

**Note:** In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of this module, but results in a lower maximum speed. See **Section 30.0 "Electrical Characteristics"** for more information.

The SPIx serial interface consists of the following four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

**Note:** All of the 4 pins of the SPIx serial interface must be configured as digital in the ANSELx registers.

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

NOTES:

## dsPIC33EVXXXGM00X/10X FAMILY

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax |              | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------|--------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 53 MUL             | MUL                  | MUL.SS          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1              | None                     |

|                    |                      | MUL.SS          | Wb,Ws,Acc    | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,Ws,Acc    | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,#lit5,Acc | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                     |

|                    |                      | MUL.US          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US          | Wb,Ws,Acc    | Accumulator = unsigned(Wb) *<br>signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,Ws,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,#lit5,Acc | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,Ws,Acc    | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                     |

|                    |                      | MULW.SS         | Wb,Ws,Wnd    | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                     |

|                    |                      | MULW.SU         | Wb,Ws,Wnd    | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.US         | Wb,Ws,Wnd    | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.UU         | Wb,Ws,Wnd    | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,#lit5,Wnd | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.SU          | Wb,#lit5,Wnd | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,#lit5,Wnd | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU          | Wb,#lit5,Wnd | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1              | None                     |

|                    |                      | MUL             | f            | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 54                 | NEG                  | NEG             | Acc          | Negate Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG             | f            | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG             | f,WREG       | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG             | Ws,Wd        | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 55                 | NOP                  | NOP             |              | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR            |              | No Operation                                      | 1             | 1              | None                     |

| 56                 | POP                  | POP             | f            | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                      | POP             | Wdo          | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                      | POP.D           | Wnd          | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                      | POP.S           |              | Pop Shadow Registers                              | 1             | 1              | All                      |

| 57                 | PUSH                 | PUSH            | f            | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                      | PUSH            | Wso          | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                      | PUSH.D          | Wns          | Push W(ns):W(ns + 1) to Top-of-Stack<br>(TOS)     | 1             | 2              | None                     |

|                    |                      | PUSH.S          |              | Push Shadow Registers                             | 1             | 1              | None                     |

| 58                 | PWRSAV               | PWRSAV          | #lit1        | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

| 59                 | RCALL                | RCALL           | Expr         | Relative Call                                     | 1             | 4              | SFA                      |

|                    |                      | RCALL           | Wn           | Computed Call                                     | 1             | 4              | SFA                      |

| 60                 | REPEAT               | REPEAT          | #lit15       | Repeat Next Instruction lit15 + 1 times           | 1             | 1              | None                     |

|                    |                      | REPEAT          | Wn           | Repeat Next Instruction (Wn) + 1 times            | 1             | 1              | None                     |

| 61                 | RESET                | RESET           |              | Software device Reset                             | 1             | 1              | None                     |

| 62                 | RETFIE               | RETFIE          |              | Return from interrupt                             | 1             | 6 (5)          | SFA                      |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| TABLE 30-6: | DC CHARACTERISTI | CS: OPERATING CURRENT (IDD) |

|-------------|------------------|-----------------------------|

|             |                  |                             |

| DC CHARACT                             | ERISTICS            |      | (unless oth | perating Condition<br>erwise stated)<br>emperature -40°C<br>-40°C |            |           |  |  |  |

|----------------------------------------|---------------------|------|-------------|-------------------------------------------------------------------|------------|-----------|--|--|--|

| Param.                                 | Typ. <sup>(2)</sup> | Max. | Units       |                                                                   | Conditions | 5         |  |  |  |

| Operating Current (IDD) <sup>(1)</sup> |                     |      |             |                                                                   |            |           |  |  |  |

| DC20d                                  | 4.5                 | 5.5  | mA          | -40°C                                                             |            |           |  |  |  |

| DC20a                                  | 4.65                | 5.6  | mA          | +25°C                                                             | 5.0V       | 10 MIPS   |  |  |  |

| DC20b                                  | 4.85                | 6.0  | mA          | +85°C                                                             | 5.00       | TO MIPS   |  |  |  |

| DC20c                                  | 5.6                 | 7.2  | mA          | +125°C                                                            |            |           |  |  |  |

| DC22d                                  | 8.6                 | 10.6 | mA          | -40°C                                                             |            |           |  |  |  |

| DC22a                                  | 8.8                 | 10.8 | mA          | +25°C                                                             | 5.0V       | 20 MIPS   |  |  |  |

| DC22b                                  | 9.1                 | 11.1 | mA          | +85°C                                                             | 5.00       | 20 101195 |  |  |  |

| DC22c                                  | 9.8                 | 12.6 | mA          | +125°C                                                            |            |           |  |  |  |

| DC23d                                  | 16.8                | 18.5 | mA          | -40°C                                                             |            |           |  |  |  |

| DC23a                                  | 17.2                | 19.0 | mA          | +25°C                                                             | 5.0V       | 40 MIPS   |  |  |  |

| DC23b                                  | 17.55               | 19.2 | mA          | +85°C                                                             | 5.00       | 40 MIPS   |  |  |  |

| DC23c                                  | 18.3                | 21.0 | mA          | +125°C                                                            |            |           |  |  |  |

| DC24d                                  | 25.15               | 28.0 | mA          | -40°C                                                             |            |           |  |  |  |

| DC24a                                  | 25.5                | 28.0 | mA          | +25°C                                                             | 5.0)/      |           |  |  |  |

| DC24b                                  | 25.5                | 28.0 | mA          | +85°C                                                             | - 5.0V     | 60 MIPS   |  |  |  |

| DC24c                                  | 25.55               | 28.5 | mA          | +125°C                                                            |            |           |  |  |  |

| DC25d                                  | 29.0                | 31.0 | mA          | -40°C                                                             |            |           |  |  |  |

| DC25a                                  | 28.5                | 31.0 | mA          | +25°C                                                             | 5.0V       | 70 MIPS   |  |  |  |

| DC25b                                  | 28.3                | 31.0 | mA          | +85°C                                                             |            |           |  |  |  |

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- CPU executing

- while(1)

```

{

NOP();

```

```

NOP ( )

```

2: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

#### TABLE 30-24: TIMER2 AND TIMER4 (TYPE B TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

Standard Operating Conditions: 4.5V to 5.5V

| AC CHARACTERISTICS |                |                                         | Operating conditions: $4.5 \vee 10.53 \vee$ (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                        |      |               |       |                                                                             |

|--------------------|----------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol         | Charac                                  | cteristic <sup>(1)</sup>                                                                                                                                                                              | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TB10               | T⊤xH           | TxCK High<br>Time                       | Synchronous<br>mode                                                                                                                                                                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB11               | ΤτxL           | TxCK Low<br>Time                        | Synchronous<br>mode                                                                                                                                                                                   | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TB15,<br>N = Prescaler Value<br>(1, 8, 64, 256) |

| TB15               | ΤτχΡ           | TxCK Input<br>Period                    | Synchronous<br>mode                                                                                                                                                                                   | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = Prescaler Value<br>(1, 8, 64, 256)                                      |

| TB20               | TCKEXT-<br>MRL | Delay from I<br>Clock Edge<br>Increment | External TxCK<br>to Timer                                                                                                                                                                             | 0.75 Tcy + 40                          |      | 1.75 Tcy + 40 | ns    |                                                                             |

Note 1: These parameters are characterized but not tested in manufacturing.

#### TABLE 30-25: TIMER3 AND TIMER5 (TYPE C TIMER) EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |                |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |               |                |               |    |                                        |

|--------------------|----------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|---------------|----|----------------------------------------|

| Param<br>No.       | Symbol         | Charao                                                       | cteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                | Min.          | Min. Typ. Max. |               |    | Conditions                             |

| TC10               | ТтхН           | TxCK High<br>Time                                            | Synchronous                                                                                                                                                                                                                                                                             | Tcy + 20      |                | _             | ns | Must also meet<br>Parameter TC15       |

| TC11               | ΤτxL           | TxCK Low<br>Time                                             | Synchronous                                                                                                                                                                                                                                                                             | Tcy + 20      | _              | —             | ns | Must also meet<br>Parameter TC15       |

| TC15               | ΤτχΡ           | TxCK Input<br>Period                                         | Synchronous,<br>with Prescaler                                                                                                                                                                                                                                                          | 2 Tcy + 40    | _              | —             | ns | N = Prescaler Value<br>(1, 8, 64, 256) |

| TC20               | TCKEXT-<br>MRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment |                                                                                                                                                                                                                                                                                         | 0.75 Tcy + 40 | _              | 1.75 Tcy + 40 | ns |                                        |

| Note 1: | These parameters are characterized but not tested in manufacturing. |

|---------|---------------------------------------------------------------------|

|         |                                                                     |

#### TABLE 30-38: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARA             | CTERISTICS                               |                                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |     |  |  |

|----------------------|------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)                                                                                                                                                                                                                                              | CKE | СКР | SMP |  |  |

| 25 MHz               | Table 30-39                              | _                                           | _                                                                                                                                                                                                                                                                                       | 0,1 | 0,1 | 0,1 |  |  |

| 25 MHz               | —                                        | Table 30-40                                 | —                                                                                                                                                                                                                                                                                       | 1   | 0,1 | 1   |  |  |

| 25 MHz               | —                                        | Table 30-41                                 | —                                                                                                                                                                                                                                                                                       | 0   | 0,1 | 1   |  |  |

| 25 MHz               | —                                        | —                                           | Table 30-42                                                                                                                                                                                                                                                                             | 1   | 0   | 0   |  |  |

| 25 MHz               | _                                        | _                                           | Table 30-43                                                                                                                                                                                                                                                                             | 1   | 1   | 0   |  |  |

| 25 MHz               | _                                        | —                                           | Table 30-44                                                                                                                                                                                                                                                                             | 0   | 1   | 0   |  |  |

| 25 MHz               | —                                        | —                                           | Table 30-45                                                                                                                                                                                                                                                                             | 0   | 0   | 0   |  |  |

#### FIGURE 30-20: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 4.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |                     |                     |       |                                                                                                                                      |

|--------------------|--------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                        | Min.                                                                                                                                                   | Тур. <sup>(1)</sup> | Max.                | Units | Conditions                                                                                                                           |

|                    | VIL    | Input Low Voltage                                                     |                                                                                                                                                        |                     |                     |       |                                                                                                                                      |

| DI10               |        | Any I/O Pins                                                          | Vss                                                                                                                                                    | —                   | 0.2 Vdd             | V     |                                                                                                                                      |

|                    | Vih    | Input High Voltage                                                    |                                                                                                                                                        |                     |                     |       |                                                                                                                                      |

| DI20               |        | I/O Pins                                                              | 0.75 VDD                                                                                                                                               | —                   | 5.5                 | V     |                                                                                                                                      |

| DI30               | ICNPU  | Change Notification Pull-up<br>Current                                | 200                                                                                                                                                    | 375                 | 600                 | μA    | VDD = 5.0V, VPIN = VSS                                                                                                               |

| DI31               | ICNPD  | Change Notification<br>Pull-Down Current <sup>(7)</sup>               | 175                                                                                                                                                    | 400                 | 625                 | μΑ    | VDD = 5.0V, VPIN = VDD                                                                                                               |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup>                                |                                                                                                                                                        |                     |                     |       |                                                                                                                                      |

| DI50               |        | I/O Pins                                                              | -200                                                                                                                                                   | _                   | 200                 | nA    | $\label{eq:VSS} \begin{split} VSS \leq V PIN \leq V DD, \\ \text{pin at high-impedance} \end{split}$                                 |

| DI55               |        | MCLR                                                                  | -1.5                                                                                                                                                   | _                   | 1.5                 | μA    | $VSS \leq VPIN \leq VDD$                                                                                                             |

| DI56               |        | OSC1                                                                  | -300                                                                                                                                                   | —                   | 300                 | nA    | $\label{eq:VSS} \begin{split} &VSS \leq VPIN \leq VDD, \\ &XT \text{ and } HS \text{ modes} \end{split}$                             |

| Dl60a              | licl   | Input Low Injection Current                                           | 0                                                                                                                                                      | —                   | _5 <sup>(4,6)</sup> | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP<br>and RB7                                                                       |

| DI60b              | Іісн   | Input High Injection Current                                          | 0                                                                                                                                                      | _                   | +5(5,6)             | mA    | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR,<br>VCAP, RB7 and all 5V<br>tolerant pins <sup>(5)</sup>                               |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | <sub>-20</sub> (7)                                                                                                                                     | _                   | +20 <sup>(7)</sup>  | mA    | Absolute instantaneous<br>sum of all $\pm$ input injection<br>currents from all I/O pins<br>(   IICL   +   IICH   ) $\leq \sum$ IICT |

#### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

Note 1: Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- 5: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 6: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

7: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted, provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

## dsPIC33EVXXXGM00X/10X FAMILY

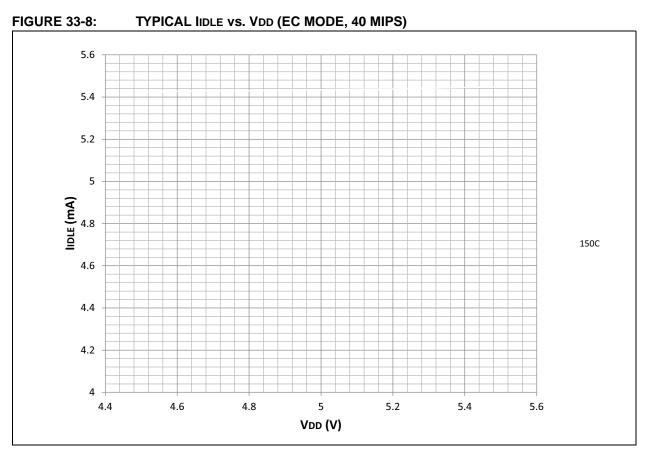

FIGURE 33-7: TYPICAL lidLe vs. Vdd (EC MODE, 20 MIPS)

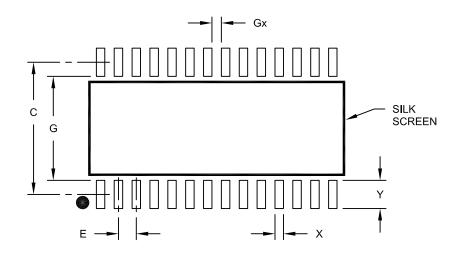

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

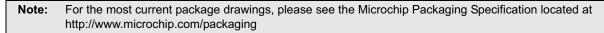

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |          |      |      |

|--------------------------|------------------|----------|------|------|

| Dimensior                | Dimension Limits |          | NOM  | MAX  |

| Contact Pitch            | E                | 1.27 BSC |      |      |

| Contact Pad Spacing      | С                |          | 9.40 |      |

| Contact Pad Width (X28)  | Х                |          |      | 0.60 |

| Contact Pad Length (X28) | Y                |          |      | 2.00 |

| Distance Between Pads    | Gx               | 0.67     |      |      |

| Distance Between Pads    | G                | 7.40     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

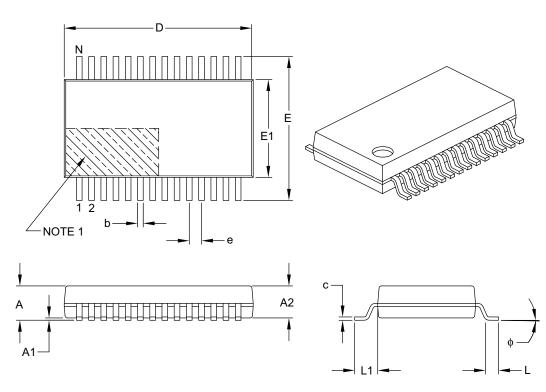

#### 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|----------|-------------|--|--|--|

| Dimension                | Dimension Limits |          |          | MAX         |  |  |  |

| Number of Pins           | Ν                |          | 28       |             |  |  |  |

| Pitch                    | е                |          | 0.65 BSC |             |  |  |  |

| Overall Height           | Α                | -        | -        | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05     | -        | —           |  |  |  |

| Overall Width            | Е                | 7.40     | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30     | 5.60        |  |  |  |

| Overall Length           | D                | 9.90     | 10.20    | 10.50       |  |  |  |

| Foot Length              | L                | 0.55     | 0.75     | 0.95        |  |  |  |

| Footprint                | L1               | 1.25 REF |          |             |  |  |  |

| Lead Thickness           | с                | 0.09     | -        | 0.25        |  |  |  |

| Foot Angle               | φ                | 0°       | 4°       | 8°          |  |  |  |

| Lead Width               | b                | 0.22     | -        | 0.38        |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

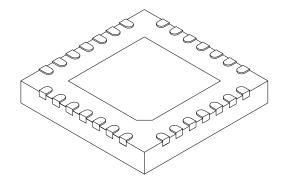

#### 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |          |      |

|-------------------------|-------------|----------|----------|------|

| Dimension               | MIN         | NOM      | MAX      |      |

| Number of Pins          | N           |          | 28       |      |

| Pitch                   | е           |          | 0.65 BSC |      |

| Overall Height          | A           | 0.80     | 0.90     | 1.00 |

| Standoff                | A1          | 0.00     | 0.02     | 0.05 |

| Terminal Thickness      | A3          | 0.20 REF |          |      |

| Overall Width           | E           | 6.00 BSC |          |      |

| Exposed Pad Width       | E2          | 3.65     | 3.70     | 4.70 |

| Overall Length          | D           | 6.00 BSC |          |      |

| Exposed Pad Length      | D2          | 3.65     | 3.70     | 4.70 |

| Terminal Width          | b           | 0.23     | 0.30     | 0.35 |

| Terminal Length         | L           | 0.30     | 0.40     | 0.50 |

| Terminal-to-Exposed Pad | K           | 0.20     | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-124C Sheet 2 of 2

# 28-Lead Plastic Quad Flat, No Lead Package (MM) – 6x6x0.9 mm Body [QFN-S] with 0.40 mm Contact Length

|                            | MILLIMETERS      |          |      |      |  |

|----------------------------|------------------|----------|------|------|--|

| Dimension                  | Dimension Limits |          | NOM  | MAX  |  |

| Contact Pitch              | E                | 0.65 BSC |      |      |  |

| Optional Center Pad Width  | W2               |          |      | 4.70 |  |

| Optional Center Pad Length | T2               |          |      | 4.70 |  |

| Contact Pad Spacing        | C1               |          | 6.00 |      |  |

| Contact Pad Spacing        | C2               |          | 6.00 |      |  |

| Contact Pad Width (X28)    | X1               |          |      | 0.40 |  |

| Contact Pad Length (X28)   | Y1               |          |      | 0.85 |  |

| Distance Between Pads      | G                | 0.25     |      |      |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2124A

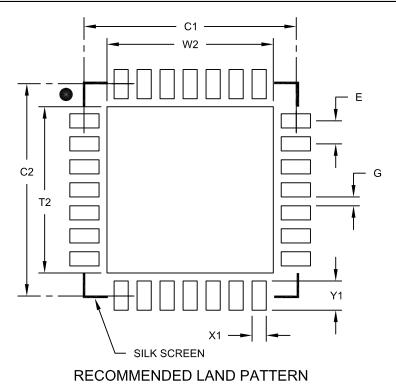

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### DETAIL 1

|                          | MILLIMETERS |             |           |      |

|--------------------------|-------------|-------------|-----------|------|

| Dimension                | Limits      | MIN         | NOM       | MAX  |

| Number of Leads          | Ν           |             | 64        |      |

| Lead Pitch               | е           |             | 0.50 BSC  |      |

| Overall Height           | A           | -           | -         | 1.20 |

| Molded Package Thickness | A2          | 0.95        | 1.00      | 1.05 |

| Standoff                 | A1          | 0.05        | -         | 0.15 |

| Foot Length              | L           | 0.45        | 0.60      | 0.75 |

| Footprint                | L1          | 1.00 REF    |           |      |

| Foot Angle               | ¢           | 0° 3.5° 7°  |           |      |

| Overall Width            | Е           |             | 12.00 BSC |      |

| Overall Length           | D           |             | 12.00 BSC |      |

| Molded Package Width     | E1          |             | 10.00 BSC |      |

| Molded Package Length    | D1          | 10.00 BSC   |           |      |

| Lead Thickness           | С           | 0.09 - 0.20 |           |      |

| Lead Width               | b           | 0.17        | 0.22      | 0.27 |

| Mold Draft Angle Top     | α           | 11°         | 12°       | 13°  |

| Mold Draft Angle Bottom  | β           | 11°         | 12°       | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2