#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm102-e-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

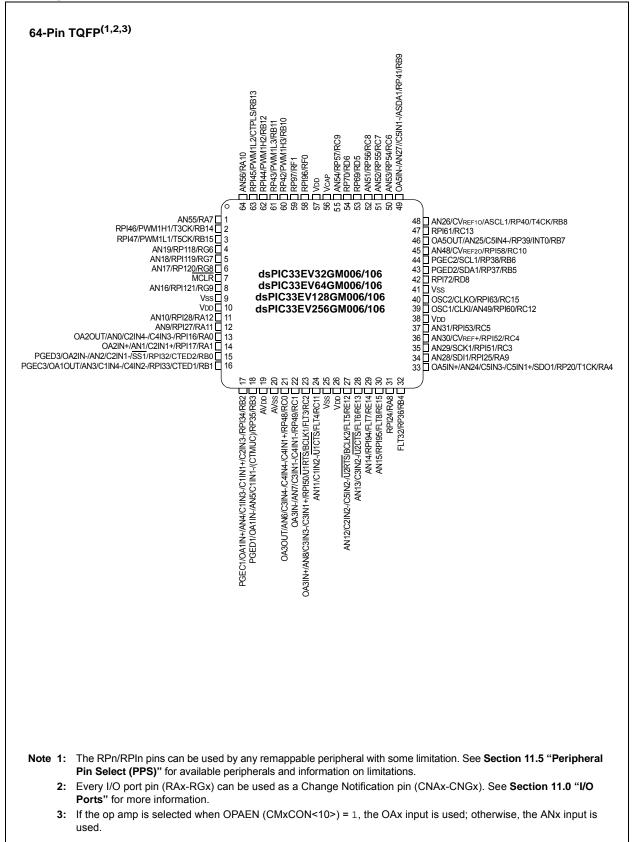

### **Pin Diagrams (Continued)**

## **Table of Contents**

| 1.0   | Device Overview                                                               |     |

|-------|-------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-Bit Digital Signal Controllers         | 17  |

| 3.0   | CPU                                                                           |     |

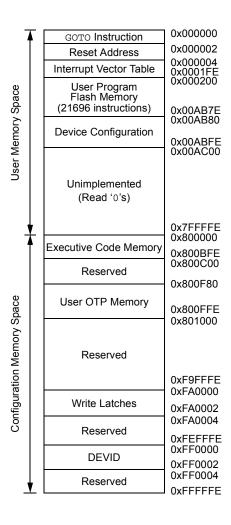

| 4.0   | Memory Organization                                                           |     |

| 5.0   | Flash Program Memory                                                          | 83  |

| 6.0   | Resets                                                                        |     |

| 7.0   | Interrupt Controller                                                          |     |

| 8.0   | Direct Memory Access (DMA)                                                    | 109 |

| 9.0   | Oscillator Configuration                                                      | 123 |

| 10.0  | Power-Saving Features                                                         | 133 |

| 11.0  | I/O Ports                                                                     | 143 |

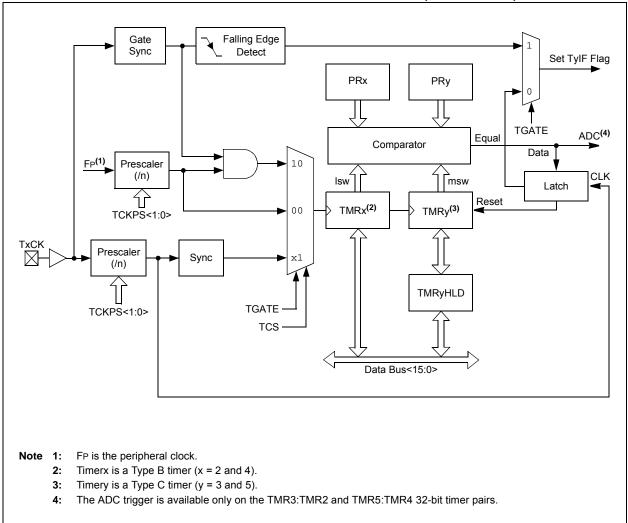

| 12.0  | Timer1                                                                        | 173 |

| 13.0  | Timer2/3 and Timer4/5                                                         | 175 |

| 14.0  | Deadman Timer (DMT)                                                           | 181 |

| 15.0  | Input Capture                                                                 | 189 |

| 16.0  | Output Compare                                                                | 193 |

| 17.0  | High-Speed PWM Module                                                         | 199 |

| 18.0  |                                                                               | 221 |

| 19.0  | Inter-Integrated Circuit (I <sup>2</sup> C)                                   | 229 |

| 20.0  | Single-Edge Nibble Transmission (SENT)                                        |     |

| 21.0  | Universal Asynchronous Receiver Transmitter (UART)                            |     |

| 22.0  | Controller Area Network (CAN) Module (dsPIC33EVXXXGM10X Devices Only)         | 253 |

| 23.0  | Charge Time Measurement Unit (CTMU)                                           |     |

| 24.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                               |     |

| 25.0  | Op Amp/Comparator Module                                                      | 301 |

| 26.0  | Comparator Voltage Reference                                                  | 313 |

| 27.0  | Special Features                                                              | 317 |

| 28.0  | Instruction Set Summary                                                       | 327 |

| 29.0  | Development Support                                                           | 337 |

|       |                                                                               |     |

|       | High-Temperature Electrical Characteristics                                   |     |

|       | Characteristics for Industrial/Extended Temperature Devices (-40°C to +125°C) |     |

| 33.0  | Characteristics for High-Temperature Devices (+150°C)                         | 439 |

|       | Packaging Information                                                         |     |

|       | endix A: Revision History                                                     |     |

|       | X                                                                             |     |

|       | Microchip Web Site                                                            |     |

|       | omer Change Notification Service                                              |     |

|       | omer Support                                                                  |     |

| Produ | luct Identification System                                                    | 497 |

# dsPIC33EVXXXGM00X/10X FAMILY

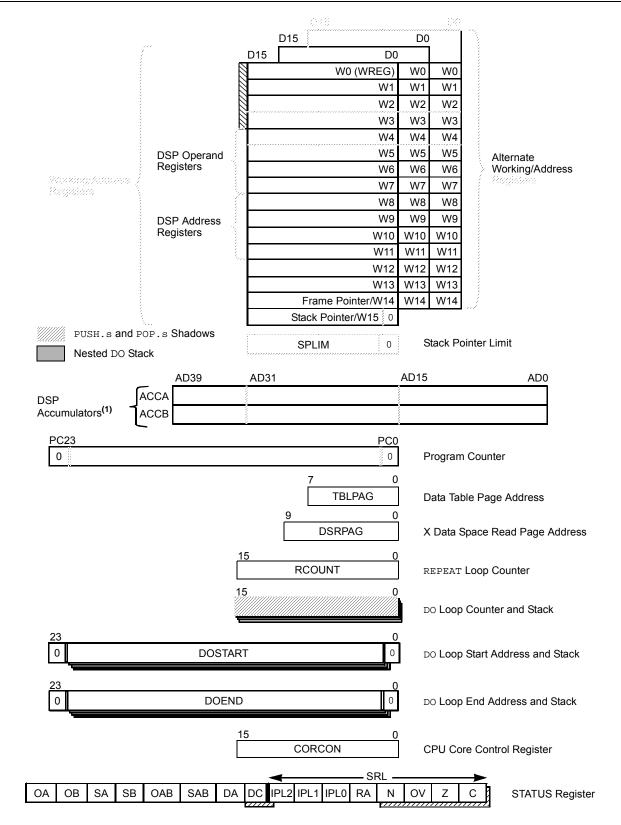

#### FIGURE 3-2: PROGRAMMER'S MODEL

**Note 1:** Memory areas are not shown to scale.

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EVXXXGM00X/10X family core has two Data Spaces: X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified, linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X DS is used by all instructions and supports all addressing modes. The X DS has separate read and write data buses. The X read data bus is the read data path for all instructions that view the DS as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class). The Y DS is used in concert with the X DS by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to the X Data Space.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | -   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0    | U-0 | U-0 | U-0 | R-0 | R-0 | R-0 | R-0   |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| U-0         | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |  |

|-------------|-----|-----|-----|-------|-------|-------|-------|--|

| —           | —   | —   | —   | PPST3 | PPST2 | PPST1 | PPST0 |  |

| bit 7 bit 0 |     |     |     |       |       |       |       |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                  |

|----------|---------------------------------------------------------------------------------------------|

| bit 3    | PPST3: Channel 3 Ping-Pong Mode Status Flag bit                                             |

|          | <ul><li>1 = DMA3STB register is selected</li><li>0 = DMA3STA register is selected</li></ul> |

| bit 2    | PPST2: Channel 2 Ping-Pong Mode Status Flag bit                                             |

|          | 1 = DMA2STB register is selected                                                            |

|          | 0 = DMA2STA register is selected                                                            |

| bit 1    | <b>PPST1:</b> Channel 1 Ping-Pong Mode Status Flag bit                                      |

|          | 1 = DMA1STB register is selected                                                            |

|          | 0 = DMA1STA register is selected                                                            |

| bit 0    | <b>PPST0:</b> Channel 0 Ping-Pong mode Status Flag bit                                      |

|          | 1 = DMA0STB register is selected                                                            |

|          | 0 = DMA0STA register is selected                                                            |

NOTES:

## 18.2 SPI Control Registers

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0           | U-0                                                                                                                                                                                        | R/W-0                                  | U-0                             | U-0               | R/W-0                       | R/W-0                  | R/W-0          |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|-------------------|-----------------------------|------------------------|----------------|--|

| SPIEN           | _                                                                                                                                                                                          | SPISIDL                                |                                 | _                 | SPIBEC2                     | SPIBEC1                | SPIBEC0        |  |

| bit 15          |                                                                                                                                                                                            |                                        |                                 |                   |                             |                        | bit 8          |  |

|                 |                                                                                                                                                                                            |                                        |                                 |                   |                             |                        |                |  |

| R/W-0           | R/C-0, HS                                                                                                                                                                                  | R/W-0                                  | R/W-0                           | R/W-0             | R/W-0                       | R-0, HS, HC            | R-0, HS, HC    |  |

| SRMPT           | SPIROV                                                                                                                                                                                     | SRXMPT                                 | SISEL2                          | SISEL1            | SISEL0                      | SPITBF                 | SPIRBF         |  |

| bit 7           |                                                                                                                                                                                            |                                        |                                 |                   |                             |                        | bit C          |  |

|                 |                                                                                                                                                                                            |                                        |                                 |                   |                             |                        |                |  |

| Legend:         |                                                                                                                                                                                            | HC = Hardware                          | e Clearable bit                 |                   | are Settable b              |                        |                |  |

| R = Readable    |                                                                                                                                                                                            | W = Writable b                         | pit                             | U = Unimple       | mented bit, re              | ead as '0'             |                |  |

| -n = Value at I | POR                                                                                                                                                                                        | '1' = Bit is set                       |                                 | '0' = Bit is cle  | eared                       | C = Clearable          | e bit          |  |

| bit 15          | SPIEN: SPIX                                                                                                                                                                                | Enable bit                             |                                 |                   |                             |                        |                |  |

| bit 10          |                                                                                                                                                                                            | he SPIx module                         | and configure                   | s SCKx SDO        | $c$ SDIx and $\overline{S}$ | <u>Sx</u> as serial po | rt pins        |  |

|                 |                                                                                                                                                                                            | the SPIx module                        | •                               |                   |                             |                        | it pino        |  |

| bit 14          | Unimplemen                                                                                                                                                                                 | ted: Read as '0                        | ,                               |                   |                             |                        |                |  |

| bit 13          | SPISIDL: SP                                                                                                                                                                                | Ix Stop in Idle M                      | ode bit                         |                   |                             |                        |                |  |

|                 |                                                                                                                                                                                            | ues the SPIx mo<br>s the SPIx modu     |                                 |                   | vice enters Idl             | e mode                 |                |  |

| bit 12-11       |                                                                                                                                                                                            | ted: Read as '0                        | -                               |                   |                             |                        |                |  |

| bit 10-8        | SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)                                                                                                                |                                        |                                 |                   |                             |                        |                |  |

|                 | Master mode:<br>Number of SPIx transfers are pending.                                                                                                                                      |                                        |                                 |                   |                             |                        |                |  |

|                 | Slave mode:                                                                                                                                                                                | Plx transfers are                      |                                 |                   |                             |                        |                |  |

| bit 7           | <b>SRMPT:</b> SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode)                                                                                                       |                                        |                                 |                   |                             |                        |                |  |

|                 | 1 = The SPIx                                                                                                                                                                               | Shift register is<br>Shift register is | empty and rea                   | •                 |                             | -                      |                |  |

| bit 6           |                                                                                                                                                                                            | x Receive Over                         |                                 |                   |                             |                        |                |  |

|                 | 1 = A new b<br>previous                                                                                                                                                                    | yte/word is com<br>data in the SPI     | pletely receive<br>BUF register | ed and discard    | led; the user               | application ha         | s not read the |  |

| L:4 F           |                                                                                                                                                                                            | has not occurre                        |                                 | lid in Enhance    |                             | - )                    |                |  |

| bit 5           | 1 = RX FIFO                                                                                                                                                                                | Ix Receive FIFO                        | D Empty bit (va                 | lid in Enhance    | a Buller mode               | e)                     |                |  |

|                 | 1 = RX FIFO<br>0 = RX FIFO                                                                                                                                                                 |                                        |                                 |                   |                             |                        |                |  |

| bit 4-2         |                                                                                                                                                                                            |                                        | errupt Mode bit                 | s (valid in Enh   | anced Buffer                | mode)                  |                |  |

|                 | SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)<br>111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)                                   |                                        |                                 |                   |                             |                        |                |  |

|                 | 110 = Interrupt when the last bit is shifted into SPIxSR, and as a result, the TX FIFO is empty                                                                                            |                                        |                                 |                   |                             |                        |                |  |

|                 | 101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete<br>100 = Interrupt when one data is shifted into SPIxSR, and as a result, the TX FIFO has one open |                                        |                                 |                   |                             |                        |                |  |

|                 |                                                                                                                                                                                            | ry location<br>pt when the SP          | ly receive buffe                | er is full (SPIRI | RF hit is set)              |                        |                |  |

|                 |                                                                                                                                                                                            | pt when the SP                         |                                 |                   |                             |                        |                |  |

|                 | 001 = Interru                                                                                                                                                                              | pt when data is                        | available in the                | e SPIx receive    | buffer (SRM                 |                        |                |  |

|                 | 000 = Interru                                                                                                                                                                              |                                        |                                 |                   |                             |                        |                |  |

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C<sup>TM</sup>)" (DS70000195) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EVXXXGM00X/10X family of devices contains one Inter-Integrated Circuit (I<sup>2</sup>C) module, I2C1.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has the following 2-pin interface:

- The SCLx pin is clock.

- The SDAx pin is data.

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting Both Master and Slave modes of Operation

- I<sup>2</sup>C Slave mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Master mode Supports 7 and 10-Bit Addressing

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves

- Serial Clock Synchronization for I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control)

- I<sup>2</sup>C Supports Multi-Master Operation, Detects Bus Collision and Arbitrates Accordingly

- · Support for Address Bit Masking up to Lower 7 Bits

- I<sup>2</sup>C Slave Enhancements:

- SDAx hold time selection of SMBus (300 ns or 150 ns)

- Start/Stop bit interrupt enables

Figure 19-1 shows a block diagram of the I<sup>2</sup>C module.

## 19.1 I<sup>2</sup>C Baud Rate Generator

The Baud Rate Generator (BRG) used for I<sup>2</sup>C mode operation is used to set the SCL clock frequency for 100 kHz, 400 kHz and 1 MHz. The BRG reload value is contained in the I2CxBRG register. The BRG will automatically begin counting on a write to the I2CxTRN register.

Equation 19-1 and Equation 19-2 provide the BRG reload formula and FSCL frequency, respectively.

#### EQUATION 19-1: BRG FORMULA

$$I2CxBRG = \left( \left( \frac{1}{FSCL} - Delay \right) \times \frac{FCY}{2} \right) - 2$$

Where:

Delay varies from 110 ns to 130 ns.

#### EQUATION 19-2: FSCL FREQUENCY

FSCL = FCY/((I2CxBRG + 2) \* 2)

NOTES:

## 24.2 ADC Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADC analog scan channel list, defined in the ADxCSSL/ADxCSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using the DMA peripheral.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1.c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- When the DMA module is enabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADCxBUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA Controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

- 5. Enabling op amps, comparator inputs and external voltage references can limit the availability of analog inputs (ANx pins). For example, when Op Amp 2 is enabled, the pins for ANO, AN1 and AN2 are used by the op amp's inputs and output. This negates the usefulness of Alternate Input mode since the MUX A selections use ANO-AN2. Carefully study the ADC block diagram to determine the configuration that will best suit your application. For configuration examples, refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual".

## 27.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EVXXXGM00X/10X family devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- In-Circuit Emulation

## 27.1 Configuration Bits

In dsPIC33EVXXXGM00X/10X family devices, the Configuration bytes are implemented as volatile memory. This means that configuration data must be programmed each time the device is powered up. Configuration data is stored at the top of the on-chip program memory space, known as the Flash Configuration bytes. Their specific locations are shown in Table 27-1. The configuration data is automatically loaded from the Flash Configuration bytes to the proper Configuration Shadow registers during device Resets.

| Note: | Configuration data is reloaded on all types |

|-------|---------------------------------------------|

|       | of device Resets.                           |

When creating applications for these devices, users should always specifically allocate the location of the Flash Configuration bytes for configuration data in their code for the compiler. This is to ensure that program code is not stored in this address when the code is compiled.

The upper 2 bytes of all Flash Configuration Words in program memory should always be '1111 1111 1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

| Note: | Performing a page erase operation on the |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | last page of program memory clears the   |  |  |  |  |  |

|       | Flash Configuration bytes, enabling code |  |  |  |  |  |

|       | protection as a result. Therefore, users |  |  |  |  |  |

|       | should avoid performing page erase       |  |  |  |  |  |

|       | operations on the last page of program   |  |  |  |  |  |

|       | memory.                                  |  |  |  |  |  |

The Configuration Flash bytes map is shown in Table 27-1.

## 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EV instruction set is almost identical to that of the dsPIC30F and dsPIC33F.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into following five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the Status Flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have the following three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write-back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

## 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

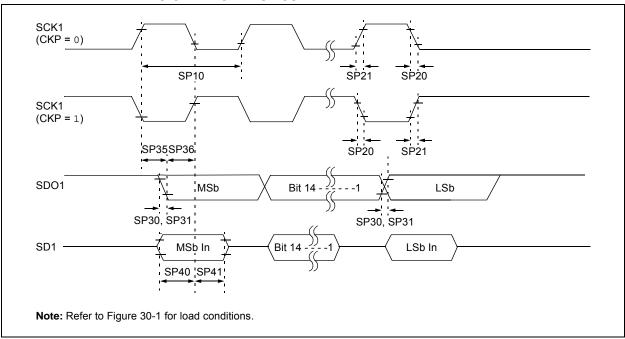

#### FIGURE 30-23: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# dsPIC33EVXXXGM00X/10X FAMILY

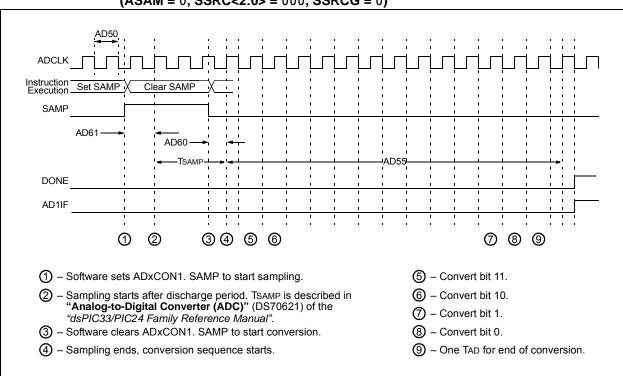

#### FIGURE 30-34: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000, SSRCG = 0)

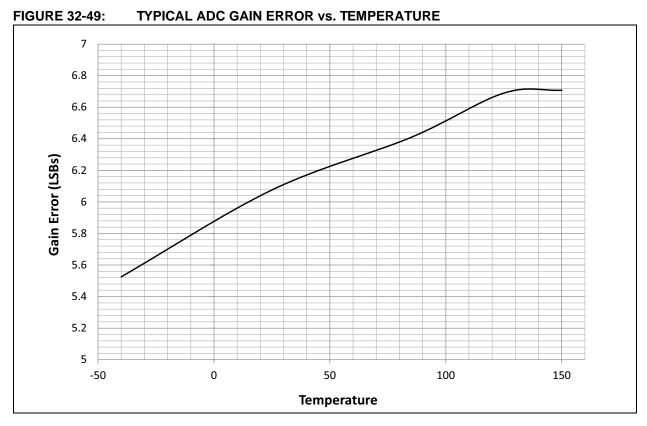

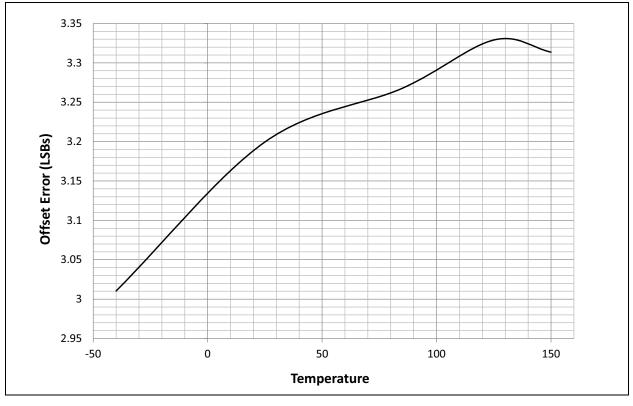

### 32.19 ADC Gain Offset Error

© 2013-2016 Microchip Technology Inc.

# dsPIC33EVXXXGM00X/10X FAMILY

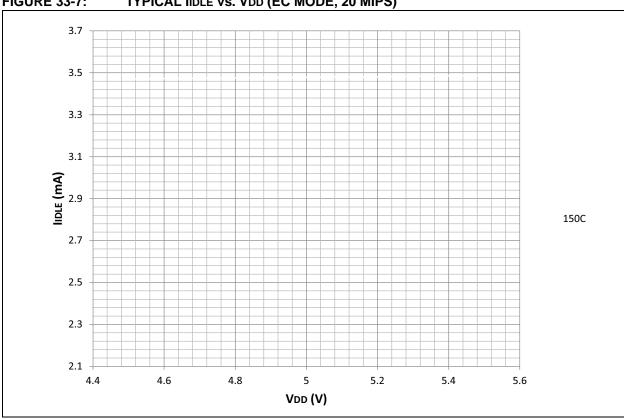

FIGURE 33-7: TYPICAL lidLe vs. Vdd (EC MODE, 20 MIPS)

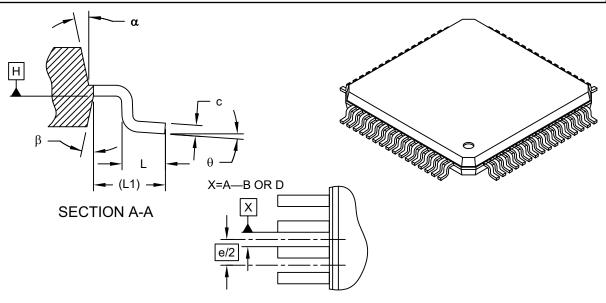

### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### DETAIL 1

|                          | MILLIMETERS         |            |           |      |

|--------------------------|---------------------|------------|-----------|------|

| Dimension                | MIN                 | NOM        | MAX       |      |

| Number of Leads          | Ν                   | 64         |           |      |

| Lead Pitch               | е                   |            | 0.50 BSC  |      |

| Overall Height           | A                   | -          | -         | 1.20 |

| Molded Package Thickness | A2                  | 0.95       | 1.00      | 1.05 |

| Standoff                 | A1                  | 0.05       | -         | 0.15 |

| Foot Length              | L                   | 0.45       | 0.60      | 0.75 |

| Footprint                | L1                  | 1.00 REF   |           |      |

| Foot Angle               | ¢                   | 0° 3.5° 7° |           |      |

| Overall Width            | Е                   |            | 12.00 BSC |      |

| Overall Length           | D                   |            | 12.00 BSC |      |

| Molded Package Width     | E1                  |            | 10.00 BSC |      |

| Molded Package Length    | D1                  | 10.00 BSC  |           |      |

| Lead Thickness           | С                   | 0.09 - 0.2 |           | 0.20 |

| Lead Width               | d Width b 0.17 0.22 |            | 0.27      |      |

| Mold Draft Angle Top     | α                   | 11° 12° 13 |           | 13°  |

| Mold Draft Angle Bottom  | β                   | 11°        | 12°       | 13°  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2