#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 11x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm102-i-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-19: NVM REGISTER MAP

|             |       |        |        |          |              |             |               |       | -     |           |       | -     |        |            |        |        | -      |               |

|-------------|-------|--------|--------|----------|--------------|-------------|---------------|-------|-------|-----------|-------|-------|--------|------------|--------|--------|--------|---------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12       | Bit 11      | Bit 10        | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| NVMCON      | 0728  | WR     | WREN   | WRERR    | NVMSIDL      | _           | _             | RPDF  | URERR | _         | —     | _     | _      | NVMOP3     | NVMOP2 | NVMOP1 | NVMOP0 | 0000          |

| NVMADR      | 072A  |        |        |          |              |             |               |       |       | NVMADR<   | 15:0> |       |        |            |        |        |        | 0000          |

| NVMADRU     | 072C  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMAD  | RU<23:16>  |        |        |        | 0000          |

| NVMKEY      | 072E  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMK   | EY<7:0>    |        |        |        | 0000          |

| NVMSRCADRL  | 0730  |        |        |          |              |             |               |       | NVMSF | RCADR<15: | 1>    |       |        |            |        |        | 0      | 0000          |

| NVMSRCADRH  | 0732  | _      | _      | _        | _            |             | _             | _     | _     |           |       |       | NVMSRC | ADR<23:16> |        |        |        | 0000          |

| Lonondy     |       |        |        | Desetual | an are chour | a in heaven | d a stress al |       |       |           |       |       |        |            |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-20: SYSTEM CONTROL REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7    | Bit 6    | Bit 5  | Bit 4     | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|----------|----------|--------|-----------|---------|---------|---------|---------|---------------|

| RCON        | 0740  | TRAPR  | IOPUWR |        | _      | VREGSF |         | СМ      | VREGS   | EXTR     | SWR      | SWDTEN | WDTO      | SLEEP   | IDLE    | BOR     | POR     | Note 1        |

| OSCCON      | 0742  | —      | COSC2  | COSC1  | COSC0  | —      | NOSC2   | NOSC1   | NOSC0   | CLKLOCK  | IOLOCK   | LOCK   | _         | CF      | _       | _       | OSWEN   | Note 2        |

| CLKDIV      | 0744  | ROI    | DOZE2  | DOZE1  | DOZE0  | DOZEN  | FRCDIV2 | FRCDIV1 | FRCDIV0 | PLLPOST1 | PLLPOST0 | _      | PLLPRE4   | PLLPRE3 | PLLPRE2 | PLLPRE1 | PLLPRE0 | 0000          |

| PLLFBD      | 0746  | -      | —      |        | —      | _      | _       | —       |         |          |          | PL     | LDIV<8:0> |         |         |         |         | 0000          |

| OSCTUN      | 0748  | -      | —      |        | —      | _      | _       | —       |         | _        | _        |        |           | TUN     | <5:0>   |         |         | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration fuses.

## TABLE 4-21: REFERENCE CLOCK REGISTER MAP

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON     | 074E  | ROON   | -      | ROSSLP | ROSEL  | RODIV3 | RODIV2 | RODIV1 | RODIV0 | _     | _     | _     | _     | _     | _     | _     | —     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-29: PWM GENERATOR 2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13       | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|--------------|---------|-----------|-----------|-----------|------------------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON2     | 0C40  | FLTSTAT | CLSTAT  | TRGSTAT      | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1      | DTC0    | DTCP     | _        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON2      | 0C42  | PENH    | PENL    | POLH         | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON2     | 0C44  | _       | CLSRC4  | CLSRC3       | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC2        | 0C46  |         |         |              |         |           |           |           | PDC2             | <15:0>    |         |          |          |          |          |          |          | 0000          |

| PHASE2      | 0C48  |         |         |              |         |           |           |           | PHASE            | 2<15:0>   |         |          |          |          |          |          |          | 0000          |

| DTR2        | 0C4A  | -       | _       |              |         |           |           |           |                  | DTR2      | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR2     | 0C4C  |         |         |              |         |           |           |           |                  | ALTDTR    | 2<13:0> |          |          |          |          |          |          | 0000          |

| TRIG2       | 0C52  |         |         |              |         |           |           |           | TRGCN            | 1P<15:0>  |         |          |          |          |          |          |          | 0000          |

| TRGCON2     | 0C54  | TRGDIV3 | TRGDIV2 | TRGDIV1      | TRGDIV0 | —         | —         | —         | —                |           |         | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP2     | 0C58  |         |         |              |         |           |           |           | PWMCA            | .P2<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON2     | 0C5A  | PHR     | PHF     | PLR          | PLF     | FLTLEBEN  | CLLEBEN   | —         | —                |           |         | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY2     | 0C5C  | -       | _       | _            |         |           |           |           |                  |           | LEB<    | :11:0>   |          |          |          |          |          | 0000          |

| AUXCON2     | 0C5E  | -       | -       | _            |         | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> |           | _       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

|             |       |         |         | (-) <b>D</b> |         |           |           |           |                  |           |         |          |          |          |          |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-30: PWM GENERATOR 3 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11    | Bit 10    | Bit 9     | Bit 8            | Bit 7     | Bit 6   | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|-------------|-------|---------|---------|---------|---------|-----------|-----------|-----------|------------------|-----------|---------|----------|----------|----------|----------|----------|----------|---------------|

| PWMCON3     | 0C60  | FLTSTAT | CLSTAT  | TRGSTAT | FLTIEN  | CLIEN     | TRGIEN    | ITB       | MDCS             | DTC1      | DTC0    | DTCP     | —        | _        | CAM      | XPRES    | IUE      | 0000          |

| IOCON3      | 0C62  | PENH    | PENL    | POLH    | POLL    | PMOD1     | PMOD0     | OVRENH    | OVRENL           | OVRDAT1   | OVRDAT0 | FLTDAT1  | FLTDAT0  | CLDAT1   | CLDAT0   | SWAP     | OSYNC    | 0000          |

| FCLCON3     | 0C64  | -       | CLSRC4  | CLSRC3  | CLSRC2  | CLSRC1    | CLSRC0    | CLPOL     | CLMOD            | FLTSRC4   | FLTSRC3 | FLTSRC2  | FLTSRC1  | FLTSRC0  | FLTPOL   | FLTMOD1  | FLTMOD0  | 0000          |

| PDC3        | 0C66  |         |         |         |         |           |           |           | PDC              | 3<15:0>   |         |          |          |          |          |          |          | 0000          |

| PHASE3      | 0C68  |         |         |         |         |           |           |           | PHASI            | E3<15:0>  |         |          |          |          |          |          |          | 0000          |

| DTR3        | 0C6A  | _       | —       |         |         |           |           |           |                  | DTR3      | <13:0>  |          |          |          |          |          |          | 0000          |

| ALTDTR3     | 0C6C  | _       | —       |         |         |           |           |           |                  | ALTDTF    | 3<13:0> |          |          |          |          |          |          | 0000          |

| TRIG3       | 0C72  |         |         |         |         |           |           |           | TRGC             | /IP<15:0> |         |          |          |          |          |          |          | 0000          |

| TRGCON3     | 0C74  | TRGDIV3 | TRGDIV2 | TRGDIV1 | TRGDIV0 |           | _         |           | —                | —         | —       | TRGSTRT5 | TRGSTRT4 | TRGSTRT3 | TRGSTRT2 | TRGSTRT1 | TRGSTRT0 | 0000          |

| PWMCAP3     | 0C78  |         |         |         |         |           |           |           | PWMCA            | AP3<15:0> |         |          |          |          |          |          |          | 0000          |

| LEBCON3     | 0C7A  | PHR     | PHF     | PLR     | PLF     | FLTLEBEN  | CLLEBEN   | -         | _                | —         | —       | BCH      | BCL      | BPHH     | BPHL     | BPLH     | BPLL     | 0000          |

| LEBDLY3     | 0C7C  | _       | _       | _       | _       |           |           |           |                  |           | LEB<    | 11:0>    |          |          |          |          |          | 0000          |

| AUXCON3     | 0C7E  | _       | _       | _       | _       | BLANKSEL3 | BLANKSEL2 | BLANKSEL1 | <b>BLANKSEL0</b> | —         | —       | CHOPSEL3 | CHOPSEL2 | CHOPSEL1 | CHOPSEL0 | CHOPHEN  | CHOPLEN  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 10.2.1 SLEEP MODE

The following events occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared before entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby mode when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

## 10.2.2 IDLE MODE

The following events occur in Idle mode:

- The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

## 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up either from Sleep mode or Idle mode.

| U-0          | U-0                        | U-0             | U-0                        | U-0              | U-0              | U-0             | U-0   |

|--------------|----------------------------|-----------------|----------------------------|------------------|------------------|-----------------|-------|

| —            | —                          | —               | —                          |                  | —                | —               | —     |

| bit 15       |                            |                 |                            |                  |                  |                 | bit 8 |

|              |                            |                 |                            |                  |                  |                 |       |

| U-0          | U-0                        | U-0             | R/W-0                      | U-0              | U-0              | U-0             | U-0   |

| —            | —                          | —               | DMA0MD <sup>(1)</sup>      | —                | —                | —               | —     |

|              |                            |                 | DMA1MD <sup>(1)</sup>      | -                |                  |                 |       |

|              |                            |                 | DMA2MD <sup>(1)</sup>      | -                |                  |                 |       |

|              |                            |                 | DMA3MD <sup>(1)</sup>      |                  |                  |                 |       |

| bit 7        |                            |                 |                            |                  |                  |                 | bit 0 |

|              |                            |                 |                            |                  |                  |                 |       |

| Legend:      |                            |                 |                            |                  |                  |                 |       |

| R = Readal   |                            | W = Writable    |                            | •                | nented bit, read |                 |       |

| -n = Value a | at POR                     | '1' = Bit is se | et                         | '0' = Bit is cle | ared             | x = Bit is unkn | iown  |

|              |                            |                 |                            |                  |                  |                 |       |

| bit 15-5     | Unimplement                |                 |                            |                  |                  |                 |       |

| bit 4        | DMA0MD: DN                 |                 |                            |                  |                  |                 |       |

|              | 1 = DMA0 mo<br>0 = DMA0 mo |                 |                            |                  |                  |                 |       |

|              | DMA1MD: DN                 |                 |                            |                  |                  |                 |       |

|              | 1 = DMA1 mo                |                 |                            |                  |                  |                 |       |

|              | 0 = DMA1 mo                |                 |                            |                  |                  |                 |       |

|              | DMA2MD: DN                 | A2 Module I     | Disable bit <sup>(1)</sup> |                  |                  |                 |       |

|              | 1 = DMA2 mo                |                 |                            |                  |                  |                 |       |

|              | 0 = DMA2 mo                | dule is enable  | ed                         |                  |                  |                 |       |

|              | DMA3MD: DN                 | MA3 Module E    | Disable bit <sup>(1)</sup> |                  |                  |                 |       |

|              | 1 = DMA3 mo<br>0 = DMA3 mo |                 |                            |                  |                  |                 |       |

| bit 3-0      | Unimplement                | ted: Read as    | <b>'</b> 0 <b>'</b>        |                  |                  |                 |       |

|              |                            |                 |                            |                  |                  |                 |       |

## REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

**Note 1:** This single bit enables and disables all four DMA channels.

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | —   | RP180R5 | RP180R4 | RP180R3 | RP180R2 | RP180R1 | RP180R0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

|        |     |         |         |         |         |         |         |

| U-0    | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|        |     | RP170R5 | RP170R4 | RP170R3 | RP170R2 | RP170R1 | RP170R0 |

## REGISTER 11-30: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | RP179R5 | RP179R4 | RP179R3 | RP179R2 | RP179R1 | RP179R0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP180R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP180 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                 |

| bit 5-0   | <b>RP179R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP179 Output Pin bits (see Table 11-3 for peripheral function numbers) |

### REGISTER 11-31: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP181R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP181R<5:0>:** Peripheral Output Function is Assigned to RP181 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 14.0 DEADMAN TIMER (DMT)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Deadman Timer (DMT)" (DS70005155) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

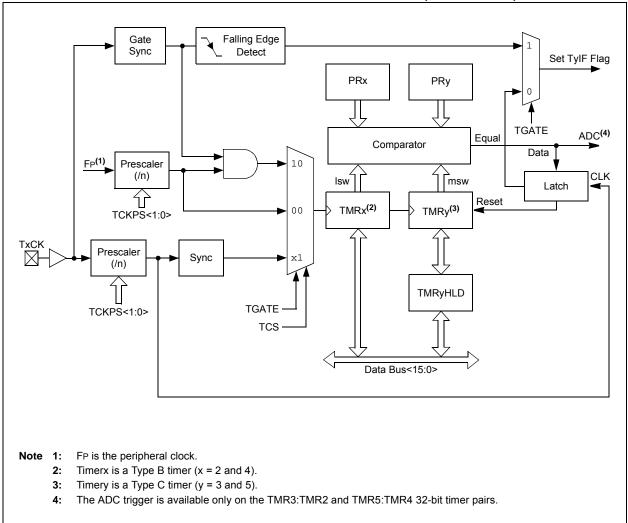

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT, which works on the system clock, is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs, until a count match occurs. Instructions are not fetched when the processor is in Sleep mode.

DMT can be enabled in the Configuration fuse or by software in the DMTCON register by setting the ON bit. The DMT consists of a 32-bit counter with a time-out count match value, as specified by the two 16-bit Configuration Fuse registers: FDMTCNTL and FDMTCNTH.

A DMT is typically used in mission-critical, and safetycritical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 14-1 shows a block diagram of the Deadman Timer module.

### FIGURE 14-1: DEADMAN TIMER BLOCK DIAGRAM

#### R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 **FLTMD FLTOUT FLTTRIEN** OCINV \_\_\_\_ \_\_\_\_ OC32 \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0, HS R/W-0 R/W-0 R/W-1 R/W-1 R/W-0 R/W-0 OCTRIG OCTRIS SYNCSEL4 SYNCSEL3 SYNCSEL2 TRIGSTAT SYNCSEL1 SYNCSEL0 bit 7 bit 0 Legend: HS = Hardware Settable bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 FLTMD: Fault Mode Select bit 1 = Fault mode is maintained until the Fault source is removed; the OCFLTA bit is cleared in software and a new PWM period starts 0 = Fault mode is maintained until the Fault source is removed and a new PWM period starts bit 14 FLTOUT: Fault Out bit 1 = PWM output is driven high on a Fault 0 = PWM output is driven low on a Fault bit 13 FLTTRIEN: Fault Output State Select bit 1 = OCx pin is tri-stated on a Fault condition 0 = OCx pin I/O state is defined by the FLTOUT bit on a Fault condition bit 12 **OCINV:** Output Compare x Invert bit 1 = OCx output is inverted 0 = OCx output is not inverted bit 11-9 Unimplemented: Read as '0' bit 8 OC32: Cascade Two OCx Modules Enable bit (32-bit operation) 1 = Cascade module operation is enabled 0 = Cascade module operation is disabled bit 7 OCTRIG: Output Compare x Trigger/Sync Select bit 1 = Triggers OCx from the source designated by the SYNCSELx bits 0 = Synchronizes OCx with the source designated by the SYNCSELx bits bit 6 TRIGSTAT: Timer Trigger Status bit 1 = Timer source has been triggered and is running 0 = Timer source has not been triggered and is being held clear bit 5 OCTRIS: Output Compare x Output Pin Direction Select bit 1 = Output Compare x is tri-stated 0 = Output Compare x module drives the OCx pin

#### REGISTER 16-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

**Note 1:** Do not use the OCx module as its own synchronization or trigger source.

2: When the OCy module is turned off, it sends a trigger out signal. If the OCx module uses the OCy module as a trigger source, the OCy module must be unselected as a trigger source prior to disabling it.

# 18.2 SPI Control Registers

## REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0           | U-0                                                                                                                      | R/W-0                                  | U-0                             | U-0               | R/W-0           | R/W-0          | R/W-0          |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|-------------------|-----------------|----------------|----------------|--|--|

| SPIEN           | _                                                                                                                        | SPISIDL                                |                                 | _                 | SPIBEC2         | SPIBEC1        | SPIBEC0        |  |  |

| bit 15          |                                                                                                                          |                                        |                                 |                   |                 |                | bit 8          |  |  |

|                 |                                                                                                                          |                                        |                                 |                   |                 |                |                |  |  |

| R/W-0           | R/C-0, HS                                                                                                                | R/W-0                                  | R/W-0                           | R/W-0             | R/W-0           | R-0, HS, HC    | R-0, HS, HC    |  |  |

| SRMPT           | SPIROV                                                                                                                   | SRXMPT                                 | SISEL2                          | SISEL1            | SISEL0          | SPITBF         | SPIRBF         |  |  |

| bit 7           |                                                                                                                          |                                        |                                 |                   |                 |                | bit C          |  |  |

|                 |                                                                                                                          |                                        |                                 |                   |                 |                |                |  |  |

| Legend:         |                                                                                                                          | HC = Hardware                          | e Clearable bit                 |                   | are Settable b  |                |                |  |  |

| R = Readable    |                                                                                                                          | W = Writable b                         | pit                             | U = Unimple       | mented bit, re  | ead as '0'     |                |  |  |

| -n = Value at I | POR                                                                                                                      | '1' = Bit is set                       |                                 | '0' = Bit is cle  | eared           | C = Clearable  | e bit          |  |  |

| bit 15          | SPIEN SPIX                                                                                                               | Enable bit                             |                                 |                   |                 |                |                |  |  |

| bit 10          | <b>SPIEN:</b> SPIx Enable bit<br>1 = Enables the SPIx module and configures SCKx, SDOx, SDIx and SSx as serial port pins |                                        |                                 |                   |                 |                |                |  |  |

|                 |                                                                                                                          | the SPIx module                        | •                               |                   |                 |                | it pino        |  |  |

| bit 14          | Unimplemen                                                                                                               | ted: Read as '0                        | ,                               |                   |                 |                |                |  |  |

| bit 13          | SPISIDL: SP                                                                                                              | Ix Stop in Idle M                      | ode bit                         |                   |                 |                |                |  |  |

|                 |                                                                                                                          | ues the SPIx most the SPIx modu        |                                 |                   | vice enters Idl | e mode         |                |  |  |

| bit 12-11       |                                                                                                                          | ted: Read as '0                        | -                               |                   |                 |                |                |  |  |

| bit 10-8        | SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)                                              |                                        |                                 |                   |                 |                |                |  |  |

|                 | Master mode:<br>Number of SPIx transfers are pending.                                                                    |                                        |                                 |                   |                 |                |                |  |  |

|                 | Slave mode:                                                                                                              | Plx transfers are                      |                                 |                   |                 |                |                |  |  |

| bit 7           | <b>SRMPT:</b> SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode)                                     |                                        |                                 |                   |                 |                |                |  |  |

|                 | 1 = The SPIx                                                                                                             | Shift register is<br>Shift register is | empty and rea                   | •                 |                 | -              |                |  |  |

| bit 6           |                                                                                                                          | x Receive Over                         |                                 |                   |                 |                |                |  |  |

|                 | 1 = A new b<br>previous                                                                                                  | yte/word is com<br>data in the SPI     | pletely receive<br>BUF register | ed and discard    | led; the user   | application ha | s not read the |  |  |

| L:4 F           |                                                                                                                          | has not occurre                        |                                 | lid in Enhance    |                 | - )            |                |  |  |

| bit 5           | 1 = RX FIFO                                                                                                              | Ix Receive FIFO                        | D Empty bit (va                 | lid in Enhance    | a Buller mode   | e)             |                |  |  |

|                 | 1 = RX FIFO<br>0 = RX FIFO                                                                                               |                                        |                                 |                   |                 |                |                |  |  |

| bit 4-2         |                                                                                                                          | SPIx Buffer Inte                       | errupt Mode bit                 | s (valid in Enh   | anced Buffer    | mode)          |                |  |  |

|                 |                                                                                                                          | pt when the SP                         | -                               |                   |                 | /              |                |  |  |

|                 |                                                                                                                          | pt when the las                        |                                 |                   |                 |                |                |  |  |

|                 | 100 = Interru                                                                                                            | pt when the las                        |                                 |                   |                 |                |                |  |  |

|                 |                                                                                                                          | ry location<br>pt when the SP          | ly receive buffe                | er is full (SPIRI | RF hit is set)  |                |                |  |  |

|                 |                                                                                                                          | pt when the SP                         |                                 |                   |                 |                |                |  |  |

|                 | 001 = Interru                                                                                                            | pt when data is                        | available in the                | e SPIx receive    | buffer (SRM     |                |                |  |  |

|                 | 000 = Interru                                                                                                            |                                        |                                 |                   |                 |                |                |  |  |

| R/W-0           | R/W-0                                                                                                                                                                       | R/W-0                                                                                    | U-0                                                                  | R/W-0, HC                           | R/W-0                                                                      | R-0                 | R-1             |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------|---------------------|-----------------|

| UTXISEL1        | UTXINV                                                                                                                                                                      | UTXISEL0                                                                                 |                                                                      | UTXBRK                              | UTXEN <sup>(1)</sup>                                                       | UTXBF               | TRMT            |

| bit 15          |                                                                                                                                                                             |                                                                                          |                                                                      |                                     |                                                                            |                     | bit 8           |

|                 |                                                                                                                                                                             |                                                                                          |                                                                      |                                     |                                                                            |                     |                 |

| R/W-0           | R/W-0                                                                                                                                                                       | R/W-0                                                                                    | R-1                                                                  | R-0                                 | R-0                                                                        | R/C-0               | R-0             |

| URXISEL1        | URXISEL0                                                                                                                                                                    | ADDEN                                                                                    | RIDLE                                                                | PERR                                | FERR                                                                       | OERR                | URXDA           |

| bit 7           |                                                                                                                                                                             |                                                                                          |                                                                      |                                     |                                                                            |                     | bit 0           |

| <del></del>     |                                                                                                                                                                             | 0 01 11                                                                                  |                                                                      |                                     |                                                                            |                     |                 |

| Legend:         | 1.11                                                                                                                                                                        | C = Clearable                                                                            |                                                                      |                                     | are Clearable bit                                                          |                     |                 |

| R = Readable    |                                                                                                                                                                             | W = Writable                                                                             | DIT                                                                  | •                                   | nented bit, read                                                           |                     |                 |

| -n = Value at F | POR                                                                                                                                                                         | '1' = Bit is set                                                                         |                                                                      | '0' = Bit is cle                    | ared                                                                       | x = Bit is unkr     | IOWN            |

| bit 15,13       | <ul> <li>11 = Reserve</li> <li>10 = Interrupt</li> <li>the trans</li> <li>01 = Interrupt</li> <li>operatio</li> <li>00 = Interrupt</li> </ul>                               | ed; do not use<br>t when a chara<br>smit buffer beco<br>t when the las<br>ns are complet | cter is transf<br>omes empty<br>it character<br>ed<br>cter is transf | is shifted out<br>Ferred to the Tra | election bits<br>ansmit Shift Reg<br>of the Transmit<br>ansmit Shift Reg   | t Shift Registe     | r; all transmit |

| bit 14          | $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle}}$ $0 = \text{UxTX Idle}$ $\frac{\text{If IREN = 1:}}{1 = \text{IrDA}^{\textcircled{B}} \text{ en}}$ $0 = \text{IrDA ence}$ | e state is '1'<br>coded UxTX Id<br>oded UxTX Idle                                        | le state is '1'<br>e state is '0'                                    |                                     |                                                                            |                     |                 |

| bit 12          | Unimplemen                                                                                                                                                                  | ted: Read as '                                                                           | )'                                                                   |                                     |                                                                            |                     |                 |

| bit 11          | 1 = Sends Sy<br>bit; cleare<br>0 = Sync Bre                                                                                                                                 | ed by hardware<br>ak transmissio                                                         | ext transmis<br>upon compl<br>n is disabled                          |                                     | followed by twe                                                            | elve '0' bits, foll | lowed by Stop   |

| bit 10          | UTXEN: UAR                                                                                                                                                                  | Tx Transmit Er                                                                           | nable bit <sup>(1)</sup>                                             |                                     |                                                                            |                     |                 |

|                 | 0 = Transmit                                                                                                                                                                |                                                                                          |                                                                      | ntrolled by UAR<br>ransmission is   | Tx<br>aborted and the                                                      | e buffer is rese    | t; UxTX pin is  |

| bit 9           | UTXBF: UAR                                                                                                                                                                  | Tx Transmit Bu                                                                           | iffer Full Stat                                                      | us bit (read-onl                    | y)                                                                         |                     |                 |

|                 | 1 = Transmit<br>0 = Transmit                                                                                                                                                |                                                                                          | ll, at least on                                                      | e more charact                      | er can be writte                                                           | n                   |                 |

| bit 8           | 1 = Transmit                                                                                                                                                                | Shift Register is                                                                        | s empty and t                                                        |                                     | ly)<br>s empty (the last<br>is in progress o                               |                     | as completed)   |

| bit 7-6         | 11 = Interrupt<br>10 = Interrupt<br>0x = Interrupt                                                                                                                          | t is set on UxRs<br>t is set on UxRs                                                     | SR transfer, i<br>SR transfer, r<br>ny character                     | naking the rece<br>is received and  | on bits<br>eive buffer full (i.<br>eive buffer 3/4 fu<br>d transferred fro | ll (i.e., has 3 da  | ita characters) |

#### REGISTER 21-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582) in the "dsPIC33/ PIC24 Family Reference Manual" for information on enabling the UART module for transmit operation.

## REGISTER 22-11: CxFEN1: CANx ACCEPTANCE FILTER ENABLE REGISTER 1

| R/W-1          | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1           | R/W-1 |

|----------------|-------|------------------|-------|--------------|------------------|-----------------|-------|

|                |       |                  | FLTE  | N<15:8>      |                  |                 |       |

| bit 15         |       |                  |       |              |                  |                 | bit 8 |

|                |       |                  |       |              |                  |                 |       |

| R/W-1          | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1           | R/W-1 |

|                |       |                  | FLTE  | N<7:0>       |                  |                 |       |

| bit 7          |       |                  |       |              |                  |                 | bit 0 |

|                |       |                  |       |              |                  |                 |       |

| Legend:        |       |                  |       |              |                  |                 |       |

| R = Readable b | oit   | W = Writable bit | t     | U = Unimpler | mented bit, read | <b>l as</b> '0' |       |

|                |       |                  |       |              |                  |                 |       |

'0' = Bit is cleared

bit 15-0

-n = Value at POR

FLTEN<15:0>: Enable Filter n to Accept Messages bits

'1' = Bit is set

1 = Enables Filter n

0 = Disables Filter n

## REGISTER 22-12: CxBUFPNT1: CANx FILTERS 0-3 BUFFER POINTER REGISTER 1

| R/W-0        | R/W-0         | R/W-0            | R/W-0            | R/W-0                              | R/W-0            | R/W-0              | R/W-0 |  |

|--------------|---------------|------------------|------------------|------------------------------------|------------------|--------------------|-------|--|

| F3BP3        | F3BP2         | F3BP1            | F3BP0            | F2BP3                              | F2BP2            | F2BP1              | F2BP0 |  |

| bit 15       |               |                  |                  |                                    | ·                |                    | bit 8 |  |

|              |               |                  |                  |                                    |                  |                    |       |  |

| R/W-0        | R/W-0         | R/W-0            | R/W-0            | R/W-0                              | R/W-0            | R/W-0              | R/W-0 |  |

| F1BP3        | F1BP2         | F1BP1            | F1BP0            | F0BP3                              | F0BP2            | F0BP1              | F0BP0 |  |

| bit 7        |               |                  |                  |                                    |                  |                    | bit 0 |  |

|              |               |                  |                  |                                    |                  |                    |       |  |

| Legend:      |               |                  |                  |                                    |                  |                    |       |  |

| R = Readab   | le bit        | W = Writable     | bit              | U = Unimplemented bit, read as '0' |                  |                    |       |  |

| -n = Value a | t POR         | '1' = Bit is set |                  | '0' = Bit is cleared               |                  | x = Bit is unknown |       |  |

|              |               |                  |                  |                                    |                  |                    |       |  |

| bit 15-12    | F3BP<3:0>:    | RX Buffer Mas    | k for Filter 3 b | oits                               |                  |                    |       |  |

|              | 1111 = Filter | hits received in | n RX FIFO bu     | ffer                               |                  |                    |       |  |

|              | 1110 = Filter | hits received in | n RX Buffer 14   | 4                                  |                  |                    |       |  |

|              | •             |                  |                  |                                    |                  |                    |       |  |

|              | •             |                  |                  |                                    |                  |                    |       |  |

|              | 0001 = Filter | hits received in | n RX Buffer 1    |                                    |                  |                    |       |  |

|              | 0000 = Filter | hits received in | n RX Buffer 0    |                                    |                  |                    |       |  |

| bit 11-8     | F2BP<3:0>:    | RX Buffer Mas    | k for Filter 2 b | its (same value                    | es as bits 15-12 | )                  |       |  |

| bit 7-4      | F1BP<3:0>:    | RX Buffer Mas    | k for Filter 1 b | its (same value                    | es as bits 15-12 | )                  |       |  |

| bit 3-0      | F0BP<3:0>:    | RX Buffer Mas    | k for Filter 0 b | its (same value                    | es as bits 15-12 | )                  |       |  |

|              |               |                  |                  |                                    |                  |                    |       |  |

x = Bit is unknown

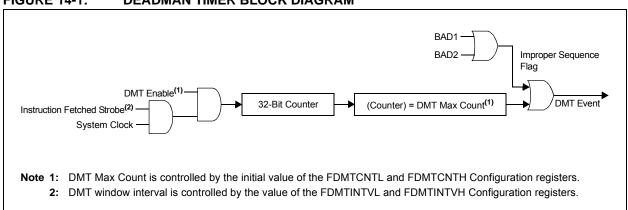

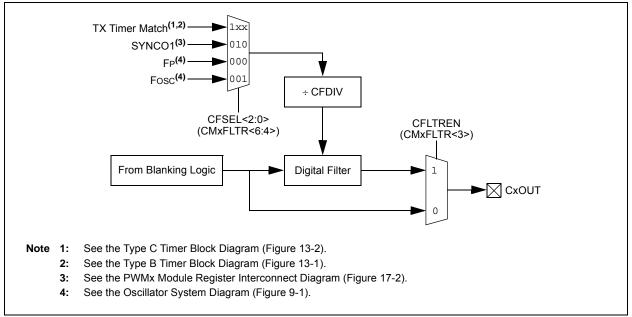

Figure 25-2, shows the user-programmable blanking function block diagram.

## FIGURE 25-2: USER-PROGRAMMABLE BLANKING FUNCTION BLOCK DIAGRAM

Figure 25-3, shows the digital filter interconnect block diagram.

#### FIGURE 25-3: DIGITAL FILTER INTERCONNECT BLOCK DIAGRAM

## REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

- bit 3 ABEN: AND Gate B Input Enable bit

- 1 = MBI is connected to AND gate

- 0 = MBI is not connected to AND gate

- bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate

- 0 = Inverted MBI is not connected to AND gate

- bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate

- bit 0 AANEN: AND Gate A Input Inverted Enable bit

- 1 = Inverted MAI is connected to AND gate

- 0 = Inverted MAI is not connected to AND gate

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed. In

these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

**Note:** For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| Field           | Description                                                                          |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------|--|--|--|--|

| #text           | Means literal defined by "text"                                                      |  |  |  |  |

| (text)          | Means "content of text"                                                              |  |  |  |  |

| [text]          | Means "the location addressed by text"                                               |  |  |  |  |

| {}              | Optional field or operation                                                          |  |  |  |  |

| $a\in\{b,c,d\}$ | a is selected from the set of values b, c, d                                         |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                                   |  |  |  |  |

| .b              | Byte mode selection                                                                  |  |  |  |  |

| .d              | Double-Word mode selection                                                           |  |  |  |  |

| .S              | Shadow register select                                                               |  |  |  |  |

| .W              | Word mode selection (default)                                                        |  |  |  |  |

| Acc             | One of two accumulators {A, B}                                                       |  |  |  |  |

| AWB             | Accumulator Write-Back Destination Address register ∈ {W13, [W13]+ = 2}              |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word-addressed instructions) $\in \{015\}$        |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                               |  |  |  |  |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |  |  |  |  |

| lit4            | 4-bit unsigned literal $\in \{015\}$                                                 |  |  |  |  |

| lit5            | 5-bit unsigned literal $\in \{031\}$                                                 |  |  |  |  |

| lit8            | 8-bit unsigned literal $\in \{0255\}$                                                |  |  |  |  |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode           |  |  |  |  |

| lit14           | 14-bit unsigned literal $\in \{016384\}$                                             |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                   |  |  |  |  |

| lit23           | 23-bit unsigned literal $\in$ {08388608}; LSb must be '0'                            |  |  |  |  |

| None            | Field does not require an entry, can be blank                                        |  |  |  |  |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |  |  |  |  |

| PC              | Program Counter                                                                      |  |  |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |  |  |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |  |  |  |  |

| Wb              | Base W register ∈ {W0W15}                                                            |  |  |  |  |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |  |  |  |  |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |  |  |

| Wm,Wn           | Dividend, Divisor Working register pair (Direct Addressing)                          |  |  |  |  |

TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax       | Description                                     | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------|-------------------------------------------------|---------------|----------------|--------------------------|

| 8                  | BSW                  | BSW.C   | Ws,Wb                 | Write C bit to Ws <wb></wb>                     | 1             | 1              | None                     |

|                    |                      | BSW.Z   | Ws,Wb                 | Write Z bit to Ws <wb></wb>                     | 1             | 1              | None                     |

| 9                  | BTG                  | BTG     | f,#bit4               | Bit Toggle f                                    | 1             | 1              | None                     |

|                    |                      | BTG     | Ws,#bit4              | Bit Toggle Ws                                   | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4               | Bit Test f, Skip if Clear                       | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC    | Ws,#bit4              | Bit Test Ws, Skip if Clear                      | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4               | Bit Test f, Skip if Set                         | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS    | Ws,#bit4              | Bit Test Ws, Skip if Set                        | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST    | f,#bit4               | Bit Test f                                      | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4              | Bit Test Ws to C                                | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4              | Bit Test Ws to Z                                | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                      | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                      | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4               | Bit Test then Set f                             | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4              | Bit Test Ws to C, then Set                      | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4              | Bit Test Ws to Z, then Set                      | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23                 | Call subroutine                                 | 2             | 4              | SFA                      |

|                    |                      | CALL    | Wn                    | Call indirect subroutine                        | 1             | 4              | SFA                      |

|                    |                      | CALL.L  | Wn                    | Call indirect subroutine (long address)         | 1             | 4              | SFA                      |

| 15                 | CLR                  | CLR     | f                     | f = 0x0000                                      | 1             | 1              | None                     |

|                    |                      | CLR     | WREG                  | WREG = 0x0000                                   | 1             | 1              | None                     |

|                    |                      | CLR     | Ws                    | Ws = 0x0000                                     | 1             | 1              | None                     |

|                    |                      | CLR     | Acc,Wx,Wxd,Wy,Wyd,AWB | Clear Accumulator                               | 1             | 1              | OA,OB,SA,<br>SB          |

| 16                 | CLRWDT               | CLRWDT  |                       | Clear Watchdog Timer                            | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM     | f                     | $f = \overline{f}$                              | 1             | 1              | N,Z                      |

|                    |                      | COM     | f,WREG                | WREG = f                                        | 1             | 1              | N,Z                      |

|                    |                      | COM     | Ws,Wd                 | $Wd = \overline{Ws}$                            | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f                     | Compare f with WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit8              | Compare Wb with lit8                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                 | Compare Wb with Ws (Wb – Ws)                    | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0     | f                     | Compare f with 0x0000                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws                    | Compare Ws with 0x0000                          | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                     | Compare f with WREG, with Borrow                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit8              | Compare Wb with lit8, with Borrow               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                 | Compare Wb with Ws, with Borrow $(Wb - Ws - C)$ | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb,Wn                 | Compare Wb with Wn, skip if =                   | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr            | Compare Wb with Wn, branch if =                 | 1             | 1 (5)          | None                     |

| 22                 | CPSGT                | CPSGT   | Wb,Wn                 | Compare Wb with Wn, skip if >                   | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr            | Compare Wb with Wn, branch if >                 | 1             | 1 (5)          | None                     |

| 23                 | CPSLT                | CPSLT   | Wb,Wn                 | Compare Wb with Wn, skip if <                   | 1             | 1<br>(2 or 3)  | None                     |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr            | Compare Wb with Wn, branch if <                 | 1             | 1 (5)          | None                     |

| 24                 | CPSNE                | CPSNE   | Wb,Wn                 | Compare Wb with Wn, skip if ≠                   | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      |         |                       |                                                 | -             | ,              |                          |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 53                 | MUL                  | MUL.SS  | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)       | 1             | 1              | None                     |

|                    |                      | MUL.SS  | Wb,Ws,Acc       | Accumulator = signed(Wb) * signed(Ws)             | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Acc       | Accumulator = signed(Wb) *<br>unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Acc    | Accumulator = signed(Wb) * unsigned(lit5)         | 1             | 1              | None                     |

|                    |                      | MUL.US  | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US  | Wb,Ws,Acc       | Accumulator = unsigned(Wb) *<br>signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc    | Accumulator = unsigned(Wb) *<br>unsigned(lit5)    | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Acc       | Accumulator = unsigned(Wb) *<br>unsigned(Ws)      | 1             | 1              | None                     |

|                    |                      | MULW.SS | Wb,Ws,Wnd       | Wnd = signed(Wb) * signed(Ws)                     | 1             | 1              | None                     |

|                    |                      | MULW.SU | Wb,Ws,Wnd       | Wnd = signed(Wb) * unsigned(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.US | Wb,Ws,Wnd       | Wnd = unsigned(Wb) * signed(Ws)                   | 1             | 1              | None                     |

|                    |                      | MULW.UU | Wb,Ws,Wnd       | Wnd = unsigned(Wb) * unsigned(Ws)                 | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5)   | 1             | 1              | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd    | Wnd = signed(Wb) * unsigned(lit5)                 | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd    | Wnd = unsigned(Wb) * unsigned(lit5)               | 1             | 1              | None                     |

|                    |                      | MUL     | f               | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 54                 | NEG                  | NEG     | Acc             | Negate Accumulator                                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG     | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG     | f,WREG          | WREG = $f + 1$                                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG     | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 55                 | NOP                  | NOP     |                 | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR    |                 | No Operation                                      | 1             | 1              | None                     |