Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 256КВ (85.5К х 24)                                                                |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 11x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

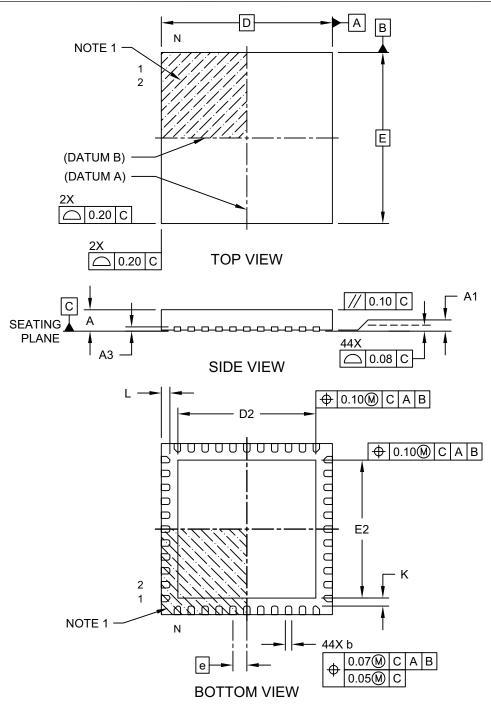

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm102t-i-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*, which are available from the Microchip web site (www.microchip.com). The following documents should be considered as the general reference for the operation of a particular module or device feature:

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "dsPIC33E/PIC24E Program Memory" (DS70000613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70000600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70000598)

- "Timers" (DS70362)

- "CodeGuard™ Intermediate Security" (DS70005182)

- "Deadman Timer (DMT)" (DS70005155)

- "Input Capture" (DS70000352)

- "Output Compare" (DS70005157)

- "High-Speed PWM"(DS70645)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582)

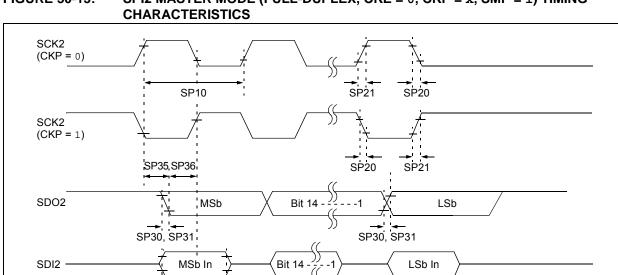

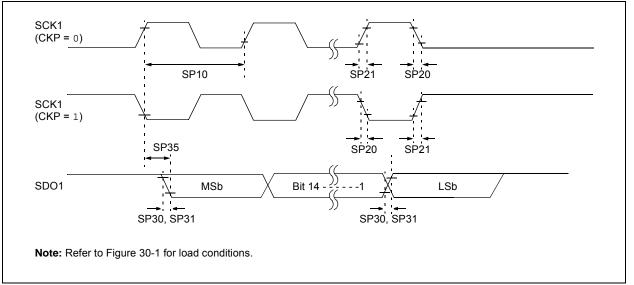

- "Serial Peripheral Interface (SPI)" (DS70005185)

- "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195)

- "Enhanced Controller Area Network (ECAN™)"(DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70000357)

- "Device Configuration" (DS70000618)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

- "Single-Edge Nibble Transmission (SENT) Module" (DS70005145)

## TABLE 1-1: PINOUT I/O DESCRIPTIONS

| Pin Name                        | Pin<br>Type | Buffer<br>Type | PPS        | Description                                                                                                                                                                        |

|---------------------------------|-------------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN19<br>AN24-AN32           | I           | Analog         | No         | Analog input channels.                                                                                                                                                             |

| AN48, AN49                      |             |                |            |                                                                                                                                                                                    |

| AN51-AN56                       |             |                |            |                                                                                                                                                                                    |

| CLKI                            | I           | ST/<br>CMOS    | No         | External clock source input. Always associated with OSC1 pin function.                                                                                                             |

| CLKO                            | 0           | _              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                            | I           | ST/<br>CMOS    | No         | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                    |

| OSC2                            | I/O         | _              | No         | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                           |

| REFCLKO                         | 0           |                | Yes        | Reference clock output.                                                                                                                                                            |

| IC1-IC4                         | 1           | ST             | Yes        | Capture Inputs 1 to 4.                                                                                                                                                             |

| OCFA                            | 1           | ST             | Yes        | Compare Fault A input (for compare channels).                                                                                                                                      |

| OC1-OC4                         | 0           |                | Yes        | Compare Outputs 1 to 4.                                                                                                                                                            |

| INT0                            | I           | ST             | No         | External Interrupt 0.                                                                                                                                                              |

| INT1                            | I           | ST             | Yes        | External Interrupt 1.                                                                                                                                                              |

| INT2                            | I           | ST             | Yes        | External Interrupt 2.                                                                                                                                                              |

| RA0-RA4, RA7-RA12               | I/O         | ST             | Yes        | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                        | I/O         | ST             | Yes        | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                  | I/O         | ST             | Yes        | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5-RD6, RD8                    | I/O         | ST             | Yes        | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                       | I/O         | ST             | Yes        | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0-RF1                         | I/O         | ST             | No         | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                         | I/O         | ST             | Yes        | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                            | I           | ST             | No         | Timer1 external clock input.                                                                                                                                                       |

| T2CK                            | I           | ST             | Yes        | Timer2 external clock input.                                                                                                                                                       |

| T3CK                            | I           | ST             | No         | Timer3 external clock input.                                                                                                                                                       |

| T4CK<br>T5CK                    |             | ST<br>ST       | No         | Timer4 external clock input.                                                                                                                                                       |

| CTPLS                           |             | ST             | No         | Timer5 external clock input.                                                                                                                                                       |

| CTED1                           | 0           | ST             | No<br>No   | CTMU pulse output.<br>CTMU External Edge Input 1.                                                                                                                                  |

| CTED2                           | i           | ST             | No         | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                           |             | ST             | Yes        | UART1 Clear-to-Send.                                                                                                                                                               |

| U1RTS                           | Ö           | _              | Yes        | UART1 Ready-to-Send.                                                                                                                                                               |

| U1RX                            | I           | ST             | Yes        | UART1 receive.                                                                                                                                                                     |

| U1TX                            | 0           |                | Yes        | UART1 transmit.                                                                                                                                                                    |

| U2CTS                           | I           | ST             | Yes        | UART2 Clear-to-Send.                                                                                                                                                               |

| U2RTS                           | 0           |                | Yes        | UART2 Ready-to-Send.                                                                                                                                                               |

| U2RX<br>U2TX                    | 0           | ST             | Yes<br>Yes | UART2 receive.<br>UART2 transmit.                                                                                                                                                  |

| SCK1                            | 1/0         | ST             | No         | Synchronous serial clock input/output for SPI1.                                                                                                                                    |

| SDI1                            | 1           | ST             | No         | SPI1 data in.                                                                                                                                                                      |

| SDO1                            | Ó           | _              | No         | SPI1 data out.                                                                                                                                                                     |

| SS1                             | I/O         | ST             | No         | SPI1 slave synchronization or frame pulse I/O.                                                                                                                                     |

| Legend: CMOS = CM<br>ST = Schmi |             |                |            |                                                                                                                                                                                    |

| PPS = Perip                     |             |                |            | TTL = TTL input buffer                                                                                                                                                             |

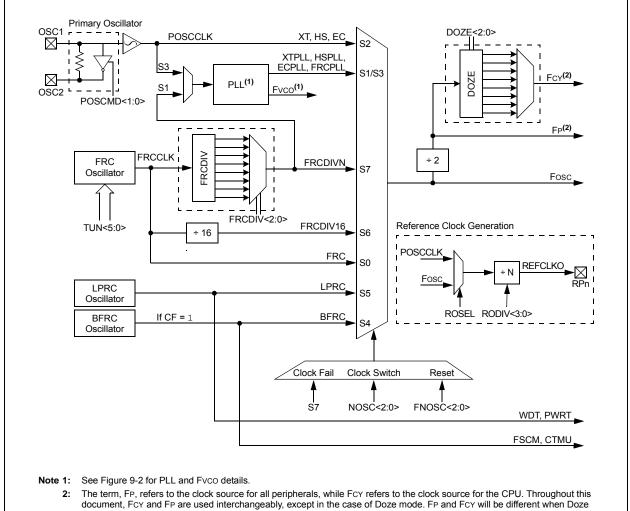

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

**OSCILLATOR SYSTEM DIAGRAM**

FIGURE 9-1:

The dsPIC33EVXXXGM00X/10X family oscillator system provides:

- On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- On-the-Fly Clock Switching between Various Clock Sources

- · Doze mode for System Power Savings

- Fail-Safe Clock Monitor (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown.

- Backup FRC (BFRC) Function that Provides a System Clock when there is a Failure in the FRC Clock

- Configuration bits for Clock Source Selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

NOTES:

## 11.6 High-Voltage Detect (HVD)

dsPIC33EVXXXGM00X/10X devices contain High-Voltage Detection (HVD) which monitors the VCAP voltage. The HVD is used to monitor the VCAP supply voltage to ensure that an external connection does not raise the value above a safe level (~2.4V). If high core voltage is detected, all I/Os are disabled and put in a tristate condition. The device remains in this I/O tri-state condition as long as the high-voltage condition is present.

## 11.7 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-10 under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes that the resulting current being injected into the device, that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name, from left-to-right. The left most function name takes precedence over any function to its right in the naming convention; for example, AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD – 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

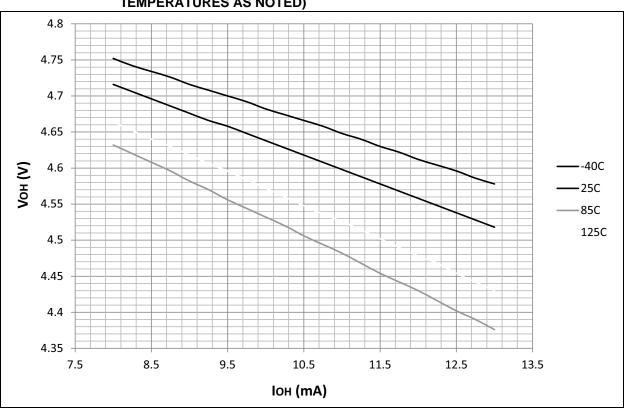

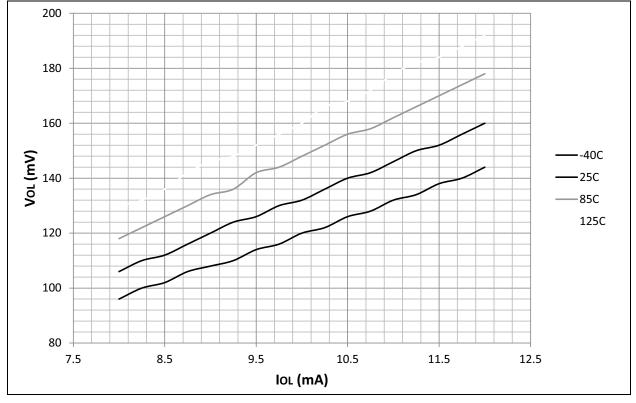

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specifications. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 4.4V at IOH = -8 mA and VDD = 5V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current, <12 mA, is technically permitted. For more information, refer to the VOH/ IOH specifications in **Section 30.0 "Electrical Characteristics"**.

## 18.2 SPI Control Registers

## REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| R/W-0           | U-0                                                                                                                                                                                                    | R/W-0                                  | U-0                             | U-0                | R/W-0                       | R/W-0                  | R/W-0          |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|--------------------|-----------------------------|------------------------|----------------|--|--|

| SPIEN           | _                                                                                                                                                                                                      | SPISIDL                                |                                 | _                  | SPIBEC2                     | SPIBEC1                | SPIBEC0        |  |  |

| bit 15          |                                                                                                                                                                                                        |                                        |                                 |                    |                             |                        | bit 8          |  |  |

|                 |                                                                                                                                                                                                        |                                        |                                 |                    |                             |                        |                |  |  |

| R/W-0           | R/C-0, HS                                                                                                                                                                                              | R/W-0                                  | R/W-0                           | R/W-0              | R/W-0                       | R-0, HS, HC            | R-0, HS, HC    |  |  |

| SRMPT           | SPIROV                                                                                                                                                                                                 | SRXMPT                                 | SISEL2                          | SISEL1             | SISEL0                      | SPITBF                 | SPIRBF         |  |  |

| bit 7           |                                                                                                                                                                                                        |                                        |                                 |                    |                             |                        | bit C          |  |  |

|                 |                                                                                                                                                                                                        |                                        |                                 |                    |                             |                        |                |  |  |

| Legend:         |                                                                                                                                                                                                        | HC = Hardware                          | e Clearable bit                 |                    | are Settable b              |                        |                |  |  |

| R = Readable    |                                                                                                                                                                                                        | W = Writable b                         | pit                             | U = Unimple        | mented bit, re              | ead as '0'             |                |  |  |

| -n = Value at I | POR                                                                                                                                                                                                    | '1' = Bit is set                       |                                 | '0' = Bit is cle   | eared                       | C = Clearable          | e bit          |  |  |

| bit 15          | SPIEN: SPIX                                                                                                                                                                                            | Enable bit                             |                                 |                    |                             |                        |                |  |  |

| bit 10          |                                                                                                                                                                                                        | he SPIx module                         | and configure                   | s SCKx SDO         | $c$ SDIx and $\overline{S}$ | <u>Sx</u> as serial po | rt pins        |  |  |

|                 |                                                                                                                                                                                                        | the SPIx module                        | •                               |                    |                             |                        | it pino        |  |  |

| bit 14          | Unimplemen                                                                                                                                                                                             | ted: Read as '0                        | ,                               |                    |                             |                        |                |  |  |

| bit 13          | SPISIDL: SP                                                                                                                                                                                            | Ix Stop in Idle M                      | ode bit                         |                    |                             |                        |                |  |  |

|                 |                                                                                                                                                                                                        | ues the SPIx most the SPIx modu        |                                 |                    | vice enters Idl             | e mode                 |                |  |  |

| bit 12-11       | Unimplemented: Read as '0'                                                                                                                                                                             |                                        |                                 |                    |                             |                        |                |  |  |

| bit 10-8        | SPIBEC<2:0                                                                                                                                                                                             | >: SPIx Buffer E                       | lement Count I                  | oits (valid in Er  | nhanced Buffe               | er mode)               |                |  |  |

|                 | Master mode:<br>Number of SPIx transfers are pending.                                                                                                                                                  |                                        |                                 |                    |                             |                        |                |  |  |

|                 | Slave mode:                                                                                                                                                                                            | Plx transfers are                      |                                 |                    |                             |                        |                |  |  |

| bit 7           | SRMPT: SPIX                                                                                                                                                                                            | Shift Register                         | (SPIxSR) Empt                   | ty bit (valid in E | Enhanced But                | fer mode)              |                |  |  |

|                 | 1 = The SPIx                                                                                                                                                                                           | Shift register is<br>Shift register is | empty and rea                   | •                  |                             | -                      |                |  |  |

| bit 6           |                                                                                                                                                                                                        | x Receive Over                         |                                 |                    |                             |                        |                |  |  |

|                 | 1 = A new b<br>previous                                                                                                                                                                                | yte/word is com<br>data in the SPI     | pletely receive<br>BUF register | ed and discard     | led; the user               | application ha         | s not read the |  |  |

| L:4 F           |                                                                                                                                                                                                        | has not occurre                        |                                 | lid in Enhance     |                             | - )                    |                |  |  |

| bit 5           | 1 = RX FIFO                                                                                                                                                                                            | Ix Receive FIFO                        | D Empty bit (va                 | lid in Enhance     | a Buller mode               | e)                     |                |  |  |

|                 | 1 = RX FIFO<br>0 = RX FIFO                                                                                                                                                                             |                                        |                                 |                    |                             |                        |                |  |  |

| bit 4-2         |                                                                                                                                                                                                        | SPIx Buffer Inte                       | errupt Mode bit                 | s (valid in Enh    | anced Buffer                | mode)                  |                |  |  |

|                 |                                                                                                                                                                                                        |                                        | -                               |                    |                             | /                      |                |  |  |

|                 | <ul> <li>111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)</li> <li>110 = Interrupt when the last bit is shifted into SPIxSR, and as a result, the TX FIFO is empty</li> </ul> |                                        |                                 |                    |                             |                        |                |  |  |

|                 | 100 = Interru                                                                                                                                                                                          | pt when the las                        |                                 |                    |                             |                        |                |  |  |

|                 |                                                                                                                                                                                                        | ry location<br>pt when the SP          | ly receive buffe                | er is full (SPIRI  | RF hit is set)              |                        |                |  |  |

|                 |                                                                                                                                                                                                        | pt when the SP                         |                                 |                    |                             |                        |                |  |  |

|                 | 001 = Interru                                                                                                                                                                                          | pt when data is                        | available in the                | e SPIx receive     | buffer (SRM                 |                        |                |  |  |

|                 | 000 = Interru                                                                                                                                                                                          |                                        |                                 |                    |                             |                        |                |  |  |

| U-0                 | U-0                                                          | U-0                                 | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |

|---------------------|--------------------------------------------------------------|-------------------------------------|----------------------|----------------------------------------|----------------------|----------------------|----------------------|--|

|                     |                                                              |                                     | DISSCK               | DISSDO                                 | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |

| bit 15              |                                                              |                                     | Diocon               | DICCDO                                 | MODEIO               | Olin                 | bit                  |  |

|                     |                                                              |                                     |                      |                                        |                      |                      |                      |  |

| R/W-0               | R/W-0                                                        | R/W-0                               | R/W-0                | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                |  |

| SSEN <sup>(2)</sup> | CKP                                                          | MSTEN                               | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup>                   | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |

| bit 7               |                                                              |                                     |                      | 1                                      |                      |                      | bit                  |  |

|                     |                                                              |                                     |                      |                                        |                      |                      |                      |  |

| Legend:             |                                                              |                                     |                      |                                        |                      |                      |                      |  |

| R = Readab          | le bit                                                       | W = Writable                        | bit                  | U = Unimplen                           | nented bit, read     | <b>l as</b> '0'      |                      |  |

| -n = Value a        | t POR                                                        | '1' = Bit is set                    |                      | '0' = Bit is clea                      | ared                 | x = Bit is unkr      | nown                 |  |

|                     |                                                              |                                     | _ 1                  |                                        |                      |                      |                      |  |

| bit 15-13           | -                                                            | ted: Read as '                      |                      |                                        |                      |                      |                      |  |

| bit 12              |                                                              | PI clock is disa                    | -                    | er modes only)                         |                      |                      |                      |  |

|                     |                                                              | PI clock is disa<br>PI clock is ena |                      | ao 1/U                                 |                      |                      |                      |  |

| bit 11              |                                                              | able SDOx Pin                       |                      |                                        |                      |                      |                      |  |

|                     | 1 = SDOx pin is not used by the module; pin functions as I/O |                                     |                      |                                        |                      |                      |                      |  |

|                     |                                                              | is controlled b                     |                      |                                        |                      |                      |                      |  |

| bit 10              | MODE16: Wo                                                   | ord/Byte Comm                       | unication Sele       | ect bit                                |                      |                      |                      |  |

|                     | 1 = Communication is word-wide (16 bits)                     |                                     |                      |                                        |                      |                      |                      |  |

|                     |                                                              | cation is byte-                     | . ,                  |                                        |                      |                      |                      |  |

| bit 9               |                                                              | ata Input Samp                      | ole Phase bit        |                                        |                      |                      |                      |  |

|                     | Master mode:                                                 | :<br>a is sampled at                | the end of da        | ta output time                         |                      |                      |                      |  |

|                     |                                                              |                                     |                      | data output time                       | ie                   |                      |                      |  |

|                     | Slave mode:                                                  | -                                   |                      | n Slave mode.                          |                      |                      |                      |  |

| bit 8               | CKE: Clock E                                                 | dge Select bit                      | 1)                   |                                        |                      |                      |                      |  |

|                     |                                                              |                                     |                      |                                        | clock state to Id    |                      |                      |  |

| bit 7               | SSEN: Slave                                                  | Select Enable                       | bit (Slave mo        | de) <sup>(2)</sup>                     |                      |                      |                      |  |

|                     |                                                              | s used for Slav                     |                      |                                        |                      |                      |                      |  |

|                     | 0 = SSx pin is                                               | s not used by the                   | ne module; pir       | n is controlled b                      | y port function      |                      |                      |  |

| bit 6               |                                                              | olarity Select I                    |                      |                                        |                      |                      |                      |  |

|                     |                                                              |                                     |                      | ve state is a low<br>e state is a high |                      |                      |                      |  |

| bit 5               | MSTEN: Mas                                                   | ter Mode Enab                       | le bit               |                                        |                      |                      |                      |  |

|                     | 1 = Master m<br>0 = Slave mo                                 |                                     |                      |                                        |                      |                      |                      |  |

|                     | he CKE bit is not<br>FRMEN = 1).                             | used in Frame                       | d SPI modes.         | Program this b                         | oit to '0' for Frai  | med SPI modes        | S                    |  |

| -                   | his bit must be cl                                           | eared when FF                       | RMEN = 1.            |                                        |                      |                      |                      |  |

|                     | o not set both pri                                           |                                     |                      | ers to the value                       | e of 1:1.            |                      |                      |  |

#### REGISTER 18-2: SPIxCON1: SPIx CONTROL REGISTER 1

**3:** Do not set both primary and secondary prescalers to the value of 1:1.

| R/W-0         | R/W-0                                                                   | R/W-0            | R/W-0            | R/W-0                              | R/W-0             | R/W-0              | R/W-0 |  |

|---------------|-------------------------------------------------------------------------|------------------|------------------|------------------------------------|-------------------|--------------------|-------|--|

| F7BP3         | F7BP2                                                                   | F7BP1            | F7BP0            | F6BP3                              | F6BP2             | F6BP1              | F6BP0 |  |

| bit 15        |                                                                         | -                |                  |                                    |                   |                    | bit 8 |  |

|               |                                                                         |                  |                  |                                    |                   |                    |       |  |

| R/W-0         | R/W-0                                                                   | R/W-0            | R/W-0            | R/W-0                              | R/W-0             | R/W-0              | R/W-0 |  |

| F5BP3         | F5BP2                                                                   | F5BP1            | F5BP0            | F4BP3                              | F4BP2             | F4BP1              | F4BP0 |  |

| bit 7         |                                                                         |                  |                  |                                    |                   |                    | bit 0 |  |

|               |                                                                         |                  |                  |                                    |                   |                    |       |  |

| Legend:       |                                                                         |                  |                  |                                    |                   |                    |       |  |

| R = Readable  | e bit                                                                   | W = Writable bit |                  | U = Unimplemented bit, read as '0' |                   |                    |       |  |

| -n = Value at | POR                                                                     | '1' = Bit is set |                  | '0' = Bit is cleared               |                   | x = Bit is unknown |       |  |

|               |                                                                         |                  |                  |                                    |                   |                    |       |  |

| bit 15-12     | F7BP<3:0>:                                                              | RX Buffer Masl   | k for Filter 7 b | its                                |                   |                    |       |  |

|               | 1111 = Filter                                                           | hits received in | NRX FIFO bu      | ffer                               |                   |                    |       |  |

|               | 1110 <b>= Filter</b>                                                    | hits received in | RX Buffer 14     | 1                                  |                   |                    |       |  |

|               | •                                                                       |                  |                  |                                    |                   |                    |       |  |

|               | •                                                                       |                  |                  |                                    |                   |                    |       |  |

|               | •<br>0001 - Filtor                                                      | hits received in |                  |                                    |                   |                    |       |  |

|               | 0001                                                                    | hits received in |                  |                                    |                   |                    |       |  |

| bit 11-8      |                                                                         |                  |                  | its (same value                    | es as bits 15-12) |                    |       |  |

|               |                                                                         |                  |                  | -                                  | -                 |                    |       |  |

| bit 7-4       | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits 15-12) |                  |                  |                                    |                   |                    |       |  |

## REGISTER 22-13: CxBUFPNT2: CANx FILTERS 4-7 BUFFER POINTER REGISTER 2

bit 3-0 **F4BP<3:0>:** RX Buffer Mask for Filter 4 bits (same values as bits 15-12)

| R/W-0             | R/W-0                | R/W-0                                                                                                                                                                            | R/W-0            | R/W-0                | R/W-0                              | R/W-0              | R/W-0  |  |

|-------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|------------------------------------|--------------------|--------|--|

| F15BP3            | F15BP2               | F15BP1                                                                                                                                                                           | F15BP0           | F14BP3               | F14BP2                             | F14BP1             | F14BP0 |  |

| bit 15            |                      |                                                                                                                                                                                  |                  |                      | •                                  |                    | bit 8  |  |

|                   |                      |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

| R/W-0             | R/W-0                | R/W-0                                                                                                                                                                            | R/W-0            | R/W-0                | R/W-0                              | R/W-0              | R/W-0  |  |

| F13BP3            | F13BP2               | F13BP1                                                                                                                                                                           | F13BP0           | F12BP3               | F12BP2                             | F12BP1             | F12BP0 |  |

| bit 7             |                      |                                                                                                                                                                                  |                  |                      |                                    |                    | bit 0  |  |

|                   |                      |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

| Legend:           |                      |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

| R = Readable bit  |                      | W = Writable                                                                                                                                                                     | W = Writable bit |                      | U = Unimplemented bit, read as '0' |                    |        |  |

| -n = Value at POR |                      | '1' = Bit is set                                                                                                                                                                 |                  | '0' = Bit is cleared |                                    | x = Bit is unknown |        |  |

|                   |                      |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

| bit 15-12         | F15BP<3:0>:          | RX Buffer Ma                                                                                                                                                                     | sk for Filter 15 | 5 bits               |                                    |                    |        |  |

|                   | 1111 = Filter        | hits received in                                                                                                                                                                 | n RX FIFO but    | ffer                 |                                    |                    |        |  |

|                   | 1110 <b>= Filter</b> | hits received in                                                                                                                                                                 | n RX Buffer 14   | ļ.                   |                                    |                    |        |  |

|                   | •                    |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

|                   | •                    |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

|                   | 0001 <b>= Filter</b> | hits received ir                                                                                                                                                                 | n RX Buffer 1    |                      |                                    |                    |        |  |

|                   | 0000 <b>= Filter</b> | hits received in                                                                                                                                                                 | n RX Buffer 0    |                      |                                    |                    |        |  |

| bit 11-8          | F14BP<3:0>:          | RX Buffer Ma                                                                                                                                                                     | sk for Filter 14 | l bits (same va      | lues as bits 15-                   | 12)                |        |  |

| bit 7-4           | F13BP<3:0>:          | RX Buffer Ma                                                                                                                                                                     | sk for Filter 13 | 3 bits (same va      | lues as bits 15-                   | 12)                |        |  |

| bit 3-0           | F12BP<3:0>:          | <b>F13BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 13 bits (same values as bits 15-12)<br><b>F12BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 12 bits (same values as bits 15-12) |                  |                      |                                    |                    |        |  |

|                   |                      |                                                                                                                                                                                  |                  |                      |                                    |                    |        |  |

#### REGISTER 22-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

#### REGISTER 22-20: CxRXMnSID: CANx ACCEPTANCE FILTER MASK n STANDARD IDENTIFIER REGISTER (n = 0-2)

|                                    |                                          | •                                                                                      | •                               |                                    |                                                            |                 |                |  |  |

|------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------|------------------------------------|------------------------------------------------------------|-----------------|----------------|--|--|

| R/W-x                              | R/W-x                                    | R/W-x                                                                                  | R/W-x                           | R/W-x                              | R/W-x                                                      | R/W-x           | R/W-x          |  |  |

| SID10                              | SID9                                     | SID8                                                                                   | SID7                            | SID6                               | SID5                                                       | SID4            | SID3           |  |  |

| bit 15                             |                                          |                                                                                        |                                 |                                    | •                                                          |                 | bit 8          |  |  |

| R/W-x                              | R/W-x                                    | R/W-x                                                                                  | U-0                             | R/W-x                              | U-0                                                        | R/W-x           | R/W-x          |  |  |

| SID2                               | SID1                                     | SID0                                                                                   | _                               | MIDE                               | _                                                          | EID17           | EID16          |  |  |

| bit 7                              |                                          |                                                                                        |                                 |                                    |                                                            |                 | bit C          |  |  |

|                                    |                                          |                                                                                        |                                 |                                    |                                                            |                 |                |  |  |

| Legend:                            |                                          |                                                                                        |                                 |                                    |                                                            |                 |                |  |  |

| R = Readable bit W = Writable bit  |                                          |                                                                                        |                                 | U = Unimplemented bit, read as '0' |                                                            |                 |                |  |  |

| -n = Value at POR '1' = Bit is set |                                          |                                                                                        |                                 | '0' = Bit is cle                   | eared                                                      | x = Bit is unkr | Iown           |  |  |

| bit 15-5<br>bit 4                  | 1 = Includes<br>0 = Bit, SIDx,           | Standard Identi<br>bit, SIDx, in filto<br>, is a don't care<br>h <b>ted:</b> Read as ' | er comparisor<br>in filter comp |                                    |                                                            |                 |                |  |  |

| bit 3                              | 1 = Matches<br>the filter<br>0 = Matches | either standard                                                                        | types (standa                   | address messa                      | address) that c<br>ge if filters match<br>/lessage SID/EII | n, i.e., if:    | e EXIDE bit ir |  |  |

| bit 2                              | Unimplemer                               | nted: Read as                                                                          | 0'                              |                                    |                                                            |                 |                |  |  |

| bit 1-0                            | 1 = Includes                             | Extended Ider<br>bit, EIDx, in filt<br>a, is a don't car                               | ter compariso                   |                                    |                                                            |                 |                |  |  |

|                                    |                                          |                                                                                        |                                 |                                    |                                                            |                 |                |  |  |

#### REGISTER 22-21: CxRXMnEID: CANx ACCEPTANCE FILTER MASK n EXTENDED IDENTIFIER REGISTER (n = 0-2)

| R/W-x                             | R/W-x            | R/W-x       | R/W-x                                                   | R/W-x                                                                                                                   | R/W-x                                                                                                 | R/W-x                                                                                                              |

|-----------------------------------|------------------|-------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|                                   |                  | EID<        | <15:8>                                                  |                                                                                                                         |                                                                                                       |                                                                                                                    |

|                                   |                  |             |                                                         |                                                                                                                         |                                                                                                       | bit 8                                                                                                              |

| R/W-x                             | R/W-x            | R/W-x       | R/W-x                                                   | R/W-x                                                                                                                   | R/W-x                                                                                                 | R/W-x                                                                                                              |

|                                   |                  | EID         | <7:0>                                                   |                                                                                                                         |                                                                                                       |                                                                                                                    |

|                                   |                  |             |                                                         |                                                                                                                         |                                                                                                       | bit 0                                                                                                              |

|                                   |                  |             |                                                         |                                                                                                                         |                                                                                                       |                                                                                                                    |

| R = Readable bit W = Writable bit |                  |             | U = Unimplemented bit, read as '0'                      |                                                                                                                         |                                                                                                       |                                                                                                                    |

| OR                                | '1' = Bit is set |             | '0' = Bit is clea                                       | ared                                                                                                                    | x = Bit is unkr                                                                                       | nown                                                                                                               |

|                                   | R/W-x            | R/W-x R/W-x | EID<br>R/W-x R/W-x R/W-x<br>EID<br>bit W = Writable bit | EID<15:8>          R/W-x       R/W-x       R/W-x         EID<7:0>         Dit       W = Writable bit       U = Unimplen | EID<15:8> $R/W-x R/W-x R/W-x R/W-x R/W-x$ $EID<7:0>$ bit W = Writable bit U = Unimplemented bit, real | EID<15:8> $R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x$ $EID<7:0>$ bit W = Writable bit U = Unimplemented bit, read as '0' |

bit 15-0

- EID<15:0>: Extended Identifier bits

- 1 = Includes bit, EIDx, in filter comparison

- 0 = Bit, EIDx, is a don't care in filter comparison

| R/W-0          | U-0                                                                                                     | R/W-0                                                                                                    | R/W-0                                       | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |  |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------|----------------------------------------|----------------|-------|--|--|--|--|--|--|

| HLMS           | 0-0                                                                                                     | OCEN                                                                                                     | OCNEN                                       | OBEN             | OBNEN                                  | OAEN           | OANEN |  |  |  |  |  |  |

|                |                                                                                                         | OCEN                                                                                                     | OCINEIN                                     | OBEN             | OBNEN                                  | UAEN           |       |  |  |  |  |  |  |

| bit 15         |                                                                                                         |                                                                                                          |                                             |                  |                                        |                | bit 8 |  |  |  |  |  |  |

| R/W-0          | R/W-0                                                                                                   | R/W-0                                                                                                    | R/W-0                                       | R/W-0            | R/W-0                                  | R/W-0          | R/W-0 |  |  |  |  |  |  |

| NAGS           | PAGS                                                                                                    | ACEN                                                                                                     | ACNEN                                       | ABEN             | ABNEN                                  | AAEN           | AANEN |  |  |  |  |  |  |

| bit 7          |                                                                                                         |                                                                                                          |                                             |                  |                                        |                | bit   |  |  |  |  |  |  |

|                |                                                                                                         |                                                                                                          |                                             |                  |                                        |                |       |  |  |  |  |  |  |

| Legend:        |                                                                                                         |                                                                                                          |                                             |                  |                                        |                |       |  |  |  |  |  |  |

| R = Readab     | le bit                                                                                                  | W = Writable                                                                                             | bit                                         | U = Unimpler     | mented bit, read                       | <b>as</b> '0'  |       |  |  |  |  |  |  |

| -n = Value a   | t POR                                                                                                   | '1' = Bit is se                                                                                          |                                             | '0' = Bit is cle | ared                                   | x = Bit is unk | nown  |  |  |  |  |  |  |

| bit 15         | 1 = The mask                                                                                            | ing (blanking)                                                                                           |                                             | event any asse   | rted ('0') compai<br>rted ('1') compai |                |       |  |  |  |  |  |  |

| bit 14         | Unimplemen                                                                                              | ted: Read as                                                                                             | '0'                                         |                  |                                        |                |       |  |  |  |  |  |  |

| bit 13         | OCEN: OR G                                                                                              | ate C Input E                                                                                            | nable bit                                   |                  |                                        |                |       |  |  |  |  |  |  |

|                |                                                                                                         | nnected to OF<br>t connected to                                                                          | <b>U</b>                                    |                  |                                        |                |       |  |  |  |  |  |  |

| bit 12         |                                                                                                         |                                                                                                          | nverted Enable                              | e bit            |                                        |                |       |  |  |  |  |  |  |

|                |                                                                                                         | = Inverted MCI is connected to OR gate                                                                   |                                             |                  |                                        |                |       |  |  |  |  |  |  |

|                | 0 = Inverted I                                                                                          | MCI is not con                                                                                           | nected to OR g                              | ate              |                                        |                |       |  |  |  |  |  |  |