Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 256КВ (85.5К х 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 36-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 36-UQFN (5x5)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ev256gm103-e-m5 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

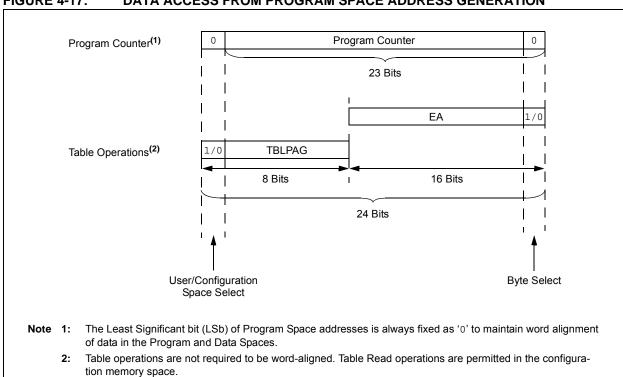

The CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 3.1 Registers

The dsPIC33EVXXXGM00X/10X family devices have sixteen, 16-bit Working registers in the programmer's model. Each of the Working registers can act as a Data, Address or Address Offset register. The sixteenth Working register (W15) operates as a Software Stack Pointer for interrupts and calls.

In addition, the dsPIC33EVXXXGM00X/10X devices include two alternate Working register sets, which consist of W0 through W14. The alternate registers can be made persistent to help reduce the saving and restoring of register content during Interrupt Service Routines (ISRs). The alternate Working registers can be assigned to a specific Interrupt Priority Level (IPL1 through IPL6) by configuring the CTXTx<2:0> bits in the FALTREG Configuration register.

The alternate Working registers can also be accessed manually by using the CTXTSWP instruction.

The CCTXI<2:0> and MCTXI<2:0> bits in the CTXTSTAT register can be used to identify the current, and most recent, manually selected Working register sets.

### 3.2 Instruction Set

The device instruction set has two classes of instructions: the MCU class of instructions and the DSP class of instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

### 3.3 Data Space Addressing

The Base Data Space can be addressed as 4K words or 8 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EV devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Space boundary is device-specific.

The upper 32 Kbytes of the Data Space (DS) memory map can optionally be mapped into Program Space (PS) at any 16K program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Data Space Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. For more information on EDS, PSV and table accesses, refer to "Data Memory" (DS70595) and "dsPIC33E/PIC24E Program Memory" (DS70000613) in the "dsPIC33/ PIC24 Family Reference Manual".

On dsPIC33EV devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms. Figure 3-1 illustrates the block diagram of the dsPIC33EVXXXGM00X/10X family devices.

### 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

| R/W-0               | U-0                          | R/W-0                                                 | R/W-0                                                | EGISTER             | R-0             | R-0             | R-0        |

|---------------------|------------------------------|-------------------------------------------------------|------------------------------------------------------|---------------------|-----------------|-----------------|------------|

| VAR                 | 0-0                          | US1                                                   | US0                                                  | EDT <sup>(1)</sup>  | DL2             | DL1             | R-0<br>DL0 |

| pit 15              | _                            | 031                                                   | 030                                                  | EDI                 | DL2             |                 | bLU        |

| R/W-0               | R/W-0                        | R/W-1                                                 | R/W-0                                                | R/C-0               | R-0             | R/W-0           | R/W-0      |

| SATA                | SATB                         | SATDW                                                 | ACCSAT                                               | IPL3 <sup>(2)</sup> | SFA             | RND             | IF         |

| bit 7               | SAID                         | SAIDW                                                 | ACCOAL                                               | IF LOV /            | SFA             | RIND            | bit        |

| Legend:             |                              | C = Clearable                                         | - bit                                                |                     |                 |                 |            |

| R = Readable        | bit                          | W = Writable                                          |                                                      | U = Unimplem        | onted hit rea   | d as '0'        |            |

| -n = Value at F     |                              | '1' = Bit is set                                      |                                                      | '0' = Bit is clea   |                 | x = Bit is unkr |            |

|                     | -                            |                                                       |                                                      |                     |                 |                 |            |

| bit 15              | 1 = Variable e               | exception proce                                       | ocessing Later<br>essing latency                     | is enabled          |                 |                 |            |

| L:4 4 4             |                              |                                                       | sing latency is                                      | enabled             |                 |                 |            |

| bit 14<br>bit 13-12 | •                            | ted: Read as '                                        | 0<br>igned/Signed (                                  | Control hito        |                 |                 |            |

|                     | 01 = DSP eng<br>00 = DSP eng | gine multiplies<br>gine multiplies<br>gine multiplies | are signed                                           |                     |                 |                 |            |

| bit 11              |                              |                                                       | ation Control bi<br>e $DO$ loop at th                | e end of the cu     | rrent loop iter | ation           |            |

| bit 10-8            | 111 = 7 DO lo                | ops are active                                        |                                                      | ts                  |                 |                 |            |

| bit 7               |                              | Saturation En                                         |                                                      |                     |                 |                 |            |

|                     |                              | ator A saturatio<br>ator A saturatio                  |                                                      |                     |                 |                 |            |

| bit 6               | 1 = Accumula                 | Saturation En<br>ator B saturatio<br>ator B saturatio | n is enabled                                         |                     |                 |                 |            |

| bit 5               | 1 = Data Space               | ce write satura                                       | from DSP Engi<br>tion is enabled<br>tion is disabled |                     | Enable bit      |                 |            |

| bit 4               | -                            | cumulator Satu                                        | ration Mode S                                        |                     |                 |                 |            |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### 4.3 Special Function Register Maps

### TABLE 4-1: CPU CORE REGISTER MAP

| IADLL 4     | - • • |        |        | LOISIL     |             |           |        |           |             |              |       |            |              |              |             |       |       |                   |

|-------------|-------|--------|--------|------------|-------------|-----------|--------|-----------|-------------|--------------|-------|------------|--------------|--------------|-------------|-------|-------|-------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12      | Bit 11    | Bit 10 | Bit 9     | Bit 8       | Bit 7        | Bit 6 | Bit 5      | Bit 4        | Bit 3        | Bit 2       | Bit 1 | Bit 0 | All<br>Reset<br>s |

| W0          | 0000  |        |        |            |             |           |        |           | W0 (W       | REG)         |       |            |              |              |             |       |       | 0000              |

| W1          | 0002  |        |        |            |             |           |        |           | Ŵ           |              |       |            |              |              |             |       |       | 0000              |

| W2          | 0004  |        |        |            |             |           |        |           | W           | 2            |       |            |              |              |             |       |       | 0000              |

| W3          | 0006  |        |        |            |             |           |        |           | W           | 3            |       |            |              |              |             |       |       | 0000              |

| W4          | 0008  |        |        |            |             |           |        |           | W           | 4            |       |            |              |              |             |       |       | 0000              |

| W5          | 000A  |        |        |            |             |           |        |           | W           | 5            |       |            |              |              |             |       |       | 0000              |

| W6          | 000C  |        |        |            |             |           |        |           | We          | 6            |       |            |              |              |             |       |       | 0000              |

| W7          | 000E  |        |        |            |             |           |        |           | W           | 7            |       |            |              |              |             |       |       | 0000              |

| W8          | 0010  |        |        |            |             |           |        |           | W           | 8            |       |            |              |              |             |       |       | 0000              |

| W9          | 0012  |        |        |            |             |           |        |           | W           | 9            |       |            |              |              |             |       |       | 0000              |

| W10         | 0014  |        |        |            |             |           |        |           | W1          | 0            |       |            |              |              |             |       |       | 0000              |

| W11         | 0016  |        |        |            |             |           |        |           | W1          | 1            |       |            |              |              |             |       |       | 0000              |

| W12         | 0018  |        |        |            |             |           |        |           | W1          | 2            |       |            |              |              |             |       |       | 0000              |

| W13         | 001A  |        |        |            |             |           |        |           | W1          | 3            |       |            |              |              |             |       |       | 0000              |

| W14         | 001C  |        |        |            |             |           |        |           | W1          | 4            |       |            |              |              |             |       |       | 0000              |

| W15         | 001E  |        |        |            |             |           |        |           | W1          | 5            |       |            |              |              |             |       |       | 0800              |

| SPLIM       | 0020  |        |        |            |             |           |        |           | SPL         | IM           |       |            |              |              |             |       |       | xxxx              |

| ACCAL       | 0022  |        |        |            |             |           |        |           | ACC         | AL           |       |            |              |              |             |       |       | xxxx              |

| ACCAH       | 0024  |        |        |            |             |           |        |           | ACC         | AH           |       |            |              |              |             |       |       | xxxx              |

| ACCAU       | 0026  |        |        | Sig        | n Extension | of ACCA<3 | 9>     |           |             |              |       |            | ACC          | CAU          |             |       |       | xxxx              |

| ACCBL       | 0028  |        |        |            |             |           |        |           | ACC         | BL           |       |            |              |              |             |       |       | xxxx              |

| ACCBH       | 002A  |        |        |            |             |           |        |           | ACC         | BH           |       |            |              |              |             |       |       | xxxx              |

| ACCBU       | 002C  |        |        | Sig        | n Extension | of ACCB<3 | 9>     |           |             |              |       |            | ACC          | CBU          |             |       |       | xxxx              |

| PCL         | 002E  |        |        |            |             |           | Pro    | ogram Cou | nter Low We | ord Register | r     |            |              |              |             |       | _     | 0000              |

| PCH         | 0030  | _      | _      | _          | _           | _         | _      | _         | _           | _            |       | F          | Program Cou  | inter High W | ord Registe | r     |       | 0000              |

| DSRPAG      | 0032  | _      | _      | _          | _           | _         | _      |           |             |              | Dat   | a Space Re | ad Page Reg  | gister       |             |       |       | 0001              |

| DSWPAG      | 0034  | —      | _      |            |             | _         | _      | _         |             |              |       | Data Spa   | ce Write Pag | e Register   |             |       |       | 0001              |

| RCOUNT      | 0036  |        |        |            |             |           |        | REPEAT LC | op Counter  | Register     |       |            |              |              |             |       | 0     | xxxx              |

| DCOUNT      | 0038  |        |        |            |             |           |        | DC        | OUNT<15:1   | >            |       |            |              |              |             |       | 0     | xxxx              |

| DOSTARTL    | 003A  |        |        |            |             |           |        | DOS       | TARTL<15    | :1>          |       |            |              |              |             |       | 0     | xxxx              |

| DOSTARTH    | 003C  | _      | _      |            | _           |           |        | _         | _           | _            | _     |            |              | DOSTART      | H<5:0>      |       |       | 00xx              |

| DOENDL      | 003E  |        |        |            |             |           |        | DO        | ENDL<15:1   | >            |       |            |              |              |             |       | —     | xxxx              |

| Lanandi     |       |        |        | - unimalar |             |           |        |           |             |              |       |            |              |              |             |       |       |                   |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: PMD REGISTER MAP FOR dsPIC33EVXXXGM00X/10X FAMILY DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1               | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|---------|---------|--------|--------|--------|--------|-------|-------|--------|--------|--------|---------------------|-------|---------------|

| PMD1        | 0760  | T5MD   | T4MD   | T3MD   | T2MD    | T1MD    | _      | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD <sup>(1)</sup> | AD1MD | 0000          |

| PMD2        | 0762  | _      | —      | —      | —       | IC4MD   | IC3MD  | IC2MD  | IC1MD  |        | —     |       | _      | OC4MD  | OC3MD  | OC2MD               | OC1MD | 0000          |

| PMD3        | 0764  | —      | —      | —      | —       | —       | CMPMD  | _      | _      |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD4        | 0766  | —      | —      | —      | —       | —       | —      | _      | _      |        | —     |       | _      | REFOMD | CTMUMD | _                   | —     | 0000          |

| PMD6        | 076A  | —      | —      | —      | —       | —       | PWM3MD | PWM2MD | PWM1MD |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

| PMD7        | 076C  | _      | —      | —      | —       | -       | —      | —      | _      | -      | —     | -     | DMA0MD | —      | —      |                     | —     | 0000          |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA1MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA2MD |        |        |                     |       |               |

|             |       |        |        |        |         |         |        |        |        |        |       |       | DMA3MD |        |        |                     |       |               |

| PMD8        | 076E  | —      | —      | —      | SENT2MD | SENT1MD | —      | _      | DMTMD  |        | —     |       | _      | —      | —      | _                   | —     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This feature is available only on dsPIC33EVXXXGM10X devices.

### TABLE 4-31: PORTA REGISTER MAP FOR dsPIC33EVXXXGMX06 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|--------|-------|-------|-------|--------|---------------|

| TRISA       | 0E00  | _      | —      | —      |        |            | TRISA< | 12:7>  |       |       | —     | —     | TRISA4 | —     | _     | TRISA | <1:0>  | 1F93          |

| PORTA       | 0E02  | _      | —      | —      |        |            | RA<12  | 2:7>   |       |       |       | —     | RA4    | —     | -     | RA<   | 1:0>   | 0000          |

| LATA        | 0E04  | _      | —      | —      |        |            | LATA<1 | 2:7>   |       |       |       | —     | LATA4  | —     | -     | LATA  | <1:0>  | 0000          |

| ODCA        | 0E06  | —      | —      | —      |        |            | ODCA<  | 12:7>  |       |       |       | _     | ODCA4  | —     | -     | ODCA  | <1:0>  | 0000          |

| CNENA       | 0E08  | _      | _      | _      |        |            | CNIEA< | 12:7>  |       |       | _     | _     | CNIEA4 | _     | _     | CNIEA | <1:0>  | 0000          |

| CNPUA       | 0E0A  | —      | —      | —      |        |            | CNPUA< | :12:7> |       |       |       | _     | CNPUA4 | —     | -     | CNPU  | ۹<1:0> | 0000          |

| CNPDA       | 0E0C  | _      | _      | _      |        |            | CNPDA< | :12:7> |       |       | _     | _     | CNPDA4 | _     | _     | CNPD  | A<1:0> | 0000          |

| ANSELA      | 0E0E  | _      | —      | —      |        | ANSA<12:9> |        |        |       | ANSA7 |       | —     | ANSA4  | —     | -     | ANSA  | <1:0>  | 1E93          |

| SR1A        | 0E10  | _      | —      | —      |        | —          | _      | SR1A9  |       |       |       | —     | SR1A4  | —     | -     |       |        | 0000          |

| SR0A        | 0E12  | _      | _      | —      |        | _          | _      | SR0A9  |       |       |       | —     | SR0A4  | —     | _     |       | _      | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-32: PORTA REGISTER MAP FOR dsPIC33EVXXXGMX04 DEVICES

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10             | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3     | Bit 2      | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|--------|--------|--------|--------|--------------------|-------|--------|-------|-------|-------|------------|-----------|------------|-------|-------|---------------|

| TRISA       | 0E00  | _      | _      | _      | _      | _      |                    | TRISA | <10:7> |       | —     | —     |            | -         | TRISA<4:0> | >     |       | DF9F          |

| PORTA       | 0E02  | _      | _      | _      | _      | _      |                    | RA<1  | 0:7>   |       | —     | —     |            |           | RA<4:0>    |       |       | 0000          |

| LATA        | 0E04  | —      | _      | _      | _      | _      |                    | LATA< | 10:7>  |       |       | —     |            |           | LATA<4:0>  |       |       | 0000          |

| ODCA        | 0E06  | —      | _      | _      | _      | _      |                    | ODCA< | <10:7> |       |       | —     |            | (         | ODCA<4:0>  | >     |       | 0000          |

| CNENA       | 0E08  | —      | —      | _      | _      |        |                    | CNIEA | <10:7> |       |       | —     | CNIEA<4:0> |           |            |       | 0000  |               |

| CNPUA       | 0E0A  | —      | —      | _      | _      |        |                    | CNPUA | <10:7> |       |       | —     | CNPUA<4:0> |           |            |       |       | 0000          |

| CNPDA       | 0E0C  | —      | —      | _      | _      |        |                    | CNPDA | <10:7> |       |       | —     |            | C         | NPDA<4:0   | >     |       | 0000          |

| ANSELA      | 0E0E  | —      | —      | _      | _      |        | ANSA<10:9> — ANSA7 |       |        | —     | ANSA4 | —     |            | ANSA<2:0> | •          | 1813  |       |               |

| SR1A        | 0E10  | —      | —      | _      | _      |        |                    | SR1A9 | _      | _     |       | —     | SR1A4      | —         | —          |       |       | 0000          |

| SR0A        | 0E12  | —      | —      | _      | _      |        |                    | SR0A9 | _      | _     |       | —     | SR0A4      | —         | —          |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### FIGURE 4-17: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

### **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 3 | SLEEP: Wake-up from Sleep Flag bit     |

|-------|----------------------------------------|

|       | 1 = Device has been in Sleep mode      |

|       | 0 = Device has not been in Sleep mode  |

| bit 2 | IDLE: Wake-up from Idle Flag bit       |

|       | 1 = Device was in Idle mode            |

|       | 0 = Device was not in Idle mode        |

| bit 1 | BOR: Brown-out Reset Flag bit          |

|       | 1 = A Brown-out Reset has occurred     |

|       | 0 = A Brown-out Reset has not occurred |

| bit 0 | POR: Power-on Reset Flag bit           |

|       | 1 = A Power-on Reset has occurred      |

|       | 0 = A Power-on Reset has not occurred  |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN<1:0> Configuration bits are '11' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

### 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EVXXXGM00X/10X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

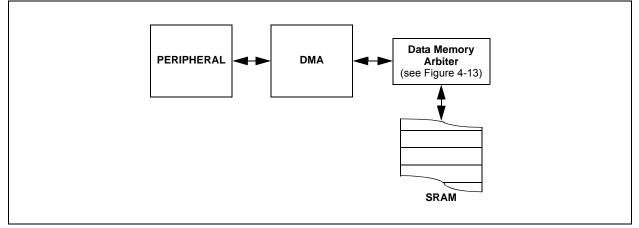

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM. For the simplified DMA block diagram, refer to Figure 8-1.

In addition, DMA can access the entire data memory space. The data memory bus arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. The peripherals supported by the DMA Controller include:

- CAN

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

### FIGURE 8-1: PERIPHERAL TO DMA CONTROLLER

### **REGISTER 8-7:** DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | PAI   | )<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 PAD<15:0>: DMA Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0            | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|------------------|-------|-------|

| —      | —   |       |       | CNT<  | 13:8> <b>(2)</b> |       |       |

| bit 15 |     |       |       |       |                  |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-----------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <b>(2)</b> |       |       |       |

| bit 7 |       |       |       |                 |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- **2:** The number of DMA transfers = CNT<13:0> + 1.

| U-0          | U-0                  | U-0              | U-0 | U-0              | U-0              | U-0             | U-0    |

|--------------|----------------------|------------------|-----|------------------|------------------|-----------------|--------|

| _            | —                    | —                | —   | —                | —                | —               | —      |

| bit 15       |                      |                  |     |                  |                  |                 | bit    |

|              |                      |                  |     |                  |                  |                 |        |

| U-0          | U-0                  | U-0              | U-0 | R-0              | R-0              | R-0             | R-0    |

| _            | —                    | —                | —   | PWCOL3           | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7        |                      |                  |     |                  |                  |                 | bit    |

|              |                      |                  |     |                  |                  |                 |        |

| Legend:      |                      |                  |     |                  |                  |                 |        |

| R = Readab   | le bit               | W = Writable     | bit | U = Unimpler     | nented bit, read | as '0'          |        |

| -n = Value a | t POR                | '1' = Bit is set |     | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

|              |                      |                  |     |                  |                  |                 |        |

| bit 15-4     | Unimplemen           | ted: Read as '   | 0'  |                  |                  |                 |        |

| bit 3        |                      | annel 3 Periph   |     | Ilision Flag bit |                  |                 |        |

|              | $\perp = vvrite col$ | ision is detecte | a   |                  |                  |                 |        |

### REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

| 1 = Write collision is detected     |

|-------------------------------------|

| 0 = Write collision is not detected |

|                                     |

0 = Write collision is not detected

1 = Write collision is detected0 = Write collision is not detected

PWCOL2: Channel 2 Peripheral Write Collision Flag bit

PWCOL1: Channel 1 Peripheral Write Collision Flag bit

bit 0 PWCOL0: Channel 0 Peripheral Write Collision Flag bit

- 1 = Write collision is detected

- 0 = Write collision is not detected

bit 2

bit 1

### REGISTER 17-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7-6       | <b>DTC&lt;1:0&gt;:</b> Dead-Time Control bits<br>11 = Dead-Time Compensation mode<br>10 = Dead-time function is disabled<br>01 = Negative dead time is actively applied for Complementary Output mode<br>00 = Positive dead time is actively applied for all Output modes |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | DTCP: Dead-Time Compensation Polarity bit <sup>(3)</sup><br><u>When Set to '1':</u><br>If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                           |

|               | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.<br>If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                       |

| bit 4-3       | Unimplemented: Read as '0'                                                                                                                                                                                                                                                |

| bit 2         | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                                                                                                      |

|               | 1 = Center-Aligned mode is enabled<br>0 = Edge-Aligned mode is enabled                                                                                                                                                                                                    |

| bit 1         | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                                                                                                     |

|               | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base mode</li> <li>0 = External pins do not affect PWMx time base</li> </ul>                                                                                   |

| bit 0         | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                                                                                                           |

|               | <ul> <li>1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate</li> <li>0 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the PWMx period boundary</li> </ul>                                                 |

| Note 1:<br>2: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.<br>These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                    |

| 3:            | DTC<1:0> = 11 for DTCP to be effective; else, DTCP is ignored.                                                                                                                                                                                                            |

- 4: The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.

- **5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

## 19.2 I<sup>2</sup>C Control Registers

### REGISTER 19-1: I2CxCON1: I2Cx CONTROL REGISTER 1

| R/W-0  | U-0 | R/W-0   | R/S-1                 | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|---------|-----------------------|--------|-------|--------|-------|

| I2CEN  |     | I2CSIDL | SCLREL <sup>(1)</sup> | STRICT | A10M  | DISSLW | SMEN  |

| bit 15 |     |         |                       |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 | •     |       | •         |           | •         |           | bit 0     |

| Legend:           | Legend:S = Settable bitHC = Hardware Clearable bit |                               |                    |  |

|-------------------|----------------------------------------------------|-------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                   | U = Unimplemented bit, read a | <b>as</b> '0'      |  |

| -n = Value at POR | '1' = Bit is set                                   | '0' = Bit is cleared          | k = Bit is unknown |  |

| bit 15  | I2CEN: I2Cx Enable bit (writable from SW only)                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enables the I<sup>2</sup>C module and configures the SDAx and SCLx pins as serial port pins</li> <li>0 = Disables the I<sup>2</sup>C module and all I<sup>2</sup>C pins are controlled by port functions</li> </ul> |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                       |

| bit 13  | I2CSIDL: I2Cx Stop in Idle Mode bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Discontinues module operation when the device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                      |

| bit 12  | SCLREL: SCLx Release Control bit (I <sup>2</sup> C Slave mode only) <sup>(1)</sup>                                                                                                                                               |

|         | Module resets and (I2CEN = 0) sets SCLREL = 1.                                                                                                                                                                                   |

|         | $\frac{\text{If STREN = }0}{2}$                                                                                                                                                                                                  |

|         | 1 = Releases clock                                                                                                                                                                                                               |

|         | 0 = Forces clock low (clock stretch)                                                                                                                                                                                             |

|         | If STREN = 1:<br>1 = Releases clock                                                                                                                                                                                              |

|         | 0 = Holds clock low (clock stretch); user may program this bit to '0', clock stretch at the next SCLx low                                                                                                                        |

| bit 11  | STRICT: Strict I <sup>2</sup> C Reserved Address Rule Enable bit                                                                                                                                                                 |

|         | 1 = Strict reserved addressing is enforced                                                                                                                                                                                       |

|         | In Slave mode, the device does not respond to reserved address space and addresses falling in that category are NACKed.                                                                                                          |

|         | 0 = Reserved addressing would be Acknowledged                                                                                                                                                                                    |

|         | In Slave mode, the device will respond to an address falling in the reserved address space. When there is a match with any of the reserved addresses, the device will generate an ACK.                                           |

| bit 10  | A10M: 10-Bit Slave Address Flag bit                                                                                                                                                                                              |

|         | 1 = I2CxADD is a 10-bit slave address<br>0 = I2CxADD is a 7-bit slave address                                                                                                                                                    |

| bit 9   | DISSLW: Slew Rate Control Disable bit                                                                                                                                                                                            |

|         | <ul> <li>1 = Slew rate control is disabled for Standard Speed mode (100 kHz, also disabled for 1 MHz mode)</li> <li>0 = Slew rate control is enabled for High-Speed mode (400 kHz)</li> </ul>                                    |

| bit 8   | SMEN: SMBus Input Levels Enable bit                                                                                                                                                                                              |

|         | <ul> <li>1 = Enables the input logic so thresholds are compliant with the SMBus specification</li> <li>0 = Disables the SMBus-specific inputs</li> </ul>                                                                         |

| Note 1: | Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.                                                                                                 |

**2:** Automatically cleared to '0' at the beginning of slave transmission.

| R/W-0         | R/W-0                                                                                          | R/W-0            | R/W-0            | R/W-0         | R/W-0            | R/W-0              | R/W-0  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------|------------------|------------------|---------------|------------------|--------------------|--------|--|--|--|

| F15BP3        | F15BP2                                                                                         | F15BP1           | F15BP0           | F14BP3 F14BP2 |                  | F14BP1             | F14BP0 |  |  |  |

| bit 15        |                                                                                                |                  |                  |               | •                |                    | bit 8  |  |  |  |

|               |                                                                                                |                  |                  |               |                  |                    |        |  |  |  |

| R/W-0         | R/W-0                                                                                          | R/W-0            | R/W-0            | R/W-0         | R/W-0            | R/W-0              | R/W-0  |  |  |  |

| F13BP3        | F13BP2                                                                                         | F13BP1           | F13BP0           | F12BP3        | F12BP2           | F12BP1             | F12BP0 |  |  |  |

| bit 7         |                                                                                                |                  |                  |               |                  |                    | bit 0  |  |  |  |

|               |                                                                                                |                  |                  |               |                  |                    |        |  |  |  |

| Legend:       |                                                                                                |                  |                  |               |                  |                    |        |  |  |  |

| R = Readable  | e bit                                                                                          | W = Writable bit |                  | U = Unimpler  | mented bit, read | <b>l as</b> '0'    |        |  |  |  |

| -n = Value at | POR                                                                                            | '1' = Bit is set | ' = Bit is set   |               | ared             | x = Bit is unknown |        |  |  |  |

|               |                                                                                                |                  |                  |               |                  |                    |        |  |  |  |

| bit 15-12     | F15BP<3:0>:                                                                                    | RX Buffer Ma     | sk for Filter 15 | 5 bits        |                  |                    |        |  |  |  |

|               | 1111 = Filter                                                                                  | hits received in | n RX FIFO but    | ffer          |                  |                    |        |  |  |  |

|               | 1110 <b>= Filter</b>                                                                           | hits received in | n RX Buffer 14   | ļ.            |                  |                    |        |  |  |  |

|               | •                                                                                              |                  |                  |               |                  |                    |        |  |  |  |

|               | •                                                                                              |                  |                  |               |                  |                    |        |  |  |  |

|               | 0001 <b>= Filter</b>                                                                           | hits received ir | n RX Buffer 1    |               |                  |                    |        |  |  |  |

|               | 0000 = Filter hits received in RX Buffer 0                                                     |                  |                  |               |                  |                    |        |  |  |  |

| bit 11-8      | it 11-8 <b>F14BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 14 bits (same values as bits 15-12) |                  |                  |               |                  |                    |        |  |  |  |

| bit 7-4       | <b>F13BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 13 bits (same values as bits 15-12)         |                  |                  |               |                  |                    |        |  |  |  |

| bit 3-0       | F12BP<3:0>: RX Buffer Mask for Filter 12 bits (same values as bits 15-12)                      |                  |                  |               |                  |                    |        |  |  |  |

|               |                                                                                                |                  |                  |               |                  |                    |        |  |  |  |

### REGISTER 22-15: CxBUFPNT4: CANx FILTERS 12-15 BUFFER POINTER REGISTER 4

### REGISTER 22-16: CxRXFnSID: CANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

|               |                            | -                                                                                                                                                  | •            |                   |                  |                 |       |  |  |  |  |

|---------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| R/W-x         | R/W-x                      | R/W-x                                                                                                                                              | R/W-x        | R/W-x             | R/W-x            | R/W-x           | R/W-x |  |  |  |  |

| SID10         | SID9                       | SID8                                                                                                                                               | SID7         | SID6              | SID5             | SID4            | SID3  |  |  |  |  |

| bit 15        |                            |                                                                                                                                                    |              |                   |                  |                 | bit 8 |  |  |  |  |

|               |                            |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

| R/W-x         | R/W-x                      | R/W-x                                                                                                                                              | U-0          | R/W-x             | U-0              | R/W-x           | R/W-x |  |  |  |  |

| SID2          | SID1                       | SID0                                                                                                                                               |              | EXIDE             |                  | EID17           | EID16 |  |  |  |  |

| bit 7         |                            |                                                                                                                                                    |              |                   |                  |                 | bit C |  |  |  |  |

|               |                            |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

| Legend:       |                            |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

| R = Readabl   | e bit                      | W = Writable                                                                                                                                       | bit          | U = Unimpler      | nented bit, read | <b>as</b> '0'   |       |  |  |  |  |

| -n = Value at | POR                        | '1' = Bit is set                                                                                                                                   |              | '0' = Bit is cle  | ared             | x = Bit is unkr | Iown  |  |  |  |  |

|               |                            |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

| bit 15-5      | SID<10:0>: S               | Standard Identif                                                                                                                                   | ier bits     |                   |                  |                 |       |  |  |  |  |

|               | 0                          |                                                                                                                                                    | •            | 1' to match filte |                  |                 |       |  |  |  |  |

|               | 0                          | -                                                                                                                                                  |              | 0' to match filte | er               |                 |       |  |  |  |  |

| bit 4         | Unimplemen                 | ted: Read as '                                                                                                                                     | 0'           |                   |                  |                 |       |  |  |  |  |

| bit 3         | EXIDE: Exter               | nded Identifier I                                                                                                                                  | Enable bit   |                   |                  |                 |       |  |  |  |  |

|               | If MIDE = 1:               |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

|               |                            | , ,                                                                                                                                                |              | ed Identifier add |                  |                 |       |  |  |  |  |

|               | 0 = Matches                | only messages                                                                                                                                      | with Standar | d Identifier add  | resses           |                 |       |  |  |  |  |

|               | Ignores EXID               | )E bit.                                                                                                                                            |              |                   |                  |                 |       |  |  |  |  |

| bit 2         | Unimplemented: Read as '0' |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

| bit 1-0       | •                          | Extended Iden                                                                                                                                      |              |                   |                  |                 |       |  |  |  |  |

|               |                            |                                                                                                                                                    |              | 1' to match filte | er               |                 |       |  |  |  |  |

|               | 0                          | <ul> <li>1 = Message address bit, EIDx, must be '1' to match filter</li> <li>0 = Message address bit, EIDx, must be '0' to match filter</li> </ul> |              |                   |                  |                 |       |  |  |  |  |

|               | 0                          |                                                                                                                                                    |              |                   |                  |                 |       |  |  |  |  |

### REGISTER 22-17: CxRXFnEID: CANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x                              | R/W-x      | R/W-x              | R/W-x   | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|------------------------------------|------------|--------------------|---------|------------------------------------|-------|-----------------|-------|--|

|                                    |            |                    | EID     | <15:8>                             |       |                 |       |  |

| bit 15                             |            |                    |         |                                    |       |                 | bit 8 |  |

| R/W-x                              | R/W-x      | R/W-x              | R/W-x   | R/W-x                              | R/W-x | R/W-x           | R/W-x |  |

|                                    |            |                    | EID     | )<7:0>                             |       |                 |       |  |

| bit 7                              |            |                    |         |                                    |       |                 | bit 0 |  |

| Legend:                            |            |                    |         |                                    |       |                 |       |  |

| R = Readable                       | bit        | W = Writable b     | it      | U = Unimplemented bit, read as '0' |       |                 |       |  |

| -n = Value at POR '1' = Bit is set |            |                    |         | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |

|                                    |            |                    |         |                                    |       |                 |       |  |

| bit 15-0                           | EID<15:0>: | Extended Identifie | er bits |                                    |       |                 |       |  |

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

### 30.2 AC Characteristics and Timing Parameters

This section defines the dsPIC33EVXXXGM00X/10X family AC characteristics and timing parameters.

### TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 4.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for ExtendedOperating voltage VDD range as described in Section 30.1 "DCCharacteristics". |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

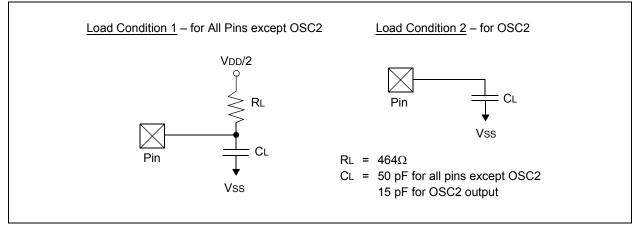

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                          |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | —    | 15   | pF    | In XT and HS modes, when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | —    | —    | 50   | pF    | EC mode                                                             |

| DO58         | Св     | SCLx, SDAx            | _    |      | 400  | pF    | In I <sup>2</sup> C mode                                            |

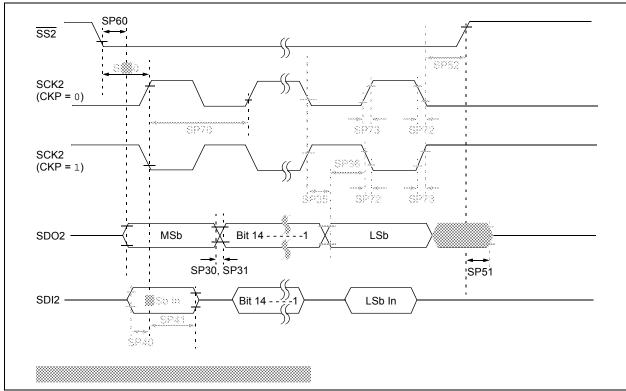

# FIGURE 30-17: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-44:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

|        |                       |                                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                      |  |

|--------|-----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |  |

| SP70   | FscP                  | Maximum SCK1 Input Frequency                                                 |                                                                                                                                                                                                                                                                                         | _                   | 25   | MHz   | See Note 3                           |  |

| SP72   | TscF                  | SCK1 Input Fall Time                                                         | —                                                                                                                                                                                                                                                                                       |                     |      | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP73   | TscR                  | SCK1 Input Rise Time                                                         | _                                                                                                                                                                                                                                                                                       |                     |      | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                                                   | —                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                                                   | —                                                                                                                                                                                                                                                                                       |                     |      | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge                                    | —                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                                      |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge                                 | 20                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                      |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge                                   | 20                                                                                                                                                                                                                                                                                      |                     |      | ns    |                                      |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge                                    | 15                                                                                                                                                                                                                                                                                      | _                   | _    | ns    |                                      |  |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SS1} \downarrow$ to SCK1 $\uparrow$ or SCK1 $\downarrow$<br>Input | 120                                                                                                                                                                                                                                                                                     | —                   | _    | ns    |                                      |  |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance                                       | 10                                                                                                                                                                                                                                                                                      | _                   | 50   | ns    | See Note 4                           |  |

| SP52   | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                                                        | 1.5 Tcy + 40                                                                                                                                                                                                                                                                            |                     | _    | ns    | See Note 4                           |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ." column is at 5.0V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 40 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

**4:** Assumes 50 pF load on all SPI1 pins.

| DC CHARACTERISTICS  |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 4.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |      |       |                                   |

|---------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|-----------------------------------|

| Param<br>No.        | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min. | Тур.  | Max. | Units | Conditions                        |

| CTMU Current Source |        |                                                                                                                                                                                                                                                                                         |      |       |      |       |                                   |

| CTMUI1              | IOUT1  | Base Range                                                                                                                                                                                                                                                                              | _    | 550   | _    | nA    | CTMUICON<9:8> = 01                |

| CTMUI2              | IOUT2  | 10x Range                                                                                                                                                                                                                                                                               | —    | 5.5   | _    | μA    | CTMUICON<9:8> = 10                |

| CTMUI3              | Ιουτ3  | 100x Range                                                                                                                                                                                                                                                                              | —    | 55    | _    | μA    | CTMUICON<9:8> = 11                |

| CTMUI4              | IOUT4  | 1000x Range                                                                                                                                                                                                                                                                             | —    | 550   | _    | μA    | CTMUICON<9:8> = 00                |